Timing Diagram Mvi A, 32

Diunggah oleh

Rohan VaidyaDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Timing Diagram Mvi A, 32

Diunggah oleh

Rohan VaidyaHak Cipta:

Format Tersedia

0 62.

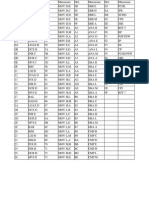

Draw the 8085 timing of execution of the 2 byte instruction MVI A, 32H (load the accumulator with the data 32 H) store in location as follows Memory location Machine Code Mnemonics 2000 3E MVIA,32H 2000 32 Ans.

This is a 2 byte instruction so it requires 2 machine cycles to fetch the instruction I Op code fetch and 2 Memory read 1 OPCODE fetch The program counter places the address on the higher order and the lower order address bus The op code at this memory location is read into the microprocessor The PC is then incremented by 1 to point to the next byte This machine cycles requires 4 T states This is a 2 byte instruction so it requires 2 machine cycles to fetch the instruction I Op code fetch and 2 Memory read 1 OPCODE fetch The program counter places the address on the higher order and the lower order address bus The op code at this memory location is read into the

microprocessor The PC is then incremented by 1 to point to the next byte This machine cycles requires 4 T states 2 Memory Read The data is read from the addressed memory location into the specific register The PC is again incremented by one to point to next instruction after MVI The same timing diagram is applicable to following instructions also ACI data ADI data, ANI data CPI data, CR1 data, SUI data SBI data, XRI data MVI R, data The only difference is that op codes for these instructions are different

Anda mungkin juga menyukai

- PCB-Design-Training Report (Summer Internship)Dokumen27 halamanPCB-Design-Training Report (Summer Internship)soundarya raghuwanshi86% (7)

- Blood Bank Management System ReportDokumen29 halamanBlood Bank Management System ReportHVXajbckBelum ada peringkat

- Unit - V Procedure and Macro: (12 - Marks)Dokumen18 halamanUnit - V Procedure and Macro: (12 - Marks)50harsh palyekarBelum ada peringkat

- Arm7 - Lpc2148 Embedded Processor Based ProjectsDokumen2 halamanArm7 - Lpc2148 Embedded Processor Based ProjectsManish Narkhede75% (4)

- 8086 Microprocessor Interfacing MCQ SDokumen4 halaman8086 Microprocessor Interfacing MCQ SDeepak Ahlawat67% (3)

- Assembler Directives and OperatorsDokumen6 halamanAssembler Directives and Operatorsvijaykannamalla100% (1)

- Gtu IOT PracticalsDokumen65 halamanGtu IOT Practicalsbaba100% (1)

- SMPS PPT Summer Traning by VijayDokumen60 halamanSMPS PPT Summer Traning by VijayVijay Kaplsya86% (7)

- Digital Visitor Counter Using 8051 MicrocontrollerDokumen23 halamanDigital Visitor Counter Using 8051 MicrocontrollerChandra Bhanu83% (24)

- Clap Switch Report EditedDokumen47 halamanClap Switch Report EditedKeshav Krishna60% (5)

- Assignment-3 Ch3 Question 1-10: CL, DH, and DLDokumen3 halamanAssignment-3 Ch3 Question 1-10: CL, DH, and DLRitika100% (1)

- System Software Question Bank 2012 With Part-B AnswersDokumen49 halamanSystem Software Question Bank 2012 With Part-B Answerssumathi7975% (16)

- Linear Integrated Circuit Questions and AnswersDokumen22 halamanLinear Integrated Circuit Questions and Answerselakya79% (24)

- Fire Fighting Robot PPT 1Dokumen12 halamanFire Fighting Robot PPT 1naveennaresh63% (8)

- ITSU 1001 Introduction To Computer Systems and Networking: Tutorial 5 For Lesson 5Dokumen5 halamanITSU 1001 Introduction To Computer Systems and Networking: Tutorial 5 For Lesson 5Rakesh ydavBelum ada peringkat

- 8051 Microcontroller (2 Marks - Question Bank)Dokumen13 halaman8051 Microcontroller (2 Marks - Question Bank)Dr. N.Shanmugasundaram97% (34)

- Digital Signal Processor C5X Addressing ModesDokumen40 halamanDigital Signal Processor C5X Addressing ModesGurjeet Singh60% (5)

- Introduction 89C51/8051 Microcontroller Kit of Vi MicrosystemsDokumen20 halamanIntroduction 89C51/8051 Microcontroller Kit of Vi MicrosystemsAssini Hussain83% (6)

- 8086 and Memory Interfacing - FinalDokumen28 halaman8086 and Memory Interfacing - FinalAnushkaSinha100% (2)

- Addressing Mode Numerical ExampleBCA (TU) Second SemesterDokumen11 halamanAddressing Mode Numerical ExampleBCA (TU) Second SemesterAvishek Ranjitkar100% (2)

- Microcontroller Lab Viva Questions & AnswersDokumen29 halamanMicrocontroller Lab Viva Questions & AnswersAmbika Narayan73% (15)

- Microcontroller Viva Questions and AnswersDokumen5 halamanMicrocontroller Viva Questions and Answerspankaj yadav100% (2)

- MPMC 2marks (Unit 1 To 5) (Q & A)Dokumen32 halamanMPMC 2marks (Unit 1 To 5) (Q & A)Ganapathy Ramadoss100% (2)

- Microprocessor Viva Questions and AnswersDokumen9 halamanMicroprocessor Viva Questions and Answersdhiliban198975% (8)

- Module-6 Thumb Instruction SetDokumen54 halamanModule-6 Thumb Instruction Setsai Karthik100% (1)

- Single-Node Architecture: Hardware ComponentsDokumen43 halamanSingle-Node Architecture: Hardware ComponentsRavi AnnepakaBelum ada peringkat

- Unit - Iii Instruction Set of 8086 Microprocessor: (16 - Marks)Dokumen54 halamanUnit - Iii Instruction Set of 8086 Microprocessor: (16 - Marks)50harsh palyekar100% (1)

- Department of Electrical & Electronics Engineering: Mini Project Presentation On "Automatic Street Light"Dokumen21 halamanDepartment of Electrical & Electronics Engineering: Mini Project Presentation On "Automatic Street Light"Ayush Kumar67% (3)

- Basic Operational ConceptsDokumen2 halamanBasic Operational ConceptsHarinath Ramamoorthy67% (3)

- Question With Answer MP & MCDokumen13 halamanQuestion With Answer MP & MCMATHANKUMAR.SBelum ada peringkat

- Report Project StopwatchDokumen21 halamanReport Project StopwatchMr Predator97% (36)

- AVR Microcontroller Question BankDokumen2 halamanAVR Microcontroller Question BankmadhurithkBelum ada peringkat

- The 8051 Mcq'sDokumen7 halamanThe 8051 Mcq'sAnsh Vashist75% (4)

- Turn ON and Off Characteristics of SCRDokumen17 halamanTurn ON and Off Characteristics of SCRVedant .Chavan100% (2)

- 8085 Lab Viva QuestionsDokumen7 halaman8085 Lab Viva Questionsgdfgdflgjlk100% (2)

- 8086 Interrupts and Interrupt ResponsesDokumen8 halaman8086 Interrupts and Interrupt ResponsesNiharika Korukonda100% (1)

- COA Unit-1 FinalDokumen34 halamanCOA Unit-1 Finalpriyanka60% (5)

- 8155 Programmable InterfaceDokumen25 halaman8155 Programmable InterfaceDilesh Jeewon88% (26)

- Full Form of Networking TermsDokumen2 halamanFull Form of Networking TermsPrem Abish Pokhrel75% (4)

- DSP Important Viva QuestionsDokumen3 halamanDSP Important Viva QuestionsDeepak Sahu100% (2)

- Register Organization of 8086 PDFDokumen10 halamanRegister Organization of 8086 PDFDevikaBelum ada peringkat

- Microcontroller MCQ QuizDokumen5 halamanMicrocontroller MCQ QuizDeepika SharmaBelum ada peringkat

- Iot Practical FileDokumen21 halamanIot Practical Filetushar0% (2)

- PIC QuestionsDokumen4 halamanPIC Questionsgopikrishnarao100% (1)

- Hex Code of 8085 Assembly LanguageDokumen3 halamanHex Code of 8085 Assembly LanguageAkif Nawab60% (5)

- Experiment 7 AIM To Study The Potentiometer As An Error Detector. APPARATUS: Potentiometric Error Detector Kit Theoretical BackgroundDokumen3 halamanExperiment 7 AIM To Study The Potentiometer As An Error Detector. APPARATUS: Potentiometric Error Detector Kit Theoretical BackgroundSunayana Domadia100% (1)

- Data Patterns Interview QuestionsDokumen2 halamanData Patterns Interview Questionsshafi hasmani67% (3)

- Question Bank Advanced ProcessorsDokumen2 halamanQuestion Bank Advanced ProcessorsManish Narkhede67% (3)

- Temperature Based Fan Speed ControllDokumen30 halamanTemperature Based Fan Speed ControllChethan Chinnu67% (3)

- Introduction To 8051 ProgrammingDokumen24 halamanIntroduction To 8051 Programmingveeramaniks408Belum ada peringkat

- NPCBL Executive Trainee (Electronoics) 2018 QuestionsDokumen6 halamanNPCBL Executive Trainee (Electronoics) 2018 QuestionsAnonymous BFawKerBelum ada peringkat

- Power Electronics VivaDokumen7 halamanPower Electronics VivaAbhay Shankar Bharadwaj100% (1)

- PS 2 Viva Question and AnswersDokumen5 halamanPS 2 Viva Question and AnswersPraveen Nayak Bhukya0% (3)

- Interfacing A Multiplexed Seven Segment Display With The 8086 MicroprocessorDokumen9 halamanInterfacing A Multiplexed Seven Segment Display With The 8086 Microprocessorshourya sinhaBelum ada peringkat

- Timing and Control UnitDokumen22 halamanTiming and Control Unitaditya88_4u0% (1)

- Reset Circuit of 8051 ControllerDokumen3 halamanReset Circuit of 8051 ControllerSuwilanji Joshua Chilongo100% (1)

- Chapter 2introduction To The C2xx DSP Core and Code GenerationDokumen4 halamanChapter 2introduction To The C2xx DSP Core and Code Generationdivya624Belum ada peringkat

- 8051 MCQDokumen25 halaman8051 MCQRohan Bachhav100% (1)

- Chapter 4Dokumen71 halamanChapter 4Yididiya TilahunBelum ada peringkat

- Timing Diagram PDFDokumen8 halamanTiming Diagram PDFSneha SinghBelum ada peringkat

- Example of AdcDokumen2 halamanExample of AdcRohan VaidyaBelum ada peringkat

- Unit VI-8051Dokumen61 halamanUnit VI-8051Afshan KaleemBelum ada peringkat

- Introduction To Protected ModeDokumen1 halamanIntroduction To Protected ModeRohan VaidyaBelum ada peringkat

- 8085 Instruction Addressing Modes ImppDokumen87 halaman8085 Instruction Addressing Modes ImppRohan VaidyaBelum ada peringkat

- Microprocessor and MicrocontrollerDokumen11 halamanMicroprocessor and MicrocontrollerRohan VaidyaBelum ada peringkat

- Introduction To Protected ModeDokumen1 halamanIntroduction To Protected ModeRohan VaidyaBelum ada peringkat

- InterruptsDokumen2 halamanInterruptsRohan VaidyaBelum ada peringkat

- 8085 BasicDokumen3 halaman8085 BasicRohan VaidyaBelum ada peringkat

- Syllabus 8051Dokumen1 halamanSyllabus 8051Rohan VaidyaBelum ada peringkat

- Gray To Binary ConversionDokumen2 halamanGray To Binary ConversionRohan VaidyaBelum ada peringkat

- At 89 C 52Dokumen24 halamanAt 89 C 52Rohit MehtaBelum ada peringkat

- SpinDokumen26 halamanSpinRohan VaidyaBelum ada peringkat

- Boolean InstructionsDokumen2 halamanBoolean InstructionsRohan VaidyaBelum ada peringkat