Ls6410 s3c6410 Arm11 Core Board

Diunggah oleh

TRIGUN-XDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Ls6410 s3c6410 Arm11 Core Board

Diunggah oleh

TRIGUN-XHak Cipta:

Format Tersedia

www.linksprite.

com

LS6410 S3C6410 ARM11 Core Board

1 / 20

www.linksprite.com

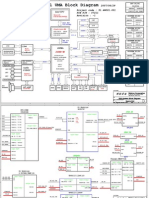

LS6410CORE integrates S3C6410, two 16 bit 128MB mobile DDR, 1GB MLC NAND Flash K9G8G08, power management circuit, Ethernet chip DM9000AEP, audio IC WM9713 of dual input channels/dual output channels, iNand Flash, etc.

2 / 20

www.linksprite.com

1. Pin Definition

Pin 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 Name KP_COL3 KP_COL4 KP_COL5 KP_COL6 KP_COL7 EINT20 EINT21 PWR_ON_OFF GND CLK_32K SD0_CD SD0_D0 SD0_D1 SD0_D2 SD0_D3 SD0_CLK SD0_CMD XVD0 XVD1 XVD2 XVD3 XVD4 XVD5 XVD6 XVD7 XVD8 XVD9 XVD10 XVD11 XVD12 XVD13 XVD14 XVD15 XVD16 Description Note Additional Function IO IO IO IO IO IO IO

Keypad matrix column scan 3 Keypad Matrix column scan 4 Keypad matrix column scan 5 Keypad matrix column scan 6 Keypad matrix column scan 7 External interrupt 20 External interrupt 21 Power enable, active high Power ground 32.768KHz waveform output SDIO channel 0 enable, active 10K resister pull low up Data line 0 of SDIO channel 0 10K resister pull up Data line 1 of SDIO channel 0 10K resister pull up Data line 2 of SDIO channel 0 10K resister pull up Data line 3 of SDIO channel 0 10K resister pull up Clock of SDIO channel 0 10K resister pull up Command signal of SDIO 10K resister pull channel 0 up Data 0 of LCD signal B0 Data 1 of LCD signal B1 Data 2 of LCD signal B2 Data 3 of LCD signal B3 Data 4 of LCD signal B4 Data 5 of LCD signal B5 Data 6 of LCD signal B6 Data 7 of LCD signal B7 Data 8 of LCD signal G0 Data 9 of LCD signal G1 Data 10 of LCD signal G2 Data 11 of LCD signal G3 Data 12 of LCD signal G4 Data 13 of LCD signal G5 Data 14 of LCD signal R6 Data 15 of LCD signal R7 Data 16 of LCD signal R0 3 / 20

IO or EINT12 IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO

www.linksprite.com

35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55

XVD17 XVD18 XVD19 XVD20 XVD21 XVD22 XVD23 XHSYNC XVSYNC XVDEN XVCLK CTS1 RXD1 RTS1 TXD1 GND EINT0 EINT1 EINT2 EINT5 EINT6

Data 17 of LCD signal Data 18 of LCD signal Data 19 of LCD signal Data 20 of LCD signal Data 21 of LCD signal Data 22 of LCD signal Data 23 of LCD signal Raw Scan Signal of LCD Column Scan Signal of LCD DE signal of LCD Clock signal of LCD Serial port 1 TTL CTS Serial Port 1 TTL RXD Serial Port 1 TTL RTS Serial Port 1 TTL TXD Power Gound External Interrupt 0 External Interrupt 1 External Interrupt 2 External Interrupt 5 External Interrupt 6

R1 R2 R3 R4 R5 R6 R7

Can only triggered by high level

IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO

56 57 58 59

EINT9 EINT10 EINT11 EINT13

External Interrupt 9 External Interrupt 10 External Interrupt 11 External Interrupt 13

60

EINT14

External Interrupt 14

61

EINT15

External Interrupt 15

Used to select NAND during booting Used to select NAND during booting Used to select NAND during booting

IO IO IO IO

IO

IO

62 63 64 65 66 67 68 69 70 71 72

EINT16 EINT17 EINT18 MIC1 HOST_DHOST_D+ PWM1 PWM0 BBP BBN SPKL

External Interrupt 16 External Interrupt 17 External Interrupt 18 Single channel MIC input USB HOST D- pin USD HOST D+ pin PWM output 1 PWM output 0 MIC differential input + MIC differential input Audio output Left channel 4 / 20

IO IO IO

IO IO Connect to GSM audio output Connect to GSM audio output

www.linksprite.com

73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112

SPKR MIC_MTN MIC_MTP MICP MICN HP_DET LOUT ROUT AC97_W AC97_YAC97_Y+ AC97_XAC97_X+ OM1 OM2 OM3 OM4 XciYDATA0 XciYDATA1 XciYDATA2 XciYDATA3 XciYDATA4 XciYDATA5 XciYDATA6 XciYDATA7 XciCLK XciHREF XciPCLK XciRSTN XciVSYNC RXD0 TXD0 CTS0 RTS0 RXD2 TXD2 RXD3 TXD3 XirSDBW GND

Audio output Right channel Audio output Audio output+

Connect to GSM audio input Connect to GSM audio input

MIC input + MIC input Headphone plug in detection Headphone plug (active low) in detection Headphone Left channel Headphone Right channel Audio IC touch function 5 line touch common pin Audio IC touch YAudio IC touch Y+ Audio IC touch XAudio IC touch X+ Boot configuration pin Refer to boot configuration Boot Configuration pin Refer to boot configuration Boot Configuration pin Refer to boot configuration Boot Configuration pin Refer to boot configuration Camera interface data line 0 Camera interface data line 1 Camera interface data line 2 Camera Interface data line 3 Camera Interface data line 4 Camera Interface data line 5 Camera Interface data line 6 Camera Interface data line 7 Camera Interface Clock Horizontal Sync Clock Pixel Clock Signal Camera module Reset signal Frame Sync Clock Signal Serial port 0 TTL RXD Serial port 0 TTL TXD Serial port 0 TTL CTS Serial port 0 TTL RTS Serial port 2 TTL RXD Serial port 2 TTL TXD Serial port 3 TTL RXD Serial port 3 TTL TXD Infra-red control signal Power Ground 5 / 20

IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO

www.linksprite.com

113 114 115

NET_SPEED NET_LINK AVDD25

116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147

NET_TXNET_TX+ NET_RXNET_RX+ SPI0_MISO SPI0_CLK SPI0_MOSI SPI0_CS SPI1_MISO SPI1_CLK SPI1_MOSI SPI1_CS SD1_CD SD1_CLK SD1_CMD SD1_D0 SD1_D1 SD1_D2 SD1_D3 SD1_D4 SD1_D5 DS1_D6 SD1_D7 AIN0 AIN1 AIN2 AIN3 TS_YM TS_YP TS_XM TS_XP IIC0_SCL

Network speed indicator Active Low output Network Link indicator output Active Low 2.5V output To supply the Ethernet transformer Ethernet Differential TXEthernet Differential TX+ Ethernet Differential RXEthernet Differential RX+ SPI channel 0 MISO SPI channel 0 CLK SPI channel 0 MOSI SPI channel 0 CS SPI channel 1 MISO Dual Function: SD2_CMD SPI channel 1 CLK Dual Function: SD2_CLK SPI channel 1 MOSI SPI channel 1 CS SD channel 1 channel selection (active low) SD channel 1 CLK SD channel 1 Command signal SD channel 1 data 0 SD channel 1 data 1 SD channel 1 data 2 SD channel 1 data 3 SD channel 1 data 4 Dual function: SD2_D0 SD channel 1 data 5 Dual function: SD2_D1 SD channel 1 data 6 Dual function: SD2_D2 SD channel 1 data 7 Dual function: SD2_D3 ADC channel 0 ADC precision: 10 bit ADC channel 1 ADC channel 2 ADC channel 3 Touch YTouch Y+ Touch XTouch X+ IIC bus clock Need external 10K pull up 6 / 20

IO or EINT IO or EINT IO or EINT IO or EINT IO or EINT IO or EINT IO or EINT IO or EINT IO IO IO IO IO IO IO IO IO IO IO

www.linksprite.com

148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170

IIC0_SDA DAC0 DAC1 GND OTG_DOTG_D+ OTG_ID OTGDRV_VBUS DVBUS nRESET VDD_RTC VDD_MAX KP_ROW0 KP_ROW1 KP_ROW2 KP_ROW3 KP_ROW4 KP_ROW5 KP_ROW6 KP_ROW7 KP_COL0 KP_COL1 KP_COL2

IIC bus data TV analog output signal 0 TV analog output signal 1

Need external 10K pull up Connect to TV output Connect to TV output

Power Ground OTG Data OTG Data+ OTG ID signal OTG power output enable signal OTG power input detection signal Reset signal (active low) RTC backup battery input 1.8-3.0V Signal main power input 2.7-6.5V Keypad matrix row scan 0 Keypad matrix row scan 1 Keypad matrix row scan 2 Keypad matrix row scan 3 Keypad matrix row scan 4 Keypad matrix row scan 5 Keypad matrix row scan 6 Keypad matrix row scan 7 Keypad matrix column scan 0 Keypad matrix column scan 1 Keypad matrix column scan 2

IO IO IO IO IO IO IO IO IO IO IO

7 / 20

www.linksprite.com

2. Core Board Package

Thickness: 2.85mm Length: 60mm Width: 60mm Pin pitch: 1.27mm

Recommended footprint as follows: 1. Add a layer of silkscreen to prevent the core board shots with via on the motherboard.

8 / 20

www.linksprite.com

2. Add a rectangle opening on the motherboard as shown in the following figure.

9 / 20

www.linksprite.com

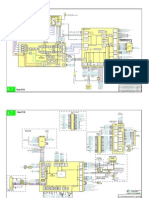

3. PCB Layout

3.1 Core Board PCB normal line width and line interval

1. Normal signal line interval 4 mil. 2. TOP layer: the first line outside BGA has a line interval of 5 mil.

3. Lines under BGA has an interval of 4 mil.

10 / 20

www.linksprite.com

4. The minimal line width of power and GND is 10 mil, and maxium 20 mil.

3.2 Size of via and distribution of blind and buried via This core board uses blind and buried via. There are no empty via.

11 / 20

www.linksprite.com

3.3 Core Board Stackup

12 / 20

www.linksprite.com

3.4 Core Board Impedance Control

3.5 Core board layout

13 / 20

www.linksprite.com

14 / 20

www.linksprite.com

15 / 20

www.linksprite.com

16 / 20

www.linksprite.com

17 / 20

www.linksprite.com

Power plane separation:

18 / 20

www.linksprite.com

19 / 20

www.linksprite.com

Components placement:

20 / 20

Anda mungkin juga menyukai

- Z TurnboardDokumen9 halamanZ Turnboardjobey erfeeBelum ada peringkat

- ICM7211Dokumen13 halamanICM7211Volkan YılmazBelum ada peringkat

- ElektronikaDokumen24 halamanElektronikaGunawan NababanBelum ada peringkat

- Casio Ctk500Dokumen21 halamanCasio Ctk500Joel Moreno100% (1)

- Dell Inspiron 1545 Wistron Roberts Discrete Rev - 1 SCHDokumen60 halamanDell Inspiron 1545 Wistron Roberts Discrete Rev - 1 SCHWilgen GarciaBelum ada peringkat

- Casio CTK500 Service ManualDokumen21 halamanCasio CTK500 Service ManualFelix Fernando SantamariaBelum ada peringkat

- JUMPtec Intelligent LVDS InterfaceDokumen11 halamanJUMPtec Intelligent LVDS InterfaceDalek SkaroBelum ada peringkat

- BB Top Level Vilbet 03-Jan-07 Tkoivusa 18-Aug-03 Dd-Mmm-Yy IljarvinDokumen32 halamanBB Top Level Vilbet 03-Jan-07 Tkoivusa 18-Aug-03 Dd-Mmm-Yy IljarvinJuan Daniel Angeles AnguloBelum ada peringkat

- ID-LA-IsO Series Low Cost RFID Reader Module Used Animal Tagging LF ISO11785Dokumen10 halamanID-LA-IsO Series Low Cost RFID Reader Module Used Animal Tagging LF ISO11785AbleIDLtdBelum ada peringkat

- Dell Xps m1530 Intel Discrete - Wistron HawkeDokumen57 halamanDell Xps m1530 Intel Discrete - Wistron Hawkemaoh80Belum ada peringkat

- IC CXD3068Q DatasheetDokumen134 halamanIC CXD3068Q Datasheetnaupas007Belum ada peringkat

- Service Manual: CDX-L480XDokumen20 halamanService Manual: CDX-L480Xkeremelekika7Belum ada peringkat

- Fujitsu Siemens Esprimo V6535 PDFDokumen47 halamanFujitsu Siemens Esprimo V6535 PDFPC MediaPointBelum ada peringkat

- TP6813 Data Sheet v1.0Dokumen10 halamanTP6813 Data Sheet v1.0Ljupco BozinovskiBelum ada peringkat

- Chassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioDokumen16 halamanChassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioRobert Vicuña100% (1)

- Main PCB: Neptune LtsDokumen3 halamanMain PCB: Neptune LtsArdianta YoppiBelum ada peringkat

- 8050QRDokumen121 halaman8050QRcjarekBelum ada peringkat

- MBI5025Dokumen13 halamanMBI5025Claudio Miguel Trindade VazBelum ada peringkat

- USB Controller For Low Cost VoIP SolutionsDokumen38 halamanUSB Controller For Low Cost VoIP SolutionsDoug SiskBelum ada peringkat

- IN44780U Dot Matrix Liquid Crystal Display Controller & DriverDokumen10 halamanIN44780U Dot Matrix Liquid Crystal Display Controller & DriverSilviu AdgjBelum ada peringkat

- Acer Aspire 5930GDokumen50 halamanAcer Aspire 5930Gperaja12Belum ada peringkat

- 8-Bit Microcontroller With 1K Bytes In-System Programmable Flash Attiny13 PreliminaryDokumen18 halaman8-Bit Microcontroller With 1K Bytes In-System Programmable Flash Attiny13 Preliminarymike_helplineBelum ada peringkat

- Vestel DVD 5500Dokumen14 halamanVestel DVD 5500tlw72Belum ada peringkat

- DELL Inspiron N4020Dokumen88 halamanDELL Inspiron N4020Deddy SuyantoBelum ada peringkat

- Casio CTK541 Service ManualDokumen25 halamanCasio CTK541 Service ManualAlex Hernández50% (2)

- STA013Dokumen38 halamanSTA013rohan09Belum ada peringkat

- STA013 STA013B STA013T: Mpeg 2.5 Layer Iii Audio DecoderDokumen38 halamanSTA013 STA013B STA013T: Mpeg 2.5 Layer Iii Audio DecoderSandesh PatiBelum ada peringkat

- Ps Primer Arm7 Um v1Dokumen50 halamanPs Primer Arm7 Um v1Anantha RajaBelum ada peringkat

- BL 0306Dokumen2 halamanBL 0306Ngoc Nguyen VanBelum ada peringkat

- ST7066UDokumen42 halamanST7066UConIntBelum ada peringkat

- DLA001Dokumen36 halamanDLA001Rogerio GuimarãesBelum ada peringkat

- Som Panasonic CQ-EH5461TU / 39100-S5A-910-M1 - CivicDokumen41 halamanSom Panasonic CQ-EH5461TU / 39100-S5A-910-M1 - CivicdanielgabiniBelum ada peringkat

- Dell Inspiron 1525 Schematic DiagramDokumen47 halamanDell Inspiron 1525 Schematic Diagramogon601100% (2)

- AC6901A DatasheetDokumen13 halamanAC6901A DatasheetIgor LevochkinBelum ada peringkat

- ¡ Semiconductor: General DescriptionDokumen17 halaman¡ Semiconductor: General DescriptionNguyễn Thành LinhBelum ada peringkat

- SL 223m Daewoo LCD TVDokumen74 halamanSL 223m Daewoo LCD TVJesus Garcia HernandezBelum ada peringkat

- Technical Manual - Manual Técnico Panasonic Honda Fit Jazz 0502cqjh4480kDokumen30 halamanTechnical Manual - Manual Técnico Panasonic Honda Fit Jazz 0502cqjh4480kEric Lúcio Silva RodriguesBelum ada peringkat

- ARM7Dokumen76 halamanARM7Bajrang sisodiyaBelum ada peringkat

- Daewoo DPC-7200PDDokumen42 halamanDaewoo DPC-7200PDЕвгений СафоновBelum ada peringkat

- Winstar Display DatasheetDokumen20 halamanWinstar Display DatasheetAlejandroBelum ada peringkat

- Exploring Arduino: Tools and Techniques for Engineering WizardryDari EverandExploring Arduino: Tools and Techniques for Engineering WizardryPenilaian: 4.5 dari 5 bintang4.5/5 (5)

- Beginning STM32: Developing with FreeRTOS, libopencm3 and GCCDari EverandBeginning STM32: Developing with FreeRTOS, libopencm3 and GCCBelum ada peringkat

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkDari EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkBelum ada peringkat

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxDari EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxPenilaian: 4 dari 5 bintang4/5 (2)

- PIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsDari EverandPIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsPenilaian: 5 dari 5 bintang5/5 (1)

- Beginning Arduino Nano 33 IoT: Step-By-Step Internet of Things ProjectsDari EverandBeginning Arduino Nano 33 IoT: Step-By-Step Internet of Things ProjectsBelum ada peringkat

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3Dari EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3Belum ada peringkat

- Microprocessor Architectures and Systems: RISC, CISC and DSPDari EverandMicroprocessor Architectures and Systems: RISC, CISC and DSPPenilaian: 4 dari 5 bintang4/5 (1)

- Microcontroller Projects in C for the 8051Dari EverandMicrocontroller Projects in C for the 8051Penilaian: 5 dari 5 bintang5/5 (1)

- Dutch Oven CookingDokumen74 halamanDutch Oven Cookingcaj411Belum ada peringkat

- Wave City CenterDokumen11 halamanWave City CenterRishabh SansanwalBelum ada peringkat

- The WedgeDokumen7 halamanThe Wedgebanditgsk0% (1)

- Common Sense Media 2021Dokumen64 halamanCommon Sense Media 2021Alcione Ferreira SáBelum ada peringkat

- Humber College Cover Letter Resuma Thank You Leter DraftDokumen4 halamanHumber College Cover Letter Resuma Thank You Leter Draftapi-401811891Belum ada peringkat

- Google Chrome OsDokumen2 halamanGoogle Chrome Osniravkapadia100Belum ada peringkat

- LeisureDokumen4 halamanLeisurePorshothman ElenggovenBelum ada peringkat

- 8987492Dokumen713 halaman8987492Alex Eduardo ParraBelum ada peringkat

- Some of The Very Best Poems of ORHAN VELİ - A Turkish Poet Fine DaysDokumen5 halamanSome of The Very Best Poems of ORHAN VELİ - A Turkish Poet Fine DaysmeleknazBelum ada peringkat

- Service Manual: STR-DE497P/K4800P/K5800PDokumen52 halamanService Manual: STR-DE497P/K4800P/K5800PLonCin123Belum ada peringkat

- Jazz Blues - Solo Technique - Chord Voicing - Jens LarsenDokumen35 halamanJazz Blues - Solo Technique - Chord Voicing - Jens Larsenrla9762380% (5)

- NEA-Live and NEA-DVR - Deep DiveDokumen59 halamanNEA-Live and NEA-DVR - Deep DiveRobertBelum ada peringkat

- ENG362 DramaDokumen201 halamanENG362 Dramaツ ツBelum ada peringkat

- Proshea Apparel CatalogDokumen18 halamanProshea Apparel CatalogJaharudin JuhanBelum ada peringkat

- Cisco Mobility Express: Step 1. Set UpDokumen6 halamanCisco Mobility Express: Step 1. Set Upjarko tarrilloBelum ada peringkat

- Watertown Tree Lighting and Christmas Parade 2017Dokumen2 halamanWatertown Tree Lighting and Christmas Parade 2017NewzjunkyBelum ada peringkat

- Halbert Expedition Sales LetterDokumen6 halamanHalbert Expedition Sales LetterObiBelum ada peringkat

- Lifestyle & Weight ManagementDokumen18 halamanLifestyle & Weight ManagementKathrina LingadBelum ada peringkat

- Who Wants To Be A Millionaire - Template by SlideLizardDokumen51 halamanWho Wants To Be A Millionaire - Template by SlideLizardThu Hà TrầnBelum ada peringkat

- Eastview Bowl - The Gallery Grill and Tap Bar MenuDokumen8 halamanEastview Bowl - The Gallery Grill and Tap Bar MenuBryn BeckerBelum ada peringkat

- 1 2 A. Introduction 2 B. Reasons For Choosing Bukit Tangkiling 5 6 A. Types of Tourism 6 B. A3 10 15 A. Problems 15 16 A. Solutions 16 Bibliography 17 Attachment 18Dokumen21 halaman1 2 A. Introduction 2 B. Reasons For Choosing Bukit Tangkiling 5 6 A. Types of Tourism 6 B. A3 10 15 A. Problems 15 16 A. Solutions 16 Bibliography 17 Attachment 18Monica HapsariBelum ada peringkat

- TLE9 COOKERY Q3 M2 Different-Sandwich-Ingredients FVDokumen7 halamanTLE9 COOKERY Q3 M2 Different-Sandwich-Ingredients FVLauro Jr. AtienzaBelum ada peringkat

- Presentation Michael Jackson InglesDokumen2 halamanPresentation Michael Jackson InglesClara Luz Cantillo EscorciaBelum ada peringkat

- Camp QuestsDokumen19 halamanCamp QuestsTracyBelum ada peringkat

- Simplex FrameDokumen38 halamanSimplex Framedrskathirrvelu0% (1)

- Gym Candy by Steven DorringtonDokumen4 halamanGym Candy by Steven DorringtonJean chaBelum ada peringkat

- 2023 Bermuda National Athletics Association Cross Country October 21st ResultsDokumen3 halaman2023 Bermuda National Athletics Association Cross Country October 21st ResultsBernewsAdminBelum ada peringkat

- Heidelberg Prinect Signa Station 45 Cracktorrent13 PDFDokumen4 halamanHeidelberg Prinect Signa Station 45 Cracktorrent13 PDFBradyBelum ada peringkat

- Agnetha FältskogDokumen8 halamanAgnetha Fältskog-'maяiannis aaQ'zBelum ada peringkat

- Stepper Motor C CodeDokumen4 halamanStepper Motor C CodeJoël Mwabi100% (1)