Reg - No Reg - No: B.E./B.Tech. Degree Examination, May/June 2012 Sixth Semester

Diunggah oleh

Bala KumarDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Reg - No Reg - No: B.E./B.Tech. Degree Examination, May/June 2012 Sixth Semester

Diunggah oleh

Bala KumarHak Cipta:

Format Tersedia

[VIDYARTHIPLUS.

COM] February 16, 2013

REG.NO

REG.NO ANNA UNIVERSITY CHENNAI 60 0025

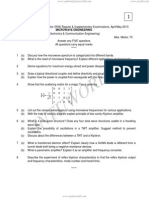

B.E./B.Tech. DEGREE EXAMINATION, MAY/JUNE 2012 Sixth Semester Electronics and Communication Engineering EC 2354/EC 64 VLSI DESIGN

(common to PTEC 2354 VLSI DESIGN for B.E. (part time) fifth semester electronics and communication engineering regulation 2009 ) (regulation 2008) TIME : THREE HOURS ANSWER ALL QUESTIONS PART-A (10 X 2 = 20)

1. DRAW THE IV CHARACTERISTICS OF MOS TRANSISTOR. 2. BREIF THE DIFFERENT OPERATING REGIONS OF MOS SYSTEM. 3. DRAW THE EQUIVALENT CIRCUIT STRUCTURE OF LEVEL 1 MOSFET MODEL IN SPICE. 4. BRIEF ABOUT THE VARIATION OF FRINGING FIELD FACTOR WITH THE INTERCONNECT GEOMETRY. 5. COMPARE CMOS COMBINATIONAL LOGIC GATES WITH REFERENCE TO THE EQUIVALENT N-MOS DEPLETION LOAD LOGIC WITH REFERENCE TO THE AREA REQUIREMENT. 6. WHAT ARE THE ADVANTAGE OF USING A PSEUDO N-MOS GATE INSTEAD OF A FULL CMOS GATE 7. WHAT ARE THE FACTORS THAT CAUSE TIMING FAILURES? 8. WHAT ARE THE ADVANTAGE OF A SINGLE STUCK AT FAULT? 9. WITH COMPONENT INSTANTITATION, WRITE A VHDL PROGRAM FOR A BUFFER.

MAX:100 MARKS

[VIDYARTHIPLUS.COM] February 16, 2013

10. WRITE A NOTE ON TRANSPORT DELAY

PART-B (10 X 2 = 20)

11. (a) DISCUSS IN DETAIL ABOUT: (1) FULL-CUSTOM MASK LAYOUT DESIGN (8) (2) CMOS INVERTER LAYOUT DESIGN (8) [OR] (b) (I) WITH A NEAT DIAGRAM DISCUSS IN DETAIL ABOUT DC TRANSFER CHARACTERISTICS OF CMOS. (8) (II) WRITE A SHORT NOTES ON THE FOLLOWING ALONG WITH THE MASK VIEW (i) OXIDE RELATED CAPACITANCE (4) (ii) JUNCTION CAPACITANCE (4) 12. (a) (i) OBTAIN AN EXPRESSION FOR LEVEL 2 MODEL EQUATION OF MOSFET IN SPICE. (8) (ii) DISCUSS IN DETAIL ABOUT: (1) VARIATION OF MOBILITY WITH ELECTRIC FIELD. (2) VARIATION OF CHANNEL LENGTH IN SATURATION MODES. (3) SATURATION OF CARRIER VELOCITY. (8) [OR] (b)(i) HOW DO THE SPICE MOSFET MODEL ACCOUNT FOR THE PARASITIC DEVICE CAPACITANCES?(8) (ii) EXPLAIN THE CHARECTERIZATION OF CIRCUITS.(8) 13. (a) (i)FOR A TWO INPUT NAND GATE DERIVE AN EXPRESSION FOR THE DRAIN CURRENT. (8) (ii) DRAW A CMOS NOR2 GATE AND ITS COMPLEMENTARY OPERATION WITH NECESSARY EQUATIONS. (4) (iii) OBTAIN A CMOS LOGIC DESIGN REALIZING THE BOOLEAN FUNCTION Z=A(D+E)+BC (8) [OR] (b) (i) DRAW A CIRCUIT DIAGRAM OF THE CMOS SR LATCH AND EXPL AIN IN DETAIL. (8) (ii) ALONG WITH THE NECESSARY INPUT AND OUTPUT WAVEFORMS OF THE CMOS DFF NEGATIVE EDGE TRIGGERED MASTER SLAVE D FLIP FLOP. (8)

[VIDYARTHIPLUS.COM] February 16, 2013

14. (a) (i) EXPLAIN INDETAIL ABOUT PARTITION AND MUX TESTING WITH NECESSARY EXAMPLE AND DIAGRAM. (8) (ii) EXPLAIN THE PRINCIPLE OF SILICON DEBUG. (8) [OR] (b) (i) ELABORATE THE SCAN BASED TECHNIQUES. (8) (ii) DISCUSS IN DETAIL ABOUT: (I) PSEUDO RANDOM PATTERN GENERATOR. (4) (II) OUTPUT RESPONSE ANALYSER. (4)

15. (a) USING MIXED LEVEL MODE WRITE A VHDL PROGRAM FOR A (i) COMPARATOR. (8) (ii) D FLIP FLOP. [OR] (b) WITH ALL THE THREE TYPES OF MODELING WRITE A VHDL PROGRAM FOR A (i) DECODER (8) (ii) FULL ADDER. (8) (8)

Anda mungkin juga menyukai

- MJ12 PDFDokumen6 halamanMJ12 PDFSarika VadivelanBelum ada peringkat

- EC2354 - VLSI DesignDokumen2 halamanEC2354 - VLSI DesignSriramBelum ada peringkat

- Digital Electronics Exam 2012Dokumen7 halamanDigital Electronics Exam 2012Meluami J. ParoriBelum ada peringkat

- 2008 Anna UniversityDokumen1 halaman2008 Anna UniversitysasitsnBelum ada peringkat

- Ec 1354 Vlsi DesignDokumen5 halamanEc 1354 Vlsi Designdhasarathan_rajaBelum ada peringkat

- VLSI Design - CMOS Inverter Scaling, PTL & SOI FabricationDokumen1 halamanVLSI Design - CMOS Inverter Scaling, PTL & SOI FabricationelakyaBelum ada peringkat

- Anna University VLSI Design Question PaperDokumen3 halamanAnna University VLSI Design Question PapersrgperumalBelum ada peringkat

- r05410207 Vlsi DesignDokumen7 halamanr05410207 Vlsi Design9010469071Belum ada peringkat

- Ec 1354Dokumen5 halamanEc 1354kvnelavarasiBelum ada peringkat

- University Question Papers - VLSIDokumen26 halamanUniversity Question Papers - VLSIVijayBelum ada peringkat

- B.E./B.Tech. DEGREE EXAMINATION, APRIL/MAY 2008. Seventh Semester Electronics and Communication Engineering EC1403-MICROWAVE ENGINEERINGDokumen2 halamanB.E./B.Tech. DEGREE EXAMINATION, APRIL/MAY 2008. Seventh Semester Electronics and Communication Engineering EC1403-MICROWAVE ENGINEERINGjubairBelum ada peringkat

- VLSI Design ECE A InternalexamDokumen2 halamanVLSI Design ECE A InternalexamJeslin AntonioBelum ada peringkat

- EC 1312 - Digital Logic Circuits Question BankDokumen5 halamanEC 1312 - Digital Logic Circuits Question BankDeepak RavichandranBelum ada peringkat

- Previous PapersDokumen12 halamanPrevious PapersKaran SanaBelum ada peringkat

- PH 136 - Semiconductor Physics and Opto ElectronicsDokumen3 halamanPH 136 - Semiconductor Physics and Opto ElectronicssubhazBelum ada peringkat

- Microwave EngineeringDokumen4 halamanMicrowave EngineeringAbhishekBarmaBelum ada peringkat

- Ec 1401 Vlsi DesignDokumen2 halamanEc 1401 Vlsi DesignsubhazBelum ada peringkat

- Question Bank: Department of Electrical and Electronics Engineering Subject Code & NameDokumen0 halamanQuestion Bank: Department of Electrical and Electronics Engineering Subject Code & NameThasleema BanuBelum ada peringkat

- VLSI DesignDokumen5 halamanVLSI DesignqwertyuiopBelum ada peringkat

- Code No: R05320402Dokumen4 halamanCode No: R05320402chvsrsettiBelum ada peringkat

- FPGA Based System DesignDokumen2 halamanFPGA Based System Designammayi9845_930467904Belum ada peringkat

- M.Tech I Semester Supplementary Examinations February/March 2018Dokumen1 halamanM.Tech I Semester Supplementary Examinations February/March 2018baburao_kodavatiBelum ada peringkat

- Roll No.: B. TechDokumen3 halamanRoll No.: B. TechShivani VarshneyBelum ada peringkat

- Vlsi Design - Department of Electronics and CommunicationDokumen6 halamanVlsi Design - Department of Electronics and CommunicationAnirnya SamantaBelum ada peringkat

- Network Analysis and Synthesis: Code: EC3T4Dokumen4 halamanNetwork Analysis and Synthesis: Code: EC3T4Alumni GECBelum ada peringkat

- VLSIDesignDokumen5 halamanVLSIDesignVenkatesh KolatiBelum ada peringkat

- Ec1311 Com EngDokumen4 halamanEc1311 Com EngRameez FaroukBelum ada peringkat

- Paper 1Dokumen2 halamanPaper 1P KishoreBelum ada peringkat

- Vlsi QP 21,22Dokumen11 halamanVlsi QP 21,22Arunitha ArulnathanBelum ada peringkat

- SE) V (-2017 (02) - II: Candidate Should Write His/her Roll No. HereDokumen7 halamanSE) V (-2017 (02) - II: Candidate Should Write His/her Roll No. HereTechnical boxBelum ada peringkat

- A.R. Engineering College, Villupuram Ece Department: Ec2203/Digital ElectronicsDokumen8 halamanA.R. Engineering College, Villupuram Ece Department: Ec2203/Digital ElectronicsNitu VlsiBelum ada peringkat

- EC1201 Electronic Devices and Circuits NotesDokumen6 halamanEC1201 Electronic Devices and Circuits NotesRameez FaroukBelum ada peringkat

- B.E. / B.Tech. Degree Examination, November/ December 2007Dokumen2 halamanB.E. / B.Tech. Degree Examination, November/ December 2007tamilmaranBelum ada peringkat

- See Cmos Vlsi Jan 2020Dokumen3 halamanSee Cmos Vlsi Jan 20201ms21ec132Belum ada peringkat

- r20 I Year I Sem Supplementary, October 2022Dokumen14 halamanr20 I Year I Sem Supplementary, October 2022Tulja ThakurBelum ada peringkat

- RF AND MICROWAVE ENGINEERING - Nov/Dec 2011 Anna University Previous Year Model Question PaperDokumen3 halamanRF AND MICROWAVE ENGINEERING - Nov/Dec 2011 Anna University Previous Year Model Question PapereldhosejmBelum ada peringkat

- Vlsi Design April 2019Dokumen4 halamanVlsi Design April 2019RakeshBelum ada peringkat

- Question Bank For DLCDokumen8 halamanQuestion Bank For DLCAvina AshBelum ada peringkat

- Question Paper Code: X10348: Reg. NoDokumen2 halamanQuestion Paper Code: X10348: Reg. NoJaikumar RajendranBelum ada peringkat

- Gujarat Technological University: InstructionsDokumen2 halamanGujarat Technological University: InstructionsArchana TrivediBelum ada peringkat

- A1429 VlsiDokumen8 halamanA1429 VlsiratnamsBelum ada peringkat

- Previous Question PapersDokumen4 halamanPrevious Question Papersshaker423Belum ada peringkat

- Chapter - ICDokumen9 halamanChapter - ICbelyalamgirBelum ada peringkat

- 2 Ec2354 - Vlsi DesignDokumen2 halaman2 Ec2354 - Vlsi Designkrishna_ScrbidBelum ada peringkat

- VLSI Question PaperDokumen3 halamanVLSI Question Paper209X1A04D2 SHAIK ASMABelum ada peringkat

- WWW - Manaresults.Co - In: Set No. 1Dokumen1 halamanWWW - Manaresults.Co - In: Set No. 1Rajesh PylaBelum ada peringkat

- Vlsi QBDokumen5 halamanVlsi QBManaswiBelum ada peringkat

- Vlsi Model 4-QPDokumen2 halamanVlsi Model 4-QPsanthoshBelum ada peringkat

- EC8095-VLSI Design - QP - by WWW - LearnEngineering.inDokumen11 halamanEC8095-VLSI Design - QP - by WWW - LearnEngineering.inKiran KumarBelum ada peringkat

- (Answer Any Four Questions) (Each Carries 5 Marks) (Answer Any Four Questions) (Each Carries 5 Marks)Dokumen1 halaman(Answer Any Four Questions) (Each Carries 5 Marks) (Answer Any Four Questions) (Each Carries 5 Marks)arun@1984Belum ada peringkat

- Question BanksDokumen74 halamanQuestion BanksVidhya GanesanBelum ada peringkat

- S5 S6 Electrical & Electronics EngineeringDokumen209 halamanS5 S6 Electrical & Electronics EngineeringThomas NigilBelum ada peringkat

- Question BankDokumen9 halamanQuestion BankNiyas AhamedBelum ada peringkat

- Tagore Engineering College Dept of Electronics and Communication Ec2304 Microprocessors and Microcontrollers Unit Test-IiiDokumen1 halamanTagore Engineering College Dept of Electronics and Communication Ec2304 Microprocessors and Microcontrollers Unit Test-IiipremaprabuBelum ada peringkat

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyDari EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyBelum ada peringkat

- Nanotechnology Commercialization: Manufacturing Processes and ProductsDari EverandNanotechnology Commercialization: Manufacturing Processes and ProductsBelum ada peringkat

- Characteristic Modes: Theory and Applications in Antenna EngineeringDari EverandCharacteristic Modes: Theory and Applications in Antenna EngineeringBelum ada peringkat

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionDari EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionBelum ada peringkat

- Hybrid Nanomaterials: Advances in Energy, Environment, and Polymer NanocompositesDari EverandHybrid Nanomaterials: Advances in Energy, Environment, and Polymer NanocompositesSuneel Kumar SrivastavaBelum ada peringkat

- Computational Liquid Crystal Photonics: Fundamentals, Modelling and ApplicationsDari EverandComputational Liquid Crystal Photonics: Fundamentals, Modelling and ApplicationsBelum ada peringkat

- Tirunelveli Tamil1Dokumen2 halamanTirunelveli Tamil1Bala KumarBelum ada peringkat

- Glory of Murugan - The Tamil God of War and WisdomDokumen64 halamanGlory of Murugan - The Tamil God of War and WisdomBala KumarBelum ada peringkat

- Glory of Murugan - The Tamil God of War and WisdomDokumen64 halamanGlory of Murugan - The Tamil God of War and WisdomBala KumarBelum ada peringkat

- ESDokumen1 halamanESBala KumarBelum ada peringkat

- Energy Efficient Information Fusion in Wireless Sensor NetworksDokumen5 halamanEnergy Efficient Information Fusion in Wireless Sensor NetworksBala KumarBelum ada peringkat

- Mariamman Thalattu.8.27.14 PDFDokumen89 halamanMariamman Thalattu.8.27.14 PDFAlaguchitraBelum ada peringkat

- MARRIAGEDokumen1 halamanMARRIAGEBala KumarBelum ada peringkat

- ESDokumen1 halamanESBala KumarBelum ada peringkat

- EE 2014 SolvedDokumen32 halamanEE 2014 SolvedJammalaVenkataramanaBelum ada peringkat

- Rejinpaul Important QuestionsDokumen2 halamanRejinpaul Important QuestionsBala KumarBelum ada peringkat

- Answer Key IAE-1Dokumen2 halamanAnswer Key IAE-1Bala KumarBelum ada peringkat

- Ce6461 Set2 PDFDokumen2 halamanCe6461 Set2 PDFAnonymous yiBHUtqCdBelum ada peringkat

- Embedded Systecse & It QBDokumen7 halamanEmbedded Systecse & It QBBala KumarBelum ada peringkat

- EEE SylbDokumen108 halamanEEE SylbBala KumarBelum ada peringkat

- UG Practical ScheduleDokumen1 halamanUG Practical ScheduleBala KumarBelum ada peringkat

- Energy Efficient Information Fusion in Wireless Sensor NetworksDokumen5 halamanEnergy Efficient Information Fusion in Wireless Sensor NetworksBala KumarBelum ada peringkat

- 9th English Lesson2 PDFDokumen7 halaman9th English Lesson2 PDFBala KumarBelum ada peringkat

- Zonal - Practical: User Manual For Principal LoginDokumen16 halamanZonal - Practical: User Manual For Principal LoginBala KumarBelum ada peringkat

- Computers HardwareDokumen2 halamanComputers HardwareBala KumarBelum ada peringkat

- Registration Form PDFDokumen1 halamanRegistration Form PDFBala KumarBelum ada peringkat

- VLSI Design Nov 2011Dokumen3 halamanVLSI Design Nov 2011Suseel Jai KrishnanBelum ada peringkat

- Registration Form PDFDokumen1 halamanRegistration Form PDFBala KumarBelum ada peringkat

- Energy-And Cost-Efficient Mobile Communication Using Multi-Cell MIMO and RelayingDokumen11 halamanEnergy-And Cost-Efficient Mobile Communication Using Multi-Cell MIMO and RelayingBala KumarBelum ada peringkat

- HiDokumen8 halamanHiBala KumarBelum ada peringkat

- Novel Feedback Bit Allocation Methods For Multi-Cell Joint Processing SystemsDokumen7 halamanNovel Feedback Bit Allocation Methods For Multi-Cell Joint Processing SystemsBala KumarBelum ada peringkat

- EE2251 EM1 2marksDokumen19 halamanEE2251 EM1 2marksBala KumarBelum ada peringkat

- Con CurrencyDokumen43 halamanCon CurrencymailmecarthicBelum ada peringkat

- EM VidyarthiplusDokumen24 halamanEM VidyarthiplusBala KumarBelum ada peringkat

- IceDokumen31 halamanIceBala KumarBelum ada peringkat

- SP 5500 V5.1 1.0Dokumen17 halamanSP 5500 V5.1 1.0Rama Tenis CopecBelum ada peringkat

- Application Research of MRAC in Fault-Tolerant Flight ControllerDokumen1 halamanApplication Research of MRAC in Fault-Tolerant Flight ControlleradcadBelum ada peringkat

- Power System Stability-Chapter 3Dokumen84 halamanPower System Stability-Chapter 3Du TrầnBelum ada peringkat

- Library System Case StudyDokumen55 halamanLibrary System Case StudyUmakanth Nune50% (6)

- The Structure of MatterDokumen3 halamanThe Structure of MatterFull StudyBelum ada peringkat

- The Role of Pets in PreadolescentDokumen17 halamanThe Role of Pets in PreadolescentshimmyBelum ada peringkat

- SD Revenue Account Determination SetupDokumen10 halamanSD Revenue Account Determination SetupkarthikbjBelum ada peringkat

- Steel Design 6 April 2023 PDFDokumen2 halamanSteel Design 6 April 2023 PDFTristan CatapangBelum ada peringkat

- Vitamins With Minerals Oral PowderDokumen8 halamanVitamins With Minerals Oral PowderWH PANDWBelum ada peringkat

- Chemistry Investigatory File Handmade NewDokumen17 halamanChemistry Investigatory File Handmade NewMadhusudan PeriwalBelum ada peringkat

- 4-1 E Handbook 2013-14Dokumen53 halaman4-1 E Handbook 2013-14Siva Reddy KunduruBelum ada peringkat

- Experiment 1 - Friction Losses in PipesDokumen34 halamanExperiment 1 - Friction Losses in PipesKhairil Ikram33% (3)

- CBCS StatisticsDokumen79 halamanCBCS StatisticsXING XINGBelum ada peringkat

- Quasi VarianceDokumen2 halamanQuasi Varianceharrison9Belum ada peringkat

- Continuous DeploymentDokumen2 halamanContinuous DeploymentVenkat Reddy0% (1)

- Ace Signal and System PDFDokumen144 halamanAce Signal and System PDFYash Rai100% (1)

- Triad Over Root Chords Companion PDF 2.1Dokumen18 halamanTriad Over Root Chords Companion PDF 2.1Vlado PetkovskiBelum ada peringkat

- MSC Syllabus PDFDokumen34 halamanMSC Syllabus PDFMayadarBelum ada peringkat

- Use Jinja2 To Create TemplatesDokumen44 halamanUse Jinja2 To Create TemplatesmBelum ada peringkat

- Digital Techniques/Electronic Instrument SystemsDokumen29 halamanDigital Techniques/Electronic Instrument SystemsE DBelum ada peringkat

- Laing Electric Heater-CirculatorDokumen20 halamanLaing Electric Heater-Circulatorkamilawehbe100% (1)

- Manual 2012-08 EDokumen59 halamanManual 2012-08 EfiorelaBelum ada peringkat

- Automate Distribution of Quantity in MIGODokumen8 halamanAutomate Distribution of Quantity in MIGOyougesh100% (2)

- Propeller Model Tests GuideDokumen12 halamanPropeller Model Tests GuideOdpewğw RlelelwBelum ada peringkat

- General Types of Intermolecular Forces 11-LDokumen33 halamanGeneral Types of Intermolecular Forces 11-LClarenz N. Turan100% (1)

- Non-Performing Assets: A Comparative Study Ofsbi&Icici Bank From 2014-2017Dokumen8 halamanNon-Performing Assets: A Comparative Study Ofsbi&Icici Bank From 2014-2017Shubham RautBelum ada peringkat

- ROBERT_BECKER.BOM Wrapped Ref Des (Current Date, Sort by Item SeqDokumen5 halamanROBERT_BECKER.BOM Wrapped Ref Des (Current Date, Sort by Item SeqNAUBERTO F. DOS SANTOSBelum ada peringkat

- Design of Low Head Weirs for Great Ruaha RiverDokumen2 halamanDesign of Low Head Weirs for Great Ruaha RiverJames LaurentBelum ada peringkat

- Fire Strength Performance ofDokumen3 halamanFire Strength Performance ofMarimuthu KannimuthuBelum ada peringkat