BoostPFC Rivero

Diunggah oleh

JavierHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

BoostPFC Rivero

Diunggah oleh

JavierHak Cipta:

Format Tersedia

1

Control de Convertidores Boost con PFC Mod. y Control de Conv. Electr onicos de Potencia - Proyecto Docente: Dr. Gabriel Eirea

Ing. Nicol as F. Rivero Rodr guez, IIE - FI - UDELAR Email: nicolas@ng.edu.uy

Resumen En este trabajo se presenta una primer aproximaci on al estudio de las diferentes estrategias de control para un convertidor Boost DC-DC con correcci on de factor de potencia. La alimentaci on se realiza desde una red de alterna a trav es de un recticador de puente completo. Un dise no u nico del tren de potencia es empleado en todos los casos a n de facilitar la comparaci on. Se presentan c alculos y ejemplos ilustrativos para cada estrategia de control, as como tambi en los resultados de simulaciones utilizando modelos conmutados. Palabras Clave Convertidor, boost, correcci on de Factor de Potencia, PFC.

I. I-A. Motivaci on

n Introduccio

Radicionalmente, los recticadores se compon an de un puente de diodos seguido de una capacitor en la etapa de entrada, como se indica en la gura 1.

REGULADOR DE SALIDA

La topolog a Boost (ver g. 3) se ajusta muy bien a este objetivo, pues presenta el inductor a la entrada, lo cual facilita el control de la corriente de entrada (ver [3]), que es una variable continua. El dise no t pico consiste en un convertidor Boost precedido de un puente recticador de onda completa (ver g. 4). De hecho es la topolog a mas utilizada en la etapa de entrada prerreguladora de recticadores de alta eciencia y baja distorsi on arm onica. Con ella se logran adem as: 1. la aceptaci on de un amplio rango de tensiones de entrada; 2. simplicidad en el dise no del driver de la llave, pues esta queda conectada a la tensi on de referencia. Las principales desventajas son: 1. la tensi on de salida debe ser mayor que la tensi on de pico m axima de la red de alimentaci on1 ; 2. imposibilidad de limitar la corriente de entrada (debe agregarse circuiter a auxiliar para ello, tanto en funcionamiento como en el arranque). Continuamente se est an proponiendo topolog as derivadas del Boost b asico para la implementaci on de prerreguladores. Por ejemplo: 1. inductor en la l nea antes del puente recticador y dos diodos del puente cambiados por llaves controladas para reducir las p erdidas, o derivados de esta estrategia (ver [4]); 2. dos inductores a la entrada trabajando con un desfasaje de 180o (Interleaved PFC Boost Pre-regulator, ver [5], [6]) y variantes (ver [7]); 3. Boost seguidor, en el cual la tensi on de salida sigue la variaci on de la tensi on de entrada (ver [8], [9]); etc.

Fig. 1. Recticador tradicional.

La eciencia, as como la calidad de energ a son factores cada vez mas importantes en el dise no de convertidores de energ a. El esquema tradicional genera formas de onda con mucha distorsi on en la corriente de entrada (ver g. 2). Disponer de convertidores que tengan baja distorsi on arm onica y buen factor de potencia se ha convertido en algo est andar en la actualidad (ver [1], [2]), por lo cual estas soluciones ya no son aceptables.

Fig. 3. Convertidor Boost b asico.

Por estas razones, es de inter es estudiar las distintas estrategias de control para este tipo de convertidor, a n de identicar las fortalezas y debilidades de cada una de ellas.

VC ii

Fig. 2. Recticador tradicional. Formas de Onda.

Para lograr una buena performance se vuelve fundamental poder controlar la corriente consumida por el equipo, para hacer que su forma de onda se asemeje a la de tensi on de alimentaci on y que la red la vea lo mas parecido posible a una carga resistiva.

Fig. 4. Convertidor Boost con alimentaci on AC.

1 Esto no es un inconveniente signicativo ya que la etapa de salida del recticador se encarga de bajar la tensi on, adem as de lograr una regulaci on na en torno al valor deseado.

I-B.

Hip otesis de trabajo

entonces IL = 0.25 2 y como

Virms L IL = D / fS

En la gura 3 se muestra el circuito correspondiente al convertidor DC-DC tipo boost. La llave S1 es controlada, mientras que la llave S2 se implementa con un diodo. Para el caso de estudio Vi ser a una sinusoide pasada por un puente recticador de onda completa. En la gura 4 se muestra el convertidor boost en esta situaci on, precedido por un puente de diodos, alimentado desde una red de corriente alterna. Todos los diodos se consideran ideales, as como tambi en la llave S1. La red de alterna se considera de potencia innita. La carga se modela mediante una resistencia de valor adecuado. I-C. Estrategias de control

V02 RVirms

D= L se puede calcular L=

V0 Virms V0

(V0 Virms )RVi2 rms

0.25

3 2fS V0

L = 102.6H Se toma L = 100 H. Para este valor se tiene que IL = 4.95 A, siendo ILpico = 19.3 A. I-D.2. Capacitor de salida: Para el dimensionado del capacitor de salida, se busca un ripple pico a pico m aximo de 10 % en la tensi on de salida (20V ). Como la tensi on de salida del convertidor es pr acticamente constante, la corriente de salida presenta una forma de onda similar a la potencia de entrada. Si el factor de potencia se acerca a la unidad, la potencia de entrada es un sen2 o lo que es lo mismo 1 cos(2 (2fred )t). Por lo tanto, la amplitud de la componente AC de la corriente de salida antes del capacitor es igual a su componente DC. Asumiendo que no hay p erdidas (alta eciencia), la potencia de entrada es igual a la de salida. ICpico = v0 = ICpico Pi P0 = V0 V0

Las estrategias de control analizadas son las que se indican a continuaci on. 1. Control por corriente de pico. 2. Control por corriente de pico con rampa de compensaci on. 3. Control por corriente promedio. 4. Control utilizando bloque PWM generalizado. 5. Control por hist eresis de corriente. 6. Control de corriente al l mite entre DCM2 y CCM3 . El an alisis se centrar a en la performance en cuanto a factor de potencia y distorsi on arm onica a la entrada del convertidor. Tambi en se estudiar an los efectos de una baja en la tensi on de la red de alimentaci on y la respuesta din amica del lazo de control de tensi on de salida. I-D. Dise no de componentes de potencia

De acuerdo con la hip otesis indicadas, una vez denidos los requerimientos del convertidor, resta dimensionar la inductancia de entrada (L en la g. 4) y el capacitor de salida (C en la g. 4). Ver [10]. En la tabla I se incluyen los datos de la red de alterna de alimentaci on del convertidor, potencia y tensi on de salida deseadas, as como ripple m aximo en la corriente de entrada y en la tensi on de salida.

Entrada Virms = 220 V fred = 50 Hz iL = 25 % iLpico Salida V0 = 400 V P0 = 3 kW V0 = 10 % V0

ICpico 1 C= = 597F 2 2fred C 4fred v0

Se elige C = 700 F, por lo que el ripple de la tensi on de salida es 17V . Por u ltimo se agregan resistencias par asitas a la inductancia y al capacitor. Los valores utilizados se resumen en la tabla II.

L = 100 H RL = 0.15 C = 700 F RC = 0.05 TABLA II Valores de los componentes del circuito.

TABLA I o. Requerimientos de disen

Se utiliza una frecuencia de conmutaci on fS = 200 kHz. Para lograr la potencia de salida, la carga se modela como R = 53.3 . I-D.1. Inductor de entrada: Se elige un valor m aximo de ripple de corriente por el inductor de 25 % del valor de pico. El c alculo de L, asumiendo conducci on continua se presenta a continuaci on. Se tiene que ILpico = 2Iirms Iirms =

V0 Virms

I-E.

Lazos de control

I0 =

2 V0 RVirms

2 Modo de conducci on discontinua (Discontinuous Conduction Mode, seg un sigla en ingl es). 3 Modo de conducci on continua (Continuous Conduction Mode).

Para el funcionamiento del prerregulador con correcci on de factor de potencia, se requieren dos lazos de control. Uno se encarga de regular la corriente de entrada iL , y el otro la tensi on de salida V0 . I-E.1. Lazo de control de corriente: El lazo de control de corriente se encarga de mantener la corriente de entrada en el valor deseado. Es un lazo r apido, siendo la frecuencia de conmutaci on fS la que lo limita (la frecuencia de corte t picamente puede estar entre fS /10 y fS /5. La variaci on de tensi on de entrada, se nal con un per odo de 1/(2fred ) es siempre mucho mas lenta, por lo cual en general no hay dicultad para seguir la se nal de programaci on de corriente. La implementaci on del lazo de control de corriente es la que caracteriza al esquema de control utilizado.

I-E.2. Feed-forward de la tensi on de entrada: La se nal de programaci on de corriente se obtiene multiplicando el error en la tensi on de salida por una se nal proporcional a la tensi on de entrada Vi . Esto hace que un cambio en el valor RMS de la tensi on de entrada se propague con el cuadrado de dicho valor RMS en la potencia de salida. Para eliminar este efecto, se divide por < Vi >2 , obteniendo una se nal de programaci on de corriente independiente de este problema. Todos los esquemas de control analizados utilizan feedforward de la tensi on de entrada, excepto el control utilizando bloque PWM generalizado (ver V). I-E.3. Lazo de control de tensi on: El lazo de control de la tensi on de salida es el que genera la amplitud de la se nal de programaci on de corriente. Dicho lazo va a tender a que la potencia de entrada sea constante, lo que llevar a a una muy mala forma de onda de corriente a la entrada. Es por esto que la frecuencia de corte de la transferencia a lazo abierto debe ser mucho menor que la frecuencia de Vi (o sea 2fred ) para conseguir un comportamiento de tipo resistivo. El resultado de esto es que la regulaci on de tensi on de salida es muy lenta (las transiciones pueden tomar varios ciclos de red), y en la pr actica se deben tomar precauciones adicionales para evitar sobrecorrientes (ver [3]). La transferencia a lazo abierto se puede aproximar por 1+ A

s z

Q S R CLK >0

+-

<Vi>2 x KVo

+-

Vo

ref

Fig. 5. Esquema de control por corriente de pico.

distorsi on de la se nal de programaci on de corriente. La se nal de referencia de corriente generada se compara con la corriente iL . Cuando iL supera el umbral se apaga la llave. Un reloj vuelve a cerrar la llave luego de transcurrido el intervalo de muestreo. Se trata de un esquema de control simple. Es de frecuencia de conmutaci on constante y no necesita amplicador de error de corriente. El amplicador de error KV0 se implementa con un integrador (ver I-E.3). II-A. Factor de potencia y distorsi on arm onica

1 1+

s p

s zRHP

1 donde z = RC es el cero introducido por el capacitor C 2 de salida con su resistencia par asita, p = RC es el polo R(1D 2 ) dominante, y zRHP = es el cero en el semiplano L derecho del conversor Boost. La utilizaci on de control en modo corriente no elimina el problema del cero en el semiplano derecho, sin embargo la ausencia del polo doble presente en el control en modo voltaje simplica el dise no del controlador (ver [11]). En todos los casos el controlador de tensi on utilizado es de tipo I (integrador):

Este esquema de control presenta la desventaja de presencia de oscilaciones subarm onicas para ciclos de trabajo mayores a 1/2 (ver [11]). Si bien esto puede evitarse en el dise no, se hace dif cil si se desea aceptar un rango amplio de tensiones de entrada. Al disminuir Vi y el ciclo de trabajo superar el mencionado umbral se presenta este fen omeno (ver g. 7, Zoom1). El an alisis espectral de iL (ver g. 7) se puede ver, por ej., un componente subarm onico fuerte en fS /2. El factor de potencia en este caso es de 0.99200, siendo el componente de desfasaje 0.99995 y kd = 0.99205. Esto se corresponde con una distorsi on arm onica de 12.68 %4 . II-B. Situaci on de tensi on de entrada reducida

KV0 (s) = I-F. Simulaciones

1330 s

Para cada una de las estrategias de control analizadas, se presentan los resultados de simulaciones del modelo conmutado del circuito correspondiente. Dichos modelos se construyeron de acuerdo a las aproximaciones indicadas en I-B y I-D. En todos los casos se utiliz o Simulink r 5.0, parte de Matlab r 6.5 release 13, The MathWorks Inc. Una buena referencia de Simulink r es [12]. Para el modelado de problemas con discontinuidades, como es este caso, y en caso de utilizar un m etodo de resoluci on de paso variable, es conveniente denir siempre un intervalo m aximo entre los puntos de c alculo para asegurar resultados correctos. Este intervalo deber a siempre ser mucho mas peque no que el per odo de conmutaci on (1/fS ). II. Control por corriente de pico

Fig. 6. Control c. pico. Comparaci on entre Vi normal y reducido.

En la gura 5 se presenta el esquema de control por corriente de pico. La multiplicaci on por la tensi on de entrada Vi , asegura un seguimiento de dicha tensi on por parte de iL para lograr un buen factor de potencia. A su vez la divisi on por < Vi >2 permite asumir variaciones en la tensi on de entrada sin generar

4 k y la distorsi on arm onica se calcularon con los primeros 50 d arm onicos de la frecuencia de red en todos los casos.

Fig. 7. Control por corriente de pico. Forma de onda de iL (derecha). Espectro de iL (izquierda).

Fig. 8. Control por corriente de pico, Vi reducida. Forma de onda y espectro de iL .

Para mantener la potencia de salida al reducirse la tensi on de entrada, la corriente de entrada debe aumentar. En la gura 8 se muestra el efecto de reducir la tensi on de entrada a 120 Vrms . Esto genera adem as otras consecuencias no deseadas. En este caso aumenta el problema de presencia de frecuencias subarm onicas, pues al bajar Vi , los ciclos de trabajo aumentan y esto hace que en mas ocasiones superen 1/2. En la gura 8 se puede ver este efecto. El factor de potencia en este caso es de 0.99667, siendo el componente de desfasaje 0.99997 y kd = 0.99670. Esto se corresponde con una distorsi on arm onica de 8.14 %. II-C. Respuesta din amica

el rango de ciclos de trabajo dentro de los cuales el sistema es estable, simplemente asign andole una pendiente adecuada a la rampa. La ganancia del comparador con rampa de compensaci on es 1 TS md + mr donde md es la pendiente de iL durante el ciclo de trabajo, mr es la pendiente de la rampa de compensaci on y TS es el per odo de conmutaci on (1/fS ). Como md = Vi /L y se agrega el t ermino mr , cuando Vi se acerca a cero la ganancia del comparador con rampa no crece indenidamente, manteni endose mucho mas constante durante todo el semiper odo. Este efecto enlentece la respuesta en las zonas en que Vi se acerca a cero, respecto al caso sin rampa, generando una deformaci on en la corriente de entrada. El problema de la variaci on de las pendientes de las rampas de corriente con Vi hace que resulte muy dif cil la utilizaci on de rampa de compensaci on, seg un se menciona en [3] y [13]. Un estudio mas profundo sobre la elecci on correcta de la pendiente de la rampa se puede ver en [11]. El valor de la rampa de compensaci on para las simulaciones se j o en 2 V /s. Esto no est a basado en ning un criterio que permita establecer una comparaci on cuantitativa con el caso sin rampa respecto a los valores calculados5 . Lo que se busca es establecer una comparaci on cualitativa. III-A. Factor de potencia y distorsi on arm onica

Se aplica un escal on en la carga, pasando de 2 kW a 3 kW. El resultado se muestra en la gura 9.

Fig. 9. Control c. pico. Respuesta a escal on de 2 kW a 3 kW.

La recuperaci on de V0 toma aproximadamente 5 ciclos de red (100 ms). El valor promedio de V0 presenta un m nimo aproximado de 360 V (90 % del valor de dise no para la tensi on de salida). III. Control por corriente de pico con rampa de n compensacio

En la gura 11 se muestra la forma de onda de corriente obtenida luego de utilizar rampa de compensaci on. Una rampa adecuada logra eliminar la presencia de oscilaciones subarm onicas (ver espectro en g. 11). El factor de potencia en este caso es de 0.98809, siendo el componente de desfasaje 0.99984 y kd = 0.98825. Esto se corresponde con una distorsi on arm onica de 15.47 %. La atenuaci on introducida por la rampa en el lazo de corriente provoca deformaciones en la forma de onda de corriente que afectan el espectro en frecuencias bajas, que son las que pesan al calcular la distorsi on arm onica. Por esta raz on la distorsi on arm onica calculada es algo mayor al caso de control por corriente de pico sin rampa. III-B. Situaci on de tensi on de entrada reducida

Q S R CLK >0

+-

<Vi>2 x KVo

+-

Voref

En la gura 13 se muestra la comparaci on entre tensi on de alimentaci on normal y tensi on de alimentaci on reducida. El factor de potencia en este caso es de 0.99670, siendo el componente de desfasaje 0.99999 y kd = 0.99670. Esto se corresponde con una distorsi on arm onica de 7.80 %. La reducci on de tensi on de entrada no genera efectos no deseados en este caso (ver g. 12). La disminuci on de la distorsi on arm onica se corresponde con haber aumentado el valor ecaz de la corriente sin cambiar signicativamente su ripple. En el caso sin rampa de compensaci on la inestabilidad del lazo de corriente empeora al reducir la tensi on de alimentaci on (ver g. 6); si bien el efecto explicado en III-A sigue presente, dicha inestabilidad hace que la distorsi on arm onica sea peor en aquel caso.

Fig. 10. Esq. de c. corriente pico con rampa de compensaci on.

Este esquema de control se basa en el control por corriente de pico, agregando una rampa de compensaci on a la se nal de programaci on de corriente (ver g. 10). Esto permite aumentar

5 Estudiar la posibilidad de establecer este tipo de criterios est a fuera del alcance de este trabajo.

Fig. 11. Control por corriente de pico con rampa de compensaci on. Forma de onda de iL (derecha). Espectro de iL (izquierda).

Fig. 12. Control por corriente de pico con rampa de compensaci on, Vi reducida. Forma de onda y espectro de iL .

PWM KiL

-+

<Vi>2 x KVo

+-

Voref

Fig. 15. Esq. de control de corriente promedio.

Fig. 13. Control c. pico c/r. Comp. entre Vi normal y reducido.

promedio la siga. Esto es especialmente importante cuando Vi est a cerca de cero y el convertidor pasa a modo de conducci on discontinua. Ver [13]. El controlador de corriente utilizado en este caso es: KiL (s) = 87892 (s + 69580) s (s + 1208 103 )

III-C.

Respuesta din amica

La gura 14 muestra el resultado de aplicar el escal on de carga. La performance es similar al caso sin rampa de compensaci on.

Como en el resto de los casos, la selecci on de este controlador no responde a ning un criterio que permita justicar una comparaci on cuantitativa de los resultados obtenidos. IV-A. Factor de potencia y distorsi on arm onica

En la gura 17 se muestra la forma de onda de corriente obtenida. Con este m etodo de control se pueden lograr niveles muy bajos de distorsi on. El factor de potencia en este caso es de 0.99987, siendo el componente de desfasaje 0.99996 y kd = 0.99991. Esto se corresponde con una distorsi on arm onica de 1.31 %. IV-B. Situaci on de tensi on de entrada reducida

Fig. 14. Control c. pico c/r. Resp. a escal on de 2 kW a 3 kW.

La recuperaci on de V0 toma aproximadamente 5 ciclos de red (100 ms). El valor promedio de V0 presenta un m nimo aproximado de 368 V (92 % del valor de dise no para la tensi on de salida). IV. Control por corriente promedio

Fig. 16. Control c. prom. Comp. entre Vi normal y reducido.

El control de corriente promedio se implementa colocando un amplicador de error de corriente en el lazo interno, KiL , seg un se muestra en la gura 15. El generador de PWM es alimentado con la se nal de error de corriente ltrada, por lo que en este caso no es necesario usar rampa de compensaci on. Este ltrado hace, adem as, que este modo sea mas inmune al ruido de conmutaci on de las llaves. Se elimina tambi en el error inherente a los m etodos de control anteriores, en los cuales el pico de corriente sigue la se nal programada cuando en realidad lo que interesa es que el

El factor de potencia en este caso es de 0.99989, siendo el componente de desfasaje 0.99997 y kd = 0.99992. Esto se corresponde con una distorsi on arm onica de 1.27 %. La reducci on de la tensi on de entrada no afecta la performance del controlador (ver g. 16 y g. 18).

Fig. 17. Control por corriente promedio. Forma de onda de iL (derecha). Espectro de iL (izquierda).

Fig. 18. Control por corriente promedio, Vi reducida. Forma de onda y espectro de iL .

IV-C.

Respuesta din amica V1 = Vprog RS iL por lo cual6 Vprog RS iL = Vprog d Vprog (1 d) = RS iL Vi Vprog = RS iL VC siendo iL proporcional a Vi , logrando el objetivo buscado en un PFC. Vprog se debe multiplicar por 1/TS antes de entrar al bloque PWM generalizado, para que quede escalada correctamente. En las simulaciones se utiliza un valor de RS = 1 . Como en el resto de los casos, no se puede justicar una comparaci on cuantitativa de los resultados obtenidos. V-A. Factor de potencia y distorsi on arm onica V2 = Vprog

Fig. 19. Control c. prom. Resp. a escal on de 2 kW a 3 kW.

La gura 19 muestra el resultado de aplicar el escal on de carga. La performance es similar a los modos de control por corriente de pico. La recuperaci on de V0 toma aproximadamente 5 ciclos de red (100 ms). El valor promedio de V0 presenta un m nimo aproximado de 372 V (93 % del valor de dise no para la tensi on de salida). V. Control utilizando bloque PWM generalizado.

En la gura 22 se muestra la forma de onda de corriente obtenida. La presencia de oscilaciones subarm onicas es signicativa. Sin embargo se logra un resultado bastante aceptable en lo que tiene que ver con la distorsi on arm onica. El factor de potencia en este caso es de 0.99696, siendo el componente de desfasaje 0.99904 y kd = 0.99792. Esto se corresponde con una distorsi on arm onica de 6.46 %. V-B. Situaci on de tensi on de entrada reducida

El esquema de control propuesto en [14] consiste en la utilizaci on de un bloque modulador PWM generalizado. Este presenta la ventaja de no requerir sensar la tensi on de entrada ni bloque multiplicador.

Q Q S R CLK

CMP + -

1/s

1/s

2 1

KVo

MODULADOR PWM GENERALIZADO

Voref

Fig. 21. Control b. PWM. Comp. entre Vi normal y reducido.

Fig. 20. Esq. de control con bloque PWM generalizado.

En la entrada del bloque PWM correspondiente al primer integrador se coloca la programaci on de corriente, esto genera en la entrada positiva del comparador un diente de sierra de amplitud proporcional a la programaci on de corriente. A su vez, en la entrada negativa del comparador se coloca el error de corriente. La entrada integradora doble del bloque PWM no se utiliza. La ecuaci on del modulador es V1 = V2 d + V3 d2 y seg un lo indicado se cumple que

El factor de potencia en este caso es de 0.97452, siendo el componente de desfasaje 0.99906 y kd = 0.97543. Esto se corresponde con una distorsi on arm onica de 22.59 %. A partir de cierto nivel de corriente iL , aparecen subarm onicos de muy baja frecuencia que afectan signicativamente la performance (ver g. 21 y g. 23).

6 R se incluye a efecto de que la unidades queden consistentes. Se S puede asumir por ej. que su valor es 1 .

10

Fig. 22. Control utilizando bloque PWM generalizado. Forma de onda de iL (derecha). Espectro de iL (izquierda).

Fig. 23. Control utilizando bloque PWM generalizado, Vi reducida. Forma de onda y espectro de iL .

11

Fig. 24. Control por hist eresis de corriente. Forma de onda de iL (derecha). Espectro de iL (izquierda).

Fig. 25. Control por hist eresis de corriente, Vi reducida. Forma de onda y espectro de iL .

12

V-C.

Respuesta din amica

El control por hist eresis de corriente, as como el control por corriente de pico, es sensible al ruido de conmutaci on. Los valores de la banda de hist eresis se obtienen multiplicando la se nal de programaci on de corriente por 1.4 y 0.6 (pico y valle respectivamente). Como en el resto de los casos, no se puede justicar una comparaci on cuantitativa de los resultados obtenidos. VI-A. Factor de potencia y distorsi on arm onica

El efecto de la frecuencia variable se puede observar en el espectro (ver g. 24). La minima frecuencia se da cuando la tensi on de entrada es m axima; desde all hacia frecuencias mas altas se concentra la mayor parte del espectro. En la zona de inter es la distorsi on es muy baja. El factor de potencia en este caso es de 0.99999, siendo el componente de desfasaje 0.99997 y kd = 0.99999. Esto se corresponde con una distorsi on arm onica de 0.55 %. VI-B.

Fig. 26. Control b. PWM. Respuesta a escal on de 2 kW a 3 kW.

Situaci on de tensi on de entrada reducida

La gura 26 muestra el resultado de aplicar el escal on de carga. La respuesta en este caso es subamortiguada, presentando una oscilaci on en los valores promedio de per odo acorde a la frecuencia de corte del lazo de tensi on (9.4 Hz). Esto hace que la tensi on promedio de salida tenga un valor m aximo de aproximadamente 407 V (1.75 % por encima del valor de dise no). La recuperaci on de V0 toma aproximadamente 5 ciclos de red (100 ms). El valor promedio de V0 presenta un m nimo aproximado de 377 V (94.25 % del valor de dise no para la tensi on de salida). VI. resis de corriente. Control por histe

Fig. 28. Control hist. Comparaci on entre Vi normal y reducido.

Q S R >0 >0

-+ +kUP

<Vi>2 x KVo

+-

kLO

Voref

Fig. 27. Esq. de control por hist eresis de corriente.

El esquema de control por hist eresis de corriente consiste en denir una banda de funcionamiento. Cuando la corriente iL supera el m aximo se apaga la llave y cuando esta desciende por debajo del m nimo se enciende la llave (ver g. 27). Esto da como resultado un control de frecuencia variable, que en el caso de un convertidor PFC puede generar frecuencias de conmutaci on muy altas cerca de los cruces por cero de la tensi on de entrada. Para evitar este problema se puede apagar la llave en un entorno del cruce por cero, como se sugiere en [15]. En este caso se implementa esta soluci on, impidiendo que la frecuencia de conmutaci on supere los 200 kHz.

Fig. 29. Control hist. Respuesta a escal on de 2 kW a 3 kW.

13

Fig. 30. Control de corriente al l mite entre DCM y CCM. Forma de onda de iL (derecha). Espectro de iL (izquierda).

Fig. 31. Control de corriente al l mite entre DCM y CCM, Vi reducida. Forma de onda y espectro de iL .

14

El factor de potencia en este caso es de 0.99999, siendo el componente de desfasaje 0.99999 y kd = 0.99999. Esto se corresponde con una distorsi on arm onica de 0.30 %. Al aumentar la corriente, la m nima frecuencia de conmutaci on es mas baja, pero como sigue siendo mucho mayor que las frecuencias de los arm onicos de inter es, la distorsi on es a un algo menor (ver g. 28 y g. 25). VI-C. Respuesta din amica

La gura 29 muestra el resultado de aplicar el escal on de carga. La respuesta en este caso es levemente subamortiguada. Esto hace que la tensi on promedio de salida tenga un valor m aximo de aproximadamente 405 V (1.25 % por encima del valor de dise no). La recuperaci on de V0 toma mas de 7 ciclos de red (140 ms). El valor promedio de V0 presenta un m nimo aproximado de 355 V (88.75 % del valor de dise no para la tensi on de salida). VII. Control de corriente al l mite entre DCM y CCM.

Fig. 33. Control lim. DCM-CCM. C. entre Vi normal y reducido.

VII-C.

Respuesta din amica

Q S R >0 <0

+-

<Vi>2 x KVo

+-

Vo

ref

Fig. 32. Esq. de c. de corriente al l mite entre DCM y CCM.

El esquema de control de corriente al l mite entre conducci on discontinua y conducci on continua es similar al control por hist eresis de corriente. En este caso la llave se prende cuando la corriente llega a cero (ver g. 32), por lo que el diodo S2 se apaga con corriente cero. El ripple de corriente es superior al caso de control por hist eresis. Igual que el control por hist eresis, el control al l mite entre DCM y CCM es de frecuencia de conmutaci on variable y es sensible al ruido de conmutaci on. El valor m aximo de la corriente se ja en 1.4 veces la se nal de programaci on de corriente. Como en el resto de los casos, no se puede justicar una comparaci on cuantitativa de los resultados obtenidos. VII-A. Factor de potencia y distorsi on arm onica

Fig. 34. Control lim. DCM-CCM. Resp. escal on de 2 kW a 3 kW.

El comportamiento es similar al control por hist eresis (ver g. 30). El factor de potencia en este caso es de 0.99999, siendo el componente de desfasaje 0.99999 y kd = 0.99999. Esto se corresponde con una distorsi on arm onica de 0.23 %. VII-B. Situaci on de tensi on de entrada reducida

La gura 34 muestra el resultado de aplicar el escal on de carga. La respuesta en este caso es levemente subamortiguada. Esto hace que la tensi on promedio de salida tenga un valor m aximo de aproximadamente 403 V (0.75 % por encima del valor de dise no). La recuperaci on de V0 toma mas de 7 ciclos de red (140 ms). El valor promedio de V0 presenta un m nimo aproximado de 355 V (88.75 % del valor de dise no para la tensi on de salida). VIII. Resultados

El factor de potencia en este caso es de 0.99996, siendo el componente de desfasaje 0.99996 y kd = 0.99999. Esto se corresponde con una distorsi on arm onica de 0.27 %. Al aumentar la corriente, las frecuencias de conmutaci on bajan. Esto se debe tener en cuenta para no llegar a valores no deseados (ver g. 31).

En la tabla III se muestra una comparaci on de los resultados entre los distintos m etodos de control para el caso de alimentaci on a tensi on nominal. La tabla IV contiene esta misma informaci on para el caso de alimentaci on con tensi on reducida. En la tabla V se incluyen datos de la respuesta al escal on en la carga para cada caso. La gura 35 incluye las formas de onda de salida obtenidas al aplicar el escal on. Por u ltimo en la tabla VI se incluye la lista de m etodos de control ordenada de acuerdo a la performance en la respuesta al escal on aplicado.

15

Fig. 35. Respuestas al escal on de carga para cada esquema de control. FP 0.99200 0.98809 0.99987 0.99696 0.99999 0.99999 cos() 0.99995 0.99984 0.99996 0.99904 0.99997 0.99999 kd 0.99205 0.98825 0.99992 0.99792 0.99999 0.99999 THD 12.68 % 15.47 % 1.31 % 6.46 % 0.55 % 0.23 % M aximo ) ( %) 100.00 100.00 100.00 101.75 101.25 100.75 M nimo ( %) 90.00 92.00 93.00 94.25 88.75 88.75 Duraci on (ciclos) 5 5 5 5 mas de 7 mas de 7

Esquema de control Corriente de pico C. pico c/rampa comp. Corriente promedio Bloque PWM gralizado. Hist eresis de corriente L mite DCM-CCM

Esquema de control Corriente de pico C. pico c/rampa de comp. Corriente promedio Bloque PWM gralizado. Hist eresis de corriente L mite entre DCM y CCM

TABLA III n de resultados sobre la corriente de entrada. Comparacio

TABLA V n de resultados en la respuesta a un escalo n de Comparacio carga.

Esquema de control Corriente de pico C. pico c/rampa comp. Corriente promedio Bloque PWM gralizado. Hist eresis de corriente L mite DCM-CCM

FP 0.99667 0.99670 0.99989 0.97452 0.99999 0.99996

cos() 0.99997 0.99999 0.99997 0.99906 0.99997 0.99996

kd 0.99670 0.99670 0.99992 0.97543 0.99999 0.99999

THD 8.14 % 7.80 % 1.27 % 22.59 % 0.30 % 0.27 %

TABLA IV n de resultados sobre la corriente de entrada a Comparacio n de entrada reducida. tensio

Esquema de control Utilizando bloque PWM generalizado Por corriente promedio Por c. de pico con rampa de compensaci on Por corriente de pico Por hist eresis de corriente Al l mite entre DCM y CCM

Performance mejor 2da 3era 4ta 5ta peor

TABLA VI todos de control ordenados por performance en la Me n de carga. respuesta a un escalo

IX.

Conclusiones control es mejor. Sin embargo, se obtienen datos comparativos interesantes que ayudan a comprender el funcionamiento de cada estrategia de control. Un an alisis mas detallado de cada caso permitir a, por ejemplo, presentar datos cuantitativos sobre rangos de potencia adecuados a cada esquema de control, inmunidad al ruido en cada caso, conveniencia de uso de otras topolog as en la etapa

El presente trabajo estudia en forma comparativa varios m etodos de control para el Prerregulador Boost con Correcci on de Factor de Potencia. Constituye una primer aproximaci on al tema, habiendo simplicado el an alisis al trabajar sobre el mismo dise no de la etapa de potencia y utilizando un modelo simple de la misma. Los valores num ericos de los par ametros calculados no se pueden tomar como gu a cuantitativa de que esquema de

16

de potencia, etc. Tambi en se podr a tener una idea mas clara sobre cuales son las limitaciones pr acticas en el dise no de cada tipo de controlador. Lograr factores de potencia muy buenos parece relativamente simple. No resulta tan sencillo reducir la distorsi on arm onica. Referencias

[1] J. Noon y D. Dalal, Optimize PFC Preregulator Designs, Texas Instruments Inc., Manchester, N. H., 2002. [2] M. OLoughlin, Transition PFC increases eciency to meet 80+ requirements, Texas Instruments Incorporated. [3] L. Dixon, High Power Factor Preregulator for O-Line Power Supplies, Unitrode Corporation. [4] J.-G. Cho, J.-W. Baek, D.-W. Yoo, y H.-S. Lee, Reduced Conduction Loss Zero-Voltage-Transition Power Factor Correction Converter, IEEE, 1998. [5] M. OLoughlin, The Next Innovations in Interleaved PFC Control, Texas Instruments, USA, 2008. [6] , 350-W Two-Phase Interleaved PFC Pre-regulator Design Review, Texas Instruments Incorporated, 2007. [7] , Phase Management Raises Interleaved PFC Eciency, Texas Instruments, Dallas, 2007. [8] , UCC3819 250-W Power Factor Corrected (PFC) Boost Follower Preregulator Design, Texas Instruments Incorporated, 2002. [9] , Advantages Using A Boost-Follower In A Power Factor Corrected Pre-Regulator, Texas Instruments Incorporated. [10] L. Dixon, Optimizing the Design of a High Power Factor Switching Preregulator, Unitrode Corporation. [11] R. Ridley, Designer Series, Part V, Current-Mode Control Modeling, Ridley Engineering Inc., 2001. [12] S. T. Karris, Introduction to Simulink r with Engineering Applications, Orchard Publications, 2006. [13] L. Dixon, Average Current Mode Control of Switching Power Supplies, Unitrode Corporation. [14] R. L. Palomo, J. A. M. Salda na, y E. E. Carbajal, Modeling and Control of a PFC Regulator with Redundant Power Processing, Area Mec anica y El ectrica, Facultad de Ingenier a, Universidad Aut onoma de San Luis Potos , M exico., 2008. [15] L. Rossetto, G. Spiazzi, y P. Tenti, Control Techniques for Power Factor Correction Converters, University of Padova.

Nicol as F. Rivero Rodr guez Ingeniero Electricista egresado de la Facultad de Ingenier a de la Universidad de la Rep ublica Oriental del Uruguay en 2004.

Anda mungkin juga menyukai

- ClavelinaDokumen6 halamanClavelinaJavierBelum ada peringkat

- Guia Tecnica Sondeos Geotermicos SuperficialesDokumen0 halamanGuia Tecnica Sondeos Geotermicos SuperficialesJavierBelum ada peringkat

- Sistemas de RectificaciónDokumen26 halamanSistemas de RectificaciónJavierBelum ada peringkat

- Técnicas de Modulación en Convertidores PDFDokumen224 halamanTécnicas de Modulación en Convertidores PDFMonickaferBelum ada peringkat

- Cuestionario Calderas 1Dokumen4 halamanCuestionario Calderas 1Jhon RodriguezBelum ada peringkat

- Manual Del Usuario Modulo 13 Rev 10 Oct 2019Dokumen168 halamanManual Del Usuario Modulo 13 Rev 10 Oct 2019Salvador De La Ree100% (1)

- 3 Actuadores EuplaDokumen41 halaman3 Actuadores EuplaJaime UrdialesBelum ada peringkat

- Ejercicios Semana 05Dokumen4 halamanEjercicios Semana 05osores123garciaBelum ada peringkat

- Instalaciones Eléctricas en Edificios (Infografía)Dokumen3 halamanInstalaciones Eléctricas en Edificios (Infografía)Hector TiendaBelum ada peringkat

- Ciip12 1247 1259.3798Dokumen13 halamanCiip12 1247 1259.3798giusti_xpBelum ada peringkat

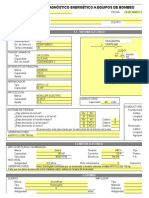

- Evaluación para Sistemas de Bombeo de Agua - Hoja de CalculoDokumen12 halamanEvaluación para Sistemas de Bombeo de Agua - Hoja de CalculodhannielllBelum ada peringkat

- Caso EnunciadoDokumen5 halamanCaso EnunciadoISEINDUSTRIALINTERNATIONAL SERIVCES S.A.S.Belum ada peringkat

- Central Hidroeléctrica RalcoDokumen6 halamanCentral Hidroeléctrica RalcoFernando TovarBelum ada peringkat

- Protocolo Bomba Diesel - 1Dokumen1 halamanProtocolo Bomba Diesel - 1David SALGUERO OLVEABelum ada peringkat

- Informe 3 Lab de PotenciaDokumen16 halamanInforme 3 Lab de PotenciaJosseph Michaell Irigoin CorraBelum ada peringkat

- Parcial 2 - Primera Ley - TermodinámicaDokumen1 halamanParcial 2 - Primera Ley - TermodinámicaDavid Espitia DiazBelum ada peringkat

- Copia de Fis Cuestionario 2aSRDokumen8 halamanCopia de Fis Cuestionario 2aSRmairymtellezBelum ada peringkat

- Partes de Un Transformador de PotenciaDokumen4 halamanPartes de Un Transformador de PotenciaDenisse RangelBelum ada peringkat

- Cantidad de MovimientoDokumen32 halamanCantidad de Movimientojuan fariasBelum ada peringkat

- Anexo Transversal ADokumen47 halamanAnexo Transversal ALizet Mayli Mejia PenadilloBelum ada peringkat

- Guia para Examen de Admision A TecNM ITQ 2023Dokumen90 halamanGuia para Examen de Admision A TecNM ITQ 2023Pablo Miguel Copca BeltranBelum ada peringkat

- Microsoft Word - TAREA POTENCIA ELECTRICADokumen8 halamanMicrosoft Word - TAREA POTENCIA ELECTRICASebastian muñoz cardona100% (1)

- Infografía Cadena de ValorDEFDokumen1 halamanInfografía Cadena de ValorDEFgabrielharrisvBelum ada peringkat

- Contenidos Ciencias 2° SecundariaDokumen5 halamanContenidos Ciencias 2° SecundariaProfra. Brenda CardielBelum ada peringkat

- Hoja de Calculo CompresibilidadDokumen10 halamanHoja de Calculo Compresibilidadcabrerajr7Belum ada peringkat

- Clasificacion de Las Turbinas HidráulicasDokumen7 halamanClasificacion de Las Turbinas HidráulicasfranBelum ada peringkat

- Separata Materia - 2007Dokumen7 halamanSeparata Materia - 2007Kelly MejíaBelum ada peringkat

- Practica 4 MAQUINAS ELECTRICASDokumen13 halamanPractica 4 MAQUINAS ELECTRICASSandy Catalán de IzaBelum ada peringkat

- Material de Estudio - Parte IIDokumen53 halamanMaterial de Estudio - Parte II111sinpar111Belum ada peringkat

- Tarea Instrumentación 2Dokumen4 halamanTarea Instrumentación 2Ari MirandaBelum ada peringkat

- Calculos BciDokumen5 halamanCalculos BciLeonardo Salgado GonzálezBelum ada peringkat

- Ciclo CombinadoDokumen3 halamanCiclo CombinadoHéctor J. CajasBelum ada peringkat

- Ensayo GeotermiADokumen7 halamanEnsayo GeotermiAAlejandro Juarez JacomeBelum ada peringkat

- Capitulo Iv. Energia y Potencial ElectricoDokumen65 halamanCapitulo Iv. Energia y Potencial ElectricoGiuliana Estefany Alania LlanosBelum ada peringkat