Sdc-Labmanual by Prabhu Kumar Surarapu

Diunggah oleh

prabhu4scribdDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Sdc-Labmanual by Prabhu Kumar Surarapu

Diunggah oleh

prabhu4scribdHak Cipta:

Format Tersedia

SEMICONDUCTOR DEVICES AND

CIRCUITS LAB

Prepared By

Mr.PRABHU KUMAR SURARAPU

Mrs.Anitha Bontha

Assistant professors, Department of ECE

Vel Tech Dr RR&Dr SR Technical University

U3ECB04

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

2

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

COURSE CODE: U3ECB04

COURSE TITLE: SEMICONDUCTOR DEVICES AND CIRCUITS LAB

AIM: To draw the VI characteristics of various semiconductor devices and design some

application for the devices.

COURSE OBJECTIVES

On completion of this course the student will understand

The methods of biasing transistors

Design of simple amplifier circuit

Mid-band analysis of amplifier circuit using small signal equivalent circuit to

determine gain input impedance and output impedance

COURSE OUTCOMES

Apply concepts of semiconductor devices to design and analyze circuits.

Apply fundamentals of semiconductor devices in electronics projects and use

computer tools in circuit design, evaluation and analysis.

LIST OF EXPERIMENTS

1. Characteristics of semiconductor diode & Zener diode.

2. Characteristics of CE & CB Configuration of BJT.

3. Characteristics of JFET and MOSFET

4. Characteristics of SCR

5. Characteristics of UJT

6. Characteristics of photo diode and photo transistor

7. Design and Testing of Full Wave Rectifier Circuit without and with filter.

8. Characteristics of Shunt & Series Regulator.

9. Clippers and clampers

10. To design biasing circuit for BJT and finding the DC load line.

BEYOND THE SYLLABUS:

1. Design of AC-DC voltage converter using SCR

2. Design of FET amplifier

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

3

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

INDEX

SL.No Name of the Experiment page

1

Characteristics of semiconductor diode & Zener diode

2

Characteristics of CE & CB Configuration of BJT

3

Characteristics of JFET and MOSFET

4

Characteristics of SCR

5

Characteristics of UJT

6

Characteristics of photo diode and photo transistor

7

Design and Testing of Full Wave Rectifier Circuit without and with filter

8

Characteristics of Shunt & Series Regulator

9

Clippers and clampers

10

Biasing circuit for BJT and finding the DC load line.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

4

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

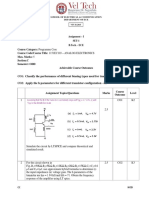

EXP NO:1 CHARACTERISTICS OF SEMICONDUCTOR DIODE & ZENER DIODE

1(A) CHARACTERISTICS OF SEMICONDUCTOR DIODE

AIM:

To study the PN junction characteristics under the forward and reverse bias.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 R.P.S (0-30)V 1

2 Ammeter (0-100)A 1

3 Voltmeter (0-1)V 1

4 Diode IN4001 1

5 Resistor 1K 1

6 Bread board 1

7 Wires

THEORY:

A PN junction diode is a two terminal junction device. It conducts only in one direction

(only on forward biasing).

Forward Bias:

On forward biasing, initially no current flows due to barrier potential. As the applied

potential exceeds the barrier potential the charge carriers gain sufficient energy to cross

the potential barrier and hence enter the other region. The holes, which are majority

carriers in the P-region, become minority carriers on entering the N-regions, and electrons,

which are the majority carriers in the N-region, become minority carriers on entering the

P-region. This injection of Minority carriers results in the current flow, opposite to the

direction of electron movement.

REVERSE BIAS:

On reverse biasing, the majority charge carriers are attracted towards the terminals

due to the applied potential resulting in the widening of the depletion region. Since the

charge carriers are pushed towards the terminals no current flows in the device due to

majority charge carriers. There will be some current in the device due to the thermally

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

5

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

generated minority carriers. The generation of such carriers is independent of the applied

potential and hence the current is constant for all increasing reverse potential. This current

is referred to as Reverse Saturation Current (IO) and it increases with temperature. When

the applied reverse voltage is increased beyond the certain limit, it results in breakdown.

During breakdown, the diode current increases tremendously.

PROCEDURE:

FORWARD BIAS:

1. Connect the circuit as per the diagram.

2. Vary the applied voltage V in steps of 0.1V.

3. Note down the corresponding Ammeter readings If.

4. Plot a graph between Vf & If

CIRCUIT DIAGRAM:

(0-100)A

1K

+ -

+ +

(0-30)V (0-1)V

-

-

Fig:1.1

Forward Bias Connection Diagram

REVERSE BIAS:

1. Connect the circuit as per the diagram.

2. Vary the applied voltage Vr in steps of 0.5V.

3. Note down the corresponding Ammeter readings Ir.

4. Plot a graph between Vr & Ir

5. Find the dynamic resistance r = V / I.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

6

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

CIRCUIT DIAGRAM:

Fig 1.2

Reverse Bias Connection Diagram

OBSERVATIONS:

1. Find the d.c (static) resistance = Vf / If.=

2. Find the d.c (static) resistance = V / I (r = V/ I) =

3. Find the forward voltage drop=

[It is equal to 0.7 for Si and 0.3 for Ge]

FORMULA FOR REVERSE SATURATION CURRENT (IO):

Io = I/[exp(V/VT)]-1=

Where VT is the voltage equivalent of Temperature = kT/q

k is Boltzmanns constant, q is the charge of the electron and T is the temperature in

degrees Kelvin.

=1 for Silicon and 2 for Germanium

V2 V1

.=

I

2

I1

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

7

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

MODEL GRAPH:

I

f

(A)

I

2

V

r

(V) I

1

V1 V2 Vf (V)

I

r

(A)

Fig 1.3

V-I Characteristics of PN Junction Diode

TABULAR COLUMN:

Forward Bias Reverse Bias

S.No Voltage(Vr)

(In Volts)

Current (Ir)

(In A)

RESULT:

Forward and Reverse bias characteristics of the PN junction diode was

Studied and the dynamic resistance under

Forward bias=_____________

Reverse bias=______________

Reverse Saturation current=_________________

S.No Voltage(Vf )

(In Volts)

Current (If)

(In A)

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

8

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

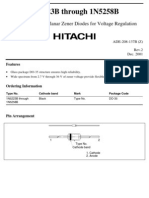

1(B) CHARACTERISTICS OF ZENER DIODE

AIM:

To study the characteristics and to determine the breakdown voltage of a zener diode

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 R.P.S (0-30)V 1

2 Ammeter (0-100)mA 1

3 Voltmeter (0-1)V 1

4 Voltmeter (0-30)V 1

5 Zener Diode 1

6 Resistor 1k 1

7 Bread board 1

8 Wires

THEORY:

A properly doped crystal diode, which has a sharp breakdown voltage, is known as zener

diode.

FORWARD BIAS:

On forward biasing, initially no current flows due to barrier potential. As the applied

potential increases, it exceeds the barrier potential at one value and the charge carriers

gain sufficient energy to cross the potential barrier and enter the other region. the holes

,which are majority carriers in p-region, become minority carriers on entering the N-

regions and electrons, which are the majority carriers in the N-regions become minority

carriers on entering the P-region. This injection of minority carriers results current,

opposite to the direction of electron movement.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

9

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

REVERSE BIAS:

When the reverse bias is applied due to majority carriers small amount of current

(ie) reverse saturation current flows across the junction. As the reverse bias is increased to

breakdown voltage, sudden rise in current takes place due to zener effect.

ZENER EFFECT:

Normally, PN junction of Zener Diode is heavily doped. Due to heavy doping the

depletion layer will be narrow. When the reverse bias is increased the potential across the

depletion layer is more. This exerts a force on the electrons in the outermost shell. Because

of this force the electrons are pulled away from the parent nuclei and become free

electrons. This ionization, which occurs due to electrostatic force of attraction, is known as

Zener effect. It results in large number of free carriers, which in turn increases the reverse

saturation current.

PROCEDURE:

FORWARD BIAS:

1. Connect the circuit as per the circuit diagram.

2. Vary the power supply in such a way that the readings are taken in steps of 0.1V.

3. Note down the corresponding ammeter readings.

4. Plot the graph : Vf (vs) If.

5. Find the dynamic resistance r = V / I.

CIRCUIT DIAGRAM:

(0-100)A

1K

+ -

+ +

(0-30)V (0-1) V

- -

Fig 1.4

Forward bias connection Diagram

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

10

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

REVERSE BIAS:

1. Connect the circuit as per the diagram.

2. Vary the power supply in such a way that the readings are taken in steps of 0.5V.

3. Note down the corresponding Ammeter readings Ir.

4. Plot a graph between Vr & Ir

5. Find the dynamic resistance r = V / I.

CIRCUIT DIAGRAM:

Fig 1.5

Reverse bias connection Diagram

TABULAR COLUMN:

Forward Bias Reverse Bias

S.No Voltage(Vr)

(In Volts)

Current (Ir)

(In mA)

S.No Voltage(Vf )

(In Volts)

Current (If)

(In mA)

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

11

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

MODEL GRAPH:

I

f

(in mA)

I

2

V

B

I

1

V

r

V

1

V

2

V

f

(in volts) (in volts)

I

r

(in mA)

Fig 1.6

V- I Characteristics of Zener Diode

RESULT:

Forward and Reverse bias characteristics of the zener diode were studied and the

values of the various parameters were found to be:

Forward bias dynamic resistance = ---------------------

Reverse bias dynamic resistance = ----------------------

The reverse Breakdown voltage = ----------------------

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

12

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO:2 CHARACTERISTICS OF BJT IN CE &CB CONFIGURATIONS

2(A) CHARACTERISTICS OF BJT IN CE CONFIGURATION

AIM:

To study and plot the transistor characteristics in CE configuration.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Dual R.P.S (0-30)V 1

2

Ammeter

(0-10)mA 1

(0-100)A 1

3

Voltmeter

(0-2)V 1

(0-30)V 1

4 Transistor BC 107 1

5 Zener Diode 1

6 Resistor 10 k ,1k 1

7 Bread board 1

8 Wires

THEORY:

A BJT is a three terminal two junction semiconductor device in which the

conduction is due to both the charge carrier. Hence it is a bipolar device and it amplifier the

sine waveform as they are transferred from input to output. BJT is classified into two types

NPN or PNP. A NPN transistor consists of two N types in between which a layer of P is

sandwiched. The transistor consists of three terminal emitter, collector and base. The

emitter layer is the source of the charge carriers and it is heartily doped with a moderate

cross sectional area. The collector collects the charge carries and hence moderate doping

and large cross sectional area. The base region acts a path for the movement of the charge

carriers. In order to reduce the recombination of holes and electrons the base region is

lightly doped and is of hollow cross sectional area. Normally the transistor operates with

the EB junction forward biased.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

13

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

In transistor, the current is same in both junctions, which indicates that there is a

transfer of resistance between the two junctions. Hence known as transfer resistance of

transistor.

PROCEDURE:

INPUT CHARECTERISTICS:

1. Connect the circuit as per the circuit diagram.

2. Set VCE , vary VBE in regular interval of steps and note down the Corresponding IB

reading. Repeat the above procedure for different values of VCE.

3. Plot the graph: VBE Vs IB for a constant VCE.

OUTPUT CHARACTERISTICS:

1. Connect the circuit as per the circuit diagram.

2. Set IB, Vary VCE in regular interval of steps and note down the corresponding IC

reading. Repeat the above procedure for different values of IB.

3. Plot the graph: VCE Vs IC for a constant IB.

CIRCUIT DIAGRAM:

(0 30)mA

1 K

-

A

+

(0 250) A

C

+

+

10 K

+

A

-

(0-30)V

BC107 V (0-30)V

-

+

+

B

(0-30)V

(0-1)V

-

V

E

-

-

Fig 2.1

CE Configuration Connection Diagram

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

14

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

TABULAR COLUMN:

INPUT CHARACTERISTICS:

VCE=1V VCE=2V

VBE(V) IB(A) VBE(V) IB(A)

OUTPUT CHARACTERISTICS:

IB=20A IB=40A

VCE(V) IC(mA) VCE(V) IC(mA)

MODEL GRAPH:

INPUT CHARACTERISTICS: OUTPUT CHARACTERSTICS:

A

mA

I

B

I

C

V

CE

= 0V

V

CE

= 5V

I

B

=60A

I

B

=40A

I

B

=20A

0

V

BE

(V)

0

V

CE

(V)

Fig 2.2

V-I Characteristics of BJT (CE Configuration)

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

15

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

RESULT:

The transistor characteristics of a Common Emitter (CE) configuration were

plotted.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

16

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

2(B) CHARACTERISTICS OF BJT IN CB CONFIGURATION

AIM:

To study and plot the transistor characteristics in CB configuration.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Dual R.P.S (0-30)V 1

2

Ammeter

(0-10)mA 1

(0-10)A 1

3

Voltmeter

(0-2)V 1

(0-30)V 1

4 Transistor BC 107 1

5 Zener Diod 1

6 Resistor 10 k ,1k 1

7 Bread board 1

8 Wires

THEORY:

In this configuration the base is made common to both the input and out. The emitter

is given the input and the output is taken across the collector. The current gain of this

configuration is less than unity. The voltage gain of CB configuration is high. Due to the high

voltage gain, the power gain is also high. In CB configuration, Base is common to both input and

output. In CB configuration the input characteristics relate IE and VEB for a constant VCB.

Initially let VCB = 0 then the input junction is equivalent to a forward biased diode and the

characteristics resembles that of a diode. Where VCB = +VI (volts) due to early effect IE

increases and so the characteristics shifts to the left. The output characteristics relate IC and

VCB for a constant IE. Initially IC increases and then it levels for a value IC = IE. When IE is

increased IC also increases proportionality. Though increase in VCB causes an increase in ,

since is a fraction, it is negligible and so IC remains a constant for all values of VCB once it

levels off.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

17

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

PROCEDURE:

INPUT CHARACTERISTICS:

It is the curve between emitter current IE and emitter-base voltage VBE at constant

collector-base voltage VCB.

1. Connect the circuit as per the circuit diagram.

2. Set VCE=5V, vary VBE in steps of 0.1V and note down the corresponding

IB. Repeat the above procedure for 10V, 15V.

3. Plot the graph VBE Vs IB for a constant VCE.

4. Find the h parameters.

OUTPUT CHARACTERISTICS:

It is the curve between collector current IC and collector-base voltage VCB at constant

emitter current IE.

1. Connect the circuit as per the circuit diagram.

2. Set IB=20A, vary VCE in steps of 1V and note down the corresponding IC.

Repeat the above procedure for 40A, 80A, etc.

3. Plot the graph VCE Vs IC for a constant IB.

4. Find the h parameters

CIRCUIT DIAGRAM:

Fig 2.3

CB Configuration Connection Diagram

(0-1)mA (0-30)mA

10 K

+ - + -

1K -

+

+ +

(0-30)V VEB

(0-2)V (0-30)V (0-30)V

-

- -

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

18

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

TABULAR COLUMN:

INPUT CHARACTERISTICS:

S.No. VCB = V VCB = V VCB = V

VEB IE VEB IE VEB IE

(V) (A) (V) (A) (V) (A)

OUTPUT CHARACTERISTICS:

S.No. IE= mA IE= mA IE= mA

VCB Ic VCB Ic VCB Ic

(V) (mA) (V) (mA) (V) (mA)

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

19

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

MODEL GRAPH:

INPUT CHARACTERISTICS:

I

C

(mA)

VCB1

IE2

VCB2

IE1 VEB1 VEB2 VEB (V)

OUTPUT CHARACTERISTICS:

I

C

(mA) I

E3

IC2 IE2

IC1

IE1

VCB1 VCB2 VCB (V)

Fig 2.4

V-I Characteristics of BJT (CB Configuration)

RESULT:

The transistor characteristics of a Common Base (CB) configuration were plotted

and studied.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

20

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO: 3 CHARACTERISTICS OF JFET & MOSFET

3(A) CHARACTERISTICS OF JFET

AIM:

To study and plot the characteristics of JFET.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Dual R.P.S (0-30)V 1

2 Ammeter (0-30)mA 1

3

Voltmeter

(0-10)V 1

(0-30)V 1

4 FET BFW10 1

5 Resistor 68 k ,1k 1

6 Bread board 1

7 Wires

THEORY:

FET is a voltage operated device. It has got 3 terminals. They are Source, Drain &

Gate. When the gate is biased negative with respect to the source, the pn junctions are

reverse biased & depletion regions are formed. The channel is more lightly doped than the

p type gate, so the depletion regions penetrate deeply in to the channel. The result is that

the channel is narrowed, its resistance is increased, & ID is reduced. When the negative bias

voltage is further increased, the depletion regions meet at the center & ID is cutoff

completely.

PROCEDURE:

DRAIN CHARACTERISTICS:

1. Connect the circuit as per the circuit diagram.

2. Set the gate voltage VGS = 0V.

3. Vary VDS in steps of 1 V & note down the corresponding ID

4. Repeat the same procedure for VGS = -1V.

5. Plot the graph VDS Vs ID for constant VGS.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

21

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

OBSERVATIONS

1. D.C (Static) drain resistance rD=VDS/ID

2. A.C(Dynamic) drain resistance rd=VDS/ID

3. Open source impedance,YOS=1/rd

CIRCUIT

DIAGRAM:

(0-30mA)

1k

A

G

D

68K

BFW10

S

+

-

(0-30)V

V (0-10)V

V

(0-30)V

+

(0-30)V

-

Fig 3.1

JFET Connection Diagram

TRANSFER CHARACTERISTICS:

1. Connect the circuit as per the circuit diagram.

2. Set the drain voltage VDS = 5 V.

3. Vary the gate voltage VGS in steps of 1V & note down the corresponding ID.

4. Repeat the same procedure for VDS = 10V.

Plot the graph VGS Vs ID for constant VDS.

FET PARAMETER CALCULATION:

Drain Resistance rd =

V

DS

V

ID

GS

Transconductance gm =

ID

V

V

GS

DS

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

22

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

Amplification factor =rd . gm

TABULAR COLUMN:

DRAIN CHARACTERISTICS:

VGS = 0V VGS = -1V

VDS (V) ID(mA) VDS (V) ID(mA)

TRANSFER CHARACTERISTICS:

VDS =5volts VDS = 10volts

VGS (V) ID(mA) VGS (V) ID(mA)

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

23

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

MODEL GRAPH:

DRAIN CHARACTERISTICS:

I

D

(

m

A

)

V

GS

= 0V

V

GS

= -1V

V

GS

= -2V

V

GS

= -3V

0

VDS (volts)

TRANSFER CHARACTERISTICS:

ID(mA)

VDS =Const

VGS (V)

Fig 3.2

Drain and Transfer(V-I) characteristics of JFET

RESULT:

Thus the Drain & Transfer characteristics of given FET is Plotted.

Rd =

gm =

=

IDSS =

Pinch off voltage VP =

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

24

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO CHARACTERISTICS OF MOSFET

AIM:

To study and plot the characteristics of MOSFET.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Dual R.P.S (0-30)V 1

2 Ammeter (0-30)A 1

3 Voltmeter (0-30)V 2

4 MOSFET CD4007 1

5 Resistor 1

6 Bread board 1

7 Wires

THEORY:

The MOS (metal-oxide- semiconductor) transistor (or MOSFET) is the basic building

block of most computer chips, as well as of chips that include analog and digital circuits. In

this lab, we will work with what is called an n-channel MOS transistor. The internal

structure and operation of this device, as well as of its complement, the p-channel MOSFET

are studied in semiconductor device courses. Here we will concern ourselves only with

external i-v behavior.

A common symbol for the n-channel MOS transistor is shown in Fig. 3.3(a). Of the

terminals shown, the ones we will focus on are the source, the drain, and the gate. In the

transistor we will be working with in this lab, the fourth terminal, labeled body in Fig.

3.3(a), is not accessible externally; rather, it is internally connected to the source, as

shown by the broken line. For simplicity, then, we will use the symbol shown in Fig. 3.3

(b).

(a) Fig 3.3 (b)

n channel MOSFET

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

25

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

To study the MOS transistor, we can connect two external voltage sources to it, as

shown in Fig.3.5. These provide the drain-source voltage vDS and the gate-source voltage

vGS. The voltage vDS may cause a drain-to-source current iDS as shown, provided that there

is a path for this current from the drain (through the device) to the source. Whether such a

path exists or not depends on the value of vGS. For small values of vGS, no such path is

established within the device, and iDS is zero. The device then looks like an open circuit

between the drain and the source. For a sufficiently high vGS, an internal current path,

called a channel, is established between the drain and the source. Now a current iDS can

flow. The precise value of vGS determines how easy it is for the channel to conduct the

current; the higher the vGS value, the easier such conduction is and the larger the value of

iDS, other things being equal. For a given vGS, the value of iDS will also depend on vDS and

will tend to increase with the latter.

PROCEDURE:

1. Hook up the circuit of Fig. 3.5. This circuit will be used in the following steps to

investigate the i-v characteristics of the n-channel MOSFET. The chip used in this

experiment is a CD4007, containing six MOSFETs. We will use only one of them, as

shown in the pin assignment in Fig. 3.4

Fig 3.4

Pin Diagram

2. Set vGS = 5 V Measure the drain current iDS, versus the drain-source voltage, vDS, from

0 to 5 V Make sure you take measurements at a sufficient number of vDS values since

you will later need to plot iDS versus vDS. Include a point at vDS = 0.1 V for later use.

3. Repeat the entire step 2 for vGS = 3 V and vDS = 1 V.

4. With vDS = 5 V, determine the value of vGS at which the current iDS becomes

negligible; assume that for our purposes this means 5 A. This value of vGS is

close to the so-called threshold voltage of the transistor, and it is positive for an

"enhancement mode" MOSFET, which is what we are working with here.

5. Using the data you have collected in steps 2 and 3, plot a family of curves for the

drain current, iDS, versus the drain-source voltage, vDS from 0 to 5 V, with vGS as a

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

26

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

parameter. Use a single set of vDS - iDS axes for this plot. There should be one curve

for each vGS value (1 V, 3 V, and 5 V) on this family of curves. Label each curve with

the corresponding vGS value.

6. You should be able to observe on the above plot that, for each curve, the current tends to

a constant (or, as we say, saturates) as v

DS

is made large. What is, approximately, the

saturation value of the current for each of the three v

GS

values?

CIRCUIT DIAGRAM:

Fig 3.5

MOSFET Connection Diagram

TABULAR COLUMN:

VGS = 5V VGS = 3V

VGS=1V

VDS (V) ID(mA) VDS (V) ID(mA) VDS (V) ID(mA)

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

27

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

MODEL GRAPH:

Fig 3.6

V-I Characteristics of MOSFET

RESULT:

Thus the characteristics of given MOSFET is Plotted.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

28

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO:4 CHARACTERISTICS OF SILICON CONTROL RECTIFIER

Aim:

To obtain the V-I characteristics of SCR and find the break over voltage and holding

current.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Dual R.P.S (0-30)V 1

2 Ammeter (0-10)mA 1

(0-100)mA 1

3 Voltmeter (0-30)V

1

4 Diode 1N4001 1

5 SCR TYN604 1

6 Resistor 330,10 1

7 Bread board 1

8 Wires

THEORY:

A silicon controlled rectifier (SCR) is a semiconductor device that acts as a true

electronic switch. It can change the alternating current in to direct current. It can

control the amount of power fed to the load. Thus the SCR combines the features of

rectifier and a transistor. If the supply voltage is less than the break over voltage, the

gate will open (IG = 0). Then increase the supply voltage from zero, a point is reached

when the SCR starts conducting. Under this condition, the voltage across the SCR

suddenly drop and most of the supply voltage appears across the load resistance

RL.If proper gate current is made to flow the SCR can close at much smaller supply

voltage.

PROCEDURE:

The connections are made as per in the circuit diagram.

First by varying RPS 2 then gate current (IG) is kept constant.

The voltage between anode and cathode is increased in step by step by

varying the RPS 1.

The corresponding anode current (IA) is noted.

The process is repeated for two more constant value of IG, the readings are tabulated.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

29

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

Fig 4.1

Connection Diagram for SCR

Tabulation:

S. No Anode- Gate Anode Anode

Cathode Current Current Cathode

Voltage Vak Ig (mA) Ia (mA) volt when

(Volts)

SCR in

ON (volts)

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

30

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

MODEL GRAPH:

Fig 4.2

V-I Characteristics of SCR

RESULT:

Thus the V-I characteristics of SCR was obtained and graph was drawn.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

31

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO:5 CHARACTERISTICS OF UNIJUNCTION TRASISTOR

AIM:

To Plot and study the characteristics of UJT & determine its intrinsic standoff Ratio.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Dual R.P.S (0-30)V 1

2 Ammeter (0-30)mA

1

3 Voltmeter

(0-30)V

1

(0-10)V 1

4 UJT 2N2646 1

5 Resistor 1K 2

6 Bread board 1

7 Wires

THEORY:

UJT(Double base diode) consists of a bar of lightly doped n-type silicon with a small

piece of heavily doped P type material joined to one side. It has got three terminals. They

are Emitter(E), Base1(B1),Base2(B2).Since the silicon bar is lightly doped, it has a high

resistance & can be represented as two resistors, rB1 & rB2. When VB1B2 = 0, a small

increase in VE forward biases the emitter junction. The resultant plot of VE & I E is simply

the characteristics of forward biased diode with resistance. Increasing VEB1 reduces the

emitter junction reverse bias. When VEB1 = VrB1 there is no forward or reverse bias. & IE =

0. Increasing VEB1 beyond this point begins to forward bias the emitter junction. At the

peak point, a small forward emitter current is flowing. This current is termed as peak

current( IP ). Until this point UJT is said to be operating in cutoff region. When IE increases

beyond peak current the device enters the negative resistance region. In which the

resistance rB1 falls rapidly & VE falls to the valley voltage.Vv. At this point IE = Iv. A further

increase of IE causes the device to enter the saturation region.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

32

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

PROCEDURE:

1. Connect the circuit as per the circuit diagram.

2. Set VB1B2 = 0V, vary VEB1 , & note down the readings of IE & VEB1

3. Set VB1B2 = 10V , vary VEB1 , & note down the readings of IE & VEB1

4. Plot the graph : IE Versus VEB1 for constant VB1B2.

5. Find the intrinsic standoff ratio.

CIRCUIT DIAGRAM:

1K (0-30)mA

1K

A

E

V

B2

V

(0-30)V

(0-30)V

(0-30)V

(0-30)V

Fig 5.1

UJT Connection Diagram

FORMULA FOR INTRINSIC STANDOFF RATIO:

= VP - VD/ VB1B2., where VD = 0.7V.

PROCEDURE:

1. Give the circuit connections as per the circuit diagram.

2. The dc input voltage is set to 20 V in RPS.

3. The output sweep waveform is measured using CRO.

4. The graph of output sweep waveform is plotted

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

33

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

TABULAR COLUMN:

VB1B2 =0V

VB1B2 =10V

VEB1(V)

IE(mA)

VEB1(V)

IE(mA)

MODEL GRAPH:

Peak point

V

P

I

P

Negative resistance region

V

EB1

(V)

Valley point V

B1B2

= V

V

B1B2

= 0V

I

V

I

E

(mA)

Fig 5.2

V-I Characteristics of UJT

RESULT:

Thus the characteristics of given UJT was Plotted & its intrinsic standoff Ratio = ----.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

34

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO:6 CHARACTERISTICS OF PHOTO DIODE AND PHOTO TRANSISTOR

6(A) CHARACTERISTICS OF PHOTO DIODE

AIM:

To plot distance Vs Photocurrent Characteristics of Photodiode.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Dual R.P.S (0-30)V 1

2

Ammeter

(0-10)mA 1

(0-100)A 1

3 Voltmeter (0-10)V 1

4 LDR 1K 1

5 Photo Diode BPW34 1

6 Bread board 1

7 Wires

THEORY:

A silicon photodiode is a solid state light detector that consists of a shallow

diffused P-N junction with connections provided to the outside world. When the top

surface is illuminated, photons of light penetrate into the silicon to a depth determined by

the photon energy and are absorbed by the silicon generating electron-hole pairs.

The electron-hole pairs are free to diffuse (or wander) throughout the bulk of the

photodiode until they recombine. The average time before recombination is the minority

carrier lifetime.

At the P-N junction is a region of strong electric field called the depletion region.

It is formed by the voltage potential that exists at the P-N junction. Those light generated

carriers that wander into contact with this field are swept across the junction. If an external

connection is made to both sides of the junction a photo induced current will flow as long

as light falls upon the photodiode. In addition to the photocurrent, a voltage is produced

across the diode. In effect, the photodiode functions exactly like a solar cell by generating a

current and voltage when exposed to light.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

35

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

PROCEDURE:

1. Connect circuit as shown in figure

2. Maintain a known distance between the bulb and photodiode say 5cm

3. Set the voltage of the bulb,vary the voltage of the diode in steps of 1 volt and note down the

diode current Ir.

4. Repeat above procedure for VL=4V,6V,etc. Plot

the graph: Vd Vs Ir for constant VL

CIRCUIT DIAGRAM:

Fig 6.1

Photodiode Connection Diagram

TABULAR

COLUMN:

S. No

Distance(cm) IR (A)

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

36

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

MODEL GRAPH:

Fig 6.2

Characteristic Graph of Photodiode

RESULT:

The characteristic of Photodiode is to be tabulated and the graphs are plotted.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

37

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

6(B) CHARACTERISTICS OF PHOTO TRANSISTOR

AIM:

To plot the V-I Characteristics of Phototransistor.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Dual R.P.S (0-30)V 1

2 Ammeter (0-10)mA 1

3 Voltmeter (0-30)V 1

4 Phototransistor IR 3MM 935 NM 1

5 Resistor 220 1

6 Bread board 1

7 Wires

THOERY:

The photo transistor is a 3 terminal device which gives an electrical

current as output if an input light excitation is provided. It works in reverse bias.

When reverse biased along with the reverse bias current ICO, the light current IL is

also added to the total output current. The amount of current flow depends on the

input light intensity given as excitation. Phototransistor is basically a photodiode

with amplification and operates by exposing its base region to the light source.

Phototransistor light sensors operate the same as photodiodes except that they can

provide current gain and are much more sensitive than the photodiode with

currents are 50 - 100 times greater than that of the standard photodiode.

Phototransistors consist mainly of a bipolar NPN transistor with the collector-base

PN-junction reverse-biased. The phototransistors large base region is left

electrically unconnected and uses photons of light to generate a base current which

in turn causes a collector to emitter current to flow.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

38

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

PROCEDURE:

1. Connect the circuit as per circuit diagram.

2.Keep the input light excitation fixed. Then vary the Vce in the steps 1V till the

maximum voltage rating of the transistor is reached and then note down the

corresponding values of Ic

3. Tabulate the readings. For various values of input excitation record the values Vce

and Ic and plot the characteristics of the photo transistor.

CIRCUIT DIAGRAM:

Fig 6.3

Photo transistor Connection diagram

TABULAR COLUMN:

V

ce

(V) I

c

(mA)

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

39

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

MODEL GRAPH:

Fig 6.4

Characteristic Graph of Photo transistor

RESULT:

The characteristic of the photo transistor was plotted.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

40

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO: 7 DESIGN AND TESTING OF FULL WAVE RECTIFIER CIRCUIT

WITHOUT AND WITH FILTER.

AIM:

To design a full wave rectifier circuit with and without filter for desired DC voltage

and DC current.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Center tapped

Transformer

1

2 Ammeter (0-30)mA 1

3 Voltmeter (0-30)V

1 (0-1)V

4 Diode 1N4007 2

5 Resistor 220 1

6 CRO 1

7 Probes

8 Bread board 1

9 Wires

THEORY:

In full-wave rectifier current flows through the load in the same direction for both

half cycles of input AC voltage .This can be achieved with two diodes working alternatively.

During the +ve half cycle one diode conducts and supplies current to the load. During the

negative half cycle the other diode conducts and current flows through the load in the same

direction. Thus the full-wave rectifier produces continuous pulsating DC output.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

41

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

DESIGN:

Rectifier Without Filter

Given Vdc= ---volts, Idc = ---mA

Vdc = Idc * RL

When no filter circuit is present the output DC level , Vdc=2Vm /.

The RMS value of the secondary voltage of the transformer is Vrms = Vm / 2.

The diode used must have PIV rating > 2Vm.

Rectifier With Capacitor Filter

Given Vdc= ---volts, Idc = ---mA for a ripple of ---% with the reasonable size capacitor

filter to be designed, the o/p Dc level comes closer to Vm .

Ripple factor for full-wave rectifier with capacitor filter is given by

r (theoritical) = 1 / 4 *3 *f*C * RL

r (practical ) = Vac / Vdc

PROCEDURE:

1. Make circuit connections for the designed values as per the diagram.

2. Switched ON the power supply.

3. Note the DC voltage and current and also the ripple factor.

4. Verify the values with the given designed values.

5. For FWR with filter circuit, connect a capacitor across load resistor.

6. The same procedure is repeated for both with and without filter.

7. Then trace the o/p waves in CRO.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

42

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

CIRCUIT DIAGRAM:

Fig 7.1Full wave Rectifier Circuit without Filter

IN 4007

RL

( 0 - 30 ) V

230V / AC

N

IN 4007

( 0 - 30 ) mA

P

( 0 - 1 ) V

C

CRO

A

V

V

Idc

Vdc

Vac

Fig 7.2 Full wave Rectifier Circuit with Filter

TABULAR COLUMN:

Without filter

Vdc(theo)

(V)

Vdc(prac)

(V)

Idc(theo)

(mA)

Idc(prac)

(mA)

Ripple factor

r (theo)

Ripple

factor r

(prac)

P

N

230V / AC

IN 4007

IN 4007

( 0 - 30 ) mA

( 0 - 30 ) V

RL

A

V

CRO

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

43

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

With filter

Vdc(theo)

(V)

Vdc(prac)

(V)

Idc(theo)

(mA)

Idc(prac)

(mA)

Ripple factor

r (theo)

Ripple

factor r

(prac)

MODEL GRAPH:

Fig 7.3 full wave rectifier Model graph

RESULT:

Thus the half wave rectifier with and without filter is constructed for the given

design specification.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

44

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO: 8 CHARACTERISTICS OF SHUNT & SERIES REGULATOR

8(A) CHARACTERISTICS OF SERIES REGULATOR

AIM:

To study Transistor series voltage regulator, when input voltage Vin is fixed while

Load resistance RL is variable.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 R.P.S (0-30)V 1

2 Voltmeter 0-30)V 3

3 Zenar Diode 1N4007 2

4 Resistor 200&Resisor Load

Box

1

5 Transistor 2N3904 1

6 Bread board 1

7 Wires

THEORY:

Circuits that maintain power supply voltages or current output within specified limits, or

tolerances are called Regulators. They are designated as dc voltage or dc current regulators,

depending on their specific application.

Voltage regulator circuits are additions to basic power supply circuits, which are made up

of rectifier and filter sections (Fig 8.1). The purpose of the voltage regulator is to provide

an output voltage with little or no variation. Regulator circuits sense changes in output

voltages and compensate for the changes

Fig 8.1

Basic Voltage regulator Block Diagram

There are two types of voltage regulators. Basic voltage regulators are classified as

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

45

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

either Series or Shunt, depending on the location or position of the regulating element(s) in

relation to the circuit load resistance. Fig 2 illustrates these two basic types of voltage

regulators. Broken lines have been used in the figure to highlight the difference between

the series and shunt regulators.

Fig 8.2

Shunt and Series regulators

The schematic drawing in view B is that of a series regulator. It is called series

regulator because the regulating device is connected in series with the load resistance. Fig

8.2 illustrates the principle of series voltage regulation. From the figure it is clear that the

regulator is in series with the load resistance (RL) and that the fixed resistor (RS) is in

series with the load resistance. You already know the voltage drop across affixed resistor

remains constant unless the current flowing through it varies (increases or decreases).

The schematic for a typical series voltage regulator is shown in Fig8.3. Notice that this

regulator has a NPN transistor 2N3904 in place of the variable resistor found in Fig 8.2.

Because the total load current passes through this transistor, it is sometimes called a pass

transistor. Other components, which make up the circuit, are the current limiting resistor

of 200 and the Zener diode of 5.6V

Recall that a Zener diode is a diode that block current until a specified voltage is

applied. Remember also that the applied voltage is called breakdown, or Zener voltage.

When the Zener voltage is reached, the Zener diode conducts from its anode to its cathode

(with the direction of the arrow).

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

46

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

In this voltage regulator, Transistor has a constant voltage applied to its base. This

voltage is often called the reference voltage. As the change in the circuit output voltage

occur, they are sensed at the emitter of the transistor producing a corresponding change in

the forward bias of the transistor. In other words, transistor compensates by increasing or

decreasing its resistance in order to change the circuit voltage division.

CIRCUIT OPERATION:

CASE 1 : when input voltage is constant while Load varies.

Here NPN Transistor used in series controls the amount of the input voltage that gets to the

output and zener diode provides the reference voltage. The zener establishes the value of

the base voltage for transistor. Keep in mind the polarities of different voltages, they are

related by the equation

VL + VBE - V z = 0 Kirchoff's voltage law

Therefore VBE = VZ -VL Here VZ is fixed

The output voltage across load will equal the zener voltage minus a 0.7-volt

drop across the forward biased base-emitter junction of transistor, or 4.9V (5.6 - 0.7).

When current demand is increased by decreasing RL, VL tends to decrease. It will increase

VBE because VZ is fixed. This will increase forward bias of the transistor thereby increasing

its level of conduction. This will lead to decrease in the collector-emitter resistance of the

transistor which will slightly increase the input current to compensate for decrease in RL

so that VL = ILRL will remain at constant value.

CASE 2: when input voltage varies while Load remains constant.

When the input voltage increases, output voltage across increases momentarily. This

momentarily deviation or variation, from the required regulated output voltage of 4.9 volts

is a result of a rise in the input voltage. Since the base voltage of transistor is held at 5.6V by

zener, that's why the forward bias of transistor decreases. Because this bias voltage is less

than the normal 0.7 volts, the resistance of transistor increases, thereby increasing the

voltage drop across the transistor.

This voltage drop restores the output voltage to the required regulated voltage of 4.9V.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

47

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

PROCEDURE:

Connect + 12V dc power supply at their indicated position from external source.

1. Connect one voltmeter between test point 1 and ground to measure input

voltage Vin.

2. Connect ohmmeter between test point 4 and ground and set the value of load

resistance RL at some fixed value [full load (1.1K), 1K, 500 ...]

3. Connect a patch cord between test point 2 and 3.

4. Connect voltmeter between test point 4 and ground to measure output

voltage Vout.

5. Switch ON the power supply.

6. Vary the potentiometer P1 to set fixed value of input voltage Vin = 9V and

measure the corresponding values of

a. Output voltage Vout between test points 4 and ground.

b. Zener voltage VZ between test points 5 and ground.

c. Forward bias voltage VBE of transistor between test point 5 and 4.

7. Disconnect the patch cord between test point 3 and 4.

8 .Repeat the procedure from step 3 for different sets of load resistance RL and

note the results in an observation Table.

Fig 8.3

Series Voltage Regulator

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

48

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

TABULAR COLUMN:

Load

Voltage Forward Output voltage

Sr. Across bias Vout at constant

Resistance

No. Zener voltage Input voltage

RL

VZ VBE Vin = 9 volt

1.

Full Load

(1.1K)

2. 1K

3. 800

4. 600

5. 400

6. 200

7. No Load

Note: To measure Voltage at No Load disconnects patch cord between test point 2 and 3,

measure voltage between test point 2 and ground.

CALCULATIONS:

Percentage regulation is given by formula

% Regulation = [(VNL - VFL) / VFL] * 100

Where,

R = resistance in series

VNL = no-load or open-circuit terminal voltage. VFL = full-load

terminal voltage.

RESULT:

1. The result of Experiment reveal that for the network of Fig 8.3 with a fixed input

voltage Vin the output voltage will remain close to 4.9 V for a range of load resistance

that extends from _________ to ___________ .

2. Percentage regulation = _________% .

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

49

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

8(B) CHARACTERISTICS OF SHUNT REGULATOR

AIM:

Study of Transistor shunt voltage regulator, when input voltage Vin is fixed while

Load resistance RL is variable.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 R.P.S (0-30)V 1

2 Voltmeter 0-30)V 3

3 Zener Diode 1N4007 2

4 Resistor 51&Resisor Load Box 1

5 Transistor 2N3904 1

6 Bread board 1

7 Wires

THEORY:

CIRCUIT OPERATION:

Case 1: when input voltage is constant while Load varies.

Since VZ is fixed, any decrease or increase in VL will have a corresponding effect on VBE.

Suppose, VL decreases, then as seen from the above relation VBE also decreases.

As a result, IB decreases, hence IC ( = IB) decreases, thereby decreasing I and hence VR

(=IR). Consequently, VL increases because at all times

Vin = VR + VL or VL = Vin - VR

From the above description it is concluded that when by any reason VL decreases VR also

decreases thereby keeping VL constant.

Similarly, when by any reason VL increases VR also increases thereby keeping VL constant.

Case 2: when input voltage varies while Load remains constant.

When the input voltage increases, output voltage across RL also increases momentarily.

This momentarily deviation or variation, from the required regulated output voltage of 6.3

volts is a result of a rise in the input voltage. This increases forward bias of transistor.

Recall that the voltage drop across Zener remains constant at 5.6V. Since the output voltage

is composed of the Zener voltage and the base-emitter voltage, the output voltage

momentarily increases. At this time, the increase in the forward bias of transistor lowers

the resistance of the transistor allowing more current to flow through it. Since this current

must also pass through R, there is also an increase in the voltage drop across this resistor.

Due to increase in this voltage drop across R, voltage across VL remains close to the

required regulated value of output voltage.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

50

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

PROCEDURE:

Connect + 12V DC power supply at its indicated position from external source.

1. Connect one voltmeter between test point 1 and ground to measure input voltage

Vin.

2. Connect ohmmeter between test point 5 and ground and set the value of load

resistance RL at some fixed value [full load (1.1K), 1K, 500 ]

3. Connect a 2mm patch cord between test point 3 and 4.

4. Connect voltmeter between test point 5 and ground to measure output voltage

Vout.

5. Switch On the power supply.

6. Vary the potentiometer P1 to set fixed value of input voltage Vin = 9V and measure

the corresponding values of

a. Output voltage Vout between test points 5 and ground.

b.Zener voltage VZ between test points 2 and 6.

c.Forward bias voltage VBE of transistor between test point 6 and ground.

7. Disconnect the patch cord between test point 3 and 4.

8. Repeat the procedure from step 3 for different sets of load resistance RL and note

the results in an observation Table.

CIRCUIT DIAGRAM:

Fig 8.3

Shunt Voltage Regulator

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

51

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

TABULAR COLUMN:

Load

Voltage Forward Output voltage

Sr. Across bias Vout at constant

Resistance

No. Zener voltage Input voltage

RL

VZ VBE Vin = 9 volt

1. Full Load (1.1K)

2. 1K

3. 800

4. 600

5. 400

6. 200

7. No Load

Note: To measure Voltage at No Load disconnects patch cord between test point 3 and 4,

measure voltage between test point 3 and ground.

CALCULATIONS:

Percentage regulation is given by formula

% Regulation = [(VNL - VFL) / VFL] * 100 VNL = no-

load or open-circuit terminal voltage.

VFL = full-load terminal voltage.

RESULTS:

1. The result of Experiment 1 reveal that for the network of Figure 3 with a fixed input

voltage Vin the output voltage will remain close to 6.3 V for a range of

load resistance that extends from __________ to __________ .

2. Percentage regulation = __________%.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

52

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO: 9 CLIPPERS AND CLAMPERS

9(A) CLIPPERS

AIM:

To study the clipping circuits for different reference voltages and to verify the responses.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 R.P.S (0-30)V 1

2 Voltmeter 0-30)V 3

3 Diode 1N4001 2

4 Resistor 1K 1

5 CRO 1

6 Function Generator 1

7 Bread board 1

8 Wires

THEORY:

When sinusoidal or non-sinusoidal waveforms are applied to non linear networks

consisting one nonlinear device such as diode or transistor the resultant output waveform

may be different from the i/p waveform. Hence the nonlinear circuit said to shape the i/p

voltage waveform. This is called non linear wave shaping.

The clipping circuit may be defined as a circuit that limits the amplitude of a voltage

by removing the signal above or below the reference voltage. Either +ive side or

ive side or both sides of the waveform may be clipped. Clipping circuits are also known as

voltage or current limiters.

The diode clipper circuits are classified according to the placement of the diode in

the circuit as a series diode clipper or shunt diode clipper.

SHUNT DIODE CLIPPERS:

i) WITH POSITIVE BIAS CLIPPERS:

Assuming the diode used is an ideal the shunt diode clipper with +ve bias is shown

in the figure. The diode is forward biased only when Vi > Vr as the cathode is at the

potential of Vr. To make the diode forward bias the potential at the cathode must be

greater than Vr.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

53

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

During the +ve half cycle Vi>Vr the diode acts as a short circuit and o/p voltage is

equals to the reference voltage Vr. When Vi <Vr the diode is reverse bias and the total i/p

voltage Vi appears across the open circuit o/p terminals as shown in the figure.

ii) WITH NEGATIVE BIAS CLIPPERS:

Assuming the diode used is an ideal in the shunt clippers with ve bias is shown in

the figure. The diode is forward bias during ve half cycle when Vi<Vr during this period

diode acts as a short circuit and the o/p voltage equals to the reference voltage Vr.

During complete +ve half cycle as well as during ve half cycle when Vi > Vr the

diode is reverse biased and it acts as a open circuit. Therefore Vi appears across open

circuit terminals of the o/p circuit.

SERIES DIODE CLIPPERS:

Assuming the diode used is an ideal the series diode clippers with +ve bias as shown in the

figure, The diode conducts during ve half cycle as well as during +ve half cycle when Vi<Vr

as the anode of the diode is at the potential Vr. During this conduction the current flows

through the resistor when an o/p voltage appears across the open circuited o/p terminals

which is equal to Vi . During +ve half cycle when Vi >Vr the diode is reverse biased no

current flows through the resistor and the o/p voltage equal to the reference voltage Vr.

Assuming the diode used is an ideal one the series diode clipper with +ve bias is

shown in the figure. The diode conducts only when Vi >Vr as the cathode is at the potential

of Vr. To make diode forward bias anode potential must be greater than Vr. During +ve half

cycle when Vi > Vr the diode is forward bias and the current flows through the diode as

well as resistor. An o/p voltage appears across the open circuit output terminals which are

equal to Vi. During ve half cycle as well as during +ve half cycle when Vi<Vr the diode is

reverse bias and no current flows through the diode , hence through the resistor . Thus o/p

voltage equals to the reference voltage Vr.

UNBIASED SHUNT CLIPPERS:

During the +ve half cycle the diode is forward biased and diode acts as a short

circuit for the i/p signal. Therefore o/p voltage is zero. During ve half cycle the diode is

reverse biased and the diode acts as an open circuit. Thus Vi=Vr . During ve half cycle the

diode is forward bias and acts as a short circuit for the i/p signal. Therefore o/p is equal to

zero. During +ve half cycle the diode is reverse biased and the diode acts as an open circuit

thus the o/p voltage = i/p voltage.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

54

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

PROCEDURE:

1. Connect the circuit as shown in the figure.

2. Connect the function generator at the input terminals and CRO at the output

terminals of the circuit.

3. Apply a sine wave signal of frequency 1KHz, Amplitude greater than the

reference voltage at the Input and observe the output waveforms of the

circuits.

4. Repeat the procedure for remaining figures.

CIRCUIT DIAGRAMS:

Fig 9.1

Shunt diode positive clipper

Fig 9.2

Input and Output of Shunt positive clipper

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

55

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

Fig 9.3

Shunt diode negative clipper

Fig 9.4

Input and Output of Shunt negative clipper

Fig 9.5

Series diode positive clipper

Fig 9.6

Input and Output of series positive clipper

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

56

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

Fig 9.7

Series diode negative clipper

Fig 9.8

Input and Output of series negative clipper

RESULT:

The Diode applications are observed with clipper circuits and plotted different

responses.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

57

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

9(B) CLAMPERS

AIM:

To study the clamping circuits for different reference voltages and to verify the

responses.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 R.P.S (0-30)V 1

2 Voltmeter 0-30)V 3

3 Diode 1N4001 2

4 Resistor 1K 1

5 Capacitor 0.1f 1

6 CRO 1

7 Function Generator 1

8 Bread board 1

9 Wires

THEORY:

Clamping circuits are circuits, which are used to clamp or fix the extremity of a

periodic wave form to some constant reference level. Clamping circuits may be one way

clamps or two way clamps.

The clamping circuits only changes the dc level of the input signal .It does not affect

its shape. Clamping circuits may be positive voltage clamping circuits or negative voltage

clamping circuits. In positive clamping, the negative extremity of the wave form is at the

reference level and the entire wave form appears above the reference level. i.e. the output

wave form is positively clamped with reference to the reference level. In negative clamping

the positive extremity of the wave form is fixed at the reference level and the entire wave

form appears below the reference voltage. i.e. the output wave form is negatively clamped

with reference to the reference level.

The capacitors are essential in the clamping circuits. The difference between the

clipping and clamping circuits is that while the clipper clips off an unwanted portion of

the input wave form, the clipper simply clamps the maximum positive or negative peak

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

58

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

of the wave form to a desired level.

CIRCUIT DIAGRAM:

Fig 9.9

Positive Clamper

Fig 9.10

Input and output of Positive clamper

Fig 9.11

Negative Clamper

Fig 9.12

Input and output of Negative clamper

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

59

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

RESULT:

The Diode applications are observed with clamper circuit and plotted different

responses.

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

60

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

EXP NO: 10 BIASING CIRCUIT FOR BJT AND FINDING THE DC LOAD LINE

AIM:

To study the load line and operation point of basic transistor amplifier.

APPARATUS &COMPONENTS REQUIRED:

SL.No Name Range/Specification Qty

1 Dual R.P.S (0-30)V 1

2 Ammeter (0-50)A 1

2 Voltmeter 0-30)V 3

3 Diode 1N4001 2

4 Resistor 100K,1K 2,1

5 Capacitor 0.1f 1

6 CRO 1

7 Function Generator 1

8 Bread board 1

9 Wires

THEORY:

Circuit Diagram and Equations

The basic BJT common emitter takes the form shown:

KVL equation around B-E loop:

KVL equation around C-E loop:

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

61

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

Fig 10.1

Load-Line Analysis - Output Side

Returning to the circuit, observe that VCC and RC form a Thevenin equivalent, with

output variables IC and V CE. Thus we can plot this load line on the transistor output

characteristics, because neither VCC nor RC are time-varying, this load line is fixed

1. The collector-emitter operating point is given by the intersection of the load line and

the appropriate base current curve. When Vin = 0, IB = IBQ, and the quiescent

point is ICQ, VCEQ. At Vin max , IB = IB max , and the operating point is IC max, VCE

min. At Vin min, IB = IB min, and the operating point is IC min , VCE max .

2. If the total change in VCE is greater than total change in Vin, we have an amplifier

PROCEDURE:

1. Connect the circuit shown in Figure(3)

2. With vin= 0, vary the VBB to obtain the IC according to the Table (1). Then record

the values of the VCE.

3. Set the input voltage (vin) to the value that obtain the maximum swing on the output

voltage (vCE).when the operating point in the middle of the load line.

4. Vary the biasing voltage VBB to obtain the IC = (2, 5 and 8) mA. Then plot the output

voltage of each value.

CIRCUIT DIAGRAM:

Fig 10.2

Basic Transistor Amplifier Circuit

V E L T E C H D R . R R & D R S R T E C H N I C A L U N I V E R S I T Y

62

U3ECB04 SEMICONDUCTOR DEVICES AND CIRCUITS LAB III SEM ECE

TABULAR COLUMN:

IC(mA) 0 2 4 5 6 8 10

VCE(V)

MODEL GRAPH:

Fig 10.3

DC load line on the output characteristics

RESULT:

The V-I Characteristics and load line is drawn for the output of given BJT

Amplifier circuit.

Anda mungkin juga menyukai

- BJT Characteristics Lab Manual for Devices LabDokumen54 halamanBJT Characteristics Lab Manual for Devices LabreneeshczBelum ada peringkat

- List of ExperimentsDokumen214 halamanList of Experimentssenthil786Belum ada peringkat

- List of Experiments for Electronics Devices and Circuits LaboratoryDokumen213 halamanList of Experiments for Electronics Devices and Circuits Laboratoryrajesh0682Belum ada peringkat

- List of Experiments: Ee2207 Electronic Devices and Circuits Laboratory (Revised)Dokumen54 halamanList of Experiments: Ee2207 Electronic Devices and Circuits Laboratory (Revised)prakashkumarBelum ada peringkat

- Edc Lab ManualDokumen216 halamanEdc Lab ManualKalai YarasiBelum ada peringkat

- EC6361 Electronics LaboratoryDokumen97 halamanEC6361 Electronics LaboratoryBaskarBelum ada peringkat

- Electron Devices and Circuits LabDokumen217 halamanElectron Devices and Circuits Labprashant4235Belum ada peringkat

- s3 LabDokumen54 halamans3 LabVishal bijiBelum ada peringkat

- AE Lab Manual For EeeDokumen53 halamanAE Lab Manual For EeeSRUJANA VBelum ada peringkat

- EDC Lab ManualDokumen68 halamanEDC Lab ManualRocky AdityaBelum ada peringkat

- Electronic Devices & Circuits: Laboratory ManualDokumen61 halamanElectronic Devices & Circuits: Laboratory ManualFadila IsmailBelum ada peringkat

- 2-1 EDC Lab Manual Jntuk R20 - 201021Dokumen96 halaman2-1 EDC Lab Manual Jntuk R20 - 201021Durgasaiteja923 SunnyBelum ada peringkat

- EC 252 EDC Lab Manual PDFDokumen63 halamanEC 252 EDC Lab Manual PDFMurali KrishnaBelum ada peringkat

- Principle of Electronics EnggDokumen47 halamanPrinciple of Electronics EnggNilabh KumarBelum ada peringkat

- Electronics Device Circuit Lab SheetDokumen27 halamanElectronics Device Circuit Lab Sheetjimfinch512Belum ada peringkat

- PN Junction and Zener Diode CharacteristicsDokumen68 halamanPN Junction and Zener Diode CharacteristicsGoutham ShanBelum ada peringkat

- EDC Lab ManualDokumen63 halamanEDC Lab Manualranjitha gavniBelum ada peringkat

- Ecb 2182 Electronics and Microprocessors Lab Manual: S.Sadhish Prabhu, Ap/EceDokumen63 halamanEcb 2182 Electronics and Microprocessors Lab Manual: S.Sadhish Prabhu, Ap/EceNeoBelum ada peringkat

- Electronics Lab 2019Dokumen37 halamanElectronics Lab 2019Noor HussainBelum ada peringkat

- Edc Lab ManualDokumen70 halamanEdc Lab ManualreneeshczBelum ada peringkat

- EDC Lab Manual EeeDokumen106 halamanEDC Lab Manual EeeVishnu Kumar NadarBelum ada peringkat

- Electronic Devices and Circuits Lab NewDokumen86 halamanElectronic Devices and Circuits Lab NewleevasusanBelum ada peringkat

- PN Diode LabDokumen4 halamanPN Diode LabAbhishekh TiwariBelum ada peringkat

- Electronic Components Circuits: (Diode Characteristies - Rectifier - Clipper)Dokumen14 halamanElectronic Components Circuits: (Diode Characteristies - Rectifier - Clipper)em2200139Belum ada peringkat

- ElectronicsLab - Manual March2010Dokumen64 halamanElectronicsLab - Manual March2010pnarendrareddy.mscBelum ada peringkat

- EDC LAB ManualDokumen142 halamanEDC LAB Manualsangeethasiva67% (3)

- Electron DeviceDokumen112 halamanElectron DevicekrishnaBelum ada peringkat

- Ec3361 Edc Lab ManualDokumen50 halamanEc3361 Edc Lab ManualjerlinBelum ada peringkat

- 3rd Semester Lab 201Dokumen36 halaman3rd Semester Lab 201Noor HussainBelum ada peringkat

- FullDokumen67 halamanFullKalaiselvan PunniyamoorthyBelum ada peringkat

- 15EI251L E&ilap ManualDokumen56 halaman15EI251L E&ilap ManualAnushka TantiaBelum ada peringkat

- C-20 P e Practicle ComletetDokumen80 halamanC-20 P e Practicle Comletetamrutha cBelum ada peringkat

- SD Lab Manual 17.3.22Dokumen67 halamanSD Lab Manual 17.3.22ParthaSarathyBelum ada peringkat

- PE Lab 2 ReportDokumen15 halamanPE Lab 2 ReportMaryamBelum ada peringkat

- Device Exp 2 Student ManualDokumen4 halamanDevice Exp 2 Student Manualgg ezBelum ada peringkat

- EDC 3rd SemDokumen52 halamanEDC 3rd Semvijay kumar100% (1)

- Electric Circuits and Electron Device Lab ManualDokumen24 halamanElectric Circuits and Electron Device Lab ManualSuganthan Dboss100% (1)

- Experiment # 05: Diode and Transistor ObjectivesDokumen13 halamanExperiment # 05: Diode and Transistor ObjectivesKainat AshfaqBelum ada peringkat

- Automatic Power Factor Detection and CorDokumen53 halamanAutomatic Power Factor Detection and CorAshritaBelum ada peringkat

- Electronics Devices & Circuit Lab ManualDokumen53 halamanElectronics Devices & Circuit Lab Manualbiswajit7sarkar100% (1)

- Experiment-No 2Dokumen5 halamanExperiment-No 2carloBelum ada peringkat

- Electronic Unit 1Dokumen35 halamanElectronic Unit 1Sudheer ManepalliBelum ada peringkat

- Electronics & Microprocessor Lab ManualDokumen80 halamanElectronics & Microprocessor Lab ManualCyril Robinson Azariah John100% (5)

- Electronic Devices and Circuits Lab ManualDokumen67 halamanElectronic Devices and Circuits Lab ManualSudha Saravanan100% (3)

- Lab Manual Power ElectronicsDokumen39 halamanLab Manual Power ElectronicsZainab AnwarBelum ada peringkat

- EEE111 - Lab ManualDokumen28 halamanEEE111 - Lab ManualAnindita MishiBelum ada peringkat

- Eee 111 Lab Manual 2-8 (Latest)Dokumen32 halamanEee 111 Lab Manual 2-8 (Latest)Ismot Jahan MoniBelum ada peringkat

- 19EEE181 ReportDokumen14 halaman19EEE181 ReportabcdBelum ada peringkat

- Clippers and Clampers LabDokumen21 halamanClippers and Clampers LabballDISCOVERIES PHballDISCOVERIESBelum ada peringkat

- Microsoft Word - BM0110 Devices Lab Manual FinalDokumen54 halamanMicrosoft Word - BM0110 Devices Lab Manual FinalAnupma KumariBelum ada peringkat

- Lab Manual: Electrical Engineering Materials & Semiconductor Devices Lab (EC-317-F)Dokumen41 halamanLab Manual: Electrical Engineering Materials & Semiconductor Devices Lab (EC-317-F)Ilavarasan TamizhBelum ada peringkat

- DEVICE EXP 2 Student - 2Dokumen4 halamanDEVICE EXP 2 Student - 2Pablo ChanBelum ada peringkat

- Passive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2Dari EverandPassive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2Belum ada peringkat

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesDari EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesPenilaian: 4.5 dari 5 bintang4.5/5 (7)

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisDari EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisBelum ada peringkat

- Nonlinear Electronics 1: Nonlinear Dipoles, Harmonic Oscillators and Switching CircuitsDari EverandNonlinear Electronics 1: Nonlinear Dipoles, Harmonic Oscillators and Switching CircuitsBelum ada peringkat

- Building Automation by Prabhu Kumar SurarapuDokumen29 halamanBuilding Automation by Prabhu Kumar Surarapuprabhu4scribd100% (1)

- Analog Circuits or LIC and EDC Lab ManualDokumen162 halamanAnalog Circuits or LIC and EDC Lab Manualprabhu4scribdBelum ada peringkat

- Perl Introduction NotesDokumen30 halamanPerl Introduction NotessumitttyBelum ada peringkat

- Eca Unit 1 Part 1 LectureDokumen36 halamanEca Unit 1 Part 1 Lectureprabhu4scribdBelum ada peringkat

- 1156EC409 Perl Scripting-SyllabusDokumen3 halaman1156EC409 Perl Scripting-Syllabusprabhu4scribdBelum ada peringkat

- ElectricDokumen12 halamanElectricprabhu4scribdBelum ada peringkat

- AnalogDokumen12 halamanAnalogprabhu4scribdBelum ada peringkat

- Haphazardly Sampled Data Processing Algorithm Using Lomb Welch PeriodogramDokumen10 halamanHaphazardly Sampled Data Processing Algorithm Using Lomb Welch Periodogramprabhu4scribdBelum ada peringkat

- AnalogIntegratedCircuts LAB MANUAL by Prabhu Kumar SurarapuDokumen80 halamanAnalogIntegratedCircuts LAB MANUAL by Prabhu Kumar Surarapuprabhu4scribdBelum ada peringkat

- Analof Electronics UNIT 1 by Prabhu Kumar SurarapuDokumen25 halamanAnalof Electronics UNIT 1 by Prabhu Kumar Surarapuprabhu4scribdBelum ada peringkat

- Analog Integrated Circuits Lab ManualDokumen133 halamanAnalog Integrated Circuits Lab Manualprabhu4scribdBelum ada peringkat

- LINEAR INTEGRATED CIRCUIT LAB MANUAL by PRABHU PDFDokumen76 halamanLINEAR INTEGRATED CIRCUIT LAB MANUAL by PRABHU PDFprabhu4scribd100% (5)

- Topswitch: Designing Multiple Output Flyback Power Supplies WithDokumen24 halamanTopswitch: Designing Multiple Output Flyback Power Supplies WithHải TrầnBelum ada peringkat

- 1 N 5237 BDokumen8 halaman1 N 5237 BAndres CamachoiBelum ada peringkat

- F A N U C 5t 5mDokumen5 halamanF A N U C 5t 5mmradivojeBelum ada peringkat

- CHAP 3 - Zener DiodeDokumen65 halamanCHAP 3 - Zener DiodeAnees Ahmad100% (1)

- 19.5 Discrete Transistor Voltage RegulationDokumen8 halaman19.5 Discrete Transistor Voltage RegulationBayu Haris Merdiko HersuwariBelum ada peringkat

- Deogiri College Aurangabad: Marathwada Shikshan Prasarak Mandal'sDokumen5 halamanDeogiri College Aurangabad: Marathwada Shikshan Prasarak Mandal'sM SuBelum ada peringkat

- Xam Idea Physics 12thDokumen773 halamanXam Idea Physics 12thAshish GuptaBelum ada peringkat

- List of Edc ManualDokumen88 halamanList of Edc ManualPatricia Grace PerezBelum ada peringkat

- HDD TutorialDokumen8 halamanHDD Tutorialeem1kvBelum ada peringkat

- Edc MCQ Zener DiodeDokumen4 halamanEdc MCQ Zener DiodeUmaBelum ada peringkat

- Transistor-Zener Diode Regulator CircuitsDokumen7 halamanTransistor-Zener Diode Regulator Circuitsmohamed lamine elbiskriBelum ada peringkat

- Basic Electronics (BBEE103/BBEE203) - Question Bank - VTUDokumen11 halamanBasic Electronics (BBEE103/BBEE203) - Question Bank - VTUShrishail Bhat100% (1)

- EC 2155 - Circuits and Devices Lab Manual Cum ObservationDokumen108 halamanEC 2155 - Circuits and Devices Lab Manual Cum ObservationAnonymous uspYoqEBelum ada peringkat

- Solid State Voltage RegulatorDokumen9 halamanSolid State Voltage RegulatorgrcatuBelum ada peringkat

- Car Ignition With IgbtsDokumen9 halamanCar Ignition With IgbtsrobertoBelum ada peringkat

- Presentation On Analog ElectronicsDokumen334 halamanPresentation On Analog ElectronicssamuelBelum ada peringkat

- Clippers and ClampersDokumen8 halamanClippers and Clamperspuneeth kumarBelum ada peringkat

- UNIT-II 2 MarksDokumen39 halamanUNIT-II 2 MarksKumar MadhuBelum ada peringkat

- Duoyi DY294 Operating InstructionsDokumen5 halamanDuoyi DY294 Operating Instructionswertingo100% (5)

- Zener Diode Circuit Working and ApplicationsDokumen17 halamanZener Diode Circuit Working and ApplicationsSURESH SURAGANIBelum ada peringkat

- Diode types explained: LED, laser, avalanche, Zener, Schottky, photodiode and P-N junctionDokumen1 halamanDiode types explained: LED, laser, avalanche, Zener, Schottky, photodiode and P-N junctionMarshallBelum ada peringkat