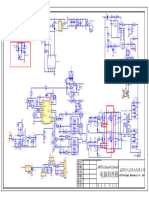

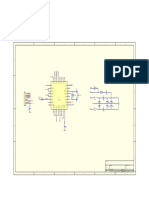

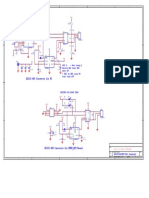

Sequencer Hardware Schematics, Rev. C

Diunggah oleh

paulphamHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Sequencer Hardware Schematics, Rev. C

Diunggah oleh

paulphamHak Cipta:

Format Tersedia

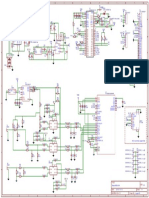

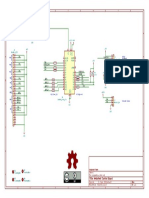

1 2 3 4 5 6

C224

U19A U19B Place twisted pair Tx and Rx termination close to DP83843 U19F

DP83843 DP83843 DP83843

MII Interface PMD Interface 10p Power and Ground Pins

R69 R70 J9

49.9 49.9 +5V

L8

MDC 35 74 C225 1 72 54

MDC TPTD+ CD_VDD0 CPTW_DVDD +5V

2 FB

+5V R108 39 34 73 3 C231 C235

MDIO TPTD- 10p L9

D C228 4 0.1u 71 53 0.0033u D

R67 CD_GND0 CPTW_DVSS

67 5 +5V FB

+5V TPRD+

C8 1.5k 6 76 TW_AVDD

10p 7 CD_VDD1 L10

0.1u 65 68

24

TPRD- R71 49.9 R72 49.9 TW_AVDD +5V

U20 8 JP6 C264 FB

SN74CBT3384 66 0.1u 75 64 C236 C237

VCM_CAP 1 CD_GND1 TW_AGND 0.0033u

3 2 0.1u

VCC

1A1 1B1 R103 39 RJ45-SI 2 L11

RXD0 4 5 18 C226 C227 10 70

1A2 1B2 RX_CLK PCS_VDD SUB_GND1

RXD1 7 6 0.1u 0.0033u HEADER 2 FB

1A3 1B3 RA15 TW_AVDD

RXD2 8 9 12 43 C265

1A4 1B4 RXD[3] FXTD+/AUITD+ L12

RXD3 11 10 1 8 0.1u 11 52

1A5 1B5 PCS_VSS CP_AVDD +5V

1 2 7 13 44 FB

1OE RXD[2] FXTD-/AUITD- R76 R77 R78 R79 R80 R81

3 6 J11 +5V C238 C239

RX_CLK 14 15 4 5 14 49 82 82 130 82 91 91 6 51 0.001u 0.1u

2A1 2B1 RXD[1] FXRD-/AUIRD- IO_VDD1 CP_AGND

RX_DV 17 16 9

2A2 2B2 Veet

MDIO 18 19 39 15 50 C234

2A3 2B3 RXD[0] FXRD+/AUIRD+

TX_CLK 21 20 8 0.001u 7 79

2A4 2B4 R68 TD+ IO_VSS1 TR_AVDD +5V

22 23 23 47

GND

2A5 2B5 +5V RX_EN FXSD-/CD-

13 10k 7 16 C240

2OE TD- IO_VDD2

NC 19 48 C2290.1u 80 0.1u

RX_ER FXSD+/CD+ TR_AGND

6 C266

R125 Vcct

20 0.001u 17

12

RX_DV IO_VSS2

39 5 46

Vccr AUIFX_VDD +5V

26

C R109 IO_VDD3 C

33 78 NC C2300.0033u 4 C241

TX_CLK TXAR100 SD

C267 45 0.1u

39 AUIFX_GND

FPGA inputs TXD3 28 60 R74 69.8k 3 0.001u 27

TXD[3] TWREF RD- IO_VSS3

RXD[0-3] - Receive Data

RX_DV - Receive Data Valid TXD2 29 61 R75 4.87k 2 36 57

TXD[2] BGREF RD+ IO_VDD5 ATP_GND

FPGA outputs TXD1 30 1 C268

TXD[1] R82 R83 R84 R85 R86 R87 Veer

MDC - Management Data Clock 0.001u 37 77

130 130 360 130 115 115 IO_VSS5 SUB_GND2

TX_CLK - Transmit Clock TXD0 31 32

TXD[0] Optek OPF5101 IO_VSS4

TXD[0-3] - Transmit Data C233

TX_EN - Transmit Enable TX_EN 25 JP7 2

TX_EN NC

R102 10k 24 1 0.1u

FPGA bidirectional 55

TX_ER 2 NC

MDIO - Management Data I/O

Place Tx termination near Optek transceiver HEADER 2 C232 56

NC

FPGA clock input Place Rx and CD termination near DP83843

RX_CLK - Receive Clock 58

10u NC

59

NC

JP3

U19C 62

3 +5V NC

DP83843

2

+5V Clock Interface & Reset

1

B JP8 X2 B

HEADER 3

2

1 3 9 U19D U19E

1 OE Output X1

JP4 DP83843 DP83843

HEADER 2 R5 NC 8 Device Configuration Interface LED Interface/PHY Address Interface

10k L13 X2 3 +5V

2 4

GND Vcc FB +5V 2

1 R97 10k

C243 1 4 42

0.0033u RESET AN0 LED_COL/PHYAD[0] +5V

CTS CB3 25.00000 MHz HEADER 3

DigiKey CTX276CT 3 41 R98 10k

AN1 LED_TX/PHYAD[1]

40 R99 10k

R73 LED_RX/PHYAD[2]

63

THIN R10010k

10k 39

LED_LINK/PHYAD[3]

NC 22

SYMBOL R10110k

U21 38

LED_FDPLO/PHYAD[4]

Ethernet_clk_enable 2 6 NC 69

RESIN RST SERIAL10

7 5 JP5 5 NC

+5V SENSE RESET SPEED10 D13 D14 D15 D16 D17

21

2 COL LED LED LED LED LED

8 4

VCC GND 1

3 1 22

CT REF R89 R88 R91 CRS

10k HEADER 2

C242 TL7705A C244 10k 10k

2.2u 0.1u

A 100base-FX: JP3=23 JP4=open JP5=closed A

100base-TX: JP3=23 JP4=12 JP5=open R92 R93 R94 R95 R96

10baseT JP3=12 JP4=12 JP5=open 1k 1k 1k 1k 1k Title

Size Number Revision

+5V

B

Date: 6-Apr-2007 Sheet of

File: C:\ppham\sequencer\sequencer2.ddb Drawn By:

1 2 3 4 5 6

Anda mungkin juga menyukai

- The Fusion Marketing Bible: Fuse Traditional Media, Social Media, & Digital Media to Maximize MarketingDari EverandThe Fusion Marketing Bible: Fuse Traditional Media, Social Media, & Digital Media to Maximize MarketingPenilaian: 5 dari 5 bintang5/5 (2)

- Bluepill ReforgedDokumen1 halamanBluepill ReforgedDaniel BaronBelum ada peringkat

- Build-In Leds Usb Type C To Usb 2.0 Usb To Serial (VCP) Lse Oscilator Microcontroller CoreDokumen1 halamanBuild-In Leds Usb Type C To Usb 2.0 Usb To Serial (VCP) Lse Oscilator Microcontroller CorelekobhBelum ada peringkat

- PS1501 Power AmpDokumen1 halamanPS1501 Power AmpAdriana DundesBelum ada peringkat

- Hardware GT2560 RevA+Dokumen2 halamanHardware GT2560 RevA+Jonatan PisuBelum ada peringkat

- UPD77C25 Programmer SchematicDokumen3 halamanUPD77C25 Programmer SchematicAli Gachkar0% (1)

- All ProDokumen1 halamanAll ProTouati Ali MHBelum ada peringkat

- CH1 Power Amplifier: S500 Schematic DocumentDokumen3 halamanCH1 Power Amplifier: S500 Schematic DocumentAtthepztt TtheaBelum ada peringkat

- Global RF 회로도 (B type) - 02Dokumen4 halamanGlobal RF 회로도 (B type) - 02김진오Belum ada peringkat

- Paso A PasaDokumen1 halamanPaso A PasaAlejandro Teruggi100% (1)

- Zed BULL SchematicDokumen1 halamanZed BULL SchematicAugustoferreira Ferreira100% (3)

- Schematic NanoVNA-H4 2Dokumen1 halamanSchematic NanoVNA-H4 2Dadang100% (2)

- Modulator PCBDokumen5 halamanModulator PCBJoel Allbert Pimentel100% (1)

- Noblex DJX340BT - 73690Dokumen7 halamanNoblex DJX340BT - 73690Juan Perondini100% (1)

- Lionel 6-12885 40watt Speed Control SchematicDokumen1 halamanLionel 6-12885 40watt Speed Control SchematicEnrique FemeniaBelum ada peringkat

- DIY Mini Inverter 11-21V 150WDokumen1 halamanDIY Mini Inverter 11-21V 150WindustriacncBelum ada peringkat

- mp123 Fonte de Alimentação PDFDokumen1 halamanmp123 Fonte de Alimentação PDFSergio Daniel BarretoBelum ada peringkat

- OCM500 SCHDokumen1 halamanOCM500 SCHNosdan LemosBelum ada peringkat

- BLDC Driver SCHDokumen1 halamanBLDC Driver SCHadi joko100% (1)

- Smart Response XEDokumen2 halamanSmart Response XEmarekBelum ada peringkat

- XBee USB Adapter SchematicDokumen1 halamanXBee USB Adapter SchematicRody Garay100% (2)

- CaptureTutorial SchematicSmartPDFDokumen1 halamanCaptureTutorial SchematicSmartPDFAaron HernandezBelum ada peringkat

- GT2560 V3.0 SCHDokumen2 halamanGT2560 V3.0 SCHleandrobuenoi75% (4)

- 8051 Project BoardDokumen1 halaman8051 Project Boardsagar21pBelum ada peringkat

- KNQ7 SchematicDokumen1 halamanKNQ7 SchematicFariborz SadeghivafaBelum ada peringkat

- Power Supply Skyworth TV5006-ZC02-02 (A)Dokumen2 halamanPower Supply Skyworth TV5006-ZC02-02 (A)Андрей ШипетунBelum ada peringkat

- CVMV26L-G Schematic DiagramDokumen6 halamanCVMV26L-G Schematic DiagrambelajartvkuBelum ada peringkat

- Schematic - STM32F401RB RET6 Development Board - 2020-05-11 - 17-18-56Dokumen1 halamanSchematic - STM32F401RB RET6 Development Board - 2020-05-11 - 17-18-56Fernando GómezBelum ada peringkat

- Inverter TV Philco Ph32M (Cmo T871029.14) : T1 T8 N-Driver 1Dokumen1 halamanInverter TV Philco Ph32M (Cmo T871029.14) : T1 T8 N-Driver 1VictorManuelBernalBlancoBelum ada peringkat

- Inverter+Philco+T871029 14Dokumen1 halamanInverter+Philco+T871029 14peres.gabriel.gabrielBelum ada peringkat

- Respirator ControlDokumen1 halamanRespirator Controlbala_paiBelum ada peringkat

- PDF Created With Fineprint Pdffactory Trial Version: 5 4 2 1 Tda2030ADokumen1 halamanPDF Created With Fineprint Pdffactory Trial Version: 5 4 2 1 Tda2030AKamol PlakulBelum ada peringkat

- Pmode2 Pmode1 Pmode0Dokumen1 halamanPmode2 Pmode1 Pmode0李明宗100% (1)

- Power In: Samyung Enc Co.,LtdDokumen1 halamanPower In: Samyung Enc Co.,LtdjasonelectronicsphilBelum ada peringkat

- PA500 SCHDokumen3 halamanPA500 SCHassistenzadavidoffstoreBelum ada peringkat

- Schemetic Smart MeterDokumen3 halamanSchemetic Smart Meteranmol24soeBelum ada peringkat

- Elecraft Kpa500 SCHDokumen17 halamanElecraft Kpa500 SCHBlagoja GjakovskiBelum ada peringkat

- UV Exposure Timer - Service ManualDokumen15 halamanUV Exposure Timer - Service ManualLaurentiu IacobBelum ada peringkat

- Aux Power Supply Circuit Diagram SYSTEM 8000 Aux Power Supply Circuit Diagram SYSTEM 8000 Aux Power Supply Circuit Diagram SYSTEM 8000Dokumen1 halamanAux Power Supply Circuit Diagram SYSTEM 8000 Aux Power Supply Circuit Diagram SYSTEM 8000 Aux Power Supply Circuit Diagram SYSTEM 8000Dea NafitasariBelum ada peringkat

- Schematic - LMR SDR V 1.5.A - 2021-11-23Dokumen3 halamanSchematic - LMR SDR V 1.5.A - 2021-11-23pajrulnetBelum ada peringkat

- Flow Chart of Troubleshooting: 9-1. Logic SectionDokumen81 halamanFlow Chart of Troubleshooting: 9-1. Logic SectionRiza VirsadaBelum ada peringkat

- MCU BaseBoardDokumen4 halamanMCU BaseBoardAbdo BendaryBelum ada peringkat

- WPL5 (Completo)Dokumen5 halamanWPL5 (Completo)Jorge Garcia100% (1)

- BT2 SCHDokumen1 halamanBT2 SCHEmilia Szuszko100% (1)

- Keypad If LEW - SCHDokumen3 halamanKeypad If LEW - SCHMohendra PatiBelum ada peringkat

- Fonte WaldirDokumen1 halamanFonte WaldirRamon H SouzaBelum ada peringkat

- Bestec - Atx 300 12es PDFDokumen1 halamanBestec - Atx 300 12es PDFjuanlampreaBelum ada peringkat

- Schematic GC-PW PSUDokumen4 halamanSchematic GC-PW PSUDimitrisBelum ada peringkat

- Esquema Eletrico Isl-165 - Awt-S118-A4-S124-A0Dokumen1 halamanEsquema Eletrico Isl-165 - Awt-S118-A4-S124-A0Cristiano NunesBelum ada peringkat

- Booster Sardinator 1Dokumen1 halamanBooster Sardinator 1guitarrielBelum ada peringkat

- MFRC522 AntDokumen1 halamanMFRC522 Antolivier CHOUILLOUBelum ada peringkat

- مخطط شاحن شور30أمبيرDokumen1 halamanمخطط شاحن شور30أمبيرابراهيم حجار100% (1)

- Hisense+rsag7 820 4737Dokumen2 halamanHisense+rsag7 820 4737Diego CabreraBelum ada peringkat

- Rsag7 820 4737Dokumen2 halamanRsag7 820 4737Miguelina RossiBelum ada peringkat

- Hisense Rsag7.820.4737 Psu SCHDokumen2 halamanHisense Rsag7.820.4737 Psu SCHserrano.flia.coBelum ada peringkat

- Rsag78204737 Roh Fuente LCD DiagramaDokumen2 halamanRsag78204737 Roh Fuente LCD DiagramaNatal2i2100% (1)

- Rsag7 820 4737 PDFDokumen2 halamanRsag7 820 4737 PDFclayclayclayBelum ada peringkat

- 100V-240V Woshine Machine Motor Driver-DiagrameDokumen1 halaman100V-240V Woshine Machine Motor Driver-DiagrameWasantha MunasinghaBelum ada peringkat

- Vest3000mkii TurntableDokumen16 halamanVest3000mkii TurntableElkin BabiloniaBelum ada peringkat

- 344 Mach Chuyen Doi Rs232 To Rs485 Cho PC, Board (Nguyen Gia Minh Thao)Dokumen1 halaman344 Mach Chuyen Doi Rs232 To Rs485 Cho PC, Board (Nguyen Gia Minh Thao)Quang Linh Lê100% (1)

- Sequencer Hardware Schematics, Rev. CDokumen1 halamanSequencer Hardware Schematics, Rev. CpaulphamBelum ada peringkat

- Sequencer Hardware Schematics, Rev. CDokumen1 halamanSequencer Hardware Schematics, Rev. CpaulphamBelum ada peringkat

- Sequencer Hardware Schematics, Rev. CDokumen1 halamanSequencer Hardware Schematics, Rev. Cpaulpham100% (1)

- Sequencer Hardware Schematics, Rev. CDokumen1 halamanSequencer Hardware Schematics, Rev. CpaulphamBelum ada peringkat

- Sequencer Hardware Schematics, Rev. CDokumen1 halamanSequencer Hardware Schematics, Rev. CpaulphamBelum ada peringkat

- Sequencer Hardware Schematics, Rev. CDokumen1 halamanSequencer Hardware Schematics, Rev. CpaulphamBelum ada peringkat

- ConnectorsDokumen3 halamanConnectorsmatrixworld20Belum ada peringkat

- Leading Architect and Enabler in Digital SocietyDokumen31 halamanLeading Architect and Enabler in Digital SocietyRifki NugrahaBelum ada peringkat

- Generic TWS600S Service ManualDokumen113 halamanGeneric TWS600S Service ManualWise So100% (2)

- Performance Analysis of Cooperative Communication For Wireless NetworksDokumen164 halamanPerformance Analysis of Cooperative Communication For Wireless NetworksIhtesham JadoonBelum ada peringkat

- Asme b16.5Dokumen246 halamanAsme b16.5hugo_siqueira_11Belum ada peringkat

- Fundamentals of Petroleum Engineering BookDokumen10 halamanFundamentals of Petroleum Engineering BookRizwan FaridBelum ada peringkat

- Fce Speaking TipsDokumen28 halamanFce Speaking TipsAnonymous fLpGQVv100% (2)

- Document 1Dokumen14 halamanDocument 1bismarckandresBelum ada peringkat

- Power GenerationDokumen34 halamanPower GenerationTaufiq AkbarBelum ada peringkat

- Japan Servo CatalogDokumen39 halamanJapan Servo CatalogKofaKing100% (1)

- Discussion SamplesDokumen5 halamanDiscussion SamplesvusalaBelum ada peringkat

- HTTP StreamsDokumen8 halamanHTTP StreamsMarcelo Castro MartinoBelum ada peringkat

- (The M.I.T. Introductory Physics Series) A. P French - Vibrations and Waves-Norton (1971)Dokumen9 halaman(The M.I.T. Introductory Physics Series) A. P French - Vibrations and Waves-Norton (1971)Simran GiriBelum ada peringkat

- 08 - Relief System Adequacy - A Step Towards SAFER Operations - Deepak - IngeneroDokumen40 halaman08 - Relief System Adequacy - A Step Towards SAFER Operations - Deepak - IngeneroCalBelum ada peringkat

- Manual ArchicadDokumen67 halamanManual ArchicadkhajaimadBelum ada peringkat

- Time Impact Analysis by BrewerConsultingDokumen3 halamanTime Impact Analysis by BrewerConsultingAAKBelum ada peringkat

- KN3906Dokumen3 halamanKN3906ingucvBelum ada peringkat

- Civil Engineering Interview QuestionsDokumen12 halamanCivil Engineering Interview Questionsjadgug100% (1)

- ABB REL5xx RIOConverterDokumen10 halamanABB REL5xx RIOConverterzinab90100% (1)

- Fireplace ManualDokumen40 halamanFireplace Manualresistancebeta6Belum ada peringkat

- Bou-Llusar Et Al 2009 EFQM Excellence ModelDokumen22 halamanBou-Llusar Et Al 2009 EFQM Excellence Modelfastford14Belum ada peringkat

- Factors Affecting Beam StrengthDokumen2 halamanFactors Affecting Beam StrengthkalpanaadhiBelum ada peringkat

- Performance of Gesture Controlled DroneDokumen11 halamanPerformance of Gesture Controlled DroneKrishna SivaBelum ada peringkat

- VDA Volume 6.3 2016 Chapter 9.1 Process Audit Action PlanDokumen8 halamanVDA Volume 6.3 2016 Chapter 9.1 Process Audit Action PlanYo GoldBelum ada peringkat

- 3 Africacert Project PublicDokumen15 halaman3 Africacert Project PublicLaïcana CoulibalyBelum ada peringkat

- Assessing The Impact of Premier Information Systems Research OverDokumen20 halamanAssessing The Impact of Premier Information Systems Research OvergasibuteaBelum ada peringkat

- Comparative Analysis of Wear Rate of Coated Hss Tool and Non-Coated Hss Tool by Using Cr-Zn-NiDokumen21 halamanComparative Analysis of Wear Rate of Coated Hss Tool and Non-Coated Hss Tool by Using Cr-Zn-Nithai avvaiBelum ada peringkat

- 29-Horizontal Subsea Xmas Tree enDokumen2 halaman29-Horizontal Subsea Xmas Tree encarthik_rajaBelum ada peringkat

- M.Tech. 2nd (Non CBCS) May 2018 - 9 - 5 - 18Dokumen2 halamanM.Tech. 2nd (Non CBCS) May 2018 - 9 - 5 - 18doob marroBelum ada peringkat

- Ti 59 - A Note On Battery CorrosionDokumen3 halamanTi 59 - A Note On Battery CorrosionLeon ZieglerBelum ada peringkat