SOC Design Verif White Paper

Diunggah oleh

Srinivas CherukuHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

SOC Design Verif White Paper

Diunggah oleh

Srinivas CherukuHak Cipta:

Format Tersedia

intelop

SoC/ASIC/SoC-FPGA/S-ASIC

Design and Verification

Methodology

Intelop Corporation

4800 Great America Pkwy.

Ste-201

Santa Clara, CA. 95054

Ph: 408-496-0333, Fax: 408-496-0444

www.intelop.com

Courtesy of Cadence design

intelop

Challenges in Embedded Systems Design

intelop

Critical Issues

intelop

Verification Effort size

intelop

Overview of Verification Methodologies

intelop

Software Simulation

intelop

Software Simulation

intelop

Hardware Acceleration

intelop

Emulation

intelop

Overview of Verification Methodologies

Formal Verification

intelop

Formal Verification : equivalence Check

intelop

Formal Verification : equivalence Check

intelop

Theorem Proving

intelop

Formal Verification : Model Check

intelop

Formal Verification : Model Checking

intelop

Formal Verification : Challenges

intelop

Semi-Formal Verification : Assertion

intelop

Semi-Formal Verification : Coverage

intelop

Semi-Formal Verification : Coverage

intelop

Semi-Formal Verification : Coverage

intelop

Semi-Formal Verification

intelop

Design Complexity

intelop

Language Heritage for SoC Design

intelop

SystemC in SoC Design

intelop

SystemC in SoC Design

intelop

Abstraction Levels of SystemC

intelop

Vera (Synopsys)

intelop

Vera (Synopsys)

intelop

System Verilog

intelop

System Verilog

intelop

Key Components of System Verilog

intelop

System Design Language Summary

intelop

SoC Verification

intelop

Embedded Processor Cores in SoC

intelop

Models of Embedded Processor

intelop

Models of Embedded Processor

intelop

Models of Embedded Processor

intelop

Verification with Embedded Processor

intelop

Verification with Embedded Processor

intelop

Simultaneous SoC design Flow

intelop

Tool utilized in HW-SW Co-Verification

intelop

Tool utilized in Co-Simulation

intelop

Conclusion

intelop

Conclusion

Anda mungkin juga menyukai

- Manasa Hanakere Krishnappa - ResumeDokumen3 halamanManasa Hanakere Krishnappa - ResumesanjuBelum ada peringkat

- Role Role CategoryDokumen64 halamanRole Role CategoryjanakipvBelum ada peringkat

- Intel FPGA P-Tile Avalon Streaming IP For PCI Express Design Example User GuideDokumen22 halamanIntel FPGA P-Tile Avalon Streaming IP For PCI Express Design Example User GuidemanchuricoBelum ada peringkat

- Introduction To SOCDokumen50 halamanIntroduction To SOCPraveen HalladmaniBelum ada peringkat

- Design FlowDokumen4 halamanDesign Flowdontmatter9x2553Belum ada peringkat

- IntelDokumen3 halamanIntelvenkimvs2Belum ada peringkat

- Ravi Sharma ResDokumen2 halamanRavi Sharma ResSunny ModiBelum ada peringkat

- DSV Vip CatalogDokumen4 halamanDSV Vip CatalogSamBelum ada peringkat

- Math WorksDokumen53 halamanMath WorksJ Jesús Villanueva GarcíaBelum ada peringkat

- Virya Infotech - Design ProcessDokumen18 halamanVirya Infotech - Design ProcessGirish MohantyBelum ada peringkat

- Course Module ASIC VerificationDokumen6 halamanCourse Module ASIC VerificationSamBelum ada peringkat

- Yee-Wen Leung 2732 Buck Hill Drive Plano, TX 75025Dokumen3 halamanYee-Wen Leung 2732 Buck Hill Drive Plano, TX 75025kiran2710Belum ada peringkat

- Design Flow VlsiDokumen42 halamanDesign Flow VlsiRahul ShandilyaBelum ada peringkat

- FPGA Senior Engineer Digital in Denver CO Resume Michael SurgeonDokumen2 halamanFPGA Senior Engineer Digital in Denver CO Resume Michael SurgeonMichael SurgeonBelum ada peringkat

- Pavitra Jinaga ResumeDokumen3 halamanPavitra Jinaga Resumeastitva08Belum ada peringkat

- i7-3612QM (2 1ghz)Dokumen3 halamani7-3612QM (2 1ghz)Sugar PourBelum ada peringkat

- How To Configure An Intel Agilex DesignDokumen3 halamanHow To Configure An Intel Agilex DesignjackBelum ada peringkat

- Data Sheet: Intel 8051 Native Code Generator and Runtime SystemDokumen2 halamanData Sheet: Intel 8051 Native Code Generator and Runtime SystemMuh AminBelum ada peringkat

- Intel 945 FeaturesDokumen2 halamanIntel 945 FeaturesgsnphaniBelum ada peringkat

- Soc Design Flow & ToolsDokumen34 halamanSoc Design Flow & ToolsradhasudhaBelum ada peringkat

- SmartPlant PID Engineering Webinar 02-28-2012Dokumen30 halamanSmartPlant PID Engineering Webinar 02-28-2012Saurabh Kumar YadavBelum ada peringkat

- Pentium Celeron N Series Datasheet Vol 1 PDFDokumen248 halamanPentium Celeron N Series Datasheet Vol 1 PDFTri Sutrisno100% (2)

- Analog Design Engineer RoleDokumen2 halamanAnalog Design Engineer RoleJeethendra PathakBelum ada peringkat

- Punit Resume WorkDokumen3 halamanPunit Resume Workapi-321948941Belum ada peringkat

- DivX FailureDokumen92 halamanDivX FailureShashidhar BhandaryBelum ada peringkat

- La Verificacion de Sistemas DigitalesDokumen19 halamanLa Verificacion de Sistemas DigitalesinghectorrBelum ada peringkat

- Aharen San - Mastering FPGA Embedded Systems A Case Study Approach To Designing and Implementing FPGA-Based Embedded Systems With TFT LCDs (Z-Library)Dokumen263 halamanAharen San - Mastering FPGA Embedded Systems A Case Study Approach To Designing and Implementing FPGA-Based Embedded Systems With TFT LCDs (Z-Library)r.dmirandaBelum ada peringkat

- Padmaja ResumeDokumen4 halamanPadmaja Resumepadmajakavuri2000Belum ada peringkat

- ESD -DAY 1-PortalDokumen35 halamanESD -DAY 1-PortaldraqulaincBelum ada peringkat

- ESD - DAY 1-EnhancedDokumen41 halamanESD - DAY 1-EnhancedINTTICBelum ada peringkat

- ARK - Intel® Core™ I3-370m Processor (3M Cache, 2Dokumen3 halamanARK - Intel® Core™ I3-370m Processor (3M Cache, 2Delzi Guindra AdriBelum ada peringkat

- Principal Electrical Hardware Engineer in Los Angeles CA Resume Robel BorjaDokumen2 halamanPrincipal Electrical Hardware Engineer in Los Angeles CA Resume Robel BorjaRobelBorjaBelum ada peringkat

- Intel - by BongDokumen4 halamanIntel - by Bongrizaflores51Belum ada peringkat

- Chassis NI Datasheet CRIO 9111Dokumen6 halamanChassis NI Datasheet CRIO 9111Anonymous 28Hm53CYBelum ada peringkat

- Vietnam IC Design Industry & LSI OverviewDokumen33 halamanVietnam IC Design Industry & LSI OverviewMạc HạBelum ada peringkat

- UntitledDokumen77 halamanUntitledpbento_24Belum ada peringkat

- DPDK Packet Processing Ia Overview PresentationDokumen35 halamanDPDK Packet Processing Ia Overview PresentationHassan WiloBelum ada peringkat

- Iad CR BookDokumen588 halamanIad CR BookSteffen MuellerBelum ada peringkat

- Kiran ResumeDokumen3 halamanKiran ResumeHemakiran kolliBelum ada peringkat

- What Is Altera Quartus Used ForDokumen9 halamanWhat Is Altera Quartus Used ForjackBelum ada peringkat

- HPC@Intel: Platforms and Technology CCGSC September 10, 2006Dokumen29 halamanHPC@Intel: Platforms and Technology CCGSC September 10, 2006Ahmet BabayevBelum ada peringkat

- Sample Design Verification EngineerDokumen7 halamanSample Design Verification Engineervishnu microarkBelum ada peringkat

- Design Flow2 PDFDokumen21 halamanDesign Flow2 PDFSandeep BoyinaBelum ada peringkat

- Emulating Large Complex SOC Devices in A XilinxDokumen20 halamanEmulating Large Complex SOC Devices in A XilinxseemabBelum ada peringkat

- Systems Security Developer Opportunity at IntelDokumen6 halamanSystems Security Developer Opportunity at IntelkalamkkBelum ada peringkat

- Senior Design Verification Engineer in Phoenix AZ Resume Lloyd HeathDokumen3 halamanSenior Design Verification Engineer in Phoenix AZ Resume Lloyd HeathLloyd HeathBelum ada peringkat

- Software Engineer - Networking Applications at Intel Corporation - Stack OverflowDokumen6 halamanSoftware Engineer - Networking Applications at Intel Corporation - Stack OverflowkalamkkBelum ada peringkat

- Task List TestingDokumen18 halamanTask List TestingGelivi GaneshBelum ada peringkat

- Altera Enixs Course PDFDokumen3 halamanAltera Enixs Course PDFLe LamBelum ada peringkat

- Shubham Mittal CVDokumen2 halamanShubham Mittal CVshantibhushan.saleBelum ada peringkat

- Performance Xeon E3 1200 HD Graphics p4000 GuideDokumen4 halamanPerformance Xeon E3 1200 HD Graphics p4000 GuideSourav SahaBelum ada peringkat

- Design Verification Engineer RTL in Austin TX Resume Sumaira KhowajaDokumen3 halamanDesign Verification Engineer RTL in Austin TX Resume Sumaira KhowajaSumairaKhowaja4Belum ada peringkat

- De Automotive ElectronicsDokumen12 halamanDe Automotive ElectronicsnitinlivingBelum ada peringkat

- RTL Design Verification Engineer in Austin TX Resume Sumaira KhowajaDokumen3 halamanRTL Design Verification Engineer in Austin TX Resume Sumaira KhowajaSumairaKhowaja3Belum ada peringkat

- Engineer Design Verification in Austin TX Resume Sumaira KhowajaDokumen3 halamanEngineer Design Verification in Austin TX Resume Sumaira KhowajaSumairaKhowaja2Belum ada peringkat

- Short Course On Phase-Locked Loops and Their Applications Day 3, PM Lecture Behavioral Simulation ExercisesDokumen16 halamanShort Course On Phase-Locked Loops and Their Applications Day 3, PM Lecture Behavioral Simulation ExercisesAndrea FasatoBelum ada peringkat

- D915gav Ag d915pgn Sy MLP PDFDokumen10 halamanD915gav Ag d915pgn Sy MLP PDFRudyC FloresBelum ada peringkat

- Simplifying The Complexities of Multicore Processors With COTS Single Board Computer SolutionsDokumen30 halamanSimplifying The Complexities of Multicore Processors With COTS Single Board Computer SolutionsLúcio TrajanoBelum ada peringkat

- Programming Microcontrollers with Python: Experience the Power of Embedded PythonDari EverandProgramming Microcontrollers with Python: Experience the Power of Embedded PythonBelum ada peringkat

- Digital System Design VHDL StopwatchDokumen25 halamanDigital System Design VHDL StopwatchSrinivas CherukuBelum ada peringkat

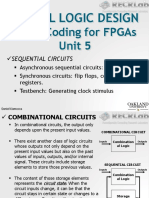

- Digital Logic Design: VHDL Coding For Fpgas Unit 6Dokumen15 halamanDigital Logic Design: VHDL Coding For Fpgas Unit 6Srinivas CherukuBelum ada peringkat

- DIGITAL LOGIC DESIGN VHDL CODING FOR FPGAS SEQUENTIAL CIRCUITSDokumen34 halamanDIGITAL LOGIC DESIGN VHDL CODING FOR FPGAS SEQUENTIAL CIRCUITSSrinivas CherukuBelum ada peringkat

- WWW Vlsiencyclopedia Com 2011 12 List of Vlsi Companies HTMLDokumen11 halamanWWW Vlsiencyclopedia Com 2011 12 List of Vlsi Companies HTMLSrinivas CherukuBelum ada peringkat

- Verilog TutorialDokumen123 halamanVerilog TutorialAbhishek KumarBelum ada peringkat

- DIGITAL LOGIC DESIGN VHDL CODING FOR FPGASDokumen19 halamanDIGITAL LOGIC DESIGN VHDL CODING FOR FPGASSrinivas CherukuBelum ada peringkat

- Digital Logic Design: VHDL Coding For Fpgas Unit 3Dokumen20 halamanDigital Logic Design: VHDL Coding For Fpgas Unit 3Srinivas CherukuBelum ada peringkat

- WWW Vlsiencyclopedia Com Search Label Timing 20analysisDokumen6 halamanWWW Vlsiencyclopedia Com Search Label Timing 20analysisSrinivas CherukuBelum ada peringkat

- Digital Logic Design: VHDL Coding For Fpgas Unit 2Dokumen21 halamanDigital Logic Design: VHDL Coding For Fpgas Unit 2Srinivas CherukuBelum ada peringkat

- Digital Logic Design: VHDL Coding For Fpgas Unit 1Dokumen14 halamanDigital Logic Design: VHDL Coding For Fpgas Unit 1Srinivas CherukuBelum ada peringkat

- 7 Series Memory ControllersDokumen36 halaman7 Series Memory ControllersSrinivas CherukuBelum ada peringkat

- 7 Series Memory ControllersDokumen36 halaman7 Series Memory ControllersSrinivas CherukuBelum ada peringkat

- Waveform CodeDokumen25 halamanWaveform CodeSrinivas CherukuBelum ada peringkat

- Range Gate Generator For FMCW Doppler Raradr PDFDokumen5 halamanRange Gate Generator For FMCW Doppler Raradr PDFSrinivas CherukuBelum ada peringkat

- Landing Radio AltimeterDokumen19 halamanLanding Radio AltimeterSrinivas CherukuBelum ada peringkat

- De RatingDokumen24 halamanDe RatingravindradsBelum ada peringkat

- Range Gate Generator For FMCW Doppler Raradr PDFDokumen5 halamanRange Gate Generator For FMCW Doppler Raradr PDFSrinivas CherukuBelum ada peringkat

- Ride Details Bill Details: Thanks For Travelling With Us, SrinivasDokumen3 halamanRide Details Bill Details: Thanks For Travelling With Us, SrinivasSrinivas CherukuBelum ada peringkat

- Coaxial Cable Delay MeasurementsDokumen12 halamanCoaxial Cable Delay MeasurementsSrinivas CherukuBelum ada peringkat

- CDC and LINTDokumen2 halamanCDC and LINTSrinivas CherukuBelum ada peringkat

- ECE232: Hardware Organization and Design: MULTIPLY (Unsigned)Dokumen18 halamanECE232: Hardware Organization and Design: MULTIPLY (Unsigned)Srinivas CherukuBelum ada peringkat

- CRN 307175091Dokumen3 halamanCRN 307175091Srinivas CherukuBelum ada peringkat

- The Fundamentals of Signal AnalysisDokumen68 halamanThe Fundamentals of Signal Analysispunith666Belum ada peringkat

- Convert Negative Pulses to Positive Pulses Using Comparators and TimersDokumen3 halamanConvert Negative Pulses to Positive Pulses Using Comparators and TimersSrinivas CherukuBelum ada peringkat

- METMEL 43 PP2 MNAI SmolaDokumen32 halamanMETMEL 43 PP2 MNAI SmolaSrinivas CherukuBelum ada peringkat

- Convert Negative Pulses to Positive Pulses Using Comparators and TimersDokumen3 halamanConvert Negative Pulses to Positive Pulses Using Comparators and TimersSrinivas CherukuBelum ada peringkat

- Lecture Notes For Digital ElectronicsDokumen43 halamanLecture Notes For Digital ElectronicsShruti GuptaBelum ada peringkat

- Signal Processing and Data Transmission Using A FpgaDokumen54 halamanSignal Processing and Data Transmission Using A FpgaSrinivas CherukuBelum ada peringkat

- Digital Signal Processing Designing For FPGA Architectures: Mariusz Rawski, Bogdan J. Falkowski, and Tadeusz ŁubaDokumen23 halamanDigital Signal Processing Designing For FPGA Architectures: Mariusz Rawski, Bogdan J. Falkowski, and Tadeusz ŁubaSrinivas CherukuBelum ada peringkat