Circuito Lógicos Con Transistores

Diunggah oleh

Diana Catalina JaimesDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Circuito Lógicos Con Transistores

Diunggah oleh

Diana Catalina JaimesHak Cipta:

Format Tersedia

Practica 2: Circuitos logicos con transistores

Profesor: Gustavo Osorio

Monitor: Manuel Alejandro Tamayo Monsalve

Sistemas Digitales

Universidad Nacional De Colombia - Sede Manizales

AbstractSe propone al estudiante estudiar el funcionamiento

de las compuertas logicas a traves de la realizacion de circuitos

con transistores

III. P RACTICA

A. Materiales

I. O BJETIVOS

Identificar el funcionamiento de algunas de las compuertas logicas basicas.

Identificar los valores de tension asociados a los niveles

logicos en un circuito digital.

Conocer el uso del transistor como dispositivo de conmutacion.

II. M ARCO T E ORICO

A. transistores

El transistor es un dispositivo electronico semiconductor

utilizado para entregar una senal de salida en respuesta a

una senal de entrada. Cumple funciones de amplificador,

oscilador, conmutador o rectificador. El termino transistor

es la contraccion en ingles de transfer resistor (resistor de

transferencia).

B. transistor de union bipolar

El transistor de union bipolar (o BJT, por sus siglas

del ingles bipolar junction transistor) se fabrica sobre un

monocristal de material semiconductor como el germanio, el

silicio o el arseniuro de galio, cuyas cualidades son intermedias

entre las de un conductor electrico y las de un aislante. Sobre el

sustrato de cristal se contaminan en forma muy controlada tres

zonas sucesivas, N-P-N o P-N-P, dando lugar a dos uniones

PN.

El comportamiento del transistor se puede ver como dos

diodos (Modelo de Ebers-Moll), uno entre base y emisor,

polarizado en directo y otro diodo entre base y colector,

polarizado en inverso. Esto quiere decir que entre base y

emisor tendremos una tension igual a la tension directa de

un diodo, es decir 0,6 a 0,8 V para un transistor de silicio y

unos 0,4 para el germanio.

Lo interesante del dispositivo es que en el colector tendremos una corriente proporcional a la corriente de base:

IC = IB, es decir, ganancia de corriente cuando > 1.

Para transistores normales de senal, vara entre 100 y 300.

Entonces, existen tres configuraciones para el amplificador:

emisor, base y colector comun.

2

2

4

2

6

2

1

transistores NPN de la referencia 2N2222 o 2N3904

transistores PNP de la referencia 2N3906

resistencias de 1 k

resistencias de 4.7 k

resistencias de 10 k

resistencias de 47 k

dip-switch para protoboard de 2 o 4 posiciones

B. Procedimiento

Implemente el circuito de la Figura. 1. Para cada estado del

interruptor, mida el valor de voltaje en la salida del circuito.

Implemente el circuito de la Figura. 2. Variar el voltaje en

la entrada A en valores de 0 y 5V, mida el valor de voltaje en

la salida del circuito.

Q1: transistor NPN 2N2222 o 2N3904 R1: resistencia de

47 k R2: resistencia de 1 k

Implemente los circuitos que se muestran de la Figura. 3 a

la Figura. 5. En cada uno de los casos variar el voltaje en la

entrada A y B a valores de 0 y 5V, mida el valor de voltaje

en la salida del circuito.

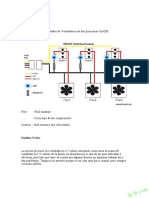

Q1-Q2: transistores NPN 2N2222 o 2N3904 R1-R2: resistencias de 10 k R3: resistencia de 4.7 k

Q1-Q2: transistores PNP 2N3906 R1-R2: resistencias de 10

k R3: resistencia de 4.7 k

Q1-Q2: transistores NPN 2N3904 Q3-Q4: transistores PNP

2N3906 R1-R3: resistencias de 47 k R2-R4-R5-R6: resistencias de 10 k R7: resistencia de 4.7 k

IV. I NFORME

El informe debera llevar el diseno y una breve explicacion

de los procedimientos empleados ademas de las comparaciones contra las compuertas digitales genericas . El informe debe estar redactado en formato IEEE transactions,

con abstract, marco teorico (de ser necesario), Simulaciones,

Resultados, Problemas y Soluciones y Conclusiones, ademas

recordar que todo buen informe tiene un sustento teorico, tal

sustento se manifiesta en el uso adecuado de las referencias

cruzadas. El informe debe presentarse el mismo da de la

sustentacion de la implementacion.

Fig. 1. Circuito para la generacion de los niveles logicos empleando un

interruptor.

Fig. 2. Circuito de la compuerta logica NOT implementado con un transistor

bipolar.

Fig. 3. Circuito de la compuerta logica AND implementado con transistores

bipolares NPN.

Fig. 4. Circuito de la compuerta logica OR implementado con transistores

bipolares PNP.

Fig. 5. Circuito de la compuerta logica NAND implementado con transistores

bipolares NPN y PNP.

Anda mungkin juga menyukai

- La Distorsión de Cruce Por Cero Es Un Tipo de Distorsión Que Se Caracteriza Por La Conmutación Entre Dispositivos Que Manejan Una CargaDokumen1 halamanLa Distorsión de Cruce Por Cero Es Un Tipo de Distorsión Que Se Caracteriza Por La Conmutación Entre Dispositivos Que Manejan Una Cargamaca arrietaBelum ada peringkat

- Problemas de Circuitos Secuenciales Aritmética y ConvertidoresDokumen10 halamanProblemas de Circuitos Secuenciales Aritmética y Convertidoresorlando_heredia7934Belum ada peringkat

- Problemas Propuestos 2018-2Dokumen4 halamanProblemas Propuestos 2018-2Jhoelito KennedyBelum ada peringkat

- LAB1Dokumen3 halamanLAB1OscarBelum ada peringkat

- Circuito de Timbre para SordosDokumen2 halamanCircuito de Timbre para SordosLucho Ponky Paternina100% (1)

- Fundamento TeóricoDokumen8 halamanFundamento TeóricoCESAR DEIVI SANTISTEBAN TUÑOQUEBelum ada peringkat

- Practica 1 Control On OFF LM35Dokumen5 halamanPractica 1 Control On OFF LM35juan c. condori ch.Belum ada peringkat

- Labort Sistemas DigitalesDokumen25 halamanLabort Sistemas DigitalesJuan FieeBelum ada peringkat

- Informe Latch y Flip FlopDokumen11 halamanInforme Latch y Flip FlopAlex Vin0% (1)

- p7 - Multiplexores y DemultiplexoresDokumen7 halamanp7 - Multiplexores y DemultiplexoresalexBelum ada peringkat

- Practica 4. Circuitos Msi Parte 2 Informe Laboratorio Circuitos DigitalesDokumen26 halamanPractica 4. Circuitos Msi Parte 2 Informe Laboratorio Circuitos DigitalesDanielaBelum ada peringkat

- Practico 5 2020 Conv DC DC PDFDokumen2 halamanPractico 5 2020 Conv DC DC PDFMISBelum ada peringkat

- Practicas 2Dokumen2 halamanPracticas 2xodriBelum ada peringkat

- Análisis de Señales2Dokumen10 halamanAnálisis de Señales2sergioBelum ada peringkat

- Diseno de Multiplicador de 2x2 BitsDokumen3 halamanDiseno de Multiplicador de 2x2 BitsLalo SanttyBelum ada peringkat

- Informe 1 Lab. Electronica IDokumen9 halamanInforme 1 Lab. Electronica IIvan TotoyBelum ada peringkat

- Trans Tema3Dokumen62 halamanTrans Tema3opachecoBelum ada peringkat

- Preinforme 6. Completo.Dokumen9 halamanPreinforme 6. Completo.Anonymous Shv3RwsWnrBelum ada peringkat

- Practica InversorDokumen6 halamanPractica InversorAlbert Atrati CordeBelum ada peringkat

- Informe Laboratorio 8Dokumen27 halamanInforme Laboratorio 8Sebastian CespedesBelum ada peringkat

- Diodo SnapDokumen3 halamanDiodo SnapMarin Gonthier100% (1)

- Digitales 1 Previo 5Dokumen11 halamanDigitales 1 Previo 5jorgeBelum ada peringkat

- Cuestionario 2Dokumen9 halamanCuestionario 2AntonioLinkEzeroBelum ada peringkat

- Practica 5Dokumen10 halamanPractica 5Diana ObandoBelum ada peringkat

- Practica 4 Contador AsincronoDokumen5 halamanPractica 4 Contador AsincronoRulo PinedaBelum ada peringkat

- TEMA 10 Analisis de Circuitos SecuencialesDokumen34 halamanTEMA 10 Analisis de Circuitos SecuencialesWanerBelum ada peringkat

- Marco TeóricoDokumen3 halamanMarco TeóricoYossep Manuel Orozco MartinezBelum ada peringkat

- Ejercicios Redes de Dos Puertos y Estabilidad de Funciones.Dokumen3 halamanEjercicios Redes de Dos Puertos y Estabilidad de Funciones.Santiago Fabian Valarezo TorresBelum ada peringkat

- Consulta Detector Picos Conversor Ac DC Circuito Zona MuertaDokumen15 halamanConsulta Detector Picos Conversor Ac DC Circuito Zona MuertaDWilliam93Belum ada peringkat

- Laboratorio 4 y 5Dokumen7 halamanLaboratorio 4 y 5Johan RMBelum ada peringkat

- Laboratorio N°1 Sistemas DigitalesDokumen8 halamanLaboratorio N°1 Sistemas DigitalesJoel AlvinagortaBelum ada peringkat

- Proyecto Conversor Analogo DigitalDokumen5 halamanProyecto Conversor Analogo DigitalsergiopastraBelum ada peringkat

- Compuerta NAND Con TransistoresDokumen2 halamanCompuerta NAND Con TransistoresDIEGO LC100% (1)

- Semaforo DigitalDokumen11 halamanSemaforo DigitalJavierHernandezBelum ada peringkat

- INFORME 2 DigitalesDokumen7 halamanINFORME 2 Digitalesbrayhan1Belum ada peringkat

- Respuesta A La Función Escalón en Un Circuito R-L-C ParaleloDokumen8 halamanRespuesta A La Función Escalón en Un Circuito R-L-C ParaleloAbel Menendez RamosBelum ada peringkat

- Informe Contador 0 Al 9 Con TransistoresDokumen9 halamanInforme Contador 0 Al 9 Con TransistoresOmatsito YanchaBelum ada peringkat

- OsciladoresDokumen4 halamanOsciladoresHector Cajilema100% (1)

- TBJDokumen5 halamanTBJErik RojasBelum ada peringkat

- 1.2.2amplificador en Emisor ComunDokumen12 halaman1.2.2amplificador en Emisor ComunOz MGBelum ada peringkat

- Practica # 3 Electrónica Digital IDokumen8 halamanPractica # 3 Electrónica Digital ImilindrosoBelum ada peringkat

- C1 Contador de RizoDokumen4 halamanC1 Contador de RizoGarcía Román Itzel JocelynBelum ada peringkat

- Alarma Con LM741Dokumen4 halamanAlarma Con LM741Carlos Jose Carvajal ManriqueBelum ada peringkat

- Reporte1 PLD FESC-4Dokumen7 halamanReporte1 PLD FESC-4roboroy13Belum ada peringkat

- Contador de 0-99 Con AlarmaDokumen3 halamanContador de 0-99 Con AlarmaMarvin GarcíaBelum ada peringkat

- Lab8. Acondicionamiento de Sensores de Presión PDFDokumen4 halamanLab8. Acondicionamiento de Sensores de Presión PDFjuan sebastian aldana camachoBelum ada peringkat

- Encendido Por Ausencia de LuzDokumen19 halamanEncendido Por Ausencia de Luzlena95060% (1)

- Lab 5 y 6 CorregidoDokumen4 halamanLab 5 y 6 CorregidoVictoria BermudezBelum ada peringkat

- Comunicacion Serial SincronaDokumen24 halamanComunicacion Serial Sincronaandres8179Belum ada peringkat

- Laboratorio#3Dokumen5 halamanLaboratorio#3Sergio100% (1)

- Linealidad de Redes AuxDokumen12 halamanLinealidad de Redes AuxKawhi LeonardBelum ada peringkat

- Laboratorio - 2 - Logica DigitalDokumen5 halamanLaboratorio - 2 - Logica DigitalSanchez EliseoBelum ada peringkat

- Informe 2Dokumen5 halamanInforme 2Jhoselin Heredia IchotaBelum ada peringkat

- Practica 2.1Dokumen11 halamanPractica 2.1Fabiola OrtuñoBelum ada peringkat

- VHDL - Descripción Serie ComportamentalDokumen19 halamanVHDL - Descripción Serie ComportamentalErika Erikja100% (1)

- 2 Modelo Matemático Inversor MonofásicoDokumen4 halaman2 Modelo Matemático Inversor MonofásicoDanielBelum ada peringkat

- Practica3. Retrolimentación Negativa en El Amplificador OperacionalDokumen3 halamanPractica3. Retrolimentación Negativa en El Amplificador OperacionalLuis Gerardo Escobedo PinalBelum ada peringkat

- INFORME FINAL 8 - Sintesis de Circuitos Secuenciales Sincronos-Reconocedores de SecuenciasDokumen6 halamanINFORME FINAL 8 - Sintesis de Circuitos Secuenciales Sincronos-Reconocedores de SecuenciasAndres CarbajalBelum ada peringkat

- CUARTO LABORATORIO DE ELECTRÓNICA I GatoDokumen15 halamanCUARTO LABORATORIO DE ELECTRÓNICA I Gatohector blancoBelum ada peringkat

- Prácticaa 4 Electrónica 1Dokumen15 halamanPrácticaa 4 Electrónica 1fernandoBelum ada peringkat

- LX - 1610 Magneto AFDokumen18 halamanLX - 1610 Magneto AFLuis Miguel CorazonBelum ada peringkat

- Practica 6Dokumen9 halamanPractica 6Alejandro Misael Fragoso AlarconBelum ada peringkat

- FototransistorDokumen14 halamanFototransistorCarol Huayta86% (7)

- Shield TemperaturaDokumen11 halamanShield TemperaturaGabriel UribeBelum ada peringkat

- Copia de Formato - IEEEDokumen3 halamanCopia de Formato - IEEEJaime RicoBelum ada peringkat

- Practica 7 BJT 2018-1Dokumen9 halamanPractica 7 BJT 2018-1Laura IO HernándezBelum ada peringkat

- If 1 Grupo 5Dokumen9 halamanIf 1 Grupo 5JEAN LEONARDO ESTRADA ROQUEBelum ada peringkat

- Electronica BasicaDokumen11 halamanElectronica Basica1203214Belum ada peringkat

- Catálogo Electrónica Monkits-1Dokumen19 halamanCatálogo Electrónica Monkits-1Norbely Rodriguez BasultoBelum ada peringkat

- Tema4 El MosfetDokumen25 halamanTema4 El MosfetRaul EsparzaBelum ada peringkat

- Proyecto CaseroDokumen34 halamanProyecto Caseropato19Belum ada peringkat

- Universidad Nacional de IngenieriaDokumen15 halamanUniversidad Nacional de IngenieriaHollmandavid VasquezBelum ada peringkat

- Sis 2.0Dokumen29 halamanSis 2.0Freddy Jonathan Condori TurpoBelum ada peringkat

- Dispositivos de Estado Sólido en MicroondasDokumen15 halamanDispositivos de Estado Sólido en MicroondasNoel Eduardo Moreno ViachicaBelum ada peringkat

- Oscilador HartleyDokumen7 halamanOscilador HartleyNataly MéndezBelum ada peringkat

- PreAmplificador de AudioDokumen1 halamanPreAmplificador de AudioAjorgeanAcostaSuclupeBelum ada peringkat

- Control Convertidor Buck-BoostDokumen14 halamanControl Convertidor Buck-BoostYeins Agualimpia CopeteBelum ada peringkat

- Laboratorio 1 Transistores BJTDokumen10 halamanLaboratorio 1 Transistores BJTfer86bd100% (1)

- Informe Lab 2 Compuertas MotorDokumen7 halamanInforme Lab 2 Compuertas MotorGillian CamachoBelum ada peringkat

- Taller Mantenimiento de Sistemas Análogos y Digitales, Componentes ElectrónicosDokumen4 halamanTaller Mantenimiento de Sistemas Análogos y Digitales, Componentes ElectrónicosKILIAN DIAZ MIRANDABelum ada peringkat

- Silabus Electronica EspeDokumen6 halamanSilabus Electronica EspeDiego MeraBelum ada peringkat

- Transistores de Unión Bipolar (TBJ)Dokumen14 halamanTransistores de Unión Bipolar (TBJ)Miguel Ángel Montes ParraBelum ada peringkat

- Amplificadores y Fuentes de AlimentacionDokumen15 halamanAmplificadores y Fuentes de AlimentacionAlan GomezBelum ada peringkat

- Informe 4 Lab Lectronica 2 Grupo 11Dokumen8 halamanInforme 4 Lab Lectronica 2 Grupo 11Brayan LaraBelum ada peringkat

- Calif Inf 2.1 Chilan-Constante-Davila-Ortega-Punina 2Dokumen39 halamanCalif Inf 2.1 Chilan-Constante-Davila-Ortega-Punina 2Samuel PallaresBelum ada peringkat

- Crecimiento EpitaxialDokumen26 halamanCrecimiento EpitaxialEnrique GarcíaBelum ada peringkat

- Baybus - FanBus - RheoBus - ElectroBus - PWM - 220VDokumen17 halamanBaybus - FanBus - RheoBus - ElectroBus - PWM - 220VdiemariasBelum ada peringkat

- Ecu Renix y Sistemas Jeep 88-90Dokumen34 halamanEcu Renix y Sistemas Jeep 88-90Hector Mata100% (2)

- Casos de Punto de Equilibrio 1Dokumen2 halamanCasos de Punto de Equilibrio 1Jeenert Espinoza ValenzuelaBelum ada peringkat

- Catalogo General de Productos 2017 (20170801)Dokumen186 halamanCatalogo General de Productos 2017 (20170801)SamHdzBelum ada peringkat