Memory Organization

Diunggah oleh

ericdunnDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Memory Organization

Diunggah oleh

ericdunnHak Cipta:

Format Tersedia

Memory Organization 1

MEMORY ORGANIZATION

• Memory Hierarchy

• Main Memory

• Auxiliary Memory

• Associative Memory

• Cache Memory

• Virtual Memory

• Memory Management Hardware

Computer Organization Computer Architectures Lab

Memory Organization 2 Memory Hierarchy

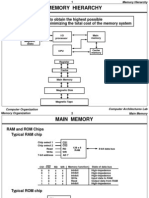

MEMORY HIERARCHY

Memory Hierarchy is to obtain the highest possible

access speed while minimizing the total cost of the memory system

Auxiliary memory

Magnetic

tapes I/O Main

processor memory

Magnetic

disks

CPU Cache

memory

Register

Cache

Main Memory

Magnetic Disk

Magnetic Tape

Computer Organization Computer Architectures Lab

Memory Organization 3 Main Memory

MAIN MEMORY

RAM and ROM Chips

Typical RAM chip

Chip select 1 CS1

Chip select 2 CS2

Read RD 128 x 8 8-bit data bus

RAM

Write WR

7-bit address AD 7

CS1 CS2 RD WR Memory function State of data bus

0 0 x x Inhibit High-impedence

0 1 x x Inhibit High-impedence

1 0 0 0 Inhibit High-impedence

1 0 0 1 Write Input data to RAM

1 0 1 x Read Output data from RAM

1 1 x x Inhibit High-impedence

Typical ROM chip

Chip select 1 CS1

Chip select 2 CS2

512 x 8 8-bit data bus

ROM

9-bit address AD 9

Computer Organization Computer Architectures Lab

Memory Organization 4 Main Memory

MEMORY ADDRESS MAP

Address space assignment to each memory chip

Example: 512 bytes RAM and 512 bytes ROM

Hexa Address bus

Component address 10 9 8 7 6 5 4 3 2 1

RAM 1 0000 - 007F 0 0 0 x x x x x x x

RAM 2 0080 - 00FF 0 0 1 x x x x x x x

RAM 3 0100 - 017F 0 1 0 x x x x x x x

RAM 4 0180 - 01FF 0 1 1 x x x x x x x

ROM 0200 - 03FF 1 x x x x x x x x x

Memory Connection to CPU

- RAM and ROM chips are connected to a CPU

through the data and address buses

- The low-order lines in the address bus select

the byte within the chips and other lines in the

address bus select a particular chip through

its chip select inputs

Computer Organization Computer Architectures Lab

Memory Organization 5 Main Memory

CONNECTION OF MEMORY TO CPU

Address bus CPU

16-11 10 9 8 7-1 RD WR Data bus

Decoder

3 2 1 0

CS1

CS2

Data

RD 128 x 8

RAM 1

WR

AD7

CS1

CS2

Data

RD 128 x 8

RAM 2

WR

AD7

CS1

CS2

Data

RD 128 x 8

RAM 3

WR

AD7

CS1

CS2

RD 128 x 8 Data

RAM 4

WR

AD7

CS1

CS2

Data

1- 7 512 x 8

8

9 } AD9 ROM

Computer Organization Computer Architectures Lab

Anda mungkin juga menyukai

- Fundamentals of Modern Computer Architecture: From Logic Gates to Parallel ProcessingDari EverandFundamentals of Modern Computer Architecture: From Logic Gates to Parallel ProcessingBelum ada peringkat

- Nintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8Dari EverandNintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8Belum ada peringkat

- PC Troubleshooting: Mr. Joseph B. Ramirez JRDokumen112 halamanPC Troubleshooting: Mr. Joseph B. Ramirez JRGauthier ToudjeuBelum ada peringkat

- Class Notes: Memory Technology and System-Level Memory DesignDokumen44 halamanClass Notes: Memory Technology and System-Level Memory DesignHarish ReddyBelum ada peringkat

- 5 - Internal MemoryDokumen22 halaman5 - Internal Memoryerdvk100% (1)

- Computer Structure - MemoryDokumen61 halamanComputer Structure - MemoryLotso Chik100% (1)

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Dari EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Belum ada peringkat

- CHAPTER 5. Memory Element: Electrical Engineering Department PTSBDokumen93 halamanCHAPTER 5. Memory Element: Electrical Engineering Department PTSBPrevenaManiamBelum ada peringkat

- Memory Organization and HierarchyDokumen44 halamanMemory Organization and HierarchyHerambh DubeyBelum ada peringkat

- Lec2 MemDokumen12 halamanLec2 MemparagBelum ada peringkat

- Memory OrganizationDokumen22 halamanMemory OrganizationsivaBelum ada peringkat

- CHAPTER 5. Memory Element: Amir Abu Bakar Electrical Engineering Department PtssDokumen87 halamanCHAPTER 5. Memory Element: Amir Abu Bakar Electrical Engineering Department Ptssah chongBelum ada peringkat

- CH12Dokumen6 halamanCH12sara_lolo100% (1)

- Mc9211unit 5 PDFDokumen89 halamanMc9211unit 5 PDFsanthoshBelum ada peringkat

- Lecture8 Memory SysDokumen26 halamanLecture8 Memory SysathomeBelum ada peringkat

- Mp2-SUPER! - Memory Basics and Memory System Design - v0.3Dokumen27 halamanMp2-SUPER! - Memory Basics and Memory System Design - v0.3serjaniBelum ada peringkat

- CH 12Dokumen38 halamanCH 12subhasiskiitBelum ada peringkat

- Chapter 5-The Memory SystemDokumen80 halamanChapter 5-The Memory SystemPuneet BansalBelum ada peringkat

- Deco Assignment 2 .... AshutoshDokumen8 halamanDeco Assignment 2 .... Ashutoshdownlodemaster1Belum ada peringkat

- Dell Precision t5500 InstructionsDokumen80 halamanDell Precision t5500 InstructionsNikola PetrovBelum ada peringkat

- Memory HierarchyDokumen4 halamanMemory Hierarchynancy_01Belum ada peringkat

- 4 RR Unit-4 NotesDokumen96 halaman4 RR Unit-4 Notesdevillucifer9889Belum ada peringkat

- FLASH and EEPROM Memories For Data StorageDokumen28 halamanFLASH and EEPROM Memories For Data StorageMifzal IzzaniBelum ada peringkat

- Ram and Rom ChipsDokumen10 halamanRam and Rom Chipshardikbhandari12Belum ada peringkat

- 0memory HierarchyDokumen20 halaman0memory HierarchyOm PrakashBelum ada peringkat

- Ram and Rom ChipsDokumen10 halamanRam and Rom ChipsPrasanna Kumar DasBelum ada peringkat

- 01 Computer System 2010Dokumen64 halaman01 Computer System 2010waruna abeyrathnaBelum ada peringkat

- O MemorijamaDokumen36 halamanO MemorijamazaleksBelum ada peringkat

- MemoryDokumen60 halamanMemoryDev PrasadBelum ada peringkat

- Chapter 5-The Memory SystemDokumen84 halamanChapter 5-The Memory SystemupparasureshBelum ada peringkat

- 14 Ram&romDokumen40 halaman14 Ram&rompatilrajucBelum ada peringkat

- Memory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryDokumen6 halamanMemory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryShaik ShariefBelum ada peringkat

- Computer Basics DefinitonDokumen8 halamanComputer Basics DefinitonJeetender nath100% (1)

- Bab-1 Pengantar Personal Computer (PC) 1Dokumen30 halamanBab-1 Pengantar Personal Computer (PC) 1haniBelum ada peringkat

- UG - EC303 DSP Part-5 Buses and Momory - Print PDFDokumen21 halamanUG - EC303 DSP Part-5 Buses and Momory - Print PDFapuurvaBelum ada peringkat

- Computer Literacy: A Look at The Brains of The Computer, The, and Its Associated ComponentsDokumen32 halamanComputer Literacy: A Look at The Brains of The Computer, The, and Its Associated ComponentsNivedita kBelum ada peringkat

- IT Workshop Lab Manual PDFDokumen166 halamanIT Workshop Lab Manual PDFAnusha KakumanuBelum ada peringkat

- Motherboard PPT Bhupen GargDokumen20 halamanMotherboard PPT Bhupen GargBhupen GargBelum ada peringkat

- DCA1104 & Understanding PC & Troubleshooting_Siddharth PalDokumen8 halamanDCA1104 & Understanding PC & Troubleshooting_Siddharth Palsiddharthpscs6Belum ada peringkat

- Memory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryDokumen23 halamanMemory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual Memoryayush ajayBelum ada peringkat

- Unit 5Dokumen42 halamanUnit 5godifab162Belum ada peringkat

- Memory OrganisationDokumen34 halamanMemory OrganisationricketbusBelum ada peringkat

- 13 MemoryDokumen13 halaman13 MemoryNishanthoraBelum ada peringkat

- Different RAM Types and Its UsesDokumen3 halamanDifferent RAM Types and Its Usessinu66Belum ada peringkat

- Memory Terms GlossaryDokumen10 halamanMemory Terms Glossaryalexk001Belum ada peringkat

- RamDokumen4 halamanRamSimbolon XvBelum ada peringkat

- Memory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryDokumen22 halamanMemory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryADITYA KUMAR SINGHBelum ada peringkat

- Connecting With Computer Science Chapter 3 ReviewDokumen7 halamanConnecting With Computer Science Chapter 3 ReviewWalid_Sassi_TunBelum ada peringkat

- HARDWAREDokumen84 halamanHARDWAREjettestBelum ada peringkat

- The Motherboard: A Look at The Brains of The Computer, The Motherboard, and Its Associated ComponentsDokumen36 halamanThe Motherboard: A Look at The Brains of The Computer, The Motherboard, and Its Associated ComponentsNuhu MagwaiBelum ada peringkat

- Computer HardwareDokumen56 halamanComputer HardwareKenneth BautistaBelum ada peringkat

- Different RAM Types and Its UsesDokumen8 halamanDifferent RAM Types and Its Usesdanielle leigh100% (6)

- Random Access MemoryDokumen19 halamanRandom Access MemoryOrlando FelixBelum ada peringkat

- MotherboardDokumen21 halamanMotherboardYash KumarBelum ada peringkat

- Memory: Computer OrganizationDokumen28 halamanMemory: Computer OrganizationAteeqAftabBelum ada peringkat

- MemoryDokumen37 halamanMemoryPatrick RamosBelum ada peringkat

- Unit8 MemoryOrganizationDokumen10 halamanUnit8 MemoryOrganizationlovi bahunBelum ada peringkat

- A+ Chapter 4 RAM - Finalc-CleanDokumen20 halamanA+ Chapter 4 RAM - Finalc-CleanTatenda David GondweBelum ada peringkat

- MemoryDokumen38 halamanMemoryRohit PaulBelum ada peringkat

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Dari EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Belum ada peringkat

- Course File: Fundamentals of Computer & Information Technologies Code: - (A304102)Dokumen26 halamanCourse File: Fundamentals of Computer & Information Technologies Code: - (A304102)Shivani GargBelum ada peringkat

- Oa Course FileDokumen29 halamanOa Course FileShivani GargBelum ada peringkat

- Oa Course FileDokumen29 halamanOa Course FileShivani GargBelum ada peringkat

- Bca CSDokumen35 halamanBca CSShivani GargBelum ada peringkat

- Hospital Management System: OOSD Assignment 1 Object Oriented AnalysisDokumen27 halamanHospital Management System: OOSD Assignment 1 Object Oriented AnalysisShivani GargBelum ada peringkat

- Shiv AniDokumen18 halamanShiv AniShivani GargBelum ada peringkat

- Ticket Reservation SystemDokumen22 halamanTicket Reservation SystemwixnoesaBelum ada peringkat