Evk1100 Schematics Revc

Diunggah oleh

Muhammad FaisalHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Evk1100 Schematics Revc

Diunggah oleh

Muhammad FaisalHak Cipta:

Format Tersedia

5

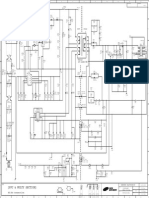

PB[31..0] PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PB8 PB9 PB10 PB11 PB12 PB13 PB14 PB15 PB16 PB17 PB18 PB19 PB20 PB21 PB22 PB23 PB24 PB25 PB26 PB27 PB28 PB29 PB30 PB31

(NM : Not Mounted)

U16 PA[30..0] PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7 PA8 PA9 PA10 PA11 PA12 PA13 PA14 PA15 PA16 PA17 PA18 PA19 PA20 PA21 PA22 PA23 PA24 PA25 PA26 PA27 PA28 PA29 PA30 PC5 PC4 PC3 PC2 PC1 PC0 25 27 30 32 34 39 41 43 45 47 48 50 53 54 56 57 58 60 62 64 66 73 74 75 76 77 78 79 80 122 123 133 132 125 124 86 85 68 39R 70 39R 71 23 81 82 83 PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7 PA8 PA9 PA10 PA11 PA12 PA13 PA14 PA15 PA16 PA17 PA18 PA19 PA20 PA21 PA22 PA23 PA24 PA25 PA26 PA27 PA28 PA29 PA30 PC5 PC4 PC3 PC2 PC1 PC0 VBUS DM DP

PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PB8 PB9 PB10 PB11 PB12 PB13 PB14 PB15 PB16 PB17 PB18 PB19 PB20 PB21 PB22 PB23 PB24 PB25 PB26 PB27 PB28 PB29 PB30 PB31

88 90 96 98 100 102 104 106 111 113 115 119 121 126 127 134 136 139 141 143 3 5 6 9 11 13 14 15 19 20 21 22

PC[5..0]

USB[2..1] VBUS USB1 R85 USB2 R84 RESETn VDDANA ADVREF AGND

PX0 PX1 PX2 PX3 PX4 PX5 PX6 PX7 PX8 PX9 PX10 PX11 PX12 PX13 PX14 PX15 PX16 PX17 PX18 PX19 PX20 PX21 PX22 PX23 PX24 PX25 PX26 PX27 PX28 PX29 PX30 PX31 PX32 PX33 PX34 PX35 PX36 PX37 PX38 PX39 TCK TDO TDI TMS

1 2 4 10 12 24 26 31 33 35 38 40 42 44 46 59 61 63 65 67 87 89 91 95 97 99 101 103 105 107 110 112 114 118 120 135 137 140 142 144 129 130 131 128

PX0 PX1 PX2 PX3 PX4 PX5 PX6 PX7 PX8 PX9 PX10 PX11 PX12 PX13 PX14 PX15 PX16 PX17 PX18 PX19 PX20 PX21 PX22 PX23 PX24 PX25 PX26 PX27 PX28 PX29 PX30 PX31 PX32 PX33 PX34 PX35 PX36 PX37 PX38 PX39 JTAG0 JTAG1 JTAG2 JTAG3

PX[39..0]

VCC3 R1 10k

C

RESETn

JTAG[3..0]

3 4 SW1 SKRAALE010 2 1

C1 100n

RESET_n VDDIN VDDIO_1 VDDIO_2 VDDIO_3 VDDIO_4 VDDIO_5 VDDIO_6 VDDIO_7 VDDOUT VDDANA ADVREF AGND VDDCORE_1 VDDCORE_2 VDDCORE_3 VDDCORE_4 VDDPLL

GND_1 GND_2 GND_3 GND_4 GND_5 GND_6 GND_7 GND_8 GND_9 8 18 28 37 52 72 94 109 117

29 51 55 138 84

17 92 7 36 69 93 108 116

16

VDDSYS

AT32UC3A0512-0ESAL

49

NC

TP71 TESTPAD R18 0R

B

VDDCORE

RESET Circuitry

VDDIN VDDIO

R20 0R

VDDOUT

CLOCK Circuitry

PC[5..0] PC0 PC1 PC2 PC3 PC4 PC5 Xin32 Xout32 Xin0 Xout0 Xin1 Xout1 Xin0

CPU Main Clock XC1 Q12.0-SMU4-30-30/30Xout0 C2 22p C3 22p

VDDOUT C121 1.8V output 2.2u 470p VDDCORE VDDCORE C16 100n C122

Decoupling capacitance

VDDCORE C101 C102 C103 C104 1.8V Core power supply 2.7n 2.7n 2.7n 2.7n 33n

VDDCORE C35 C105 2.2u

VDDIO C126 33n Spare Clock XC2 Q12.0-SMU4-30-30/30VDDANA C30 100n AGND C123 33n Xin1 C4 22p Xout1 C5 22p Xin32 C6 22p RTC Clock Q13FC1450000614 XC5 Xout32 C7 22p

C117 C118 C119 C120 33n 33n 33n

100n

VDDSYS C108 C116 C106 1.8V PLL power supply 2.7n 33n 2.2u

VDDIN

A

C113 C114 C115 3.3V core power supply 33n 33n 33n <Core Design> ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title C37 4.7u Size A3 Date:

5 4 3 2

VDDIO C17 3.3V I/O power supply 100n 100n 100n 100n 33n C27 C28 C29

VDDIO C109 C110 C111 C112 33n 33n 33n

VDDIO

EVK1100 Document Number PROCESSOR Tuesday, December 18, 2007

1

Rev C 1 of 13

Sheet

(NM : Not Mounted)

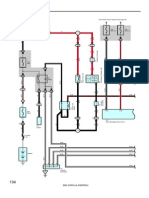

5V Regulator

PJ-002AH-SMT 4 1 3 2 J3 TP43 TESTPAD 2 D9 MBRS340T3G 1 U12 2 3 8 1 5 6 10 11 C8 22 uF C67 470n VIN1 VIN2 ON/OFF CB NC1 NC2 NC3 NC4 NC5 FB GND PGND SWITCH1 SWITCH2 SWITCH3 14 13 12 4 7 C69 L5 Vin VBUS 2 MSS1278-153MLB Vin 7 6 MMS 228 T TP33 TESTPAD D10 MBRS340T3G 2 C10 47u 3 8 SW2 1

Device current limiter TP42 TESTPAD VBUS_IN VBUS_IN 2 3 VCC5 R3 C20 100n 47k 5 4 U2 IN1 IN2 OC EN GND OUT3 OUT2 OUT1 8 7 6 VCC5

D

R2

0R TP1 TP3 TESTPAD TESTPAD

TP72 TESTPAD

C18 4.7u

TPS2020D 1 Board USB powered

9 15

LM2678SD-5.0/NOPB

10n

Test Point duplicated to allow one present on each side of the board VCC5 Host VBUS generation with Overcurrent Detection in output VCC5 R87 R7 47k U4 2 3 5 4 IN1 IN2 OC EN GND OUT3 OUT2 OUT1 8 7 6 VBUS 0R R79 0R TP2 TP12 TESTPAD TESTPAD VDDANA

R6 47k PX[39..0] PB[31..0] PX33 Over_Current_Detect PB17

C24 4.7u

C25 100n VCC5

3.3V Regulator

U17 3 1 C41 100n VIN GND LMS8117ADTX-3.3 R142 2.2k C40 VOUT 2 V3

TP74 TESTPAD R22 2 0R

TP13 TP14 TESTPAD TESTPAD VDDIO

TPS2020D 1

D8 EL15-21UGC

GRM188R60J105KA01 R8 R86 150R 0R 1

TP10 TP15 TESTPAD TESTPAD VDDIN

Shall only be added if TPS2020B R141 0R

B

TP16 TP17 TESTPAD TESTPAD VCC3 R23 0R

VDDANA intends to provide a clean 3.3V power supply for analog blocks VDDIO intends to provide a clean 3.3V power supply for ATUC3A0512 buffers VDDIN intends to provide a clean 3.3V power supply for ATUC3A0512 internal regulator VCC3 intends to provide a clean 3.3V power supply for all peripherals

AGND

TP8 TP32 TESTPADTESTPAD

R80 0R GND

TP9 TP31 TESTPADTESTPAD <Core Design> ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title Size A3 Date:

5 4 3 2

EVK1100 Document Number POWER Tuesday, December 18, 2007

1

Rev C 2 of 13

Sheet

REF_CLK VCC3 TP52 TESTPAD R136 MDC MDIO RESETn LEDLINK

LEDACT_LINK

(NM : Not Mounted)

Not Mounted R139 U14 VCC3 220R 50MHzCFPS73 4 VCC Output 3 VCC3

D

1.5k

GND

NC

VCC3

DGND IOGND X1 X2 IOVDD33 MDC MDIO RESET LED_LINK/AN0 LED_SPEED/AN1 LED_ACT/COL/AN_EN 25MHz_OUT

36 35 34 33 32 31 30 29 28 27 26 25

U13

VDDANA R132 R131 RBIAS PFBOUT AVDD33 RESERVED7 RESERVED6 AGND PFBIN1 TD + TD AGND RD + RD 24 23 22 21 20 19 18 17 16 15 14 13 R97 18R C39 150R 100n 4.7k C92 C93 VDDANA VDDANA C90 100n C32 AGND R127 51R VCC3 GRM188R60J105KA01 100n 10uF/10V VCC3

C

C128 33n

C91 VCC3 RX_DV RX_ER RX0 RX1 R135

100n 2.2k

VCC3 C38 100n C127 33n

TX_CLK TX_EN TXD_0 TXD_1 TXD_2 TXD_3/SNI_MODE PWR_DOWN/INT TCK TDO TMS TRST TDI

VCC3

37 38 39 40 41 42 43 44 45 46 47 48

PFBIN2 RX_CLK RX_DV/MII_MODE CRS/CRS_DV/LED_CFG RX_ER/MDIX_EN COL/PHYAD0 RXD_0/PHYAD1 RXD_1/PHYAD2 RXD_2/PHYAD3 RXD_3/PHYAD4 IOGND IOVDD33

VDDANA R98 2.2k R99 2.2k AGND

TP44 TESTPAD

C33

GRM188R60J105KA01 J18 LEDLINK R19 100R

B

R128 51R

C99 100n

TP45 TESTPAD

3 5 4

TD+ 1 CT TDRD+ CT RD75R NC GND 75R Yellow 1nF 75R Green 11 12 2 1 75R 2 3 4

1 2 3 4 R134 5 6 R133 7 8 R138 9 10 11 12

DP83848I 7 R129 51R VCC3 6 TP46 TESTPAD 8 9 TP47 TESTPAD 10 13 14

5 6 7 8

R17 100R

2.2k

2.2k

PA24 PA[30..0] R130 51R C100 100n

PB[31..0] TP48 TP49 TP50 TP51 TESTPAD TESTPAD TESTPAD TESTPAD PB0 PB1 PB2 PB3 PB5 PB6 PB7 PB8 PB9 PB15 REF_CLK TX_EN TX0 TX1 RX0 RX1 RX_ER MDC MDIO RX_DV

2.2k

TX_EN TX0 TX1

Shield Shield J3026G01DNLT

LEDACT_LINK

VCC3

<Core Design> ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A4 Date: Document Number ETHERNET Tuesday, December 18, 2007 Sheet 3

1 A

Rev C of 13

(NM : Not Mounted)

PA[30..0]

PA11

R25

0R

USB_ID

C

TP7 TP22 TESTPADTESTPAD J5 VBUS DD+ ID GND SHIELD1 SHIELD2 SHIELD3 SHIELD4

B

VBUS 1 2 3 4 5 6 7 8 9 USB1 USB2

USB[2..1]

USB_ID

TP73 TP20 TESTPADTP4 TESTPADTESTPAD

TP5 TP21 TESTPADTESTPAD

TP6 TP11 TESTPADTESTPAD

B

MUSB-05-F-AB-SM-A

<Core Design> ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A Date:

5 4 3

Document Number USB Tuesday, December 18, 2007

2

Rev C Sheet 4

1

of

13

(NM : Not Mounted)

SPI

D

VCC3 R92 100k J6 SPI0_CS0 SPI0_SCK SPI0_MISO SPI0_MOSI 1 2 3 4 5 6 PIN HEADER 1x6 PIP

D

C44

VCC3 100n

PA[30..0]

C

TESTPAD TESTPAD TESTPAD TESTPAD TESTPAD TESTPAD

PA10 PA11 PA12 PA13 PA14 PA15 PA16 PA17 PA18 PA19

SPI0_CS0 SPI0_MISO SPI0_MOSI SPI0_SCK R112 0R

TP53 TP54 TP55 TP56 TP57 TP58

SD/MMC

SPI1_CS0 SPI1_SCK SPI1_MOSI SPI1_MISO SPI1_CS1 SPI1_CS2

VCC3 VCC3 VCC3 VCC3

C

R28 100k

R29 100k

R30 100k

R31 100k J7

R115 R118

0R 0R

SPI1_MISO SPI1_CS1

PA[30..0]

PA2 PA7

7 8 9 1 5 2 10 12 11

SPI_CARDDETECT SPI_WRITEPROTECTn

D0 D1 D2 D3 CLK CMD DETECT WP SW_COM SCDA1A0900

NC

13

SPI1_SCK SPI1_MOSI SPI_CARDDETECT SPI_WRITEPROTECTn

VCC3 VDD VSS1 VSS2 VSS3 4 3 6 14

VCC3 R32 100k SPI1_CS0 SPI1_MISO SPI1_MOSI SPI1_SCK RESETn U8 1 2 3 4 SI SCK RESET CS SO GND VCC WP 8 7 6 5 R35 100k

DATAFLASH

VCC3

R34 R33 100k 100k

VCC3

VCC3 C45 100n

<Core Design> VCC3

A

C46 100n

DECOUPLING CAPACITOR CLOSE TO THE DEVICE

ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A Date: Document Number SPI Tuesday, December 18, 2007

2

Rev C Sheet 5

1

of

13

(NM : Not Mounted)

PA[30..0] 4,5 PA5 PA6 PA8 PA9 R40 R41 R42 R43 0R 0R 0R 0R

USART 1

U1_Rx U1_Tx U1_RTS U1_CTS J9.1 J9.2 J9.3 J9.4 J9.5 J9.6 J9.7 J9.8 J9.9 Pin Direction Input Input Output Output Signal Ground Input Output Input Input Signal to connect to a modem DCD Data Carrier Detect RXD Received Data TXD Transmitted Data DTR Data Terminal Ready DSR RTS CTS RI Data Set Ready Request To Send Clear To Send Ring Indicator

USART 0

PA[30..0] 4,5 PA[30..0] 4,5

PA1 PA0 PA4 PA3 R38 R39 0R 0R

U0_Tx U0_Rx U0_CTS U0_RTS

D

PB[31..0] 4,5

VCC3 C47 100n

U9 C48 100n 1 3 4 5 11 10 12 9 TESTPAD C1+ C1C2+ C2-

16

PB23 PB24 PB25 PB26

R44 R45 R46 R47

0R 0R 0R 0R

U1_DCD U1_DSR U1_DTR U1_RI

VCC

MAX3232ECAE+ C49 V+ 2 V6 C50

100n J8 100n 10 1 6 2 7 3 8 4 9 5 11 17SM209SB64

VCC3 C52 C53 V+ VSHDN RS-232 T1OUT T2OUT T3OUT 27 3 C54 100n TP29 26 100n 100n 10k VCC3 J9 10 1 6 2 7 3 8 4 9 5 11 17SM209SB64 TP30 U10 C1+ C1C2+ C56 100n C2TP25 TESTPAD TTL/CMOS 14 T1IN U1_Tx 13 T2IN U1_RTS 12 T3IN U1_DTR 21 20 TESTPAD 19 18 17 16 15 23 R1OUTB R2OUTB R1OUT R2OUT R3OUT R4OUT R5OUT EN GND R1IN R2IN R3IN R4IN R5IN C55 100n 28 24 1 2 U0_Tx U0_CTS U0_Rx U0_RTS C51 100n TESTPAD

22 R48

GND

T1IN T1OUT T2IN T2OUT R1OUT R1IN R2OUT R2IN

TP27 TESTPAD TX0 14 CTS0 7 R54 RX0 13 RTS0 8 R53

0R 0R

VCC

TP23 TESTPAD Tx1 9 RTS1 10 DTR1 11

15

TP28

TESTPAD

R49

0R

Standard UART on USART_0

TP26 U1_Rx U1_CTS U1_RI U1_DCD U1_DSR

TP24 4 5 6 7 8

TESTPAD Rx1 CTS1 RI1 DCD1 DSR1

R50

0R

PA[30..0] 4,5

PA29 PA30 R88 10k VCC3 SDA SCL 1 2 3 4 J10 VCC3 VCC3 R89 10k

R51 R52

0R 0R

TWI

SDA SCL

25

R57 10k MAX3241EEUI+

USART_1 supports modem interface (UC3A as DTE)

PIN HEADER 1x4 PIP TWI Interface available on a a 4 pins footprint Do not cable any component. Hearder 4 footprint.

<Core Design>

A

ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A4 Date:

5 4 3 2

Document Number USART Tuesday, December 18, 2007 Sheet 6

1

Rev C of 13

(NM : Not Mounted)

Sensors

SENSORS

AVCC3 2 D11 TEMT6000 AVCC3

JOYSTICK

AVCC3

AVCC3 R58 100k

ADC0 R62 NCP18WF104J03RB

ADC2

R61

R63 2 0R

PA[30..0] 4,5 ADC1

VCC3 PA21 PA22 PA23 ADC0 ADC1 ADC2 SW7 SKRHABE010 Joy_A EXTINT TW1 PT10-5034-BLACK Joy_C 1 2 3 7 A CTR C Shield1 B COM D Shield2 4 5 6 8 Joy_D PA[30..0] 4,5 Joy_B R64 10k

VCC3 R65 10k

VCC3 R90 10k

VCC3 R91 10k

VCC3 R81 10k

C57 10n 2

PT-10MV 10 104 A 2020 R137 200k 1

Temperature

Photoresistor

Potentiometer

PA25 PA26 PA20 PA27 PA28

Joy_A Joy_B EXTINT Joy_C Joy_D

VCC3 R66 10k

C

VCC3 R67 10k

VCC3 R68 10k

PUSH BUTTONS

TP69 TESTPAD USW3

LEDS

VCC3 2 VCC3 2 VCC3 2 VCC3 2

C

TP67 TESTPAD USW1

TP68 TESTPAD USW2

D4 EL15-21UGC 3 3 3

D5 EL15-21UGC

D6 EL15-21UGC

D7 EL15-21UGC

4 SW4 SKRAALE010 2 1

C58 100n

4 SW5 SKRAALE010 2 1

C59 100n

4 SW6 SKRAALE010 2 1

C60 100n TESTPAD TP59 PX[39..0] 4,5 PX16 PX19 PX22 USW1 USW2 USW3 LED0 R73 150R TESTPAD TP60 LED1 R74 150R TESTPAD TP61 LED2 R75 150R TESTPAD TP62 LED3 R76 150R

VCC3 2 4

VCC3 2 4

1 PB[31..0] 4,5

PB27 PB28 PB29 PB30

SML-020MLT D2 1 3 R69 150R TESTPAD TP63 R70 150R TP64 TESTPAD

SML-020MLT D3 1 3 R71 150R TESTPAD TP65 R72 150R TP66 TESTPAD PB[31..0] 4,5

LED0 LED1 LED2 LED3

PB19 PB20 PB21 PB22

LED4 LED5 LED6 LED7

LED5

LED6

Bicolore Leds on PB bus : LED4, LED5, LED6 & LED7 on PWM channels

LED7

LED4

<Core Design> ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title Size A3 Date:

5 4 3 2

EVK1100 Document Number SENSORS Tuesday, December 18, 2007

1

Rev C 7 of 13

Sheet

VCC3 C34 4.7u

D

(NM : Not Mounted)

C65 100n C124 C31 33n 4.7u

D

C61 100n

C125 33n SDRAM

U11 PX[39..0] 4,5 PX0 PX1 PX2 PX3 PX4 PX5 PX6 PX7 PX8 PX9 PX10 PX11 PX14 PX17 PX18 PX20 PX21 PX23 PX24 PX25 PX26 PX27 PX28 PX29 PX30 PX31 PX32 PX34 PX35 PX36 PX37 PX38 PX39 PB[31..0] 4,5 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 SDA10 A13 A14 A16 A17 DQM0 DQM1 SDWEn CASn RASn CS1n R77 SDCKE R93 VCC3 SDCK 4.7k 4.7k 37 38 CKE CLK 23 24 25 26 29 30 31 32 33 34 22 35 36 20 21 15 39 16 17 18 19 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 BA0 BA1

D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 DQM1 CS1n A17 A16 A14 A13 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 DQM0 D15 D14 D13 D12 D11

DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 VDDQ1 VDDQ2 VDDQ3 VDDQ4 VDD1 VDD2 VDD3 VSS1 VSS2 VSS3 VSSQ1 VSSQ2 VSSQ3 VSSQ4

2 4 5 7 8 10 11 13 42 44 45 47 48 50 51 53 3 9 43 49 1 14 27 54 41 28 52 46 12 6

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

DQML DQMH WE CAS RAS CS

VCC3

40

NC

MT48LC16M16A2

PB10 PB11 PB12 PB13 PB14 PB16

<Core Design> SDCK SDCKE RASn CASn SDWEn SDA10 ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A Date: Document Number MEMORIES Tuesday, December 18, 2007

2

Rev C 8

1

Sheet

of

13

(NM : Not Mounted)

PB[31..0] 4,5

PB4 PB10 PB11 PB12 PB13 PB14 PB16 PB17 PB19 PB20 PB21

MSEO1 MD00 MD01 MD02 MD03 MD04 MD05 MSEO0 EVTIn EVTO MCKO

JTAG[3..0] 4,5

JTAG0 JTAG1 JTAG2 JTAG3

JTAG_TCK JTAG_TDO JTAG_TDI JTAG_TMS

TESTPAD TESTPAD TESTPAD TESTPAD TESTPAD

TESTPAD

TESTPAD

TESTPAD

NEXUS INTERFACE

VCC3 RESETn JTAG_TDO R78 10k JTAG_TCK JTAG_TMS JTAG_TDI 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43

J57 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 GND1 GND3 GND5 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 GND2 GND4 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42

TP34 TP35 TP36 TP37 TP38

TP39

TP40

VCC3 EVTIn

J58 MD05 MD04 MD03 MD02 MD01 MD00 EVTO MCKO MSEO1 MSEO0 JTAG_TCK JTAG_TDO JTAG_TMS EVTO JTAG_TDI 1 3 5 7 9 STL2-660VTT-10U Pin Header SMD 2,54mm 2 4 6 8 10

TP41

VCC3 RESETn

VCC3

VCC3

VCC3

C77 100n

C78 100n

C79 100n

JTAG INTERFACE

2-5767004-2

<Core Design> ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A Date:

5 4 3

Document Number MEMORIES Tuesday, December 18, 2007

2

Rev C 9

1

Sheet

of

13

(NM : Not Mounted)

No component shall be implemented for this connector Only a footprint of Header 1.27mm shall be present on PCB

D

This connector allows easy connection of peripheral in the prototyping area J27

PA[30..0]

PA[30..0]

J26 PB[31..0] PB0 R140 PB2 PB4 PB6 PB8 PB10 PB12 PB14 PB[31..0] GND 0R 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 VCC3 PB1 PB3 PB5 PB7 PB9 PB11 PB13 PB15 VCC3 PB17 PB19 PB21 PB23 PB25 PB27 PB29 PB31 PC5 VCC3 PB[31..0]

PA[30..0]

PA[30..0] PB[31..0]

PB[31..0]

PA0 PA2 PA4 PA6 PA8 PA10 PA12 PA14 PA16 PA18 PA20 PA22 PA24 PA26 PA28 PA30 PX0 PX2 PX4 PX6 PX8 PX10 PX12 PX14 PX16 PX18 PX20 PX22 PX24 PX26 PX28 PX30 PX32 PX34 PX36 PX38

GND

PB[31..0]

PC[5..0]

PB16 PB18 PB20 PB22 PB24 PB26 PB28 PB30 PC4

GND

PB[31..0]

PX[39..0]

GND GND

PB[31..0]

PX[39..0]

PC[5..0]

PX[39..0]

GND

2x20 FEMALE HEADER

PX[39..0]

PX[39..0]

GND

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79

VCC3 PA1 PA3 PA5 PA7 PA9 PA11 PA13 PA15 PA17 PA19 PA21 PA23 PA25 PA27 PA29 VCC3 VCC3 PX1 PX3 PX5 PX7 PX9 PX11 PX13 PX15 PX17 PX19 PX21 PX23 PX25 PX27 PX29 PX31 PX33 PX35 PX37 PX39 VCC3

PA[30..0]

PA[30..0]

PA[30..0]

PA[30..0]

C

RESETn PX[39..0]

PX[39..0]

PX[39..0]

PX[39..0]

PX[39..0]

2x40 FEMALE HEADER

<Core Design>

A

ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A4 Date:

5 4 3 2

Document Number EXPANSION Tuesday, December 18, 2007 Sheet 10

1

Rev C of 13

(NM : Not Mounted)

EA-DIP204-4 Blue white LCD KS0073 controller

LCD1 VCC5 18R R103 LCD Module

4 X 20 Characters

PB18 R21 PB[31..0]

0R

LCD_A 17 LCD_C 18 15

A C NC VEE VDD VSS

3 2 1

TP70 TESTPAD LCD_ADJ2

VCC3

R105 3266W-1-502_LF

LCD_ADJ2 VCC3 GND

C

LCD_ADJ2 LCD_VDD LCD_VSS

3 2 1

VCC3

R82 10k

SPI1_MISO SPI1_CS2 SPI1_MOSI SPI1_SCK RESETn

B

14 13 12 11 10 9 8 7 4 5 6 16

D7 D6 D5 D4 D3 D2 D1 D0 RS R/W E RES DIP204-4e

VCC3

C76 100n

<Core Design> ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A Date:

5 4 3

Document Number LCD Tuesday, December 18, 2007

2

Rev C Sheet 11

1

of

13

(NM : Not Mounted)

24 lines of array + 1 line of VCC + 1 line of VSS

D

VCC3

D

J60

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 PIN HEADER 1x16

E14

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

E3 E13 SJ-5076 FIDUCIAL E2 E12 SJ-5076 MOUNTING HOLE E15

J61

PIN HEADER 1x16

J69

PIN HEADER 1x16

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

J62

C

PIN HEADER 1x16

J70

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 PIN HEADER 1x16

MOUNTING HOLE

C

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

E16 FIDUCIAL

J63

PIN HEADER 1x16

J71

PIN HEADER 1x16

E11 SJ-5076

E1 MOUNTING HOLE

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

J64

PIN HEADER 1x16

J72

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 PIN HEADER 1x16 E10 SJ-5076

FIDUCIAL

E17

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

J65

PIN HEADER 1x16

J73

PIN HEADER 1x16 PCB1

MOUNTING HOLE

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

J66

PIN HEADER 1x16

J74

PIN HEADER 1x16

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

J67

PIN HEADER 1x16

J75

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 PIN HEADER 1x16 A0609.3.1000.B

J68

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 PIN HEADER 1x16

<Core Design> 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

A

J85

PIN HEADER 1x16

ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A4 Date: Document Number PROTO Tuesday, December 18, 2007 Sheet

1

Rev C 12 of 13

ERRATA REV C/

USART 0 U0_CTS (PA.4) must be connected to U9.9 U0_RTS (PA.3) must be connected to U9.10 U9.8 (R2IN) must be connected to J8.7 U9.7 (T2OUT) must be connected to J8.8 USART 1 U10.11 (DTR1) must be connected to J9.6 U10.8 (DSR1) must be connected to J9.4 LEDS LED 5/Green is connected to GPIO PB.19 and not to PB.20 LED 5/Red is connected to GPIO PB.20 and not to PB.19 LED 6/Green is connected to GPIO PB.21 and not to PB.22 LED 6/Red is connected to GPIO PB.22 and not to PB.21 SPI Wrong Silkscreen : MISO and SCK are swapped

<Core Design> ATMEL Nantes SA La Chantrerie BP 70602 44306 Nantes Cedex 3 FRANCE Title EVK1100 Size A Date:

5 4 3

Document Number ERRATA Tuesday, December 18, 2007

2

Rev C Sheet 13

1

of

13

Anda mungkin juga menyukai

- K Connector List: A1 A2 A3 A4 A5 A6Dokumen18 halamanK Connector List: A1 A2 A3 A4 A5 A6diemnganBelum ada peringkat

- Balita 1.3LDokumen9 halamanBalita 1.3LReinaldo ArrivillagaBelum ada peringkat

- Chery Tiggo QQ Fulwin Spare Parts Iran MVM 110 Tiggo 5 Auto Parts Code-CINA AUTO PARTS GROUPDokumen38 halamanChery Tiggo QQ Fulwin Spare Parts Iran MVM 110 Tiggo 5 Auto Parts Code-CINA AUTO PARTS GROUPCINA auto partsBelum ada peringkat

- EEPROM ADPTER Function List: Software Version: V18.21 Function Automaker Mode/Year System/IC-TypeDokumen5 halamanEEPROM ADPTER Function List: Software Version: V18.21 Function Automaker Mode/Year System/IC-Typejonathan220185Belum ada peringkat

- JVC Av-2115ee Chassis CGDokumen150 halamanJVC Av-2115ee Chassis CGarsyad1973Belum ada peringkat

- 2009 Toyota Corolla Interior Lights DiagramasDokumen13 halaman2009 Toyota Corolla Interior Lights DiagramasRubenBelum ada peringkat

- Mahindra Price ListDokumen1 halamanMahindra Price Listkishan KumarBelum ada peringkat

- Inverter AssemblyDokumen25 halamanInverter AssemblyNguyễn Khắc TâmBelum ada peringkat

- SWR Auto & Peak-Power Wattmeter Rev6 PDFDokumen4 halamanSWR Auto & Peak-Power Wattmeter Rev6 PDFkierosBelum ada peringkat

- Headlight: 110 Toyota Tacoma (Em01D0U)Dokumen6 halamanHeadlight: 110 Toyota Tacoma (Em01D0U)DanielBelum ada peringkat

- Compal La-B111p r1.0 Lenovo Y50-70schematics PDFDokumen59 halamanCompal La-B111p r1.0 Lenovo Y50-70schematics PDFgrafikkoBelum ada peringkat

- Daihatsu Ayla Workshop & Service Manual (B100) 2012Dokumen591 halamanDaihatsu Ayla Workshop & Service Manual (B100) 2012Gerald LimBelum ada peringkat

- Gila EVT1 Schematic (.BakDokumen70 halamanGila EVT1 Schematic (.BakuimBelum ada peringkat

- Schematic Diagrams-7: Display PC BoardDokumen1 halamanSchematic Diagrams-7: Display PC BoardBinh NguyenBelum ada peringkat

- 2A, 28V, 1.5Mhz Step-Down Converter: The Future of Analog Ic TechnologyDokumen16 halaman2A, 28V, 1.5Mhz Step-Down Converter: The Future of Analog Ic TechnologyCazbir MariAndradaBelum ada peringkat

- PanasonicDokumen458 halamanPanasonicAli HassanBelum ada peringkat

- 95 JDM WRX STi V2 EJ20 Pinout Wiring ChartsDokumen3 halaman95 JDM WRX STi V2 EJ20 Pinout Wiring ChartsAlex Salinas Di MirandaBelum ada peringkat

- Ecm Aveo x1Dokumen3 halamanEcm Aveo x1cerrajeria autokey100% (1)

- GSR/ B16A OBD1 ECU Pin OutDokumen3 halamanGSR/ B16A OBD1 ECU Pin OutMie Starr YusofBelum ada peringkat

- Toyota Rav4 2.2 2ad FHV Pin Out Engine PDFDokumen10 halamanToyota Rav4 2.2 2ad FHV Pin Out Engine PDFMiguel Angel Alvarado AlarconBelum ada peringkat

- Abs (RHD) Abs (RHD)Dokumen1 halamanAbs (RHD) Abs (RHD)ถาวร อู่ทรัพย์Belum ada peringkat

- Wiring HarnessDokumen23 halamanWiring HarnessRichard Andrianjaka LuckyBelum ada peringkat

- 4E-FE ECU Pinou T Pin Name Wire Color Explanation: Conn Ector 1Dokumen3 halaman4E-FE ECU Pinou T Pin Name Wire Color Explanation: Conn Ector 1Montadher JawadBelum ada peringkat

- BYD F3 Wire HarnessDokumen53 halamanBYD F3 Wire HarnessXabi Alonso SanzBelum ada peringkat

- Aopen Laptop Motherboard Schematic DiagramDokumen47 halamanAopen Laptop Motherboard Schematic DiagrampukymottoBelum ada peringkat

- pm7 p28 PatchingDokumen13 halamanpm7 p28 PatchingKi Rekso AljeroBelum ada peringkat

- Acer+E5 574+Quanta+ZRWDokumen48 halamanAcer+E5 574+Quanta+ZRWnelsonBelum ada peringkat

- 2014 Forntier IpdmDokumen3 halaman2014 Forntier IpdmMiguel Angel de la Cruz100% (1)

- RC4A-EL Manual OEMDokumen207 halamanRC4A-EL Manual OEMcarlosBelum ada peringkat

- ABS Mod - LAND ROVER CLUB V.IDokumen79 halamanABS Mod - LAND ROVER CLUB V.Itim yerbyBelum ada peringkat

- SmdcodeDokumen232 halamanSmdcodeedicibaBelum ada peringkat

- Sat Filter Left 110HzDokumen2 halamanSat Filter Left 110HzxxBelum ada peringkat

- Evo X ECUDokumen2 halamanEvo X ECUJustin StarkBelum ada peringkat

- Yaris TS Turbo Parts Catalogue - EUDokumen35 halamanYaris TS Turbo Parts Catalogue - EUCarlos FernandoBelum ada peringkat

- Am29f400bb 90si Amd Datasheet 72825Dokumen5 halamanAm29f400bb 90si Amd Datasheet 72825Joel AgbekponouBelum ada peringkat

- NT Bosch Edc7uc31 Xrom Mpc562 Egpt Allbrand 1033Dokumen3 halamanNT Bosch Edc7uc31 Xrom Mpc562 Egpt Allbrand 1033richie thenBelum ada peringkat

- Samand LX Owner ManualDokumen188 halamanSamand LX Owner ManualFrancisco La Guardia100% (1)

- Document ID: 4525240: K20 Engine Control Module X2 ( (LKL+M02) /LKK)Dokumen5 halamanDocument ID: 4525240: K20 Engine Control Module X2 ( (LKL+M02) /LKK)Alfredo MedinaBelum ada peringkat

- Toyota Problem CodesDokumen1 halamanToyota Problem CodesFluke Ranza100% (2)

- Hydraulic ExcavatorsDokumen24 halamanHydraulic ExcavatorsGuido MarconiBelum ada peringkat

- DC Motor Speed Control BC201Dokumen24 halamanDC Motor Speed Control BC201ROSEMARIO PORFIRIOBelum ada peringkat

- IECU-U0100, Data Link: Integrated Electronic Control UnitDokumen7 halamanIECU-U0100, Data Link: Integrated Electronic Control UnitBùi Xuân ĐứcBelum ada peringkat

- ECM Mitsubishi Pajero - FULL MOTORES CHECKDokumen5 halamanECM Mitsubishi Pajero - FULL MOTORES CHECKJuan Felipe Romero Rayo100% (1)

- Sansung Arm Cortex m3 - s3fm02g - Brochure-0Dokumen2 halamanSansung Arm Cortex m3 - s3fm02g - Brochure-0alexandre.oneill2479100% (1)

- Tvip PDFDokumen6 halamanTvip PDFamart79196Belum ada peringkat

- Auo T546HF02-V0-CB Auo-12405Dokumen36 halamanAuo T546HF02-V0-CB Auo-12405sschematicBelum ada peringkat

- Samsung 940FN PDFDokumen66 halamanSamsung 940FN PDFsupriyo110Belum ada peringkat

- Datasheet ASD-ADokumen13 halamanDatasheet ASD-APiraveen Venkatesh KumarBelum ada peringkat

- BSD104DV H3axDokumen21 halamanBSD104DV H3axTiborBelum ada peringkat

- FWD - Easi Pour - EmlDokumen6.166 halamanFWD - Easi Pour - EmlFranky Pinilla100% (1)

- Samsung Bn44 00369aDokumen2 halamanSamsung Bn44 00369aOrangzeb Khan100% (1)

- Grand Am Continental Tire Sports Integrating ECU PDFDokumen31 halamanGrand Am Continental Tire Sports Integrating ECU PDFsenthilvlBelum ada peringkat

- 150w BoostDokumen1 halaman150w BoostKunal Kundanam100% (1)

- MMB0 RevC SchematicDokumen1 halamanMMB0 RevC SchematicbiotekyBelum ada peringkat

- Mach Ngly Sim300czDokumen2 halamanMach Ngly Sim300czViet Bui QuocBelum ada peringkat

- Q9T4 FP91G Interface BDDokumen5 halamanQ9T4 FP91G Interface BDax63naBelum ada peringkat

- Daewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBDokumen27 halamanDaewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBJavier Silva AlanisBelum ada peringkat

- W375 L3 V1.2 SchemDokumen3 halamanW375 L3 V1.2 SchemAdrian PeterBelum ada peringkat

- Can Bus SCHDokumen1 halamanCan Bus SCHhoangdai100% (3)

- Spock: Power Serial I/ODokumen5 halamanSpock: Power Serial I/OSanyi Ocsai100% (2)

- Introduction To CMOS VLSI Design (E158) Final ProjectDokumen4 halamanIntroduction To CMOS VLSI Design (E158) Final ProjectbashasvuceBelum ada peringkat

- Technical Support - Welcome To HuaweiDokumen2 halamanTechnical Support - Welcome To HuaweiMary WarrenBelum ada peringkat

- CUDA C Programming GuideDokumen346 halamanCUDA C Programming GuidePrashant446Belum ada peringkat

- TDS WirelessOpticalDesktop700 0701ADokumen2 halamanTDS WirelessOpticalDesktop700 0701AAnissia KravitzBelum ada peringkat

- E Emanual Asus x550LDokumen116 halamanE Emanual Asus x550LKashif JameelBelum ada peringkat

- DLD 07 RegistersDokumen10 halamanDLD 07 Registerszunaedz110Belum ada peringkat

- Flash Recovery Area - Space Management Warning & Alerts (ID 305812.1)Dokumen5 halamanFlash Recovery Area - Space Management Warning & Alerts (ID 305812.1)surendra82Belum ada peringkat

- SS7Dokumen70 halamanSS7Leanne RoseBelum ada peringkat

- Intesisbox IboxDokumen27 halamanIntesisbox IboxEscape ExistBelum ada peringkat

- S Marquez Cloud ComputingDokumen5 halamanS Marquez Cloud Computingapi-281409276Belum ada peringkat

- ٢٠٢٢ ٠٧ ٢٠Dokumen23 halaman٢٠٢٢ ٠٧ ٢٠MOUSTAFA KHEDRBelum ada peringkat

- Precision DC & Stepper Motor ControllerDokumen3 halamanPrecision DC & Stepper Motor ControllercostpopBelum ada peringkat

- Msp430 Conf Feb019Dokumen5 halamanMsp430 Conf Feb019Adeeb HusnainBelum ada peringkat

- Aix HMC CommandsDokumen8 halamanAix HMC CommandsazkarashareBelum ada peringkat

- Manual Op5 15 eDokumen177 halamanManual Op5 15 eFernando DallaquaBelum ada peringkat

- Bypass FirewallDokumen8 halamanBypass Firewallamitk402Belum ada peringkat

- ResumeDokumen5 halamanResumeImtiyaz HasanBelum ada peringkat

- How To Update The FirmwareDokumen5 halamanHow To Update The FirmwareanuvindanuvindBelum ada peringkat

- Gmre Ason TrainingDokumen46 halamanGmre Ason TrainingMehdi100% (1)

- Guava For Netflix - 1Dokumen38 halamanGuava For Netflix - 1Javier BushBelum ada peringkat

- KIP 700 Technical Specs PDFDokumen2 halamanKIP 700 Technical Specs PDFTECNICO8 AUROSBelum ada peringkat

- AppleVision 850Dokumen2 halamanAppleVision 850scriBelum ada peringkat

- Smit - Fast PathDokumen11 halamanSmit - Fast PathFarouk 2ndBelum ada peringkat

- Blackmagic Decklink SDK PDFDokumen405 halamanBlackmagic Decklink SDK PDFHarold PiedrahitaBelum ada peringkat

- M.C.A. SyllabusDokumen17 halamanM.C.A. SyllabusGauravBelum ada peringkat

- Model A8 Specification: 4K UHD Media Player With HDRDokumen8 halamanModel A8 Specification: 4K UHD Media Player With HDRed_coBelum ada peringkat

- Factuur PDF TemplateDokumen2 halamanFactuur PDF TemplateAmandaBelum ada peringkat

- Bhutan-NationalGIS Technical Proposal DraftDokumen61 halamanBhutan-NationalGIS Technical Proposal DraftshankarBelum ada peringkat

- Student Grading SystemDokumen49 halamanStudent Grading SystemJomar M BuhiaBelum ada peringkat

- 241 - Ceragon - LAG CONFIG - Presentation v1.0Dokumen17 halaman241 - Ceragon - LAG CONFIG - Presentation v1.0mehdi_mehdi0% (1)