II. Bias Circuit II. Bias Circuit: Outline

Diunggah oleh

Raghu McDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

II. Bias Circuit II. Bias Circuit: Outline

Diunggah oleh

Raghu McHak Cipta:

Format Tersedia

II Bias circuit

II. Bias circuit

Outline CMOS current mirrors Definitions Basic stage for current mirrors Simple current mirror Wilson current mirror Improved Wilson current mirror Cascode current mirror Modified cascode current mirror High-compliance current mirrors (I - II) Regulated cascode current mirror Low-voltage current mirrors

II. Bias circuit

Introduction Active devices (transistors) have to be properly biased to process the signal In an analog signal processing circuit there are two fundamental parts: Processing part Bias circuit

The processing part is devoted to elaborate the signal Dynamic requirement

Current references Introduction Simple current reference Current references based on a built-in voltage Current references based on a reference voltage

The bias circuit is devoted to supply currents and/or voltages to the processing one in order to allow it to properly operate Static requirement (Low-frequency, immunity to VDD noise, temperature, and technology spread)

Voltage references Introduction Supply dividers Voltage references based on a built-in voltage Voltage references based on the band-gap voltage Voltage references based on MOS VTH difference

A. Baschirotto - Bias circuit

II 2

II Bias circuit

II Bias circuit

CMOS current mirrors

Definitions A current mirror reads a current entering in a read-node and mirror this current (with a suitable gain factor) to an output node (nodes)

VDD RL Iref Iout

CMOS current mirrors

Applications

Bias

Circuit no. 1 Circuit no. 2

Iout = kIRef k current gain

Ire f

Current Mirror

M1 M2

Read section

Ibias Current mirror

Ibias

Signal path Current mirror non-idealities

Current mirror

Current gain error Output impedance (rout)

=> reduces the output current Iout RL = kIRef R L + r out

Iref

VDD RL Iout

Read section

Iout

Saturation voltage (VCM)

=> for Vo<VCM the current mirror doesn't operate correctly => reduces the output voltage dynamic range

Current Mirror

VCM rout

Isignal Vi+ Q1 Q2

Isignal 2Isignal Isignal Vi-

Ibias

Basic trade-off: Frequency behaviour

dynamic range <=> precision

- Differential-to-Single Ended transformation - Frequency behaviour

A. Baschirotto - Bias circuit

II 3

A. Baschirotto - Bias circuit

II 4

II Bias circuit

II Bias circuit

Simple Current Mirror

Current gain

Simple Current Mirror

Output impedance (rout)

VDD

Iref

M2 Iout PMOS Insert Evaluate Calculate Vtest Itest

Iout M2

Iref M1

Iout M2

M1 Iref

M1

NMOS M1 operates in saturation

k' W IRef = I1 = 2 L (VGS1 - VTH)2 (1 + VDS1)

1

Vtest rout = Itest

Itest

VDS1 = VGS1 = VGS2 If M2 operates in saturation k' W Iout = I2 = 2 L (VGS2 - VTH)2 (1 + VDS2)

2

G S vgs gmvgs

D rds

G S vgs gmvgs

D Vtest rds

M1

M2

rout = rds2 =

W L

1 I2

Iout = IRef

W L

(1 + V DS2 ) (1 + V D S 1 )

Use of long device (large L) to increase rout Use of large (VGS VTH) for good matching (small importance of VTH mismatch)

A. Baschirotto - Bias circuit

II 5

A. Baschirotto - Bias circuit

II 6

II Bias circuit

II Bias circuit

Simple Current Mirror

Frequency behaviour

Simple Current Mirror

Output swing

Iref M1

Iout M2

Iref M1

Iout VDSsat2 M2

Small signalequivalent circuit

Iin Iout G vgs1 S

Cgs1 gm1vgs1 rds1 vgs2

The output swing in the Simple current mirror is limited to

D G

Cgs2

D S

gm2vgs2 rds2

Vout,min = VDSsat,2

M1

M2

i out gm2/gm1 iin = 1+s(Cgs1+Cgs2)/gm1 k = gm2/gm1 = Cgs2/Cgs1 i out k iin = 1+s(1+k)Cgs1/gm1 fT = gm1/Cgs1 pole = (gm1/Cgs1)/(1+k) = fT/(1+k)

A. Baschirotto - Bias circuit

II 7

A. Baschirotto - Bias circuit

II 8

II Bias circuit

II Bias circuit

Simple Current Mirror Simple Current Mirror

Factors affecting the mirror accuracy Factors affecting the mirror accuracy Channel length modulation () Channel length modulation ()

Threshold offset Parasitic resistances Imperfect geometrical matching and current mobility variation

Id

1 + VD S 2 Iout 1 IRef = W 1 + V D S 1 L

2

W L

VGS1=VGS2

VDS

It can be improved by increasing the output resistance. - use of large L (typically current mirrors are not realized with th eminimum technological L. This can results in a large capacitance at the output node)

A. Baschirotto - Bias circuit

II 9

A. Baschirotto - Bias circuit

II 10

II Bias circuit

II Bias circuit

Simple Current Mirror

Factors affecting the mirror accuracy

Simple Current Mirror

Factors affecting the mirror accuracy

Iref M1

Iout M2

Imperfect geometrical matching and current mobility variation

I 2 I k' 2 Cox 2 W 2 L 2 = k' + C + W + L ox

Threshold offset Threshold of MOS transistors in close proximity can differ by 4 mV. For transistors hundred of m apart, the threshold difference VTh can be 40 mV

VTH ' Iout = Iout 1 + 2 V G S - V T H

k' Cox k' and C are minimized with closed and centroid ox common structures

W 2 W + L 2 L

depends on the lithographyc process

Use large (VGS VTH) to improve matching Parasitic resistances A parasitic resistance in series with the source determines a voltage drop The metal resistance is of the order of 20-50 /q, with 10 squares it results 0.2-0.5 . If the current is 10 mA it results an equivalent offset of 2-5 mV.

For large W a good strategy is to have W not much larger than L and to put equal transistors in parallel

Iout Iref M1

1 2 3 4 n

W=W/n

M2

I 2 I

L 2 1 W'2 = ..... + n W' + L

A. Baschirotto - Bias circuit

II 11

A. Baschirotto - Bias circuit

II 12

II Bias circuit

II Bias circuit

Simple Current Mirror

Factors affecting the mirror accuracy

Simple Current Mirror

Design example With the following technological parameter design a simple current mirror in order that it drives to the output node 1mA and it requires 400mV Lmin = 0.5m; ; nCox = 60A/V2 ; pCox = 30A/V2 ; n = 0.1 V1 ; p = 0.2 V1 ; = 0 ; VTHN = VTHN = 0.7V

Imperfect geometrical matching and current mobility variation Example: Circuit scheme

Iref

Iout

Which is the expected output impedance ?

M1

Layout solution

I Ref

M2

M1

M1

M1

M2

M2

M1

M2

GND I Out

A. Baschirotto - Bias circuit

M2

II 13

A. Baschirotto - Bias circuit

II 14

II Bias circuit

II Bias circuit

Wilson current mirror Wilson current mirror

Increases the output resistance Output swing

Iref

Iout M3

Iref

Iout M3 VDSsat3 VGS2

M1

M2

M1

M2

VGS1 = VGS2 I1 I2

The output swing in the Wilson current mirror is limited to Vout,min = VGS2 + VDSsat,3 > VTh + 2VDSsat

W Iout L 1 1 + V D S 2 IRef = W 1 + V D S 1 L

1 + VD S 2 Iout 1 IRef = W 1 + (V D S 2 + V G S 3 ) L

2

W L

There is a sistematic error since VDS1 = VDS2 + VGS3

A. Baschirotto - Bias circuit

II 15

A. Baschirotto - Bias circuit

II 16

II Bias circuit

II Bias circuit

Wilson current mirror

Output impedance

Improved Wilson current mirror

Current gain

Iref

Iout M3

M1

Small signal equivalent circuit

M2

Iref M4

g

m 3 gs3

Iout M3 M2

M1

ix vx

G3 g R

L

m 1 g2

G2 S3 1/g r ds3

m2

ds1

VDS1 = VDS2 + VGS3 - VGS4 VDS1 = VDS2

W L

vg2 = vs3 = ix/gm2 vg3 = - gm1 vg2 rT (rT = RL //rds1)

if

VGS3 = VGS4

vx = ix/gm2 + (ix - gm3 vgs3) rds3

vx 1 gm 3 gm 3 rout = i = g + rds3 1 + g + g gm 1 rT x m2 m2 m2

Iout 1 IRef = W L

2

W 1 + V D S 2 L 1 = 1 + V D S 1 W L

gm3 rout rds3 g gm1rT m2 Higher voltage for the sensing branch (M1-M4) RL (i.e. Iref current generator impedance) must be large No sistematic error in the current gain

A. Baschirotto - Bias circuit

II 17

A. Baschirotto - Bias circuit

II 18

II Bias circuit

II Bias circuit

Improved Wilson current mirror

Iref M4 M1

Small signal equivalent circuit

g m 3 vgs3 1/g

m4 G3 G2 S3

Cascode Current Mirror

Current gain

Iout M3 M2

Iref M4 M1

Iout M3 M2

VDS1 = VDS2 + VGS3 - VGS4

ix

VDS1 = VDS2

W L

if

VGS3 = VGS4

W L

g R

L

m 1 g2

ds1

1/g

r ds3

m2

Same equations with: R L gm 4 vg3 = - gm1 vg2 r'T 1 + R g L m4 ' rT = rds1 //(RL + 1/gm4) gm3 R g 4 gm1 r'T 1 + L mg rout rds3 g RL m 4 m2 The output swing in the Wilson and improved Wilson schemes is limited to Vout,min = VGS2 + VDSsat,3 > VTh + 2VDSsat

1 + VD S 2 Iout 1 1 IRef = W 1 + V D S 1 = W L L

2 2

The current gain is accurate For large current ( i.e. with (W/L)M2 large) it allows to decrease the output capacitance using (W/L)M3 small.

A. Baschirotto - Bias circuit

II 19

A. Baschirotto - Bias circuit

II 20

II Bias circuit

II Bias circuit

Cascode Current Mirror Cascode Current Mirror

Output swing Output impedance

The output resistance is increased without feedback. Small signal equivalent circuit

Iref M4

VGS4 VGS1

Iout M3

VGS3 VDS3

R

L

G3 1/g

m4

g S3 r ds2

m 3 gs3

ix r ds3 v

1/g

M1

M2

m1

ix= gm3 vGS3+ (vx vS3)/rds3 VGS3 = VGS4 ix= vS3/rds2

The output swing is limited to: Vout,min = VGS1 + VGS4 VGS3 + VDSsat,3 Vout,min = VGS2 + VDSsat,3 > VTH + 2VDSsat

ix= gm3 ( vS3) + (vx vS3)/rds3 ix= vS3/rds2

rout = rds2 + rds3 + rds3 gm3 rds2 rds3 gm3 rds2

A. Baschirotto - Bias circuit

II 21

A. Baschirotto - Bias circuit

II 22

II Bias circuit

II Bias circuit

Multiple-Cascode Current Mirror

I Ref M9 I Out M8

Modified Cascode Current Mirror

Increase the output swing with the cascode output impedance

M5

M6

I Ref

I Out M3

M4

M3

V M1

M1

M2

M2

More cascode stage can be stacked to increase output impedance. For n stages + Output impedance rout (rds gm )n-1rds BUT: - The saturation voltage increses to: Vout,min = (n-1)VTH +nVDSsat + The current gain is accurate (VDS1= VDS2)

M4 shifts the voltage VDS1 of the amount enough to bias the gate of M3 without operating M2 out of saturation.

A. Baschirotto - Bias circuit

II 23

A. Baschirotto - Bias circuit

II 24

II Bias circuit

II Bias circuit

Modified Cascode Current Mirror

Possible implementation I Ref M4 M5 I Out M3

High-compliance current mirrors (I)

I Ref I Ref I Out M3

VTH+V

M4

M1

M6

M2

VTH+2V

M1

VTH+V

M2

M4 is matched with M3 to get VDS1 = VDS2 (at the cost of the output swing limitation). The output swing is improved by the use of a level shift VSat < V < VTH V = VGS4 - VGS5 =

All transistors operate in saturation I = I1 = I2 = I3 = I4 (current scaling is possible) 1=2=3= I4 = 4(Vov)2; Vov=V => Vov1 = Vov2 =Vov3 =Vov I3 = (Vov)2

2 L k'W IRef

4

L L W W

2 L k'W I5 =

5

1

I2 = (Vov)2; =>

VDS2 = Vov VGS3 = VTH + Vov VGS4 = VTH +2Vov

2 L IRef 1k'W 4

L L W W

Vov4 = Vov4 = 2Vov

V is fixed by he geometrical dimensions of M1, M6, M4, M5 and by Vov,4. The output swing is: Vout,min = VDS2 + VDS3 = 2VDSsat Sistematic error in the current gain (VDS1 VDS2)

I ; 4 =>

Vov =

= 44

W L M1 W L M2 W = L M3

I = 2 4

W = 4 L

M4

A. Baschirotto - Bias circuit

II 25

A. Baschirotto - Bias circuit

II 26

II Bias circuit

II Bias circuit

High-compliance current mirrors (I)

I Ref I Ref I Out M3

VTH+V

High-compliance current mirrors (II)

IBias I Ref M4 M5

M4

VTH+2V

I Out M3

M1

VTH+V

M2

M1 Current gain Sistematic error due to VDS1VDS2 Sistematic error due to body effect on M3 Output swing Vout,min = 2VDSsat Output impedance rout = rds4 gm2 rds2 The scheme can be stacked for multiple cascode M1=M2; M3=M4 => Iout=IRef

M2

VDSsat4>VTH to properly work

A. Baschirotto - Bias circuit

II 27

A. Baschirotto - Bias circuit

II 28

II Bias circuit

II Bias circuit

High-compliance current mirrors (II)

IBias I Ref M4 M5 I Out M3

Regulated-cascode current mirror

I Out I Ref M1 M3

A

M2

Vbias

M1

M2

Output impedance rout = (gm3ro3)ro2A Possible implementation

It is also possible to enter at the drain of M1 IBias I Bias2 M4 M5 I Ref M2 Output impedance

M3

IOut

Ibias

I Out M3

M1

IRef

M2

MA

M1

rout = (gm3ro3)ro2(gmAroA) Output swing Vout,min = VGSA+ VDSsat3

Iout = IBias2 + IRef

Vout,min = VTH + 2VDSsat Sistematic error since IrefIbias

(Solution proposed by Zeki, et al., IEE El. Letters, 5th June 1997, pp. 1042)

A. Baschirotto - Bias circuit

II 29

A. Baschirotto - Bias circuit

II 30

II Bias circuit

II Bias circuit

Low-voltage current mirror Output swing for different current mirrors

Comparison

1

For low-voltage application the dc voltage drops must be minimized in order to: - give the maximum room for the signal swing - not to limit the supply minimization with bias circuits This valid both for the input stage (reading the current) and for the output stage (sinking the current)

Id

Simple Cascode & Wilson 2 High-compliance Regulated Cascode

For the simple current mirror I Ref M1 I Out M2 VDSsat2

3 Triple Cascode

The output stage (M2) requires

2VTH+3VDSsat 2VDSsat VDSsat VTH+2VDSsat

VDS

Vout,min = VDSsat This is minimum, thus staked-device topologies are avoided Output impedance is increased with large L The input stage (M1) requires Vout,min = VTH + Vov + V(IRef)

The slope (1, 2, or 3) indicates the output impedance (rout)

This value can be reduced

A. Baschirotto - Bias circuit

II 31

A. Baschirotto - Bias circuit

II 32

II Bias circuit

II Bias circuit

Low-voltage current mirror

The input stage voltage requirement can be reduced by using the low-voltage current mirror

Low-voltage current mirror

Application

Operational amplifier

VDD Mb M4

Iref M3 Ibias M2 M1

Iout

Vi-

Vi+ Vo

M2

The drain of M1 is fixed to be VDD - VGS3 This is fixed to be equal to VDSsat The current mirror requires one VDSsat to operate.

Low-voltage current mirror

M1

Iout = IM3 + Iref

A. Baschirotto - Bias circuit

II 33

A. Baschirotto - Bias circuit

II 34

II Bias circuit

II Bias circuit

CMOS current mirrors

1Comparison Table 2rout rds

2 gmrds

Exercise

DC analysis of Simple CM AC analysis of Simple CM - Transfer function - Output impedance (for different L, with same W/L) 3Check the sistematic error in Wilson CM (different VDS) - Improve by using large L (with same W/L) - Check the signal swing (DC sim.) 4Cascode CM - Evaluate the output impedance (AC) - Evaluate the signal swing (DC) 5Multiple Cascode CM - Evaluate the output impedance (AC) - Evaluate the signal swing (DC) 6Large dynamic Cascode CM - Evaluate the output impedance (AC) - Evaluate the signal swing (DC) 7Low-voltage CM operation

Configuration Simple

Current gain 1 + VD S 2 1 + VD S 1 1 + VD S 2 1 + VD S 1 1 1 1 1 1 + VD S 2 1 + VD S 1 1 1 + VD S 2 1 + VD S 1

Output swing VDSsat VTH + 2VDSsat VTH + 2VDSsat VTH + 2VDSsat

Wilson

Improved Wilson Cascode Triple Cascode Triple Cascode High-compliance I

gmrds gmrds

2

2VTH + 3VDSsat g2 r3 m ds 2VTH + 3VDSsat g2 r3 m ds 2VDSsat 2VDSsat VTH + 2VDSsat

2 gmrds

High-compliance II Regulated-cascode

gmrds

2 3 gmrds

A. Baschirotto - Bias circuit

II 35

A. Baschirotto - Bias circuit

II 36

II Bias circuit

II Bias circuit

Current references

Introduction It allows to generte on-chip (no external components) a current reference Necessary for biasing analog subcircuits. The generated current reference is mirrored where required, with a suitable scaling factor. Typically the reference current in the reference current generator is much smaller than the current level in the main circuit (i.e. the scale factor is larger than one) in order to reduce power consumption in the current reference generator

Simple current reference

(supply depedent) NMOS

VDD IREF RL VB M1

IREF

PMOS

VDD M1 VB RL

Voltage VB is used to bias a current mirror For the NMOS case: IREF = |Vov1| = V DD V DS1 RL 2 I REF k' (W/L)1

Possible current reference generators Simple current reference (supply depedent) Current references based on a built-in voltage (supply indepedent) Current references based on a reference voltage (supply indepedent) Features for a reference current Supply dependence Temperature dependence Technology dependence

RL

IREF =

V DD |VTH1| |Vov1| RL

V DD |VTH1| IREF =

2 IREF k' (W/L)1

Supply dependence IREF depends on supply voltage VDD Temperature dependence positive temperature coefficient (TC) R 1: |VTH|: negative temperature coefficient |Vov|: positive temperature coefficient

II 37 A. Baschirotto - Bias circuit II 38

A. Baschirotto - Bias circuit

II Bias circuit

II Bias circuit

Typically the sum (VGS1=|VTH| + |Vov|) has a negative TC

Current references based on a built-in voltage

Basic principle The current is obtained by "extracting" a built-in voltage (Vbi) to be applied to a given resistor VDD VBIAS Built-in Voltage (Vbi) generator I=0 IREF Vbi R 1

Vbi IREF = R1 The dependence of the built-in voltage on temperature and other parameters will affect the generated reference current. The generated current is substantially independent from supply voltage. Micropower current reference based on this principle are also available.

A. Baschirotto - Bias circuit

II 39

A. Baschirotto - Bias circuit

II 40

II Bias circuit

II Bias circuit

Self-biased current reference

(V TH + Vov )-based

VDD M3 M4 M2 M1 R IREF VB

Self-biased current reference

(V TH + Vov )-based Start-up circuit

Built-in voltage:

VDD M3 M4 M2 M1 R IREF

VGS1

RI1

VTH

Vbi = VGS1 = VTH + Vov

VB

B I1

W L

W =L

(i.e. current mirror)

4

k' W I1 = I2 = 2 L (V GS1 V T H)2

1

I1 = I2 (for M3-M4 mirror) V GS1 k' W 2 R1 = 2 L (V GS1 V T H)

1

RI2 = RI1 = VGS1 =

Typically Vov is designed to be much smaller than VTH in order to have: VTH I1 R1 Low currents can be generated using large resistor (VTH+Vov in the range of 1 V) Temperature dependence R 1: positive TC VTH: negative TC Vov: positive TC (|(VTH) + |Vov|: negative TC) Complementary structure is always possible

A. Baschirotto - Bias circuit II 41

2I1 L k' W + VTH

1

Two operating points are possible (A, B) : only one (A) is the desired one It is necessary to use a startup circuitry to set the desired operating point (i.e. to ensure I 0 at the start-up) Possible start-up circuit solution

VDD M 3 I M 1 M 4 I M 2 VR1 R 1

START-UP Signal

VBIAS

At start-up, MS is turned on, thus forcing M4 in the saturation region. Then it is definitively turned off.

A. Baschirotto - Bias circuit

II 42

II Bias circuit

II Bias circuit

Self-biased low-current reference generator

Vov-based

VDD M3 M4 IREF VB M1 M2 R

Self-biased low-current reference generator

Vov-based

VDD M3 M4 IREF VB M1 M2 R

Temperature dependence: R 1: positive TC Vov: positive TC.

Built-in voltage: Vov = Vov1 Vov2

L W L L L = W ; W = m W

; m>1

2

I1=I3

slope k

I3=I4 I1=f(I2)

M3-M4 is an ideal current mirror => I3 = I4 = I1 = I2 = IREF VTH1 = VTH2

Also for this circuit a startup circuit is necessary

B

2IREF L k' W =

1

2IREF L k' W + RIREF

2

1

I2=I4

Complementary structure also available: M3, M4 n-channel transistors (source connected to VSS); M1, M2 p-channel transistors (source of M1 connected to VDD); R1 connected between source of M2 and VDD; in n-well processes, M1 and M2 in the same well.

IREF = R1

2 1 k' (W/L)

1 m

Vov generally ranges from tens to hundreds mV Small currents can be obtained with not very large R For m=10, VR 60 mV if it is required I = 1 A => R = 60k

A. Baschirotto - Bias circuit II 43

A. Baschirotto - Bias circuit

II 44

II Bias circuit

II Bias circuit

VBE-based current reference

VDD M 3 M 1

A B

VT-based current reference

(VBE-based current reference) Built-in voltage: VEB = VEB1 VEB2 = VT ln(n) M 3 M 1 I REF

1 n

M 4 Vbias M 2 VREF R 1

VDD M 4 M 2 R 1 Q 2

I Q1

Q1, Q2: substrate BJT with different emitter areas: Vbias AQ2 = nAQ1 n > 1

L W L L L = W ; W = W

Q1 is a substrate BJT M1 to M4 operate in saturation region (improved Wilson current mirror) (W/L)3 = (W/L)4, (W/L)1 = (W/L)2 I1 = I2 = IREF = I VGS1 = VGS2 => VS1 = VS2 => VEB I = R1 To generate low currents, a large R1 is needed (VEB in the range of 0.6 V) Start-up circuitry is needed Use the complementary structure for p-well processes Temperature dependence: R 1: positive TC VEB: negative TC

A. Baschirotto - Bias circuit II 45

I1 = I2 = IREF ; VA = VB I1 VEB1 = VT ln IS S I2 VEB2 = VT ln nISS

Q1

VREF = VEB

R1IREF = VEB1 VEB2 = VTR1 ln(n) VT IREF = R1 ln(n) Small currents can be obtained with small R1 Temperature dependence: R 1: positive TC V T: positive TC Start-up circuitry is needed Complementary structure available only in a p-well processes

A. Baschirotto - Bias circuit II 46

II Bias circuit

II Bias circuit

Current references based on a reference voltage

VREF VDD Vbias M1 I REF R 1

Voltage references

Introduction

Voltage references are required in a number of analog applications (e.g. signal processing, A/D converters, D/A converters, ...). Different voltage references Supply voltage dividers Voltage references based on a built-in voltage Voltage references based on the band-gap voltage Voltage references based on MOS threshold voltage difference

Useful when a reference voltage is available. This circuit has to operate at low-frequency (dc). The opamp gain can be extremely large. VREF IREF = R1 M1 in saturation region, for current mirror Temperature dependence: R 1: positive TC VREF: depends on the kind of voltage reference used It is difficult to obtain a stable VREF with a small value. => Low reference currents need large R1

A. Baschirotto - Bias circuit II 47 A. Baschirotto - Bias circuit II 48

(the last two types are actually special kinds of voltage references based on a built-in voltage).

In the following, all voltages will be referred to GND Features for a reference current Supply dependence Temperature dependence Technology dependence

II Bias circuit

II Bias circuit

Supply voltage divider

Resistive dividers

Supply voltage divider

Diode-connected NMOS transistors

Analog circuits normally have only two dc voltage supplies (VDD and ground) In order to obtain dc-bias voltages, voltage dividers can be used

Resistive or capacitive dividers are complex or silicon area consuming MOS in the diode configuration (i.e. operwting in saturation region) can be used VDD

VDD R1 VREF R2

M2 V1 M1 k' W 2 k' W 2 2 L (VDS1 VTH1) = 2 L (VDS2 VTH2)

1 2

VDS1 + VDS2 = VDD R2 VREF = R + R VDD = VDD 1 2 with < 1 Large power dissipation (small resistors) or large silicon area occupation (large resistors). VREF depends on supply voltage. To obtain good matching, R1 and/or R2 area realized by means of a suitable number of unity resistors V1 = VDS1 = 1V TH1 2V TH2 2 VDD + 1 + 2 1 + 2

1 =

W L

;

1

2 =

W L

It results a voltage division of VDD plus an offset. Body effect on M2 can affect the operation (VTH1VTH2)

A. Baschirotto - Bias circuit

II 49

A. Baschirotto - Bias circuit

II 50

II Bias circuit

II Bias circuit

MOS Supply voltage divider

Disturbs on the supply

Supply voltage divider

Diode-connected PMOS transistors VDD M1 VREF M2

If a signal vdd (usually undesired and so a disturb) is superposed to VDD , the small signal equivalent circuit must be considered.

vdd gmbvbs2 1/gm2 1/gds2 C2 v1 1/gm1 1/gds1 C1

C2 = Cgs2

C1 = Cgs1 + Cdb1 + Csb2 1 gm2 fz = 2 C2

1 gm1+gm2 fp = 2 C1+C2

At low frequency (assuming gm2 >> gds2 and gm1 >> gds1) there is a resistive partition (no capacitance effect): Body of M2 connected to source of M2 to avoid threshold voltage mismatches due to body effect Assuming VTH1 = VTH2 VTH VREF = VDS2 = 1 VDD + |VTH| 1 + 1 + gmb 1/g m1 + gm1gm2 v1lf = vdd 1/g m1 + 1/g m2 + g mb /(g m1 g m2 ) At high frequency there is a capacitive partition (no resistance effect) C2 v1hf = vdd C 1 + C 2

Vo/VDDnoise

fp fp

II

Several diode-connected transistors can be connected in series, if allowed by the supply voltage ("diode chain") to reduce current level for a given VTH

One of the two lines is valid depending if v1lf > v1hf (line I) or v1lf < v1hf (line II)

fz

fz

Frequency

It results a noise injection from the power supply (VDD)

A. Baschirotto - Bias circuit II 51 A. Baschirotto - Bias circuit II 52

II Bias circuit

II Bias circuit

Voltage references based on a built-in voltage

Basic principle Extraction of the chosen built-in voltage Vbi Generation of a current IR1 = Vbi/R1 Generation of a mirrored current IR2 = kIR1 Generation of the reference voltage VREF forcing IR 2 across a resistor R2, matched with R1 R2 VREF = R2IR2 = R2kIR1 = k R1 Vbi VDD

current mirror

(VTH+Vov)-based voltage reference

VDD M 3 M 4 I R1 M 2 VR1 R 1 R2 M5 I R2 VREF

M 1

Built-in voltage: Vth + Vov M1 to M5 in saturation region (W/L)3 = (W/L)4 I3 = I4 = I1 = I2 = IR1 (W/L)5 = k (W/L)4 IR2 = k IR1 R2 R2 VREF = k R1 VR1 = k R1 (VTH + Vov) Generally Vov is made much smaller than VTH Temperature dependence: VTH: negative TC Vov: positive TC (|(VTH) + |Vov|: negative TC)

Built-in Voltage (Vbi) generator

I=0 IR1 Vbi R 1

VREF IR2 R2

Extraction of the bult-in voltage as in current references based on a built-in voltage Temperature dependence of VREF : it is a function of the temperature dependence of Vbi

A. Baschirotto - Bias circuit II 53

Start-up circuitry needed Complementary structure available

A. Baschirotto - Bias circuit

II 54

II Bias circuit

II Bias circuit

VBE-based voltage reference

VDD M 3 M 1 VEB Q1 VR1 R 1 R2 M 4 I R1 M 2 M5 I R2 VREF

Voltage references based on the band-gap voltage

VDD I Q1 VBE VREF=VBE+mVT

VT Generation VT x m mVT

Basic principle VREF =VBE + mVT where VT = kT/q is the thermal voltage. Suitable choice of m to have zero TC at the desired operating temperature. At room temperature (T = 300 K): VBE: temperature dependence = ~2.2 mV/C VT: temperature dependence = ~+0.086 mV/C. If m = ~25.6 we have zero TC for VREF

Built-in voltage: VBE M1 to M5 in saturation region (W/L)3 = (W/L)4 => I3 = I4 = IR1 (W/L)1 = (W/L)2 => VR1 = VEB (W/L)5 = k (W/L)4 => IR2 = k IR1 R R VREF = k R2 VR1 = k R2 VEB 1 1

Temperature dependence: VBE: negative TC.

At T = 300 K we have: VREF = VBE + 25.6VT = ~1.26 V (silicon band-gap)

Start-up circuitry needed. Complementary structure for p-well processes.

A. Baschirotto - Bias circuit II 55 A. Baschirotto - Bias circuit

II 56

II Bias circuit

II Bias circuit

Band-gap voltage reference Band-gap voltage reference

R3

B

R 2 VDD

A

Compensation of temperature dependence Q1, Q2: substrate BJT with different emitter areas AQ2=nAQ1 n>1

-1.24 -1.25 -1.26

A VREF R 1

n

first-order small temperature range.

I

1

VR1 Q 2

Q1

Ref

[V]

VA = VB R2 = R3 => IR2 = IR3 = I = IQ1 = IQ2 VR1 = VEB1 VEB2 = VT ln(n) VR1 ln(n) I = R = VT R 1 1 R2 VREF = VEB1 + R VT ln(n) 1 VREF = VEB1 + mVT where R R A m = R2 ln(n) = R2 lnAQ2

1 1

-60 -40 -20 0

20 40

60 80 100 120 140 T [C]

For better compensation, more complex schemes are used. Scheme sensitive to offset voff of the operational amplifier: R 2 R2 voff VREF = VEB1 + 1 + R1 voff + R1 VT lnn1 + I2R2 Different (but matched) resistors R2 and R3 can also be used: R AQ R m = R2 lnR3 A 2 1 Q1 2 Generally, start-up circuitry is required. Similar configuration for p-well processes

Q1

For ambient temperature: m = ~25.6. Example: n = 8 => AQ2 = 8AQ1 (easy to obtain in layout) R2 = R3 = ~12.3 R1

A. Baschirotto - Bias circuit

II 57

A. Baschirotto - Bias circuit

II 58

II Bias circuit

II Bias circuit

Band-gap voltage reference

Band-gap voltage multiplier

VBG VDD VREF

Voltage references based on MOS threshold voltage difference

VDD M3 M4

D4

RA RB

D3

M1 and M2: transistors with equal k' and different threshold voltages, e. g.: both enhancement transistors with different VTH one enhancement and the other depletion transistor

I M1 VREF M2

To be used when VREF > 1.26 V is required R A VREF = VBG 1 + RB where VBG is the band-gap voltage. The multiplier can be included in the feedback loop.

VDD

VSS

M1 to M4 in saturation region VD3 = VD4 It follows that: (W/L)3 = (W/L)4 I3 = I4 = I1 = I2 I (W/L)1 = (W/L)2 Vov1 = Vov2 k'3 = k'4

VDD

Q1 VDD

Q2

R3

B

RA V RB VBG

REF

R2 VREF

A

R1 + A R2 R3

A R 1

n

VREF = VGS2 + VGS1 = VTH2 Vov2 + VTH1 + Vov1 VREF = VTH1 VTH2 VTH VTH is generally small. A voltage multiplier is required. Spread in threshold voltages, hence in VTH Offset of the operational amplifier affects VREF

II 59 A. Baschirotto - Bias circuit II 60

I

1

VR1

RA VBG RB

Q1

VSS

Q 2

For p-well processes. R A VREF = VBG 1 + RB

A. Baschirotto - Bias circuit

Anda mungkin juga menyukai

- Current MirrorsDokumen15 halamanCurrent Mirrorsashok815Belum ada peringkat

- EE42 100 Wb-Lecture19 080713-FDokumen37 halamanEE42 100 Wb-Lecture19 080713-FozanistzBelum ada peringkat

- Ecen 607 CMFB-2011Dokumen44 halamanEcen 607 CMFB-2011Girish K NathBelum ada peringkat

- Devices and Circuits Ii: Lecture GoalsDokumen6 halamanDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnBelum ada peringkat

- Fold-Cascode OPDokumen11 halamanFold-Cascode OPLinAm AmatariyakulBelum ada peringkat

- Current MirrorsDokumen76 halamanCurrent MirrorsSHRIDHAR N100% (1)

- Wide Swing Cascode Current MirrorDokumen4 halamanWide Swing Cascode Current MirrorSunil M. PaiBelum ada peringkat

- Lect 07 Differential AmpDokumen36 halamanLect 07 Differential AmpRogerZhangBelum ada peringkat

- 9.2 Schmitt TriggerDokumen11 halaman9.2 Schmitt TriggerlvsaruBelum ada peringkat

- Cur Mir 2 PDFDokumen3 halamanCur Mir 2 PDFamiglaniBelum ada peringkat

- 2.diode Clipper and ClamperDokumen12 halaman2.diode Clipper and ClamperMounika AllagaddaBelum ada peringkat

- 2019S Lec Ch9 CascodeStage&CurrentMirrors RevDokumen29 halaman2019S Lec Ch9 CascodeStage&CurrentMirrors Revp.비둘기폴더의비밀Belum ada peringkat

- Power Lab Manual 7th Sem 2011 - BGSDokumen109 halamanPower Lab Manual 7th Sem 2011 - BGSSumanth Sathyanarayana100% (1)

- IGCT TrainingDokumen57 halamanIGCT TrainingVivek KumarBelum ada peringkat

- Differential and Multistage AmplifiersDokumen85 halamanDifferential and Multistage AmplifiersShino JosephBelum ada peringkat

- EEEB273 N10 - Simplified Opamp x6Dokumen3 halamanEEEB273 N10 - Simplified Opamp x6gahbi7Belum ada peringkat

- Chap05 (7 5 06)Dokumen60 halamanChap05 (7 5 06)Amar NathBelum ada peringkat

- XR 2206 V 1Dokumen16 halamanXR 2206 V 1Leon F AceroBelum ada peringkat

- Lec17 MOSFET IVDokumen49 halamanLec17 MOSFET IVBlanca MeLendezBelum ada peringkat

- 4 Study of Characteristics of SCR, MOSFET & IGBTDokumen12 halaman4 Study of Characteristics of SCR, MOSFET & IGBTSeminars BRECWBelum ada peringkat

- Multi Stage Amplifier (L 1)Dokumen21 halamanMulti Stage Amplifier (L 1)SauravAbidRahmanBelum ada peringkat

- Power Electronics Slides and Notes DC ConvertersDokumen40 halamanPower Electronics Slides and Notes DC ConvertersAnoop MathewBelum ada peringkat

- Data Sheet: Silicon MMIC AmplifierDokumen13 halamanData Sheet: Silicon MMIC AmplifierjohnysonycumBelum ada peringkat

- ICMOSFETDokumen96 halamanICMOSFETthamy_15Belum ada peringkat

- MOSFET Lab Explores Amplifier and Inverter CircuitsDokumen9 halamanMOSFET Lab Explores Amplifier and Inverter CircuitsamngreenBelum ada peringkat

- Lecture17 Fully Diff Amps CMFBDokumen28 halamanLecture17 Fully Diff Amps CMFBmohamedBelum ada peringkat

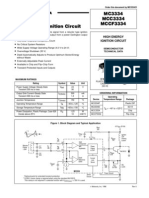

- Datasheet MC3334Dokumen6 halamanDatasheet MC3334odipasBelum ada peringkat

- Microwave Engineering Microwave Networks What Are Microwaves 589Dokumen26 halamanMicrowave Engineering Microwave Networks What Are Microwaves 589nigaar1242100% (1)

- Why Use Differential Amplifiers?: EECS 105 Fall 1998Dokumen10 halamanWhy Use Differential Amplifiers?: EECS 105 Fall 1998Nishant GhoshBelum ada peringkat

- EC410 Fall 2012 FinalDokumen8 halamanEC410 Fall 2012 FinalRabee Adil JamshedBelum ada peringkat

- A Low Voltage High Performance OTA in 0.18 Micron With High LinearityDokumen10 halamanA Low Voltage High Performance OTA in 0.18 Micron With High LinearitymohsenparsauniBelum ada peringkat

- Electronics design II amplifier calculationsDokumen14 halamanElectronics design II amplifier calculationsbhanuBelum ada peringkat

- Irams 06 Up 60 ADokumen18 halamanIrams 06 Up 60 AAndré Roberto EvangelistaBelum ada peringkat

- Data Sheet: BF998 BF998RDokumen12 halamanData Sheet: BF998 BF998Rachew911Belum ada peringkat

- DEPT. of Computer Science Engineering SRM IST, Kattankulathur - 603 203Dokumen6 halamanDEPT. of Computer Science Engineering SRM IST, Kattankulathur - 603 203yash rawat (RA1911031010029)Belum ada peringkat

- Mitsubishi SemiconductorDokumen8 halamanMitsubishi Semiconductoredgardo2004Belum ada peringkat

- EE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignDokumen39 halamanEE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignBharat Kumar100% (1)

- 1Dokumen43 halaman1Adithya ChandrasekaranBelum ada peringkat

- Electronics Circuit Design LabDokumen34 halamanElectronics Circuit Design Labsrvdhar100% (1)

- Design 4 SpaceDokumen27 halamanDesign 4 SpacepodericofBelum ada peringkat

- Electric Power and Power ElectronicsDokumen144 halamanElectric Power and Power ElectronicsmnamkyBelum ada peringkat

- 1diode PN SKDokumen37 halaman1diode PN SKKurma RaoBelum ada peringkat

- Smps For CRT Monitors With The L6565: AN1657 Application NoteDokumen9 halamanSmps For CRT Monitors With The L6565: AN1657 Application Noterdc02271Belum ada peringkat

- Current MirrorDokumen7 halamanCurrent MirrorSatyasheel SinghBelum ada peringkat

- L060 Push Pull (2UP)Dokumen10 halamanL060 Push Pull (2UP)srikanthkmsBelum ada peringkat

- 1 To 5 ManualDokumen30 halaman1 To 5 ManualRoshan DodiyaBelum ada peringkat

- L330 LowPowerOpAmps 2UPDokumen7 halamanL330 LowPowerOpAmps 2UPVan Nguyen Huu VanBelum ada peringkat

- Super Source FollowerDokumen27 halamanSuper Source Followerkhlsakfn100% (2)

- Power Devices and IGBT CharacteristicsDokumen38 halamanPower Devices and IGBT CharacteristicsKien Trung50% (2)

- 607 ACM Extraction ParametersDokumen23 halaman607 ACM Extraction ParametersAMSA84Belum ada peringkat

- ADC Power Scaling: Design Issues: Amit Tripathi Faculty of Deptt. of EN NIET, Gr. NoidaDokumen17 halamanADC Power Scaling: Design Issues: Amit Tripathi Faculty of Deptt. of EN NIET, Gr. Noidaer_amittripathiBelum ada peringkat

- Linear Wave Shaping: Department of Electronics and Communication EngineeringDokumen0 halamanLinear Wave Shaping: Department of Electronics and Communication EngineeringanishadandaBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesDari EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesPenilaian: 4.5 dari 5 bintang4.5/5 (7)

- 110 Waveform Generator Projects for the Home ConstructorDari Everand110 Waveform Generator Projects for the Home ConstructorPenilaian: 4 dari 5 bintang4/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsDari EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsBelum ada peringkat

- Project - Review ThermoelectricDokumen30 halamanProject - Review ThermoelectricAbhishek KumarBelum ada peringkat

- 01-Jan-2020 Shift B Logbook Operator PakseDokumen1 halaman01-Jan-2020 Shift B Logbook Operator PakseLove Buddha's WordsBelum ada peringkat

- Compact DX Training Manual PDFDokumen239 halamanCompact DX Training Manual PDFChrisBelum ada peringkat

- Csyc12mkf Operating Instructions ManualDokumen16 halamanCsyc12mkf Operating Instructions ManualcoronaqcBelum ada peringkat

- mx2-v1 I920-E1 9 1 csm1010813Dokumen48 halamanmx2-v1 I920-E1 9 1 csm1010813truongthang87Belum ada peringkat

- 16BT70408 - Low Power Cmos Vlsi DesignDokumen1 halaman16BT70408 - Low Power Cmos Vlsi DesignS KkBelum ada peringkat

- Rolling Door Operator ManualDokumen8 halamanRolling Door Operator ManualHector MoragaBelum ada peringkat

- Cacl P 001Dokumen5 halamanCacl P 001rize1159100% (1)

- UA6176 ManualDokumen46 halamanUA6176 ManualmpewebBelum ada peringkat

- Fuzzy Logic Implementation With MATLAB For PV-wind Hybrid SystemDokumen13 halamanFuzzy Logic Implementation With MATLAB For PV-wind Hybrid SystemZainal AbidinBelum ada peringkat

- How to Use a Tester Screwdriver to Check Electrical Equipment SafetyDokumen2 halamanHow to Use a Tester Screwdriver to Check Electrical Equipment SafetyrkhayrenBelum ada peringkat

- Electrode IDentificationDokumen3 halamanElectrode IDentificationAmit AgarwalBelum ada peringkat

- Ac Motor Controllers/Display Panel: Description, Checks, Adjustments, and TroubleshootingDokumen98 halamanAc Motor Controllers/Display Panel: Description, Checks, Adjustments, and TroubleshootingCristian Elías Cruces Caamaño100% (1)

- En SF Kel C6a P XXXSFDokumen2 halamanEn SF Kel C6a P XXXSFNaipe DobleutesBelum ada peringkat

- 04-06 T1 VW Touareg HID Conversion DIYDokumen4 halaman04-06 T1 VW Touareg HID Conversion DIYMiriam Zahir100% (1)

- Samsung La 22 26 32 C450e1 PDFDokumen100 halamanSamsung La 22 26 32 C450e1 PDFadi0% (2)

- Critical Components Table Rev35Dokumen5 halamanCritical Components Table Rev35ashishtrueBelum ada peringkat

- Gaurav - Report - 18EE33001 - BTP - Midterm ReportDokumen20 halamanGaurav - Report - 18EE33001 - BTP - Midterm ReportGaurav BisenBelum ada peringkat

- ICL7135Dokumen16 halamanICL7135JIGNESHBelum ada peringkat

- TM221CE24RDokumen19 halamanTM221CE24RRefaldyBelum ada peringkat

- Modelling and Simulation of Matrix Converter Based DC-DC ConverterDokumen5 halamanModelling and Simulation of Matrix Converter Based DC-DC ConverternivedhaBelum ada peringkat

- Low-Cost 270 MHZ Differential Receiver Amplifiers: S at G 1 S at G 10Dokumen28 halamanLow-Cost 270 MHZ Differential Receiver Amplifiers: S at G 1 S at G 10flo72afBelum ada peringkat

- AHD 414 Start-Stop-Diesel Control UnitDokumen9 halamanAHD 414 Start-Stop-Diesel Control UnitAL KUSCUBelum ada peringkat

- PNR Porcelain Bushing Brochure 33209 EN A4 202112 R002Dokumen9 halamanPNR Porcelain Bushing Brochure 33209 EN A4 202112 R002setiyawanBelum ada peringkat

- Solved Problems in Electric MotorsDokumen6 halamanSolved Problems in Electric Motorssumithra93% (15)

- Insigina 42p650a11 SVCDokumen50 halamanInsigina 42p650a11 SVCDamon BrungerBelum ada peringkat

- Technical Manual Technical Manual Technical Manual Technical ManualDokumen73 halamanTechnical Manual Technical Manual Technical Manual Technical Manualcomphome13100% (2)

- SSV Cougar XTC Operatorsl Technical Training Syllabus PDFDokumen7 halamanSSV Cougar XTC Operatorsl Technical Training Syllabus PDFlchurch13Belum ada peringkat

- Lab ManualDokumen7 halamanLab Manualdurgesh choudharyBelum ada peringkat

- XP3 16 ManualDokumen50 halamanXP3 16 Manualesakkiraj1590Belum ada peringkat