Relatorio 09

Diunggah oleh

Ataias Pereira ReisJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Relatorio 09

Diunggah oleh

Ataias Pereira ReisHak Cipta:

Format Tersedia

UnB

Universidade de Bras lia

Universidade de Bras - UnB lia Departamento de Cincias da Computao - CIC e ca Disciplina: 116351 - Circuitos Digitais; Turma: B Professores: Camilo Chang Dorea Mrcio da Costa Pereira Brando a a

Relatorio 9 Flip-ops T e D

Alunos: Ata Pereira Reis as Joo Guilherme Lo a e 10/0093817 10/0107265

25 de maio de 2012

UnB

Universidade de Bras lia

Indice

1 Objetivos 2 Materiais 3 Introduo ca 4 Procedimentos 5 Dados 6 Anlise dos Dados a 7 Concluso a Referncias e 3 3 3 4 5 9 9 10

25 de maio de 2012

UnB

Universidade de Bras lia

Objetivos

Entender conceitos bsicos de ip-ops T e D de forma prtica, por meio a a da anlise das sa a dasdos mesmos. Construir ip-ops usando portas NAND e NOT.

Materiais

Painel digital Protoboard Fios conectores Portas NAND e NOT. Alicate Ponta lgica o

Introduo ca

Flip-op T Se a entrada T estiver em estado alto, o ip-op T (toggle) inverte seu estado sempre que a entrada de clock sofrer uma modicao. Se a entrada ca T foi baixa, o ip-op mantm o valor do seu estado. e

Flip-op D (Data) O ip-op D (data ou dado, pois armazena o bit de entrada) possui uma entrada, que ligada diretamente ` sa quando o clock e a da mudado. Independentemente do valor atual da sa e da, ele ir assumir o valor a 1 se D = 1 quando o clock for mudado ou o valor 0 se D = 0 quando o clock for mudado. Este ip-op pode ser interpretado como uma linha de atraso primitiva ou um hold de ordem zero, visto que a informao colocada na sa um ciclo ca e da depois de ela ter chegado na entrada.

25 de maio de 2012

UnB

Universidade de Bras lia

Procedimentos

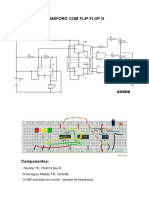

Primeiramente, foi testado o funcionamento da protoboard. Escolhida uma protoboard que funciona-se, o circuito passou a ser montados utilizando-se os CIs 7400 e 7404. Depois, iniciaram-se os passos para montagem dos ip-ops. 1. O primeiro ip-op montado foi o T. O circuito montado nesta etapa foi feito seguindo o diagrama lgico da gura 1a. Aps ter sido montado, foi o o vericada sua tabela verdade. 2. O segundo ip-op D gatilhado por n vel. O circuito montado foi feito seguindo-se o diagrama lgico da gura 2a. Aps a montagem, foi verio o cada sua tabela verdade. 3. O terceiro ip-op montado foi o ip-op tipo D gatilhado pela borda positiva. Foi feito conforme gura 3a, depois foi vericada sua tabela verdade. 4. O ultimo procedimento experimental foi vericar o tempo de setup do ip-op tipo D gatilhado pela borda positiva. Foi feito conforme gura 4.

25 de maio de 2012

UnB

Universidade de Bras lia

Dados

1. Flip-flop T (a) Diagrama lgico o

Figura 1: Flip-op T implementado com portas NAND (b) Tabelas Verdade T 0 1 Qn+1 Qn Qn

Tabela 1: Tabela Esperada

25 de maio de 2012

UnB

Universidade de Bras lia

2. Flip-flop D gatilhado por n vel (a) Diagrama lgico o

Figura 2: Diagrama Lgico - Flip-op D gatilhado por n o vel (b) Tabela Verdade Clk 0 0 1 1 D 0 1 0 1 Qn+1 Qn Qn Qn 0

Tabela 2: Tabela da verdade do ip-op D gatilhado

25 de maio de 2012

UnB

Universidade de Bras lia

3. Flip-flop D gatilhado pela borda (a) Diagrama lgico o

Figura 3: Implementao de um ip-op D gatilhado pela borda positiva com ca portas NAND (b) Tabela Verdade Clk D X 0 1 Qn+1 Qn 0 1

Tabela 3: Tabela da verdade do ip-op D gatilhado pela borda positiva

25 de maio de 2012

UnB

Universidade de Bras lia

4. TEMPO DE SET UP

Figura 4: Vericao experimental do tempo de setup com um ip-op D gatica lhado pela borda positiva

A sa sempre cava em um nesta etapa. da

25 de maio de 2012

UnB

Universidade de Bras lia

Anlise dos Dados a

1: O ip-op tipo D seguiu as especicaes da tabela verdade, s cou confusa co o na implementao e compreenso deste ip op no se saber qual o primeiro ca a a valor tomado por Qn , que poderia ser dado ao acaso a cada vez que se ligava o aparelho. 2: O ip-op tipo D gatilhado por n j retirava esse problema de no podervel a a se escolher Qn . Com isso, mantinha-se o valor de clock num n xo e o valor vel de Qn seria entrada caso clk = 1 e mostraria Qn como sa caso clk = 0. A da tabela verdade do ip-op foi vericada. 3: O ip op tipo D gatilhado por n ainda apresenta problemas caso exisvel tam glitches no sinal, que nem sempre so poss a veis de se eliminar. Nesse ip-op gatilhado por n esse problema mais controlvel, mas o sinal ter de ser selevel e a a cionado em um certo tempo de clock e obedecer a um certo tempo tsetup no qual o sinal tem de estar estvel e um certo tempo thold que o sinal tem de se manter a estvel aps o evento de clock. Foi vericado este ip-op, sua montagem foi a o bem sucedida e obedecida a tabela verdade. 4: Nesta etapa, se vericou o tempo de setup para o ip-op tipo D gatilhado pela borda positiva. Como o tempo de setup t pico de 20ns, e o clock estava e mudando s 40ns depois, o valor cava xo em 1, que comprova que o tempo o de setup menor que 40ns. e

Concluso a

A partir do experimento, pode-se analisar o funcionamento dos ip-ops dos tipos T e D, e comparar com os ip-ops do experimento anterior, alm de e entender quando e porqu utiliz-los. Alm disso, pode-se compreender as pare a e ticularidades de cada ip-op, a m de utiliz-los em determinadas situaes a co compat veis com seu design.

25 de maio de 2012

UnB

Universidade de Bras lia

Referncias e

[1] Sistemas digitais: princ pios e aplicaes, 10a edio / Ronald. J. Tocci, co ca Neal S. Widmer, Gregory L. Moss; traduo: Cludia Martins; reviso ca a a tcnica: Joo Antonio Martino. 10a ed. So Paulo : Pearson Prentice e a a Hall, 2007 [2] Digital Design: Principles & Practices, Third Edition / John F. Wakerly Prentice Hall

25 de maio de 2012

10

Anda mungkin juga menyukai

- State Space ReductionDokumen14 halamanState Space ReductionAtaias Pereira ReisBelum ada peringkat

- Relatório de Trabalho de Graduação 1Dokumen47 halamanRelatório de Trabalho de Graduação 1Ataias Pereira ReisBelum ada peringkat

- Solução Numérica Da Equação de Navier StokesDokumen12 halamanSolução Numérica Da Equação de Navier StokesAtaias Pereira ReisBelum ada peringkat

- Solução Numérica Da Equação de Navier StokesDokumen12 halamanSolução Numérica Da Equação de Navier StokesAtaias Pereira ReisBelum ada peringkat

- Relatório de PIBIC 2013Dokumen10 halamanRelatório de PIBIC 2013Ataias Pereira ReisBelum ada peringkat

- Roteiro 1Dokumen3 halamanRoteiro 1Ataias Pereira ReisBelum ada peringkat

- Navier StokesDokumen5 halamanNavier StokesAtaias Pereira ReisBelum ada peringkat

- programaCD 2012 01Dokumen3 halamanprogramaCD 2012 01Ataias Pereira ReisBelum ada peringkat

- Re La To Rio 01Dokumen14 halamanRe La To Rio 01Ataias Pereira ReisBelum ada peringkat

- KirchhoffDokumen2 halamanKirchhoffEverton BertoBelum ada peringkat

- ExercÃ-cios ResExercÃ-cios ResolvidoolvidosDokumen77 halamanExercÃ-cios ResExercÃ-cios ResolvidoolvidosGian Do Atacado Silveira0% (1)

- Circuitos com diodos: exercícios resolvidosDokumen13 halamanCircuitos com diodos: exercícios resolvidosDaniel Malinda100% (1)

- Flip-flops e dispositivos de memóriaDokumen85 halamanFlip-flops e dispositivos de memóriaCarllos LimmaBelum ada peringkat

- ESTO001 CircuitoseFotonica A04Dokumen19 halamanESTO001 CircuitoseFotonica A04Bruna Giovannini PradoBelum ada peringkat

- Familia Logica TTL e CMOSDokumen12 halamanFamilia Logica TTL e CMOSEduardo Junior GuambeBelum ada peringkat

- Analise Nodal e de MalhasDokumen18 halamanAnalise Nodal e de MalhasJerison Dias PiresBelum ada peringkat

- Amp OpDokumen5 halamanAmp OpeduardohcmendesBelum ada peringkat

- Semáforo com flip flop DDokumen3 halamanSemáforo com flip flop DPublia de la Sota50% (2)

- Inteligência artificial: O guia completo para iniciantes sobre o futuro da IADari EverandInteligência artificial: O guia completo para iniciantes sobre o futuro da IAPenilaian: 5 dari 5 bintang5/5 (6)

- Orientação a Objetos em C#: Conceitos e implementações em .NETDari EverandOrientação a Objetos em C#: Conceitos e implementações em .NETPenilaian: 5 dari 5 bintang5/5 (1)

- Arquitetura de software distribuído: Boas práticas para um mundo de microsserviçosDari EverandArquitetura de software distribuído: Boas práticas para um mundo de microsserviçosBelum ada peringkat

- Inteligência artificial: Análise de dados e inovação para iniciantesDari EverandInteligência artificial: Análise de dados e inovação para iniciantesBelum ada peringkat

- Inteligência artificial: Como aprendizado de máquina, robótica e automação moldaram nossa sociedadeDari EverandInteligência artificial: Como aprendizado de máquina, robótica e automação moldaram nossa sociedadePenilaian: 5 dari 5 bintang5/5 (3)

- Análise técnica de uma forma simples: Como construir e interpretar gráficos de análise técnica para melhorar a sua actividade comercial onlineDari EverandAnálise técnica de uma forma simples: Como construir e interpretar gráficos de análise técnica para melhorar a sua actividade comercial onlinePenilaian: 4 dari 5 bintang4/5 (4)