How To Design A Controller To Produce Signals To Control The Datapath

Diunggah oleh

Narender KumarDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

How To Design A Controller To Produce Signals To Control The Datapath

Diunggah oleh

Narender KumarHak Cipta:

Format Tersedia

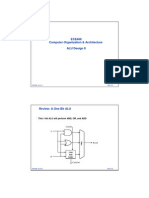

Recap: The MIPS Instruction Formats

All MIPS instructions are 32 bits long. The three instruction formats:

31 26 op 6 bits 31 op 6 bits 31 op 6 bits 26 target address 26 bits 26 rs 5 bits rs 5 bits 21 rt 5 bits 21 rt 5 bits 16 immediate 16 bits 0 16 rd 5 bits 11 shamt 5 bits 6 funct 6 bits 0 0

ECE4680 Computer Organization and Architecture Designing Single Cycle Control

R-type I-type J-type

How to design a controller to produce signals to control the datapath

The different fields are: op: operation of the instruction rs, rt, rd: the source and destination registers specifier shamt: shift amount funct: selects the variant of the operation in the op field address / immediate: address offset or immediate value target address: target address of the jump instruction

ECE4680 Control.1

2003-3-17

ECE4680 Control.2

2003-3-17

Recap: The MIPS Subset

ADD and subtract add rd, rs, rt sub rd, rs, rt

31 26 op 6 bits 21 rs 5 bits 16 rt 5 bits immediate 16 bits 0 31 op 6 bits 26 rs 5 bits 21 rt 5 bits 16 rd 5 bits 11 shamt 5 bits 6 funct 6 bits 0

Recap: A Single Cycle Datapath

We have everything except control signals (underline) Todays lecture will show you how to generate the control signals

Branch Rd RegDst Rt Rs 5 5 busA 32 0 Mux ALU Rt Jump Clk Instruction Fetch Unit Instruction<31:0> <11:15> <21:25> <16:20> <0:15>

OR Imm: ori rt, rs, imm16 LOAD and STORE lw rt, rs, imm16 sw rt, rs, imm16 BRANCH: beq rs, rt, imm16 JUMP: j target

31

1 Mux 0 RegWr 5 ALUctr

Rs Zero

Rt

Rd

Imm16 MemtoReg 0 Mux

busW 32 Clk

Rw Ra Rb 32 32-bit Registers busB 32 Extender

MemWr

32 32 WrEn Adr Data Memory

Data In 32 Clk

1 32 ALUSrc

26 op 6 bits target address 26 bits

2003-3-17

imm16

16

ExtOp

ECE4680 Control.3 ECE4680 Control.4 2003-3-17

The Big Picture: Where are We Now?

The Five Classic Components of a Computer

Processor Input Control Memory Datapath

RTL: The ADD Instruction

31 op 6 bits 26 rs 5 bits 21 rt 5 bits 16 rd 5 bits 11 shamt 5 bits 6 funct 6 bits 0

add

rd, rs, rt Fetch the instruction from memory The actual operation Calculate the next instructions address

mem[PC]

Output

R[rd] <- R[rs] + R[rt] PC <- PC + 4

Todays Topic: Designing the Control for the Single Cycle Datapath A note: 2nd step and 3rd step can be done in parallel.

ECE4680 Control.5

2003-3-17

ECE4680 Control.6

2003-3-17

Instruction Fetch Unit at the Beginning of Add / Subtract

Fetch the instruction from Instruction memory: Instruction This is the same for all instructions

30 Addr<31:2> PC<31:28> Target 4 Instruction<25:0> 26 PC Clk imm16 Instruction<15:0> 16

ECE4680 Control.7

The Single Cycle Datapath during Add and Subtract

31 26 op rs 21 rt 16 rd 11 shamt 6 funct 0

mem[PC]

R[rd] <- R[rs] + / - R[rt]

Branch = 0 30 00 30 1 Mux 0 Addr<1:0> Instruction Memory 32 Rd RegDst = 1 Rt Rs 5 5 busA 32 0 Mux ALU Jump = 0 Clk Rt Instruction Fetch Unit ALUctr = Add or Subtract Instruction<31:0> <11:15> <21:25> <16:20> <0:15>

1 Mux 0

RegWr = 1 5 busW 32 Clk

Rs Zero

Rt

Rd

Imm16 MemtoReg = 0

30 1

0 30 Adder Mux

1 30

Jump = previous Instruction<31:0>

Rw Ra Rb 32 32-bit Registers busB 32 Extender

MemWr = 0 0 Mux 32

Instruction Fetch Unit at the End of Add and Subtract

PC <- PC + 4 This is the same for all instructions except: Branch and Jump

30 Addr<31:2> PC<31:28> Target 4 Instruction<25:0> 26 PC Clk imm16 Instruction<15:0> 16

ECE4680 Control.9

Adder SignExt 30

32 WrEn Adr

1 32

imm16 Branch = previous Zero = previous

Data In 32 Clk

16

Data Memory

ALUSrc = 0 ExtOp = x

2003-3-17 ECE4680 Control.8 2003-3-17

The Single Cycle Datapath during Or Immediate

31 op 26 rs 21 rt 16 immediate 0

R[rt] <- R[rs] or ZeroExt[Imm16]

Branch = 0 Instruction<31:0> <11:15> Instruction Fetch Unit <21:25> <16:20> <0:15>

30 00 30 1 Mux 0

Addr<1:0> Instruction Memory 32

Rd RegDst = 0

Rt Rs 5 5

Jump = 0 Clk Rt busA 32 0 Mux

1 Mux 0 ALUctr = Or

RegWr = 1 5 busW 32 Clk

Rs Zero ALU

Rt

Rd

Imm16 MemtoReg = 0

30 1

0 30 Adder Mux

1 30

Jump = 0

Instruction<31:0>

Rw Ra Rb 32 32-bit Registers busB 32 Extender

MemWr = 0 0 Mux 32

The Single Cycle Datapath during Load

31 op 26 rs 21 rt 16 immediate 0

R[rt] <- Data Memory {R[rs] + SignExt[imm16]}

Branch = 0 Rd RegDst = 0 Rt Rs 5 5 busA 32 0 Mux ALU Jump = 0 Clk Rt Instruction Fetch Unit ALUctr = Add Instruction<31:0> <11:15> <21:25> <16:20> <0:15>

Adder SignExt 30

32 WrEn Adr

1 32

imm16 Branch = 0 Zero = x

Data In 32 Clk

16

Data Memory

ALUSrc = 1 ExtOp = 0

2003-3-17 ECE4680 Control.10 2003-3-17

The Single Cycle Datapath during Store

31 op 26 rs 21 rt 16 immediate 0

Data Memory {R[rs] + SignExt[imm16]} <- R[rt]

Branch = 0 Rd RegDst = x Rt Rs 5 5 busA 32 0 Mux ALU Jump = 0 Clk Rt Instruction Fetch Unit ALUctr = Add Instruction<31:0> <11:15> <21:25> <16:20> <0:15>

1 Mux 0

1 Mux 0

RegWr = 1 5 busW 32 Clk

Rs Zero

Rt

Rd

Imm16 MemtoReg = 1

RegWr = 0 5 busW

Rs Zero

Rt

Rd

Imm16 MemtoReg = x

Rw Ra Rb 32 32-bit Registers busB 32 Extender

MemWr = 0 0 Mux 32 Clk

32 WrEn Adr

Rw Ra Rb 32 32-bit Registers busB 32 Extender

MemWr = 1 0 Mux 32

32 WrEn Adr

1 32 imm16 16

1 32

imm16

Data In 32 Clk

16

Data Memory

1 32

Data In 32 Clk

Data Memory

ALUSrc = 1 ExtOp = 1

ECE4680 Control.11 2003-3-17 ECE4680 Control.12

ALUSrc = 1 ExtOp = 1

2003-3-17

The Single Cycle Datapath during Branch

31 op 26 rs 21 rt 16 immediate 0

Instruction Fetch Unit at the End of Branch

31 op 26 rs 21 rt 16 immediate 0

if (R[rs] - R[rt] == 0) then Zero <- 1 ; else Zero <- 0

Branch = 1 Rd RegDst = x Rt Rs 5 5 5 Jump = 0 Clk Rt Instruction Fetch Unit ALUctr = Subtract Instruction<31:0> <11:15> <21:25> <16:20> <0:15>

if (Zero == 1) then PC = PC + 4 + SignExt[imm16]*4 ; else PC = PC + 4

30 Addr<31:2> PC<31:28> Target Instruction<25:0> PC 30 1 Clk imm16 Instruction<15:0> 16 Adder 4 30 26 0 30 Adder Mux 30 00 1 Mux Addr<1:0> Instruction Memory 32

1 Mux 0

RegWr = 0

Rs Zero

Rt

Rd

Imm16 MemtoReg = x

busW 32 Clk

busA Rw Ra Rb 32 32 32-bit Registers busB 0 32 Extender 1 32

MemWr = 0 0 Mux 32

ALU

32 WrEn Adr

1 30

Jump = 0

Instruction<31:0>

Mux Data In 32 Clk

SignExt

imm16

16

Data Memory

30 Assume Zero = 1 to see the interesting case. Branch = 1 Zero = 1

2003-3-17

ALUSrc = 0 ExtOp = x

ECE4680 Control.13 2003-3-17 ECE4680 Control.14

The Single Cycle Datapath during Jump

31 op 26 target address 0

Instruction Fetch Unit at the End of Jump

31 op 26 target address 0

Nothing to do! Make sure control signals are set correctly!

Branch = 0 Rd RegDst = x Rt Rs 5 5 Zero ALU MemWr = 0 0 Mux 32 WrEn Adr Data In 32 Clk ALUSrc = x ExtOp = x

ECE4680 Control.15 2003-3-17

PC <- PC<31:29> concat target<25:0> concat 00

30 <0:15> Addr<31:2> PC<31:28> Target Instruction<25:0> PC 30 1 Clk imm16 Instruction<15:0> 16 Adder 4 30 26 0 30 Adder Mux 30 00 1 Mux Addr<1:0> Instruction Memory 32 <11:15>

Instruction<31:0> Instruction Fetch Unit ALUctr = x <21:25> <16:20>

Jump = 1 Clk Rt

1 Mux 0

RegWr = 0 5 busW 32 Clk

Rs

Rt

Rd

Imm16 MemtoReg = x

busA Rw Ra Rb 32 32 32-bit Registers busB 0 32 Extender 1 32

32

1 30

Jump = 1

Instruction<31:0>

Mux

SignExt

imm16

16

Data Memory

30

Branch = 0

ECE4680 Control.16

Zero = x

2003-3-17

A Summary of the Control Signals

See Appendix A RegDst ALUSrc MemtoReg RegWrite MemWrite Branch Jump ExtOp ALUctr<2:0> 31 R-type I-type J-type

ECE4680 Control.17

The Concept of Local Decoding

op RegDst ALUSrc MemtoReg RegWrite MemWrite Branch Jump ExtOp ALUop<N:0> 00 0000 R-type 1 0 0 1 0 0 0 x R-type 00 1101 10 0011 10 1011 00 0100 00 0010 ori 0 1 0 1 0 0 0 0 Or lw 0 1 1 1 0 0 0 1 Add sw x 1 x 0 1 0 0 1 Add beq x 0 x 0 0 1 0 x Subtract jump x x x 0 0 0 1 x xxx

We Dont Care :-) func 10 0000 10 0010 op 00 0000 00 0000 00 1101 10 0011 10 1011 00 0100 00 0010 add 1 0 0 1 0 0 0 x Add sub 1 0 0 1 0 0 0 x Subtract 21 rs rs rt rt target address ori 0 1 0 1 0 0 0 0 Or 16 rd lw 0 1 1 1 0 0 0 1 Add 11 shamt immediate sw x 1 x 0 1 0 0 1 Add 6 funct beq x 0 x 0 0 1 0 x Subtract jump x x x 0 0 0 1 x xxx

func 26 op op op 0 add, sub ori, lw, sw, beq jump

2003-3-17 ECE4680 Control.18

op 6

Main Control

6 ALUop N

ALU Control (Local)

ALUctr 3 ALU

2003-3-17

The Encoding of ALUop

op 6 Main Control func 6 ALUop N ALU Control (Local) ALUctr 3

The Decoding of the func Field

func op 6 Main Control 6 ALUop N ori Or 0 10 16 rt rd ALU Control (Local) ALUctr 3

How many bits?

In this exercise, ALUop has to be 2 bits wide to represent: (1) R-type instructions I-type instructions that require the ALU to perform: (2) Or, (3) Add, and (4) Subtract

ALUop (Symbolic)

Why not consider J-type?

R-type R-type 1 00 21 rs

lw Add 0 00 11

sw Add 0 00 6 shamt

beq Subtract 0 01

jump xxx xxx 0

ALUop<2:0> 31 R-type op 26

To implement the full MIPS ISA, ALUop hat to be 3 bits to represent: (1) R-type instructions I-type instructions that require the ALU to perform: (2) Or, (3) Add, (4) Subtract, and (5) And (Example: andi)

R-type R-type 1 00 ori Or 0 10 lw Add 0 00 sw Add 0 00 jump Subtract xxx xxx 0 01

2003-3-17

funct

Recall ALU Homework (also P. 286 text): funct<5:0> 10 0000 10 0010 10 0100 10 0101 10 1010

ECE4680 Control.20

Instruction Operation add subtract

ALUctr

ALUctr<2:0> 000 001 010 110 111

ALU Operation Add Subtract And Or Set-on-less-than

2003-3-17

ALU

beq

ALUop (Symbolic) ALUop<2:0>

ECE4680 Control.19

and or set-on-less-than

The Truth Table for ALUctr

R-type ALUop (Symbolic) R-type ALUop<2:0> 1 00 ori Or 0 10 lw Add 0 00 sw Add 0 00 beq Subtract 0 01

funct<3:0> 0000 0010 0100 0101 1010

Instruction Op. add subtract and or set-on-less-than

The Logic Equation for ALUctr<0>

ALUop bit<2> bit<1> bit<0> 0 1 1 x x x 1 x x func bit<3> bit<2> bit<1> bit<0> x 0 1 x 0 0 x 1 1 x 0 0 ALUctr<0> 1 1 1

ALUop bit<2> bit<1> bit<0> 0 0 0 1 1 1 1 1 0 x 1 x x x x x 0 1 x x x x x x

func bit<3> bit<2> bit<1> bit<0> x x x 0 0 0 0 1 x x x 0 0 1 1 0 x x x 0 1 0 0 1 x x x 0 0 0 1 0

ALU Operation Add Subtract Or Add Subtract And Or Set on <

ALUctr bit<2> bit<1> bit<0> 0 0 1 0 0 0 1 1 0 0 1 0 0 1 1 1 0 1 0 0 1 0 0 1

This makes func<3> a dont care

ALUctr<0> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<2> & func<1> & !func<0>

ECE4680 Control.21

2003-3-17

ECE4680 Control.22

2003-3-17

The Logic Equation for ALUctr<1>

ALUop bit<2> bit<1> bit<0> 0 1 1 1 1 x x x x x x x func bit<3> bit<2> bit<1> bit<0> ALUctr<1> x 0 0 1 x 1 1 0 x 0 0 1 x 0 1 0 1 1 1 1

The Logic Equation for ALUctr<2>

ALUop bit<2> bit<1> bit<0> 0 1 1 1 x x x x x func bit<3> bit<2> bit<1> bit<0> ALUctr<2> x 0 1 x 1 0 x 0 1 x 1 0 1 1 1

ALUctr<2> = !ALUop<2> & ALUop<1> ALUctr<1> = !ALUop<2> & ALUop<1> + ALUop<2> & !func<3> & func<2> & !func<1> ALUop<2> & func<3> & !func<2> & func<1> & !func<1> + ALUop<2> & !func<3> & func<2> & !func<1> & func<0> + ALUop<2> & func<3> & !func<2> & func<1> & !func<0>

ECE4680 Control.23

2003-3-17

ECE4680 Control.24

2003-3-17

The ALU Control Block

func 6 ALUop 3 ALU Control (Local) ALUctr 3

The Truth Table for the Main Control

RegDst op 6 ALUSrc Main Control func 6 ALU Control (Local)

:

ALUop 3 00 0000 R-type 1 0 0 1 0 0 0 x R-type 1 0 0 ori 0 1 0 1 0 0 0 0 Or 0 1 0 lw 0 1 1 1 0 0 0 1 Add 0 0 0

ALUctr 3

op

00 1101 10 0011 10 1011 00 0100 00 0010 sw x 1 x 0 1 0 0 1 Add 0 0 0 beq x 0 x 0 0 1 0 x Subtract 0 0 1 jump x x x 0 0 0 1 x xxx x x x

2003-3-17

ALUctr<0> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<2> & func<1> & !func<0> ALUctr<1> = !ALUop<2> & ALUop<1> + ALUop<2> & !func<3> & func<2> & !func<1> + ALUop<2> & func<3> & !func<2> & func<1> & !func<1> ALUctr<2> = !ALUop<2> & ALUop<1> + ALUop<2> & !func<3> & func<2> & !func<1> & func<0> + ALUop<2> & func<3> & !func<2> & func<1> & !func<0>

RegDst ALUSrc MemtoReg RegWrite MemWrite Branch Jump ExtOp ALUop (Symbolic) ALUop <2> ALUop <1> ALUop <0>

ECE4680 Control.25

2003-3-17

ECE4680 Control.26

The Truth Table for RegWrite

op RegWrite 00 0000 R-type 1 00 1101 10 0011 10 1011 00 0100 00 0010 ori lw sw beq jump 1 1 0 0 0

PLA Implementation of the Main Control

op<5>

..

op<5>

..

op<5>

..

op<5>

..

op<5>

..

<0>

op<5>

..

op<0>

<0>

<0>

<0>

<0>

RegWrite = R-type + ori + lw = !op<5> & !op<4> & !op<3> & !op<2> & !op<1> & !op<0> + !op<5> & !op<4> & op<3> & op<2> & !op<1> & op<0> + op<5> & !op<4> & !op<3> & !op<2> & op<1> & op<0>

op<5>

(R-type) (ori) (lw)

R-type

ori

lw

sw

beq

jump

RegWrite ALUSrc RegDst MemtoReg MemWrite Branch Jump ExtOp

..

op<5>

..

op<5>

..

op<5>

..

op<5>

..

<0>

op<5>

..

op<0>

<0>

<0>

<0>

<0>

R-type

ori

lw

sw

beq

jump RegWrite

ALUop<2> ALUop<1> ALUop<0>

ECE4680 Control.27

2003-3-17

ECE4680 Control.28

2003-3-17

Putting it All Together: A Single Cycle Processor

ALUop op 6 Instr<31:26> RegDst Main Control ALUSrc 3 func Instr<5:0> 6 ALU Control ALUctr 3

How is this Different from a Real MIPS Processor?

The effect of load in a real MIPS Processor is delayed: - lw $1, 100 ($2) // Load Register R1 - add $3, $1, $0 // Move old R1 into R3 - add $4, $1, $0 // Move new R1 into R4 The effect of load in our single cycle processor is NOT delayed - lw $1, 100 ($2) // Load Register R1 add $3, $1, $0 // Move new R1 into R3

:

Rt Rs 5 5 Rt

Branch Jump Clk Instruction Fetch Unit

Instruction<31:0> <11:15> <21:25> <16:20> <0:15>

Rd RegDst

1 Mux 0 RegWr 5 ALUctr busA 32 0 Mux ALU

Rt Zero

Rs

Rd

Imm16 MemtoReg 0 Mux

busW 32 Clk

Rw Ra Rb 32 32-bit Registers busB 32 Extender

MemWr

32 32 WrEn Adr

The effect of branch and jump in a real MIPS Processor is delayed: - Instruction Address: 0x00 j 1000 - Instruction Address: 0x04 add $1, $2, $3 Instruction Address: 0x1000 sub $1, $2, $3 Branch and jump in our single cycle processor is NOT delayed - Instruction Address: 0x00 j 1000 - Instruction Address: 0x1000 sub $1, $2, $3

1 32 ALUSrc

imm16 Instr<15:0>

Data In 32 Clk

16

Data Memory

ExtOp

ECE4680 Control.29 2003-3-17 ECE4680 Control.30 2003-3-17

Worst Case Timing

Clk PC Old Value Clk-to-Q New Value Old Value Old Value Old Value Old Value Old Value Old Value Old Value Delay through Extender & Mux Old Value Old Value Data Memory Access Time busW

ECE4680 Control.31

Drawback of this Single Cycle Processor

Long cycle time: Cycle time must be long enough for the load instruction: PCs Clock -to-Q + Instruction Memory Access Time + Register File Access Time + ALU Delay (address calculation) + Data Memory Access Time +

Register Write Occurs

Rs, Rt, Rd, Op, Func ALUctr ExtOp ALUSrc MemtoReg RegWr busA busB Address

Instruction Memory Access Time New Value Delay through Control Logic New Value New Value New Value New Value New Value

Register File Setup Time + Clock Skew Cycle time is much longer than needed for all other instructions

Register File Access Time New Value New Value ALU Delay New Value New

2003-3-17

Old Value

ECE4680 Control.32

2003-3-17

Where to get more information?

Chapter 5.1 to 5.3 of your text book: Daid Patterson and John Hennessy, Computer Organization & Design: The Hardware / Software Interface, Morgan Kaufman Publishers, San Mateo, California, 1998. For a reference on the MIPS architecture: Gerry Kane, MIPS RISC Architecture, Prentice Hall.

ECE4680 Control.33

2003-3-17

Anda mungkin juga menyukai

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Dari EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Belum ada peringkat

- ECE4680 Computer Organization and Architecture Designing Single Cycle ControlDokumen17 halamanECE4680 Computer Organization and Architecture Designing Single Cycle ControlNarender KumarBelum ada peringkat

- CPS 104 Computer Organization and Programming Lecture-21: Building A DatapathDokumen32 halamanCPS 104 Computer Organization and Programming Lecture-21: Building A DatapathprachesBelum ada peringkat

- CS M151B / EE M116C: Computer Systems ArchitectureDokumen34 halamanCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacBelum ada peringkat

- Processor Implementation: ECE437: Introduction To Digital Computer DesignDokumen10 halamanProcessor Implementation: ECE437: Introduction To Digital Computer DesignasdfBelum ada peringkat

- CPS 104 Computer Organization and Programming Lecture-22: Single Cycle Datapath, ControlDokumen36 halamanCPS 104 Computer Organization and Programming Lecture-22: Single Cycle Datapath, ControlprachesBelum ada peringkat

- Chap5 Processor Part-IIDokumen21 halamanChap5 Processor Part-IIIsra NazeerBelum ada peringkat

- Control: Control Unit Takes Input FromDokumen29 halamanControl: Control Unit Takes Input FromShivam KhandelwalBelum ada peringkat

- Instruction Fetch Unit: DrawbacksDokumen7 halamanInstruction Fetch Unit: DrawbacksNarender KumarBelum ada peringkat

- CpuDokumen51 halamanCpujunaidalighouriBelum ada peringkat

- Basic Computer Organization and Design: - Computer Registers - Instruction CycleDokumen21 halamanBasic Computer Organization and Design: - Computer Registers - Instruction CycleShashank PandeyBelum ada peringkat

- Arm Instruction SetDokumen54 halamanArm Instruction SetSundar VadivelanBelum ada peringkat

- Lecture 15: Processor Design: Why Everything You've Learned MattersDokumen29 halamanLecture 15: Processor Design: Why Everything You've Learned MattersDeepak SoniBelum ada peringkat

- Fetch-Execute Cycle: Minggu 1 Arsitektur KomputerDokumen12 halamanFetch-Execute Cycle: Minggu 1 Arsitektur KomputerRyan SaputraBelum ada peringkat

- Processor Design: How To Implement MIPS Simplicity Favors RegularityDokumen7 halamanProcessor Design: How To Implement MIPS Simplicity Favors RegularityNarender KumarBelum ada peringkat

- Computer Architecture: CSCE 350Dokumen41 halamanComputer Architecture: CSCE 350kherberosBelum ada peringkat

- Fundamentals of Computer Systems: A Single Cycle MIPS ProcessorDokumen29 halamanFundamentals of Computer Systems: A Single Cycle MIPS ProcessorMahi NurBelum ada peringkat

- Datapath For The MIPS Architecture (A Single-Cycle Implementation)Dokumen22 halamanDatapath For The MIPS Architecture (A Single-Cycle Implementation)Alexander TaylorBelum ada peringkat

- Computer Architecture MIPS Processor DescriptionDokumen41 halamanComputer Architecture MIPS Processor DescriptionAsif HussainBelum ada peringkat

- Exam2 ReviewDokumen54 halamanExam2 ReviewSurbhie Kalia ChebaBelum ada peringkat

- SMIPS ISA and Instruction Decoding: Introduction To Computer OrganizationDokumen47 halamanSMIPS ISA and Instruction Decoding: Introduction To Computer OrganizationSai SaurabBelum ada peringkat

- ECE4680 Computer Organization and Architecture Designing A Multiple Cycle ProcessorDokumen19 halamanECE4680 Computer Organization and Architecture Designing A Multiple Cycle ProcessorNarender KumarBelum ada peringkat

- Mips DatapathDokumen23 halamanMips DatapathKaran KampaniBelum ada peringkat

- Lec08 ARMisa 4upDokumen24 halamanLec08 ARMisa 4upMuthu LinganBelum ada peringkat

- Chapter 5 - The Processor: Datapath and ControlDokumen101 halamanChapter 5 - The Processor: Datapath and Controlapi-26072581Belum ada peringkat

- Miroprogram Control UnitDokumen21 halamanMiroprogram Control UnitSameer SalamBelum ada peringkat

- Section 6. Oscillators: HighlightsDokumen44 halamanSection 6. Oscillators: HighlightsFrancisco MartinsBelum ada peringkat

- 4 - Processor (Multi Cycle)Dokumen42 halaman4 - Processor (Multi Cycle)xuanzzkBelum ada peringkat

- CE605 SCP Datapath Final VersionDokumen21 halamanCE605 SCP Datapath Final VersionLSchwappachBelum ada peringkat

- hw7 SolDokumen5 halamanhw7 SolIvanildo Gomes100% (1)

- Unit 3 CSADokumen25 halamanUnit 3 CSAyugdevBelum ada peringkat

- HCS08 Instruction Set SummaryDokumen9 halamanHCS08 Instruction Set SummaryDereck AntonyDengo DomboBelum ada peringkat

- CS2100: Single Cycle Implementation of MIPS Standard (Computer Organisation)Dokumen16 halamanCS2100: Single Cycle Implementation of MIPS Standard (Computer Organisation)pkchukissBelum ada peringkat

- Block I Apollo Guidance Computer (AGC) : How To Build One in Your BasementDokumen110 halamanBlock I Apollo Guidance Computer (AGC) : How To Build One in Your BasementpabloBelum ada peringkat

- Microchip CRC Manual 2Dokumen16 halamanMicrochip CRC Manual 2mordehainBelum ada peringkat

- Sony Acx705akm Color LCDDokumen20 halamanSony Acx705akm Color LCDHari NurcahyadiBelum ada peringkat

- HW10 11Dokumen3 halamanHW10 11Robert RobinsonBelum ada peringkat

- Omron Cp1e PDFDokumen45 halamanOmron Cp1e PDFSuzaini SupingatBelum ada peringkat

- Speed Not Affected by Compiler OptimizationDokumen7 halamanSpeed Not Affected by Compiler OptimizationMohammad Khalid Bin AnowerBelum ada peringkat

- German Mnemonics English Mnemonics Program Elements Catalog DescriptionDokumen4 halamanGerman Mnemonics English Mnemonics Program Elements Catalog DescriptionsivasubramanianMBelum ada peringkat

- CH 8Dokumen6 halamanCH 8Mustafa JumaBelum ada peringkat

- Chapter 7Dokumen26 halamanChapter 7prachesBelum ada peringkat

- Processor: Datapath and Control: Augusto SalazarDokumen9 halamanProcessor: Datapath and Control: Augusto SalazarMartin Fuentes AcostaBelum ada peringkat

- D 32-CPU: Esign of A Bit Single CycleDokumen11 halamanD 32-CPU: Esign of A Bit Single CycleAritra GuptaBelum ada peringkat

- Computer Organization & Design: Bilgisayar Organizasyonu & TasarimiDokumen32 halamanComputer Organization & Design: Bilgisayar Organizasyonu & Tasarimimanny oluanBelum ada peringkat

- 03 Bagian 1 Arsitektur AVRDokumen22 halaman03 Bagian 1 Arsitektur AVRTito Adi NugrohoBelum ada peringkat

- CS M151B / EE M116C: Computer Systems ArchitectureDokumen36 halamanCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacBelum ada peringkat

- Ch7 1Dokumen24 halamanCh7 1Subathra Devi MourouganeBelum ada peringkat

- ARM OverviewDokumen43 halamanARM OverviewSelva KumarBelum ada peringkat

- 74164Dokumen4 halaman74164milkyway69Belum ada peringkat

- Unit 1Dokumen68 halamanUnit 1N EDUBelum ada peringkat

- Topic01B Introdiuction To Microprocessor and MicroControllers Part 2Dokumen63 halamanTopic01B Introdiuction To Microprocessor and MicroControllers Part 2Brett WildermothBelum ada peringkat

- ATV12 Communication Parameters BBV51917 1.4IE05bDokumen12 halamanATV12 Communication Parameters BBV51917 1.4IE05bRicardo Rodriguez ParedesBelum ada peringkat

- Microprocessor Architectures and Systems: RISC, CISC and DSPDari EverandMicroprocessor Architectures and Systems: RISC, CISC and DSPPenilaian: 4 dari 5 bintang4/5 (1)

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDari EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationBelum ada peringkat

- ECE4680 Computer Organization and Architecture Designing A Multiple Cycle ProcessorDokumen19 halamanECE4680 Computer Organization and Architecture Designing A Multiple Cycle ProcessorNarender KumarBelum ada peringkat

- Instruction Fetch Unit: DrawbacksDokumen7 halamanInstruction Fetch Unit: DrawbacksNarender KumarBelum ada peringkat

- Multipath 1 NotesDokumen37 halamanMultipath 1 NotesNarender KumarBelum ada peringkat

- ECE4680 Computer Organization and Architecture Virtual MemoryDokumen13 halamanECE4680 Computer Organization and Architecture Virtual MemoryNarender KumarBelum ada peringkat

- Review: The Principle of LocalityDokumen5 halamanReview: The Principle of LocalityNarender KumarBelum ada peringkat

- Midterm ReviewDokumen4 halamanMidterm ReviewNarender KumarBelum ada peringkat

- MTED 11 ChamberlinDokumen14 halamanMTED 11 ChamberlinNarender KumarBelum ada peringkat

- ECE4680 Computer Organization and Architecture Lecture 2: Performance EvaluationDokumen22 halamanECE4680 Computer Organization and Architecture Lecture 2: Performance EvaluationNarender KumarBelum ada peringkat

- Memory Addressing: or Write Is CellDokumen8 halamanMemory Addressing: or Write Is CellNarender KumarBelum ada peringkat

- Lec2 6Dokumen8 halamanLec2 6Narender KumarBelum ada peringkat

- MIPS Instruction Set Architecture: ECE4680 Computer Organization & ArchitectureDokumen4 halamanMIPS Instruction Set Architecture: ECE4680 Computer Organization & ArchitectureNarender KumarBelum ada peringkat

- ECE4680 Computer Organization and Architecture Memory Hierarchy: Cache SystemDokumen25 halamanECE4680 Computer Organization and Architecture Memory Hierarchy: Cache SystemNarender KumarBelum ada peringkat

- The Motivation For Caches: Memory SystemDokumen9 halamanThe Motivation For Caches: Memory SystemNarender KumarBelum ada peringkat

- ECE 4680 Computer Architecture and OrganizationDokumen15 halamanECE 4680 Computer Architecture and OrganizationNarender KumarBelum ada peringkat

- Operating System Requirements: ProtectionDokumen4 halamanOperating System Requirements: ProtectionNarender KumarBelum ada peringkat

- CSCI 4717/5717 Computer Architecture: Topic: Introduction Reading: Chapter 1Dokumen22 halamanCSCI 4717/5717 Computer Architecture: Topic: Introduction Reading: Chapter 1Narender KumarBelum ada peringkat

- ECE4680 Computer Organization & Architecture: MIPS Instruction Set ArchitectureDokumen11 halamanECE4680 Computer Organization & Architecture: MIPS Instruction Set ArchitectureNarender KumarBelum ada peringkat

- CSCI 610: Modern Computer Architecture CSCI 510: Advanced Computer ArchitectureDokumen4 halamanCSCI 610: Modern Computer Architecture CSCI 510: Advanced Computer ArchitectureNarender KumarBelum ada peringkat

- ECE 4680: Computer Architecture and OrganizationDokumen20 halamanECE 4680: Computer Architecture and OrganizationNarender KumarBelum ada peringkat

- The Design Process & ALU DesignDokumen6 halamanThe Design Process & ALU DesignNarender KumarBelum ada peringkat

- Review: MULTIPLY HARDWARE Version 1: °64-Bit Multiplicand Reg, 64-Bit ALU, 64-Bit Product RegDokumen6 halamanReview: MULTIPLY HARDWARE Version 1: °64-Bit Multiplicand Reg, 64-Bit ALU, 64-Bit Product RegNarender KumarBelum ada peringkat

- ECE468 Computer Organization & Architecture ALU Design II: °this 1-Bit ALU Will Perform AND, OR, and ADDDokumen16 halamanECE468 Computer Organization & Architecture ALU Design II: °this 1-Bit ALU Will Perform AND, OR, and ADDNarender KumarBelum ada peringkat

- ECE4680 Computer Organization & Architecture Divide, Floating Point, Pentium BugDokumen17 halamanECE4680 Computer Organization & Architecture Divide, Floating Point, Pentium BugNarender KumarBelum ada peringkat

- Processor Design: How To Implement MIPS Simplicity Favors RegularityDokumen7 halamanProcessor Design: How To Implement MIPS Simplicity Favors RegularityNarender KumarBelum ada peringkat

- Bhilai Steel Plant, Seel Authority of India Limited, Chattisgarh, INDIADokumen10 halamanBhilai Steel Plant, Seel Authority of India Limited, Chattisgarh, INDIANarender KumarBelum ada peringkat

- Review: A One Bit Alu: CarryinDokumen6 halamanReview: A One Bit Alu: CarryinNarender KumarBelum ada peringkat

- Science7 - q1 - Mod3 - Distinguishing Mixtures From Substances - v5Dokumen25 halamanScience7 - q1 - Mod3 - Distinguishing Mixtures From Substances - v5Bella BalendresBelum ada peringkat

- 5c3f1a8b262ec7a Ek PDFDokumen5 halaman5c3f1a8b262ec7a Ek PDFIsmet HizyoluBelum ada peringkat

- Essay Rough Draft 19Dokumen9 halamanEssay Rough Draft 19api-549246767Belum ada peringkat

- Heterogeneity in Macroeconomics: Macroeconomic Theory II (ECO-504) - Spring 2018Dokumen5 halamanHeterogeneity in Macroeconomics: Macroeconomic Theory II (ECO-504) - Spring 2018Gabriel RoblesBelum ada peringkat

- Methods of Recording Retruded Contact Position in Dentate PatientsDokumen15 halamanMethods of Recording Retruded Contact Position in Dentate PatientsYossr MokhtarBelum ada peringkat

- Analizador de Combustion Kigaz 310 Manual EngDokumen60 halamanAnalizador de Combustion Kigaz 310 Manual EngJully Milagros Rodriguez LaicheBelum ada peringkat

- Hey Friends B TBDokumen152 halamanHey Friends B TBTizianoCiro CarrizoBelum ada peringkat

- 3 Carbohydrates' StructureDokumen33 halaman3 Carbohydrates' StructureDilan TeodoroBelum ada peringkat

- Mastertop 1230 Plus PDFDokumen3 halamanMastertop 1230 Plus PDFFrancois-Belum ada peringkat

- Fss Presentation Slide GoDokumen13 halamanFss Presentation Slide GoReinoso GreiskaBelum ada peringkat

- Unit 16 - Monitoring, Review and Audit by Allan WatsonDokumen29 halamanUnit 16 - Monitoring, Review and Audit by Allan WatsonLuqman OsmanBelum ada peringkat

- LTE Networks Engineering Track Syllabus Overview - 23 - 24Dokumen4 halamanLTE Networks Engineering Track Syllabus Overview - 23 - 24Mohamed SamiBelum ada peringkat

- Prelim Examination MaternalDokumen23 halamanPrelim Examination MaternalAaron ConstantinoBelum ada peringkat

- Chapter 2 ProblemsDokumen6 halamanChapter 2 ProblemsYour MaterialsBelum ada peringkat

- RSA - Brand - Guidelines - 2019 2Dokumen79 halamanRSA - Brand - Guidelines - 2019 2Gigi's DelightBelum ada peringkat

- Mcdonald 2016Dokumen10 halamanMcdonald 2016Andrika SaputraBelum ada peringkat

- GT-N7100-Full Schematic PDFDokumen67 halamanGT-N7100-Full Schematic PDFprncha86% (7)

- Log Building News - Issue No. 76Dokumen32 halamanLog Building News - Issue No. 76ursindBelum ada peringkat

- SSGC-RSGLEG Draft Study On The Applicability of IAL To Cyber Threats Against Civil AviationDokumen41 halamanSSGC-RSGLEG Draft Study On The Applicability of IAL To Cyber Threats Against Civil AviationPrachita AgrawalBelum ada peringkat

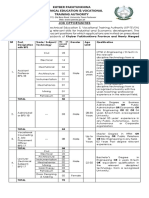

- KP Tevta Advertisement 16-09-2019Dokumen4 halamanKP Tevta Advertisement 16-09-2019Ishaq AminBelum ada peringkat

- Skills Redux (10929123)Dokumen23 halamanSkills Redux (10929123)AndrewCollas100% (1)

- Farmer Producer Companies in OdishaDokumen34 halamanFarmer Producer Companies in OdishaSuraj GantayatBelum ada peringkat

- Opc PPT FinalDokumen22 halamanOpc PPT FinalnischalaBelum ada peringkat

- Product CatalogsDokumen12 halamanProduct Catalogscab666Belum ada peringkat

- Waterstop TechnologyDokumen69 halamanWaterstop TechnologygertjaniBelum ada peringkat

- Article An Incident and Injury Free Culture Changing The Face of Project Operations Terra117 2Dokumen6 halamanArticle An Incident and Injury Free Culture Changing The Face of Project Operations Terra117 2nguyenthanhtuan_ecoBelum ada peringkat

- Tribal Banditry in Ottoman Ayntab (1690-1730)Dokumen191 halamanTribal Banditry in Ottoman Ayntab (1690-1730)Mahir DemirBelum ada peringkat

- Technical Specification For 33KV VCB BoardDokumen7 halamanTechnical Specification For 33KV VCB BoardDipankar ChatterjeeBelum ada peringkat

- A Case Study of Coustomer Satisfaction in Demat Account At: A Summer Training ReportDokumen110 halamanA Case Study of Coustomer Satisfaction in Demat Account At: A Summer Training ReportDeepak SinghalBelum ada peringkat

- Elements of ArtDokumen1 halamanElements of Artsamson8cindy8louBelum ada peringkat