Tema DSP

Diunggah oleh

Ronald Eder Chavez PalominoJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Tema DSP

Diunggah oleh

Ronald Eder Chavez PalominoHak Cipta:

Format Tersedia

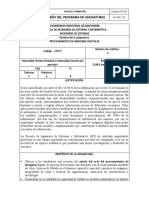

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Tema: Microcontroladores basados en procesadores digitales de seal (DSP).

1 Introduccin.

Un procesador digital de seal es un microprocesador especial con una arquitectura y unas instrucciones especficamente diseadas para implementar de forma sencilla y rpida operaciones de procesado de seal, como funciones de transferencia discretas (filtros digitales controladores digitales), transformadas de Fourier discretas. Un ejemplo de estas instrucciones especiales es la multiplicacin y acumulacin del resultado en un solo ciclo. En el mercado existen microcontroladores basados en DSP. stos contienen en un solo chip, no solo el microprocesador (DSP), sino los perifricos necesarios para controlar procesos (entradas/salidas digitales y analgicas, entradas de encoder, salidas PWM, temporizadores, etc.). Los procesadores digitales de seal pueden ser de coma fija o de coma flotante. Los de coma flotante trabajan normalmente con nmeros de 32 bits. Los de coma fija pueden trabajar con nmeros de 16 bits de 32 bits.

2 Microcontrolador basado en DSP TMS320LF2407.

Es un microcontrolador fabricado por Texas Instruments. Dispone de un procesador digital de seal de coma fija de 16 bits, ms los perifricos necesarios para controlar procesos. Entre estos perifricos se encuentran convertidores A/D, entradas de encoder incremental, salidas de PWM, temporizadores, etc. Est especialmente diseado para controlar motores elctricos o elementos movidos por motores elctricos (como mecanismos, cintas transportadoras, robots, etc.), aunque puede utilizarse para controlar cualquier proceso. Tiene una arquitectura tipo Harvard con una memoria de programa y otra de datos. Las caractersticas ms importantes son: Procesador TMS320C2XX. DSP de coma fija de 16 bits y velocidad mxima de 40 MIPS (millones de instrucciones por segundo). Memoria de datos. 2.5 kwords de RAM de 16 bits. Una parte de esta memoria de datos se puede configurar y utilizar como memoria de programa en lugar de datos. Memoria de programa. 32 kwords de memoria Flash EEPROM. 16 canales A/D de 10 bits de resolucin. 28 lneas de entrada/salida digital. 16 salidas PWM. 4 mdulos de entradas para encoder incremental. 6 unidades de captura. Perro guardin. Puerto de comunicacin serie sncrono (SPI). UART (Puerto de comunicacin serie asncrono, SCI). Controlador de bus CAN integrado. 4 temporizadores de 16 bits. Bus de datos (16 bits) y direcciones (16 bits) para memoria externa.

La siguiente figura muestra el diagrama de bloques simplificado general del microcontrolador:

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

3 Estructura bsica del procesador.

El procesador (CPU) del TMS320LF2407 es un DSP de coma fija de 16 bits (el TMS320C2XX de Texas Instruments). La siguiente figura muestra la estructura bsica del procesador:

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Tanto las instrucciones como los datos tienen una longitud de 16 bits, sin embargo, la unidad aritmtico lgica principal (CALU) y el acumulador son de 32 bits, es decir, operan con nmeros en coma fija de 32 bits. Esto permite evitar el desbordamiento en las sumas (si se programan con cuidado). Como los datos son de 16 bits, antes de entrar en la ALU hay un desplazador input shifter, que permite desplazar a la izquierda el dato de 16 bits para convertirlo en uno de 32 bits. De la misma forma, como el acumulador es de 32 bits y las variables de memoria son de 16 bits, a la salida del mismo hay un desplazador (output shifter) que permite desplazar la palabra de 32 bits a la izquierda, permitiendo adems sacar los 16 bits ms significativos los 16 menos significativos hacia la me moria de datos. El procesador dispone adems de la CALU, de un elemento especial para realizar la multiplicacin de 2 datos de 16 bits. El resultado de la multiplicacin es de 32 bits, por lo que a la salida del multiplicador hay un desplazador (product shifter) que permite desplazar a la izquierda o a la derecha, permitiendo adems sacar los 16 bits ms significativos los 16 menos significativos hacia la memoria de datos.

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Desplazador de entrada (Input Shifter). El desplazador situado a la entrada del CALU convierte el dato de 16 bits en una palabra de 32 bits. Para hacerlo desplaza a la izquierda un nmero determinado de bits, rellenando con ceros los bits de la derecha. El nmero de bits desplazados se puede variar entre 0 y 16 bits. Este desplazamiento no requiere ninguna instruccin especfica, sino que se realiza a la vez que se ejecuta una instruccin de la CALU. Por ejemplo, para una instruccin de suma en un solo ciclo se realiza el desplazamiento y la suma en la CALU. Para ello las instrucciones incluyen como parmetro el nmero de bits a desplazar. Los bits que quedan a la derecha despus del desplazamiento se rellenan con ceros. La forma de rellenar los bits que quedan a la izquierda depende del valor del bit de configuracin SXM del registro ST1. Si SXM=0, se rellenan con ceros. Si SXM=1 se rellenan de tal forma que se mantenga el signo del valor inicial de 16 bits en complemento a 2. La idea es que si el nmero de 16 bits que entra es negativo, el nmero de 32 bits resultante tambin debe serlo, por lo que en ese caso se rellenan los bits de la izquierda con unos en lugar de ceros. Cuando se opera con nmeros que pueden ser positivos o negativos el bit SXM debe valer 1, para que los signos se mantengan y las operaciones sean correctas. El resultado del desplazador de entrada es que el nmero de 32 bits que sale es:

Salida = Entrada 2 desplazamiento

es decir, se tiene en realidad un escalado de la variable con la que se va a operar.

Desplazador de salida (Output Shifter). El desplazador situado a la salida del acumulador permite desplazar el valor de ste a la izquierda un nmero determinado de bits, adems de permitir que se guarde en la memoria de datos la parte alta la parte baja del nmero de 32 bits resultante. El nmero de bits desplazado se puede variar entre 0 y 7. El desplazamiento se realiza al mismo tiempo que se ejecuta la instruccin que almacena la parte alta (SACH) la parte baja (SACL) del acumulador en la memoria de datos. Para ello estas instrucciones tiene como parmetro el nmero de bits a desplazar. Si se guarda la parte alta del acumulador el resultado es que el dato guardado finalmente en memoria es:

2desplazami ento DatoFinal = Acumulador 216

CALU (Central Arithmetic Logic Unit). La ALU principal es de 32 bits, y realiza operaciones de suma, resta, operaciones lgicas (AND, OR, etc) y desplazamientos. Todas estas operaciones se realizan en complemento a 2, por lo que con esta representacin las sumas y restas de nmeros positivos y negativos se realizan correctamente. Dispone de un sistema para evitar el desbordamiento en las operaciones de suma y resta. El modo de funcionamiento queda determinado por el valor del bit OVM del registro ST0. Si OVM=1, el procesador evita el desbordamiento de forma automtica. En ese caso si el resultado de la operacin es mayor que 7FFF FFFF (el mayor nmero positivo de 32 bits) el resultado se fija automticamente en ese valor mximo. Lo mismo sucede si el resultado es negativo y menor que 8000 0000 (el nmero ms negativo). Si OVM=0, no detecta el desbordamiento, y ste se produce de forma normal. En ese caso se puede utilizar el bit OV_FLAG del registro ST0 para comprobar si ha habido desbordamiento (ese bit se pone a 1 cuando la ltima operacin ha producido desbordamiento). Las operaciones de la CALU afectan al bit de acarreo (bit C del registro ST1). Cuando el resultado de una suma se pasa de rango en los 32 bits (el resultado es mayor de FFFF FFFF, estando el bit OVM=0), el bit C se pone a 1. Si el resultado de la suma es menor, el bit C=0. Con la resta sucede lo contrario. Si el resultado de la resta se sale del rango de 32 bits (es menor que 0) el bit C se pone a 0, mientras que si no se sale (el resultado de la resta es positivo) se pone a 1.

Multiplicador. El elemento multiplicador realiza la mult iplicacin de 2 nmeros de 16 bits, dando un resultado de 32 bits. El producto se calcula por defecto teniendo en cuenta el signo (en complemento a 2), aunque se puede realizar una multiplicacin sin signo con la instruccin especial MPYU. Dispone de un registro denominado TREG en el que se guarda uno de los 2 operandos antes de realizar la multiplicacin. Para ello se utiliza la instruccin LT. El producto se realiza, por tanto entre el valor de TREG, y un dato de memoria. El resultado del producto se almacena en un registro de 32 bits, el PREG. A la salida de este registro hay un desplazador (product shifter) que permite desplazar el resultado a la izquierda o a la derecha un nmero determinado de bits. Adems permite guardar en la memoria de datos la parte alta la parte baja del resultado del desplazamiento. Tambin permite pasar los 32 bits a la CALU para realizar una operacin. De esta forma se puede sumar al acumulador el resultado de un producto. Los posibles desplazamientos son 1 bit a la izda., 4 bits a la izda, 6 bits a la derecha sin desplazamiento. Cul de estos desplazamientos de produce depende del valor de los bits PM (2 bits) del registro ST1.

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

PM 00 01 10 11 Desplazamiento Sin desplaz. 1 bit izda. 4 bits izda. 6 bits dcha. Para modificar estos bits se utiliza una instruccin especial (instruccin SPM). El desplazamiento a la derecha se realiza siempre con extensin del signo (rellenando los bits de la izquierda con unos si el nmero es negativo), aunque el bit SXM=0. Unidad Aritmtica de los Registros Auxiliares (ARAU). Adems de la unidad aritmtica principal (CALU) y de la seccin de multiplicacin, el DSP dispone de una unidad aritmtica auxiliar que permite realizar operaciones con los registros auxiliares. El siguiente diagrama s implificado representa esta unidad aritmtica junto con los registros auxiliares:

El ARP son 3 bits del registro especial ST0, y define cul de los 8 registros auxiliares est activo. El registro auxiliar activo se utiliza para el direccionamiento indirecto. La unidad ARAU permite realizar las siguientes operaciones: Incrementar o decrementar uno de los registros auxiliares. Sumar o restar una constante de 8 bits a un registro auxiliar. Comparar el contenido del registro auxiliar AR0 con el registro auxiliar activo. El resultado de la comparacin se refleja en el bit TC del registro ST0. Las principales utilidades de esta unidad aritmtica y de los registros auxiliares son: Llevar a cabo el direccionamiento indirecto. Sirven para almacenar temporalmente valores. Permiten implementar un contador por software. Permiten ejecutar un salto condicionado a que dos variables de 16 bits sean iguales (mediante la comparacin y el bit TC).

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

4 Pila (stack). Ejecucin de subrutinas.

El procesador dispone de una pila de 8 niveles. Cuando se produce una interrupcin o se ejecuta una subrutina (instruccin CALL) se guarda el valor del contador de programa+1 en la pila. Cuando se termina una subrutina (con RET), se recupera el contador de programa desde la pila con lo que el procesador vuelve al punto del programa principal en el que estaba. Se pueden encadenar por tanto hasta 8 subrutinas sin que se produzca error de desbordamiento de pila (stack overflow).

5 Mapa de memoria del TMS320LF2407.

El mapa de la memoria de programa del DSP TMS320LF2407, tal y como est utilizado en la tarjeta de desarrollo eZdsp del laboratorio es:

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

La parte de memoria RAM configurable (256 words de FF00h a FFFFh) puede configurarse en general como memoria de programa (CNF=1) o memoria de datos (CNF=0). En la tarjeta de desarrollo est asignada a memoria de datos (no la podemos por tanto asignar a memoria de programa). Los 256 words no utilizados de esta memoria pueden ser utilizados por el usuario para escribir una parte del programa de usuario. De la direccin 8000h a la FFFFh hay espacio para direccionar 32Kw de memoria externa de programa. La tarjeta de desarrollo eZDSP incluye estos 32Kw de memoria RAM externa, por lo que pueden utilizarse para el programa de usuario. La tarjeta de desarrollo del laboratorio est configurada en modo microprocesador, con lo que la memoria RAM externa de 8000 a FFFF se refleja en el rango de 0000 a 7FFF. De esta forma el usuario puede desarrollar software y cargarlo en la RAM para poder as depurar el programa sin necesidad de grabar lo en la FLASH, que requiere de un proceso. El mapa de la memoria de datos del DSP TMS320LF2407, tal y como est utilizado en la tarjeta de desarrollo eZDSP es el de la figura. Cuando la memoria RAM de programa se configura como RAM de datos (CNF=0), sta queda direccionada justo antes de la RAM de datos de usuario B1 (entre las direcciones 0200 y 02FF). Por defecto CNF=0. La zona de memoria RAM de datos que puede ser utilizada por el programa de usuario para definir las dis tintas variables que se utilicen est dividida de la siguiente forma: 32 words entre 0060 y 007F (bloque B2), 256 words entre 0200 y 02FF (bloque B0 si CNF=0), 256 words entre 0300 y 03FF (B1) y 2 kwords entre 0800 y 0FFF. En la zona de memoria entre 7000 y 753F se sitan los registros que controlan los distintos perifricos (convertidor A/D, perro guardin, mdulo PWM, mdulo de entrada de encoder, puertos serie, etc). De la direccin 8000h a la direccin FFFFh hay espacio para direccionar 32Kw de memoria externa de datos. La tarjeta eZdsp del laboratorio dispone de esos 32Kw externos de memoria RAM, por lo que estn disponibles para almacenar las variables de usuario.

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

6 Modos de direccionamiento.

El modo de direccionamiento es la forma en que se determinan los operandos de una instruccin. El DSP320C2XX admite 3 modos de direccionamiento diferentes: Direccionamiento inmediato. El valor del operando es una parte de la propia instruccin, es decir, no se obtiene de la memoria de datos. Existen dos tipos de direccionamiento inmediato: SHORT. De los 16 bits que forman una instruccin simple, 8, 9 13 bits forman el valor del operando. Los otros 8, 7 6 bits forman al cdigo de la instruccin. El nmero de bits del operando y del cdigo depende de la instruccin. LONG. La instruccin consta de 2 words de 16 bits. La primera word tiene el cdigo de la instruccin, y la segunda word contiene el valor del operando (16 bits). La misma instruccin puede ajustarse a los dos modos anteriores en funcin del valor del operando. Por ejemplo, la instruccin ADD: Direccionamiento SHORT (ocupa 1 solo word de la memoria de programa): ADD #A2h ; suma al acumulador el valor A2h

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Cdigo de la instruccin ADD

Valor del operando

Direccionamiento LONG (ocupa 2 words de la memoria de programa): ADD #2F6Bh,3 ; suma al acumulador el valor 2F6Bh desplazado 3 bits a la izquierda

Cdigo de la instruccin ADD

Valor del operando Direccionamiento directo. La instruccin contiene la direccin de la memoria de datos que contiene el operando. Para ello la memoria de datos se divide en bloques (pginas) de 128 words. La instruccin en realidad solo contiene los 7 bits menos significativos de la direccin de memoria total del dato. Los otros 9 bits que completan la direccin los toma el sistema del DP (Data Page Pointer). El DP son 9 bits pertenecientes al registro ST0. Antes de realizar una operacin con un dato de la memoria es necesario fijar el valor correcto del Data Page Pointer donde se encuentra ese dato. Para ello se utiliza la instruccin LDP.

Por ejemplo, si se quiere sumar al acumulador el contenido de la posicin de memoria de datos 030Ah, desplazado 5 bits a la izquierda, habra que utilizar las instrucciones: LDP #06h ; se carga el Data Page Pointer con el valor de la pgina ADD 0Ah, 5 ; se suma al acumulador el contenido de 030Ah desplazado 5 bits La pgina de datos donde est la posicin de memoria 030Ah se obtiene sin ms que dividir por 80h (128 en hexadecimal). La parte entera de esta divisin da 6, que es la pgina de datos en la que est el dato con el que queremos operar. Los 7 bits menos significativos de 030Ah forman el nmero 0Ah. La instruccin ADD se podra haber puesto tambin como: LDP #06h ADD 030Ah, 5 ya que el ensamblador toma nicamente los 7 bits menos significativos de la direccin 030Ah. Normalmente se suele hacer esto (poner la direccin completa del dato), por ser ms cmodo que obtener los 7 bits menos significativos. Es fundamental no olvidarse del Data Page Pointer, puesto que si ste tiene el valor equivocado se operar con un dato diferente al que se pretenda. Por ejemplo, si el DP vale 3, y se ejecuta la instruccin: ADD 030Ah, 5 se estar sumando al acumulador el contenido de la posicin de memoria de datos 018Ah, que es una posicin no implementada cuyo valor es impredecible. Direccionamiento indirecto. El valor del operando se obtiene de la posicin de la memoria de datos cuya direccin es la indicada por uno de los 8 registros auxiliares. Cul de estos 8 registros es el que se utiliza para el direccionamiento indirecto depende del valor de los 3 bits ARP del registro ST0. Para modificar el valor de esos 3 bits se puede utilizar la instruccin MAR. Para fijar el registro auxiliar actual como el AR3 la sintaxis podra ser: MAR *, AR3 El valor del ARP se puede cambiar tambin en una instruccin cualquiera que utiliza direccionamiento indirecto. Por ejemplo, la instruccin ADD con direccionamiento indirecto tiene la sintaxis: ADD *,2,AR2

10

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Cuyo significado es: suma al acumulador el valor (desplazado 2 bits a la izda.) de la posicin de memoria de datos cuya direccin es el valor del AR actual, y cambia el valor de ARP a 2. De esta forma, a partir de aqu el AR actual es el AR2. Todo esto se realiza en una sola instruccin. El smbolo * indica el direccionamiento indirecto. Para este smbolo existen varias opciones que permiten realizar adems de todo lo anterior, un incremento o decremento del AR actual. Ejemplo: MAR *, AR3 ; el registro auxiliar actual es el AR3 (ARP=3) ADD *+,3 ; suma al acumulador el valor (desplazado 3 bits a la izda.) de la posicin de memoria cuya direccin es el valor de AR3, e incrementa el valor de AR3 ADD *-,1,AR5 ; suma al acumulador el valor (desplazado 1 bit a la izda.) de la posicin de memoria cuya direccin es el valor de AR3, decrementa el valor de AR3, y cambia el valor de ARP a 5 (a partir de ahora el AR actual es el AR5). ADD *0+, 4 ;suma al acumulador el valor (desplazado 4 bits a la izda.) de la posicin de memoria cuya direccin es el valor de AR5, e incrementa el valor de AR5 sumndole el valor de AR0. Las opciones de las instrucciones con direccionamiento indirecto son: * Direccionamiento indirecto simple. No incrementa ni decrementa el AR actual. *+ Incrementa el AR actual (le suma 1). *Decrementa el AR actual (le resta 1). *0+ Incrementa el AR actual sumndole el valor de AR0. *0Decrementa el AR actual restndole el valor de AR0. *BR0+ Similar al anterior pero con acarreo especial para realizar FFT. *BR0- Similar al anterior pero con acarreo especial para realizar FFT.

7 Instrucciones del TMS320LF2407.

El microcontrolador TMS320LF2407 tiene un procesador (DSP) TMS320C2XX en su interior. Este procesador de 16 bits (tanto las instrucciones como los datos son de 16 bits) tiene un conjunto de instrucciones muy completo. La sintaxis de las instrucciones al utilizarlas en ensamblador se explica en el ejemplo de la instruccin ADD siguiente:

donde dma representa una direccin de memoria de datos, shift es el desplazamiento, ind es uno de los smbolos de direccionamiento indirecto (*, *+, *-, *0+, *0-), #k y #lk son valores numricos, y pma representa una direccin de la memoria de programa Instrucciones lgicas y aritmticas del acumulador. AND acc=acc & (dato*2desplaz.) OR acc=acc | (dato*2desplaz.) XOR acc=acc XOR (dato*2desplaz.) CMPL NEG ABS LACC ADD SUB SFR acc= acc acc= -acc acc=|acc| acc=dato*2desplaz. acc=acc + (dato*2desplaz.) acc=acc - (dato*2desplaz.) acc=acc/2 (desplazamiento a la derecha)

11

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

SFL SACH SACL

acc=acc*2 (desplazamiento a la izquierda) dato=acchigh*2desplaz. dato=acclow*2desplaz.

Instrucciones de registros auxiliares. LAR arx=dato SAR dato=arx MAR define el registro auxiliar actual ADRK arx=arx+valor SBRK arx=arx-valor CMPR compara arx con ar0. El resultado de la comparacin va al bit TC. La comparacin realizada depende de un operando de la instruccin CMPR que puede valer 0,1,2 3. Operando Comparacin realizada 0 (arx= =ar0) TC 1 (arx < ar0) TC 2 (arx > ar0) TC 3 (arx ar0) TC Instrucciones de la seccin de multi plicacin. LT treg=dato LTA treg=dat , acc=acc+preg*2desplaz. LTS treg=dat , acc=acc-preg*2desplaz. LTP treg=dat , acc=preg*2desplaz. SPM define el desplazamiento del desplazador del producto MAC acc=acc+preg*2desplaz. , treg=dato , preg=treg*valor MACD igual que MAC, pero adems copia el dato a la posicin siguiente de la mem. de datos. MPY preg=treg*dato MPYA acc=acc+ preg*2desplaz. , preg=treg*dato MPYS acc=acc- preg*2desplaz. , preg=treg*dato MPYU igual que MPY pero los datos se consideran como enteros sin signo PAC acc=preg*2desplaz APAC acc=acc+preg*2desplaz SPAC acc=acc-preg*2desplaz SPH dato=preghigh SPL dato=preglow SQRA acc=acc+preg , preg=dato2 SQRS acc=acc-preg , preg=dato2 dato indica un valor de la memoria de datos y valor indica un valor de la memoria de programa. Instrucciones de salto. B Salta a una direccin de la memoria de programa BACC Salta a la direccin que hay en la parte baja del acumulador. BANZ Salta a una direccin si el registro auxiliar actual es 0. BCND Salta a una direccin de programa si se cumplen las condiciones. Las condiciones pueden ser: EQ (acc=0), NEQ (acc 0), LT (acc<0), LEQ (acc 0), GT (acc>0), GEQ (acc 0), NC (C=0), C (C=1), NOV (OV=0), OV (OV=1), BIO (BIO a nivel bajo), NTC (TC=0), TC (TC=1), UNC (salto incondicional). RPT Repite la instruccin siguiente N+1 veces, siendo N un operando de la instruccin Instrucciones de subrutina. CALL Ejecuta una subrutina en una direccin de programa CALA Ejecuta una subrutina en la direccin almacenada en al acumulador bajo CC Ejecuta una subrutina si la condicin es cierta (mismas condiciones que BCND). INTR Ejecuta subrutina de interrupcin software. RET Retorno de subrutina (de interrupcin o de CALL CALA CC) RETC Retorno de subrutina si la condicin es cierta (mismas condiciones que BCND). Instrucciones de control. BIT Se copia un bit de un dato al bit TC. Despus se pone una instr. condicionada a TC. CLRC Se pone a cero un bit especial (C, CNF, INTM, OVM, SXM, TC, XF).

12

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

SETC LDP LST SST PUSH POP

Se pone a uno un bit especial (C, CNF, INTM, OVM, SXM, TC, XF). Se carga la pgina de la memoria de datos. Carga el registro de estado (ST0 ST1) con el valor del dato. Guarda el valor del registro de estado (ST0 ST1) en un dato. Guarda el valor del acumulador bajo en la pila. Recupera el valor del acumulador bajo de la pila.

Instrucciones de entrada-salida y de memoria. SPLK dato=valor inmediato DMOV copia un dato en la siguiente posicin de la memoria de datos TBLR dato=contenido de la memoria de programa apuntada por el acumulador bajo TBLW copia el valor del dato en la direccin de mem. de programa apuntada por acc. bajo. BLDD mueve una word de la direccin fuente a la destino en la memoria de datos BLPD mueve una word de la memoria de programa a la memoria de datos. Las instrucciones que copian un dato en la siguiente direccin de memoria (MACD o DMOV) no se pueden ejecutar sobre datos ubicados en la memoria externa. Para ubicar el programa y los datos en el mapa de memoria se tienen que definir secciones dentro del cdigo de programa.. Todas las secciones se definen mediante un fichero de comandos de lincado. Este fichero define el mapa de memoria y cmo las secciones se alojan dentro de l. Por ejemplo: MEMORY /* Definicin del mapa de memoria a utilizar */ { PAGE 0: /* PROGRAM MEMORY */ PROG: origin = 0h , length = 08000h /* PROGRAM */ PAGE 1: /* DATA MEMORY */ RAM1: origin = 0200h , length = 0100h /* BLOCK B1 RAM (DP=#04h) */ RAM_EXT: origin = 8000h , length = 8000h /* RAM EXTERNA (DP=#0100h) */ } SECTIONS { .text : .data : .coefs: .bss : } /* Definicin de las secciones */ > > > > PROG PAGE 0 /* RAM1 PAGE 1 /* PROG PAGE 0 /* RAM_EXT PAGE 0 .text: el cdigo de programa estar en MP */ .data: las variables inicializadas en MD */ .coefs: los coeficientes estarn en MP */ /* .bss: variables sin inicializar */

dara la ubicacin mostrada en la figura Memoria de programa 0000h .text .asm .data :::::::: ::::::: .coefs :::::::::: ::::::::: .text ::::::::::: ::::::::::: Memoria de datos

.coefs

.data

0200h

8000h

8000h

La seccin donde se incluir el cdigo del programa principal ha de ser la seccin .text. Cuando se programa en C, el nombre de las secciones vienen definidas por el compilador, y por tanto el fichero de comandos de lincado ha de incluir esas secciones definidas. Para indicar el inicio de una seccin en el cdigo del programa hay que escribir .sect .nombre_seccion

13

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Ejemplo 1.

El siguiente programa calcula la suma de productos siguientes:

u (k ) = c0 e( k ) + c1e( k 1) + c 2e( k 2)

.sect error_0 error_1 error_2 coef_0 coef_1 coef_2 .data .word 00h ; word: inicializa variables .word 00h .word 00h .word 0F12h .word 23F1h .word 1241h

.sect .text ; Suponemos que error_0 contiene el valor de e(k) ; (se ha obtenido a partir de la salida) . . . SPM 2 ; El resultado del producto se desplaza 4 bits ; a la izda. al pasarlo al acumulador LACC #0 ; ACC=0 LT coef_0 MPY error_0 ; PREG=coef_0*error_0 LT coef_1 MPYA error_1 ; ACC=ACC+coef_0*error_0, PREG=coef_1*error_1, LT coef_2 MPYA error_2 ; ACC=ACC+coef_1*error_1, PREG=coef_2*error_2, APAC ; ACC=ACC+ coef_2*error_2 SACH u ; u=ACC/216 DMOV error_1 ; error_2=error_1 DMOV error_0 ; error_1=error_0 Como resultado se tiene que u=(coef_0*error_0+coef_1*error_1+coef_2*error_2)*24 /216 , adems de actualizar los valores de error_2 y error_1 para el siguiente periodo.

Ejemplo 2.

En este ejemplo se calcula el valor medio de 16 variables consecutivas de la memoria de datos. Para ello se utiliza direccionamiento indirecto y la instruccin RPT: .sect dato_1 dato_2 dato_3 dato_16 u .sect .data .word 0897h .word 294Ah .word 1490h .word 42B7h .word 0h .text LAR AR2,#dato_1 MAR *,AR2 LACC #0 RPT 15 ADD *+,12 SACH u

El resultado es que

u=

1 216

dato_i 2

i =1

16

12

1 16 dato_i 16 i =1

Ejemplo 3.

El siguiente programa calcula la suma de productos siguientes:

14

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

u (k ) = c0 e( k ) + c1e( k 1) + + c 9e( k 9)

.sect .data ; En memoria de datos se definen las variables u .word 00h error_0 .word 00h error_1 .word 00h . . . error_8 .word 00h error_9 .word 00h .sect .coefs ; En memoria de programa se definen los coeficientes coef_9 .word 0F12h coef_8 .word 23F1h . . . coef_1 .word 20A1h coef_0 .word 1002h ; Suponemos que error_0 contiene el valor de e(k) ; (se obtiene a partir de la salida) .sect .text . . . SPM 0 ; El resultado del producto no se desplaza al pasarlo al acumulador LAR AR3,#error_9 ;AR3 contiene la direccin de la variable error_2 MAR *,AR3 ; Se define AR3 como el registro auxiliar principal ; (para direcc. indirecto) LACC #0 ; ACC=0 MPY #0 ; PREG=0 RPT #9 MACD coef_9,*APAC SACH u ;u= Como resultado se tiene que

u=

1 216

coef_i error_i , a la vez que los errores se han actualizado (se ha hecho

i =0

error_9=error_8, error_8=error_7, etc) para la siguiente vez que se ejecute (en el siguiente periodo de muestreo).

8 Interrupciones.

Existen 2 tipos de interrupciones: Interrupciones software. Son producidas por una instruccin del programa. Las instrucciones que producen interrupciones son INTR, NMI y TRAP. Interrupciones hardware. Son interrupciones producidas por el cambio de una seal digital de un elemento fsico. Las interrupciones hardware se pueden clasificar en: Externas. Son producidas por cambios en seales externas al microcontrolador (pines XINT1, XINT2, PDINTA y PDINTB). Internas. Son producidas por perifricos internos del microcontrolador (convertidor A/D, temporizador, etc.). Por otra parte, tanto las interrupciones software como hardware pueden ser enmascarables o no enmascarables: Interrupciones enmascarables. Son aquellas que se pueden deshabilitar. Interrupciones no enmascarables. Son aquellas que no se pueden deshabilitar. Todas las interrupciones software y las interrupciones hardware NMI y RS son de este tipo. Cuando se produce una de estas interrupciones el procesador siempre ejecuta la rutina de interrupcin correspondiente. Cuando se produce una interrupcin el procesador sigue los siguientes pasos: 1. Deshabilita globalmente las interrupciones enmascarables (pone el bit INTM=1). Esto sucede en todas las interrupciones salvo la interrupcin software TRAP. 2. Guarda el contador de programa (PC) en la pila. 3. Carga el PC con el vector de la interrupcin correspondiente. El microprocesador tiene un montn de vectores de interrupcin, situados desde la direccin 0 en adelante de la memoria de programa (por tanto situados en la memoria FLASH). La siguiente figura muestra dichos vectores. Los ms importantes son los correspondientes a las 6 interrupciones hardware INT1 a INT6.

15

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

En el vector de la interrupcin que se va a utilizar debe haberse escrito una instruccin de salto a donde empieza el cdigo de la rutina de usuario. Interrupciones hardware enmascarables. Las interrupciones hardware enmascarables son las ms interesantes, pues son las que permiten controlar los distintos perifricos que tiene el microcontrolador (interrupciones hardware internas) y las que permiten ejecutar una interrupcin asociada a una seal digital externa al microcontrolador (de un detector por ejemplo). El procesador tiene 6 interrupciones enmascarables (INT1, ... INT6). La ms prioritaria es la 1, y la menos prioritaria la 6. Esto quiere decir que si se producen dos llamadas de interrupcin a la vez, se atiende primero a la ms prioritaria y despus a la menos prioritaria. Cada una de estas 6 interrupciones tiene conectados varios perifricos diferentes. La estructura general de la habilitacin de las interrupciones es:

16

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

B a n d e r a s y m s c a r a s d e l o s p e r i f r i c o s

B a n d e r a s y m s c a r a s d e l a s i n t e r r u p c i o n e s d e l p r o c e s a d o r

H a b i l i t a c i n g e n e r a l

I N T M X I N T 1 ( M ) X I N T 1 ( F ) X I N T 2 ( M ) X I N T 2 ( F ) I M R . 0 I N T 1

. . .

. . .

IFR.0

T M R 1 P ( M ) T M R 1 P ( F )

. . .

I M R . 1

I N T 2

. . .

IFR.1

. . .

A D C I ( M ) A D C I ( F )

. . .

I M R . 5

I N T 6

. . .

I F R . 1 5

La habilitacin global de las 6 interrupciones hardware depende del bit INTM: INTM=0 interrupciones enmascarables habilitadas. INTM=1 todas las interrupciones enmascarables deshabilitadas. Este bit se modifica con la instruccin CLRC INTM (para ponerlo a 0) y SETC INTM (para ponerlo a 1). Adems del bit de habilitacin global, existe un bit de mscara y un flag para cada interrupcin. Estos bits se encuentran en los registros especiales IMR e IFR. Si INTM=1 las 6 interrupciones estn deshabilitadas independientemente del valor de las mscaras. Cuando INTM=0, solo estarn habilitadas aquellas interrupciones cuya mscara valga 1. Los registros IMR e IFR tienen la estructura:

15 Reservados

5 INT6

4 INT5

3 INT4

2 INT3

1 INT2

0 INT1

El flag de la interrupcin se pone a 1 cuando se produce un evento que provoca esa interrupcin. Si est habilitada (INTM=0 y mscara=1) el procesador la atiende. Cuando se atiende la interrupcin el procesador borra automticamente (pone a 0) el flag correspondiente. Como cada interrupcin del procesador tiene varios perifricos conectados que pueden provocar su disparo, cada uno de stos tiene su propio flag y mscara de interrupcin para habilitarse o deshabilitarse. Por ejemplo, el temporizador 1 puede provocar la interrupcin INT2 cuando finaliza la cuenta. Para esta interrupcin hay un flag (situado en el registro EVIFRA) y una mscara (situada en el registro EVIMRA). Para que pueda producirse la interrupcin del temporizador 1 es necesario (adems de que la interrupcin INT2 est habilitada) que la mscara correspondiente est a 1. Cuando se produce el evento que provoca la interrupcin (fin del temporizador por ejemplo), el flag correspondiente se pone a 1. Si la interrupcin est habilitada es atendida por el procesador. A diferencia de los flags del registro IFR, los flags secundarios no se borran automticamente cuando el procesador atiende la interrupcin. Debido a esto es absolutamente necesario borrarlo por software al final de la rutina de interrupcin. Si no se borra cuando termina la rutina sta vuelve a ejecutarse, pues el flag sigue activo. Cada perifrico es capaz de generar una o ms interrupciones como respuesta a diversos eventos. Como la CPU no tiene suficiente capacidad para manipular todas las peticiones de interrupcin en el ncleo, hay un controlador de interrupciones centralizado (PIE) que arbitra las peticiones de interrupcin de diferentes fuentes (perifricos o pines externos). Las siguientes figuras muestran los diferentes niveles de interrupcin

17

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

18

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Si estn activas las mscaras de diferentes perifricos que pueden provocar el disparo de una misma interrupcin, se puede identificar cul es el perifrico que ha provocado la interrupcin con ayuda el PIV (peripheral interrupt vector). De esta manera, una vez dentro de la rutina de interrupcin asociada se pueden establecer saltos a diferentes trozos de cdigo en funcin del origen de la interrupcin. El ciclo de una interrupcin es el siguiente: 1. Se produce un evento de interrupcin (Ej. Underflow en T1). 2. El bit del flag asociado a dicho evento pasa a 1 (Ej. EVAIFRA.9=1). Este registro debe ser borrado por el usuario al atender la interrupcin. 3. Se revisa si la mscara asociada a dicho flag est habilitado (Ej. EVAIMRA.9=1). Si no est habilitado, la interrupcin queda bloqueada y nada sucede. De otro modo se contina con la secuencia. 4. Se solicita una interrupcin a travs del PIRQ.x respectivo (Peripheral interrupt request) (Ej. IRQ0.14). 5. Se carga en el registro PIVR la direccin del perifrico que gener la interrupcin (Ej. 0029h). 6. Se habilita el flag respectivo al nivel de interrupcin. (Ej. IFR.2=1). Este registro se borra automticamente si se atiende la interrupcin. 7. Se revisa si la mscara asociada al flag est habilitada (Ej. IMR.2=1). Si no est habilitada, la interrupcin queda bloqueada y nada sucede. De otro modo se contina con la secuencia. 8. Si el habilitador general de interrupciones est habilitado (INTM=0) se produce la interrupcin en la CPU.

19

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

En resumen se puede decir que hay 3 niveles de control de las interrupciones: Nivel global. El bit INTM permite habilitar (0) deshabilitar (1) todas las interrupciones enmascarables. Este bit se pone a 1 automticamente cuando el procesador atiende (ejecuta) una rutina de interrupcin. Por lo tanto ser necesario volver a ponerlo a 0 al final de la rutina (instruccin CLRC INTM). Nivel de interrupcin del procesador. Las mscaras del registro IMR permiten habilitar (1) deshabilitar (0) cada una de las 6 interrupciones hardware. Los flags del registro IFR son borrados automticamente por el procesador cuando la interrupcin es atendida, pro lo que no es necesario que los borre la rutina de usuario. Nivel de perifrico. Cada fuente de interrupcin de los perifricos tiene su propia mscara para habilitarlo y su flag. Los flags de este nivel no se borran automticamente por lo que es necesario borrarlos al final de la rutina de interrupcin. La rutina de interrupcin escrita en ensamblador por el usuario debe seguir los siguientes pasos: 1. Guardar el estado del procesador, es decir el valor de la parte alta y baja del acumulador y de los registros ST0 y ST1, en variables de la memoria RAM de datos. 2. Instrucciones de la rutina de usuario. 3. Borrar el flag de la interrupcin correspondiente a nivel de perifrico (si es una interrupcin hardware). 4. Restaurar el estado original del procesador (darle a la parte alta y baja del acumulador y a los registros ST0 y ST1 los valores originales guardados al principio de la rutina). 5. Habilitar globalmente las interrupciones. Instruccin CLRC INTM. Esto es necesario, pues el procesador las deshabilita cuando atiende la interrupcin. 6. Terminar la rutina con la instruccin RET ( RETC). Al ejecutar esta instruccin el PC se carga con el valor que hay en lo alto de la pila, por lo que se vuelve al programa principal. La rutina de interrupcin escrita en C por el usuario slo debe seguir los pasos 2 y 3, porque el compilador ya se encarga de generar las instrucciones en ensamblador correspondientes a los pasos 1, 4, 5 y 6. La siguiente figura muestra el flujo de programa que se sigue cuando se genera una interrupcin

20

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

La figura siguiente resume las interrupciones del DSP TMS320LF2407:

21

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Interrupciones software. Las interrupciones software sirven para ejecutar una subrutina de usuario. Por ejemplo, si en un momento dado del programa aparece la instruccin INTR 8 el procesador guarda el PC en la pila, y lo carga con el vector de la interrupcin software 8. En este vector debe haber una instruccin de salto a donde empieza la rutina que se quiere que se ejecute. Cuando termina la rutina con la instruccin RET se carga el PC con el valor de la pila y contina el programa principal. En este sentido el efecto de la interrupcin software es similar al de la instruccin CALL (llamada de subrutina). La diferencia con la instruccin CALL es que la instruccin INTR pone a 1 el bit INTM automticamente, por lo que hasta que no acaba la rutina de interrupcin software el procesador no atiende otras interrupciones hardware. Esta instruccin se podra utilizar para forzar la ejecucin de una de las rutinas asociadas a una interrupcin hardware, aunque no haya sucedido el evento que la provoca (por ejemplo INTR 3 ejecuta la rutina asociada con la interrupcin hardware INT3).

22

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

9 Perifricos del TMS320LF2407.

Adems del procesador, el DSP TMS320LF2407 dispone de varios perifricos integrados que permiten implementar el control de distintos procesos.

Entradas-salidas digitales.

El microcontrolador tiene 28 pines que pueden configurarse como entrada-salida digital o como otras funciones diversas. La figura siguiente muestra la estructura de uno de estos pines de entrada-salida digital. La asignacin del pin a la funcin primaria o a la entrada-salida digital se determina mediante los registros MCRA, MCRB y MCRC. Cuando el pin se configura como entrada-salida digital, sta puede configurarse como entrada o como salida individualmente (para ello se utilizan los registros P xDATDIR, con x = A, B, C, D, E, F, que contienen los bits que configuran como entrada o como salida, y los propios bits del valor de la entrada o la salida). La tabla siguiente muestra las principales entradas-salidas digitales, las funciones que comparten los pines y qu registro permite configurarlas. Cuando se utiliza uno de estos pines es necesario configurar adecuadamente los registros MCRA, MCRB y MCRC para elegir si se utiliza como entrada-salida digital, o con la funcin primaria.

23

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

24

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Manejador de eventos ("event manager").

Se conoce como manejador de eventos al conjunto de elementos hardware formados por los temporizadores, las unidades de captura y las unidades de comparacin y PWM. La figura siguiente resume la estructura del "event manager":

25

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Temporizadores.

Hay 4 temporizadores de 16 bits. Se pueden configurar en 3 modos de operacin diferentes, pudiendo ser ascendente, descendente o ambos. Los temporizadores siempre funcionan con recarga automtica. Adems disponen de un preescalado configurable entre 1/1, 1/2, 1/4, 1/8, ... 1/128 (se configura con 3 bits del registro TxCON). La figura siguiente muestra el esquema de uno de los temporizadores:

Los registros asociados con los temporizadores son: GPTCONA/B Contiene bits de configuracin de los 4 temporizadores. Adems de este registro existen 3 conjuntos de registros (uno para cada temporizador): TxCON Es el registro de configuracin del temporizador x (x=1,2,3 4). Se configura el preescalado, el modo de operacin, se habilita el temporizador, etc. TxPR Es el registro que contiene el periodo de cuenta. TxCMPR Es un registro que contiene un valor para comparar con la cuenta actual. TxCNT Es el registro que contiene el valor de la cuenta actual. El modo de operacin ascendente con recarga automtica se muestra en la figura:

Cuando el temporizador alcanza el valor del periodo se resetea y comienza de nuevo de forma automtica.

26

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

El modo de operacin ascendente-descendente se muestra en la figura:

El temporizador se incrementa hasta el periodo y despus se decrementa hasta cero, y as sucesivamente. El modo de operacin ascendente-descendente con entrada de direccin se muestra en la figura:

En este caso el temporizador se incrementa o decrementa segn el valor de la entrada de direccin (TDIRA/B=1 ascendente, TDIRA/B =0 descendente). Sea cual sea el modo en que funcionen los temporizadores tienen varias interrupciones asociadas: Periodo: se activa cuando el temporizador alcanza el valor del periodo (TxPINT) Comparacin: se activa cuando el temporizador alcanza el valor del registro de comparacin (TxCINT) Overflow: Se activa cuando el temporizador se sale por arriba del rango de 16 bits (pasa de FFFF a 0000). Underflow: se activa cuando el temporizador se sale por abajo del rango de 16 bits (pasa de 0000 a FFFF). Las mscaras de habilitacin y los flags de estas interrupciones estn en los registros EVxIMRy, EVxIFRy (x=A,B, y=A,B,C). Para generar una interrupcin peridica se suele utilizar la interrupcin del periodo, que permite definir el tiempo entre interrupciones simplemente escribiendo un valor adecuado en el registro del periodo. Los temporizadores 2 y 4 se pueden utilizar para contar los pulsos de la entrada de encoder incremental, en lugar de contar pulsos de reloj.

Salidas PWM asociadas a los temporizadores.

Hay 4 pines de salida (TxCMP/TxPWM con x=1,2,3 y 4) que permiten dar una seal digital modulada en ancho de pulso. Pueden ser activas a nivel alto activas a nivel bajo (se configura con el registro GPTCON). El ancho del pulso puede ser simtrico asimtrico. En el modo asimtrico el temporizador se incrementa hasta que su cuenta alcanza el valor de TxPR, momento en el cual se resetea a cero para volver a incrementarse. Cuando el valor de cuenta es mayor que TxCMPR la salida est activa, y cuando es menor inactiva:

TxPR TxCNT TxCMPR TxCMPR TxPR

t SALIDA

PWM ASIMTRICO

27

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

En el PWM simtrico el temporizador se incrementa hasta el valor de TxPR, pasando entonces a decrementarse hasta cero y as sucesivamente. La salida est activa cuando la cuenta actual es mayor que TxCMPR.

TxCNT TxCMPR TxPR TxPR

SALIDA

PWM SIMTRICO

Unidades de comparacin completa (Full compare units).

Constituyen 2 grupos de 3 pares de salidas PWM diseadas especialmente para atacar los 6 transistores de dos inversores trifsicos. Hay tres unidades de comparacin en el mdulo EVA (unidades 1, 2 y 3) y tres en el EVB (unidades 4, 5 y 6). Cada unidad de comparacin tiene dos salidas PWM asociadas Las 6 salidas de cada mdulo tienen el mismo periodo (controlado con el temporizador 1 en el EVA y con el temporizador 3 en el EVB) y un ancho de pulso programable para cada par individualmente. La figura siguiente muestra la estructura de las unidades de comparacin completas:

Pueden funcionar en modo asimtrico o en modo simtrico, igual que las salidas PWM de los temporizadores.

PWM ASIMTRICO

PWM SIMTRICO

T1CNT

T1CNT CMPR1 CMPR2 CMPR3 t PWM1 T1PR T1PR

T1PR CMPR1 CMPR2 CMPR3

T1PR

t PWM1

PWM3

PWM3

PWM5

PWM5

28

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Cada una de las 3 salidas anteriores tiene su complementaria para atacar los dos IGBT de una de las ramas del inversor (PWM1-PWM2, PWM3-PWM4, PWM5-PWM6). Las dos salidas de un mismo par nunca estn activas al mismo tiempo. Adems el sistema incorpora un tiempo muerto programable, de forma que desde que se desactiva una salida hasta que se activa la otra del mismo par transcurre un tiempo que se puede configurar. El tiempo muerto pretende garantizar que los dos transistores de una rama no estn nunca conduciendo a la vez (lo cual producira un cortocircuito).

T1CNT CMPR1

T1PR

T1PR

t PWM1 TIEMPO MUERTO PWM2

La configuracin de estas salidas PWM se realiza mediante los registros COMCONA/B, ACTRA/B, DBTCONA/B, CMPR1, CMPR2 y CMPR3.

Unidades de captura.

Son 6 entradas digitales conectadas a un mdulo especial que permite capturar el instante en que se activa cada entrada digital. Las unidades 1, 2 y 3 estn asociadas al EVA y las unidades 4, 5 y 6 estn asociadas al EVB. Cada unidad de captura del EVA pueden utilizar los temporizadores 1 y 2, y los del EVB pueden utilizar los temporizadores 3 y 4. Cada vez que se produce un pulso de subida en la entrada digital se almacena automticamente el valor del temporizador. La utilidad fundamental de estas unidades de captura es medir el periodo de una seal digital pulsante. Un ejemplo puede ser una seal de un encoder. El periodo de la seal depende de la velocidad de giro del eje, por lo que se puede utilizar para medir la velocidad del eje(=k/T). Otro ejemplo es la seal de un caudalmetro de turbina. En ese caso el periodo tambin es inversamente proporcional al caudal que circula. La figura siguiente muestra la estructura de las unidades de captura del EVA y del EVB:

29

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Para cada una de las 6 entradas existe un buffer tipo FIFO de 2 posiciones. Cuando se han producido 2 activaciones de la entrada el buffer contiene 2 tiempos. La diferencia entre ellos da el periodo de la seal digital. Al leer el registro CAPxFIFO (con x=1,,6) se lee el valor ms antiguo del buffer. Al volver a leer ese mismo registro se obtiene el valor ms nuevo. Si estando lleno el buffer se produce otra activacin de la seal, el buffer pierde el valor ms antiguo. En todo caso, si se est midiendo el periodo de una seal, en cualquier momento el buffer contendr los dos ltimos tiempos en que se produjo el pulso de subida, por lo que la diferencia de esos tiempos dar el periodo. Para configurar una unidad de captura A (para leer el periodo de una seal por ejemplo) hay que seguir los siguientes pasos: 1. Inicializar el registro CAPFIFOA. 2. Configurar el temporizador 1. 3. Configurar el registro CAPCONA. Para leer el periodo de la seal se lee dos veces seguidas el registro CAPxFIFO. La primera vez se obtiene el tiempo ms antiguo (tiempo menor) y la segunda vez se obtiene el tiempo ms nuevo (mayor). La diferencia entre ambos es el periodo de la seal.

Entradas de encoder (QEP)

Tanto el EVA como el EVB tienen un circuito QEP (quadrature encoder pulse) que permite conectar directamente las fases A y B de un encoder. El circuito QEP se asocia al temporizador 2 en el caso del EVA (pines QEP1 y QEP2) y al temporizador 4 en el caso del EVB (pines QEP3 y QEP4). La cuenta del temporizador (T2CNT o T4CNT) se incrementar o decrementar (dependiendo de la direccin de la rotacin) con cada flanco posible de las fases A y B del encoder. La DSP cuenta 4 pulsos por cada ciclo de las fases A y B. Las figuras siguiente muestra el funcionamiento de esta unidad.

La base de tiempos para el circuito QEP viene dada por el temporizador 2 (4 en el EVB). El temporizador debe configurarse en modo ascendente/descendente teniendo el circuito QEP como entrada de reloj. El bit de direccin del temporizador 2 lo cambiar el circuito QEP. Para configurar la lectura de encoder, en primer lugar se han de inicializar los registros del temporizador 2 y luego configurar T2CON (o T4CON en el EVB) en modo ascendente/descendente direccional, indicando el circuito QEP como fuente entrada de reloj, y habilitar el temporizador (T2CON.6=1).

30

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Convertidores AD.

El TMS320LF2407 dispone de un convertidor AD de 10 bits de resolucin con un multiplexor analgico de 16 entradas, que permiten leer un total de 16 canales de entrada analgica (ADCIN0- ADCIN15). La figura siguiente muestra la estructura de los convertidores AD:

De acuerdo con los registros de control es posible elegir qu canales se utilizarn y en qu orden se realizar la conversin. Adems es posible configurar el tipo de evento que inicia un lote de conversiones, que puede iniciarse por eventos externos al DSP, temporizadores o va software. Los resultados de las conversiones se guardan respetando el orden de conversin en los registros RESULT0-RESULT15. El formato del valor ledo es:

15 D9

D8

D7

... D6

D5

D4

D3

D2

D1

6 D0

5 0 0

... 0 0

1 0

0 0

Resultado de la conversin

Es decir, los 10 bits de la conversin ocupan los 10 bits ms significativos del registro que se lee del RESULTx. Como el resultado de la conversin es en realidad un nmero entre 0 y 1023, si se quiere copiar el valor convertido al acumulador habr que poner el bit SXM a 0, ya que si no el desplazador de entrada puede interpretarlo como un nmero negativo expresado en complemento a 2, en cuyo caso completar los bits de la izquierda con unos en lugar de ceros. La configuracin de los convertidores AD se realiza mediante los registros ADCTRL1, ADCTRL2, MAXCONV, y

CHSELSEQn:

31

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Bit 14: Resetea todos los registros del conversor A/D. Bits 13-12: Establece el comportamiento del conversor A/D en un breakpoint. Bits 11-8: Prescalado de reloj para la conversin (ancho de la ventana). Bit 7: Prescalado de reloj general. Bit 6: Conversin continua (termina un ciclo y se reinicia automticamente) o iniciada por un evento. Bit 5: Prioridad de una interrupcin del ADC. Bit 4: Un secuenciador de 16 estados o dos secuenciadores de 8 estados. Bit 3-0: Control de calibracin.

Bit 15: Las conversiones seteadas en el secuenciador de 16 estados se inician por un evento del Event Manager B (EVB) Bit 14: Reinicia el secuenciador 1 (8 estados) al estado 0. Bit 13: Seal de inicio para el secuenciador 1 (seteado automticamente al ocurrir el evento predefinido), escribir un 0 cancela el inicio automtico. Bit 12: Indica si la secuencia 1 est en proceso. Se pone a 0 cuando ha terminado la conversin. Bit 11-10: Habilita el generador de interrupciones al terminar la secuencia 1 o una conversin. Bit 9: Indicador de que se produjo un evento de interrupcin generado por la secuencia 1. Bit 8: Permite que un evento del Event Manager A (EVA) inicie la secuencia 1. Bit 7: Permite que un evento externo inicie la secuencia 1. Bit 6: Reinicia el secuenciador 2 (8 estados) al estado 8 (estado inicial de este secuenciador). Bit 5: Seal de inicio para el secuenciador 2 (seteado automticamente al ocurrir el evento predefinido), escribir un 0 cancela el inicio automtico. Bit 4: Indica si la secuencia 2 est en proceso. Se pone a 0 cuando ha terminado la conversin. Bit 3-2: Habilita el generador de interrupciones al terminar la secuencia 2 o una conversin. Bit 1: Indicador de que se produjo un evento de interrupcin generado por la secuencia 2. Bit 0: Permite que un evento del Event Manager B (EVB) inicie la secuencia 2. MAXCONV: Cantidad de conversiones a utilizar en cada secuenciador. Mximo 8 por secuenciador. CHSELSEQn: Indica el orden de canales a convertir.

32

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Interfaz de comunicacin serie (SCI).

Es un mdulo que permite comunicar el microcontrolador con otro elemento que disponga de puerto serie asncrono (RS232 RS485). Como las salidas del microcontrolador son entre 0 y 5V, se necesita un circuito integrado que realice el cambio a la tensin necesaria para la RS232 o para la RS485. Un integrado tpico de este tipo es el MAX232 o el MAX485. La tarjeta de desarrollo del laboratorio eZdsp LF2407 no dispone de esos integrados, por lo que para comunicar con un ordenador por RS232 sera necesario un circuito intermedio con el chip MAX232 (u otro equivalente).

33

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

Interfaz de perifricos serie (SPI).

Es un mdulo que permite la comunicacin con otro elemento que disponga de un puerto serie sncrono. Se utiliza para comunicar el microcontrolador con otros perifricos de la misma tarjeta (memorias EEPROM, convertidores DA, displays, etc).

Mdulo CAN.

Es un mdulo que permite la comunicacin a travs de un bus CAN. La arquitectura bsica del controlador CAN es la que se muestra en la figura:

Los mensajes tienen la forma que se indica en la figura:

34

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

10 Ejemplos de programas.

En este ejemplo se muestra un mismo programa tanto en lenguaje C como en ensamblador. Cada ejemplo realiza las siguientes tareas en la DSP Configura los registros SCSR1 y SCSR2 (System Control and Status Register) Deshabilita el perro guardin Configura la interfa z de memoria externa Configura los pines compartidos Configura el temporizador 1 (GP Timer 1) y las unidades de comparacin para proporcionar una seal PWM simtrica de 20 kHz y ciclo de trabajo del 25% en el pin PWM1 Configura el temporizador 2 (GP Timer 2) para dar una interrupcin cada 200 ms En la rutina de interrupcin del temporizador 2 se realizan las siguientes tareas: o Se salva el entorno o Se conmuta el pin IOPA0

Programa en C.

/********************************************************************* * Filename: example.cmd * * * * Description: Assembly code linker command file for LF2407 DSP. * *********************************************************************/ MEMORY { PAGE 0: /* Program Memory */ VECS: org=00000h, len=00040h /* internal FLASH */ FLASH: org=00044h, len=07FBCh /* internal FLASH */ EXTPROG: org=08800h, len=07800h /* external SRAM */ PAGE 1: /* Data Memory */ B2: org=00060h, B0: org=00200h, B1: org=00300h, SARAM: org=00800h, EXTDATA: org=08000h, } SECTIONS { .text: .bss: .vectors: stack: }

len=00020h len=00100h len=00100h len=00800h len=08000h

/* /* /* /* /*

internal internal internal internal external

DARAM DARAM DARAM SARAM SRAM

*/ */ */ */ */

> > > >

FLASH B1 VECS SARAM

PAGE PAGE PAGE PAGE

0 1 0 1

********************************************************************** * Filename: cvectors.asm * ********************************************************************** .ref _c_int0, _timer2_isr .sect B B B B B B B ".vectors" _c_int0 int1 int2 _timer2_isr int4 int5 int6

rset: int1: int2: int3: int4: int5: int6:

;00h ;02h ;04h ;06h ;08h ;0Ah ;0Ch

reset INT1 INT2 INT3 INT4 INT5 INT6

35

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

int7: int8: int9: int10: int11: int12: int13: int14: int15: int16: int17: int18: int19: int20: int21: int22: int23: int24: int25: int26: int27: int28: int29: int30: int31:

B B B B B B B B B B B B B B B B B B B B B B B B B

int7 int8 int9 int10 int11 int12 int13 int14 int15 int16 int17 int18 int19 int20 int21 int22 int23 int24 int25 int26 int27 int28 int29 int30 int31

;0Eh ;10h ;12h ;14h ;16h ;18h ;1Ah ;1Ch ;1Eh ;20h ;22h ;24h ;26h ;28h ;2Ah ;2Ch ;2Eh ;30h ;32h ;34h ;36h ;38h ;3Ah ;3Ch ;3Eh

reserved INT8 (software) INT9 (software) INT10 (software) INT11 (software) INT12 (software) INT13 (software) INT14 (software) INT15 (software) INT16 (software) TRAP NMI reserved INT20 (software) INT21 (software) INT22 (software) INT23 (software) INT24 (software) INT25 (software) INT26 (software) INT27 (software) INT28 (software) INT29 (software) INT30 (software) INT31 (software)

/********************************************************************* * Filename: example_c.c * * * * Description: This program illustrates basic initialization and * * operation of the LF2407 DSP. The following peripherals are * * exercised: * * 1) Timer 2 is configured to generate a 200ms period interrupt. * * 2) The IOPA0 pin is toggled in the Timer2 ISR. * * 3) Timer 1 is configured to drive 20KHz 25% duty cycle symmetric * * PWM on the PWM1 pin. * * * *********************************************************************/ /*** Address Definitions ***/ #include "f2407_c.h"

/*** Constant Definitions ***/ #define timer2_per 62500

/* 200ms timer2 period with a 1/128 timer prescaler and 30MHz CPUCLK */ /* period/2, 20KHz symmetric PWM with a 40MHz CPUCLK */ /* 25% PWM duty cycle */

#define

pwm_half_per

1000

#define

pwm_duty

750

/****************************** MAIN ROUTINE ***************************/ void main(void) { /*** Configure the System Control and Status registers ***/ *SCSR1 = 0x00FD; /* bit 15 0: reserved

36

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

bit bit bit bit bit bit bit bit bit bit bit bit */

14 13-12 11-9 8 7 6 5 4 3 2 1 0

0: 00: 000: 0: 1: 1: 1: 1: 1: 1: 0: 1:

CLKOUT = CPUCLK IDLE1 selected for low-power mode PLL x4 mode reserved 1 = enable ADC module clock 1 = enable SCI module clock 1 = enable SPI module clock 1 = enable CAN module clock 1 = enable EVB module clock 1 = enable EVA module clock reserved clear the ILLADR bit

*SCSR2 = (*SCSR2 | 0x000B) & 0x000F; /* bit bit bit bit bit bit */ 15-6 5 4 3 2 1-0 0's: 0: 0: 1: no change 11: reserved do NOT clear the WD OVERRIDE bit XMIF_HI-Z, 0=normal mode, 1=Hi-Z'd disable the boot ROM, enable the FLASH MP/MC* bit reflects state of MP/MC* pin 11 = SARAM mapped to prog and data

/*** Disable the watchdog timer ***/ *WDCR = 0x00E8; /* bits 15-8 0's: reserved bit 7 1: clear WD flag bit 6 1: disable the dog bit 5-3 101: must be written as 101 bit 2-0 000: WDCLK divider = 1 */ /*** Setup external memory interface for LF2407 EVM ***/ WSGR = 0x0040; /* bit 15-11 0's: reserved bit 10-9 00: bus visibility off bit 8-6 001: 1 wait-state for I/O space bit 5-3 000: 0 wait-state for data space bit 2-0 000: 0 wait state for program space */ /*** Setup shared I/O pins ***/ *MCRA = 0x1040; /* bit 15 0: 0=IOPB7, bit 14 0: 0=IOPB6, bit 13 0: 0=IOPB5, bit 12 1: 0=IOPB4, bit 11 0: 0=IOPB3, bit 10 0: 0=IOPB2, bit 9 0: 0=IOPB1, bit 8 0: 0=IOPB0, bit 7 0: 0=IOPA7, bit 6 1: 0=IOPA6, bit 5 0: 0=IOPA5, bit 4 0: 0=IOPA4, bit 3 0: 0=IOPA3, bit 2 0: 0=IOPA2,

/* group A pins */ 1=TCLKINA 1=TDIRA 1=T2PWM/T2CMP 1=T1PWM/T1CMP 1=PWM6 1=PWM5 1=PWM4 1=PWM3 1=PWM2 1=PWM1 1=CAP3 1=CAP2/QEP2 1=CAP1/QEP1 1=XINT1

****

37

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

bit 1 bit 0 */

0: 0:

0=IOPA1, 0=IOPA0,

1=SCIRXD 1=SCITXD

****

/*** Configure IOPA0 pin as an output ***/ *PADATDIR = *PADATDIR | 0x0100; /*** Setup timers 1 and 2, and the PWM configuration ***/ *T1CON = 0x0000; /* disable timer 1 */ *T2CON = 0x0000; /* disable timer 2 */ *GPTCONA = 0x0042; /* bit bit bit bit bit bit bit bit bit bit */ 15 14 13 12-11 10-9 8-7 6 5-4 3-2 1-0 0: 0: 0: 00: 00: 00: 1: 00: 00: 10: /* configure GPTCONA */ reserved T2STAT, read-only T1STAT, read-only reserved T2TOADC, 00 = no timer2 event starts ADC T1TOADC, 00 = no timer1 event starts ADC TCOMPOE, 1 = Enable all GP Timer compare outputs reserved T2PIN, 00 = forced low T1PIN, 10 = active high

/* Timer 1: configure to clock the PWM on PWM1 pin */ /* Symmetric PWM, 20KHz carrier frequency, 25% duty cycle */ *T1CNT = 0x0000; /* clear timer counter */ *T1PR = pwm_half_per; /* set timer period */ *T1CMPR = pwm_duty; /* set T1PWM duty cycle */ *T1CON = 0x0842; /* configure T1CON register */ /* bit 15-14 00: stop immediately on emulator suspend bit 13 0: reserved bit 12-11 01: 01 = continous-up/down count mode bit 10-8 000: 000 = x/1 prescaler bit 7 0: reserved in T1CON bit 6 1: TENABLE, 1 = enable timer bit 5-4 00: 00 = CPUCLK is clock source bit 3-2 00: 00 = reload compare reg on underflow bit 1 1: 1 = enable timer compare bit 0 0: reserved in T1CON */ /* Timer 2: configure to generate a 200ms periodic interrupt */ *T2CNT = 0x0000; /* clear timer counter */ *T2PR = timer2_per; /* set timer period */ *T2CON = 0xD740; /* configure T2CON register */ /* bit 15-14 11: operation is not affected by emulation bit 13 0: reserved bit 12-11 10: 10 = continous-up count mode bit 10-8 111: 111 = x/128 prescaler bit 7 0: T2SWT1, 0 = use own TENABLE bit bit 6 1: TENABLE, 1 = enable timer bit 5-4 00: 00 = CPUCLK is clock source bit 3-2 00: 00 = reload compare reg on underflow bit 1 0: 0 = disable timer compare bit 0 0: SELT1PR, 0 = use own period register */

38

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

/*** Setup *IMR = *IFR = *IMR =

the core interrupts ***/ 0x0000; 0x003F; 0x0004;

/* clear the IMR register */ /* clear any pending core interrupts */ /* enable desired core interrupts */

/*** Setup the event manager interrupts ***/ *EVAIFRB = 0xFFFF; /* clear all EVA group B interrupts */ *EVAIMRB = 0x0001; /* enable desired EVA group B interrupts */ /*** Enable global interrupts ***/ asm(" CLRC INTM"); /*** Proceed with main routine ***/ while(1); }

/* enable global interrupts */

/* endless loop, wait for interrupt */ /* end of main() */

/********************** INTERRUPT SERVICE ROUTINES *********************/ interrupt void timer2_isr(void) { *EVAIFRB = *EVAIFRB & 0x0001; /*** Toggle the IOPA0 pin ***/ *PADATDIR = *PADATDIR ^ 0x0001; } /* clear T2PINT flag */ /* XOR the IOPA0 bit to toggle the pin */

Programa en ensamblador.

********************************************************************** * Filename: vectors.asm * ********************************************************************** .ref start, timer2_isr .sect B B B B B B B B B B B B B B B B B B B B B B B ".vectors" start int1 int2 timer2_isr int4 int5 int6 int7 int8 int9 int10 int11 int12 int13 int14 int15 int16 int17 int18 int19 int20 int21 int22

rset: int1: int2: int3: int4: int5: int6: int7: int8: int9: int10: int11: int12: int13: int14: int15: int16: int17: int18: int19: int20: int21: int22:

;00h ;02h ;04h ;06h ;08h ;0Ah ;0Ch ;0Eh ;10h ;12h ;14h ;16h ;18h ;1Ah ;1Ch ;1Eh ;20h ;22h ;24h ;26h ;28h ;2Ah ;2Ch

reset INT1 INT2 INT3 INT4 INT5 INT6 reserved INT8 (software) INT9 (software) INT10 (software) INT11 (software) INT12 (software) INT13 (software) INT14 (software) INT15 (software) INT16 (software) TRAP NMI reserved INT20 (software) INT21 (software) INT22 (software)

39

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

int23: int24: int25: int26: int27: int28: int29: int30: int31:

B B B B B B B B B

int23 int24 int25 int26 int27 int28 int29 int30 int31

;2Eh ;30h ;32h ;34h ;36h ;38h ;3Ah ;3Ch ;3Eh

INT23 INT24 INT25 INT26 INT27 INT28 INT29 INT30 INT31

(software) (software) (software) (software) (software) (software) (software) (software) (software)

********************************************************************** * Filename: example.asm * ********************************************************************** ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Global symbol declarations ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ .def start, timer2_isr ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Address definitions ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ .include f2407.h ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Constant definitions ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ timer2_per .set 62500 ;200ms timer2 period with a 1/128 ;timer prescaler and 30MHz CPUCLK pwm_half_per .set 1000 ;period/2, 20KHz symmetric PWM with ;a 40MHz CPUCLK pwm_duty .set 750 ;25% PWM duty cycle ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Uninitialized global variable definitions ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ .bss temp1,1 ;general purpose variable ********************************************************************** * M A I N R O U T I N E * ********************************************************************** .text start: ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Configure the System Control and Status Registers ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ LDP #DP_PF1 ;set data page SPLK #0000000011111101b, SCSR1 * |||||||||||||||| * FEDCBA9876543210 * bit 15 0: reserved * bit 14 0: CLKOUT = CPUCLK * bit 13-12 00: IDLE1 selected for low-power mode * bit 11-9 000: PLL x4 mode * bit 8 0: reserved * bit 7 1: 1 = enable ADC module clock * bit 6 1: 1 = enable SCI module clock * bit 5 1: 1 = enable SPI module clock * bit 4 1: 1 = enable CAN module clock * bit 3 1: 1 = enable EVB module clock * bit 2 1: 1 = enable EVA module clock * bit 1 0: reserved * bit 0 1: clear the ILLADR bit LACC SCSR2 ;ACC = SCSR2 register OR #0000000000001011b ;OR in bits to be set

40

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

AND * * * * * * * *

bit bit bit bit bit bit

15-6 5 4 3 2 1-0

#0000000000001111b ;AND out bits to be cleared |||||||||||||||| FEDCBA9876543210 0's: reserved 0: do NOT clear the WD OVERRIDE bit 0: XMIF_HI-Z, 0=normal mode, 1=Hi-Z'd 1: disable the boot ROM, enable the FLASH no change MP/MC* bit reflects the state of the MP/MC* pin 11: 11 = SARAM mapped to prog and data (default)

SACL SCSR2 ;store to SCSR2 register ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Disable the watchdog timer ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ LDP #DP_PF1 ;set data page SPLK #0000000011101000b, WDCR * |||||||||||||||| * FEDCBA9876543210 * bits 15-8 0's reserved * bit 7 1: clear WD flag * bit 6 1: disable the dog * bit 5-3 101: must be written as 101 * bit 2-0 000: WDCLK divider = 1 ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Setup external memory interface for LF2407 EVM ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ LDP #temp1 ;set data page SPLK #0000000001000000b, temp1 * |||||||||||||||| * FEDCBA9876543210 * bit 15-11 0's: reserved * bit 10-9 00: bus visibility off * bit 8-6 001: 1 wait-state for I/O space * bit 5-3 000: 0 wait-state for data space * bit 2-0 000: 0 wait state for program space OUT temp1, WSGR ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Setup shared I/O pins ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ LDP #DP_PF2 ;set data page SPLK #0001000001000000b,MCRA ;group A pins * |||||||||||||||| * FEDCBA9876543210 * bit 15 0: 0=IOPB7, 1=TCLKINA * bit 14 0: 0=IOPB6, 1=TDIRA * bit 13 0: 0=IOPB5, 1=T2PWM/T2CMP * bit 12 1: 0=IOPB4, 1=T1PWM/T1CMP * bit 11 0: 0=IOPB3, 1=PWM6 * bit 10 0: 0=IOPB2, 1=PWM5 * bit 9 0: 0=IOPB1, 1=PWM4 * bit 8 0: 0=IOPB0, 1=PWM3 * bit 7 0: 0=IOPA7, 1=PWM2 * bit 6 1: 0=IOPA6, 1=PWM1 * bit 5 0: 0=IOPA5, 1=CAP3 * bit 4 0: 0=IOPA4, 1=CAP2/QEP2 * bit 3 0: 0=IOPA3, 1=CAP1/QEP1 * bit 2 0: 0=IOPA2, 1=XINT1 * bit 1 0: 0=IOPA1, 1=SCIRXD * bit 0 0: 0=IOPA0, 1=SCITXD ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

41

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

;Configure IOPA0 pin as an output ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ LDP #DP_PF2 ;set data page LACC #0100h ;ACC = 0100h OR PCDATDIR ;OR in PCDATDIR register SACL PCDATDIR ;store result to PCDATDIR ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Setup the software stack ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ stk_len .set 100 ;stack length stk .usect "stack",stk_len ;reserve space for stack LAR AR1, #stk ;AR1 is the stack pointer ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Setup timers 1 and 2, and the PWM configuration ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ LDP #DP_EVA ;set data page SPLK #0000h, T1CON ;disable timer 1 SPLK #0000h, T2CON ;disable timer 2 SPLK #0000000000000000b, GPTCONA * |||||||||||||||| * FEDCBA9876543210 * bit 15 0: reserved * bit 14 0: T2STAT, read-only * bit 13 0: T1STAT, read-only * bit 12-11 00: reserved * bit 10-9 00: T2TOADC, 00 = no timer2 event starts ADC * bit 8-7 00: T1TOADC, 00 = no timer1 event starts ADC * bit 6 1: TCOMPOE, 1 = Enable all GP Timer compare outputs * bit 5-4 00: reserved * bit 3-2 00: T2PIN, 00 = forced low * bit 1-0 10: T1PIN, 10 = active high ;Timer 1: Configure to clock the PWM on PWM1 pin. ;Symmetric PWM, 20KHz carrier frequency, 25% duty cycle SPLK #0000h, T1CNT ;clear timer counter SPLK #pwm_half_per, T1PR ;set timer period SPLK #pwm_duty, T1CMPR ;set PWM duty cycle SPLK #0000100001000010b, T1CON * |||||||||||||||| * FEDCBA9876543210 * bit 15-14 00: stop immediately on emulator suspend * bit 13 0: reserved * bit 12-11 01: 01 = continous-up/down count mode * bit 10-8 000: 000 = x/1 prescaler * bit 7 0: reserved in T1CON * bit 6 1: TENABLE, 1 = enable timer * bit 5-4 00: 00 = CPUCLK is clock source * bit 3-2 00: 00 = reload compare reg on underflow * bit 1 1: 1 = enable timer compare * bit 0 0: reserved in T1CON ;Timer 2: configure to generate a 200ms periodic interrupt SPLK #0000h, T2CNT ;clear timer counter SPLK #timer2_per, T2PR ;set timer period SPLK #1101011101000000b, T2CON * |||||||||||||||| * FEDCBA9876543210 * bit 15-14 11: stop immediately on emulator suspend * bit 13 0: reserved * bit 12-11 10: 10 = continous-up count mode

42

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

* bit 10-8 111: 111 = x/128 prescaler * bit 7 0: T2SWT1, 0 = use own TENABLE bit * bit 6 1: TENABLE, 1 = enable timer * bit 5-4 00: 00 = CPUCLK is clock source * bit 3-2 00: 00 = reload compare reg on underflow * bit 1 0: 0 = disable timer compare * bit 0 0: SELT1PR, 0 = use own period register ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Setup the core interrupts ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ LDP #0h ;set data page SPLK #0h,IMR ;clear the IMR register SPLK #111111b,IFR ;clear any pending core interrupts SPLK #000100b,IMR ;enable desired core interrupts ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Setup the event manager interrupts ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ LDP #DP_EVA ;set data page SPLK #0FFFFh, EVAIFRB ;clear all EVA group B interrupts SPLK #00001h, EVAIMRB ;enabled desired EVA group B interrupts ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Enable global interrupts ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ CLRC INTM ;enable global interrupts ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;Main loop ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ loop: NOP B loop ;branch to loop ********************************************************************** * I N T E R R U P T S E R V I C E R O U T I N E S * ********************************************************************** ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ;GP Timer 2 period interrupt (core interrupt INT3) ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ timer2_isr: ;Context save to the software stack MAR *,AR1 ;ARP=stack pointer MAR *+ ;skip one stack location (required) SST #1, *+ ;save ST1 SST #0, *+ ;save ST0 SACH *+ ;save ACCH SACL *+ ;save ACCL ;Clear the T2PINT interrupt flag LDP #DP_EVA ;set data page SPLK #00001h, EVAIFRB ;clear T2PINT flag ;Toggle the IOPC0 pin LDP #DP_PF2 ;set data page LACC #0001h ;ACC = 0001h XOR PADATDIR ;XOR the IOPC0 bit to toggle the pin SACL PADATDIR ;store result to PCDATDIR ;context restore from the software stack MAR *, AR1 ;ARP = AR1 MAR *;SP points to last entry LACL *;restore ACCL ADD *-,16 ;restore ACCH LST #0, *;restore ST0 LST #1, *;restore ST1, unskip one stack location CLRC INTM ;re-enable interrupts

43

Computadores Industriales. Tema : Procesadores Digitales de Seal (DSP).

RET

;return from the interrupt

44

Anda mungkin juga menyukai

- Protecciones Con DigsilentDokumen145 halamanProtecciones Con DigsilentJosue Zuñiga100% (1)

- Ejercicios GrafcetDokumen4 halamanEjercicios GrafcetRonald Eder Chavez Palomino100% (2)

- PS501 V2.0 Mi Primer ProyectoDokumen15 halamanPS501 V2.0 Mi Primer ProyectoRonald Eder Chavez PalominoBelum ada peringkat

- Sentron Pac3100 Manual Es 01 Es-MXDokumen174 halamanSentron Pac3100 Manual Es 01 Es-MXmecatronicatres100% (3)

- Tipo de MicrologixDokumen10 halamanTipo de MicrologixgerzaelBelum ada peringkat

- Laboratorio 6Dokumen25 halamanLaboratorio 6Raul Medrano Tantaruna100% (1)

- Disparo Del Tiristor Con Componentes DiscretosDokumen13 halamanDisparo Del Tiristor Con Componentes DiscretosRonald Eder Chavez PalominoBelum ada peringkat

- Adc Pic16f877Dokumen17 halamanAdc Pic16f877jv047050% (2)

- Teoria Maquinas de EstadoDokumen28 halamanTeoria Maquinas de EstadoRonald Eder Chavez PalominoBelum ada peringkat

- Problemas de Circuitos DigitalesDokumen16 halamanProblemas de Circuitos DigitalesRonald Eder Chavez PalominoBelum ada peringkat

- Teoria Maquinas de EstadoDokumen28 halamanTeoria Maquinas de EstadoRonald Eder Chavez PalominoBelum ada peringkat

- Unidad2 - Paso2 - Carlos Daney - MancillaDokumen6 halamanUnidad2 - Paso2 - Carlos Daney - MancillacdmancillaBelum ada peringkat

- PCM Script en MatlabDokumen5 halamanPCM Script en MatlabAndres Felipe Llanten MontillaBelum ada peringkat

- Paso1 - Yenny SantamariaDokumen8 halamanPaso1 - Yenny SantamariaSM GESTION Y CONSULTORIA SASBelum ada peringkat

- Mae StriaDokumen47 halamanMae Striajhon_jnBelum ada peringkat

- Transformada de Fourier ExposicionDokumen27 halamanTransformada de Fourier ExposicionPAOPK2100% (1)

- Cap2 - 01 - TRATAMIENTO DE SEÑALES EN TIEMPO DISCRETO PDFDokumen32 halamanCap2 - 01 - TRATAMIENTO DE SEÑALES EN TIEMPO DISCRETO PDFrodrigo_rh100% (1)

- Tarea - Muestreo IDokumen2 halamanTarea - Muestreo ICarlos LunaBelum ada peringkat

- 4 - ADC (Conversion de Señales Analogicas A Digitales)Dokumen23 halaman4 - ADC (Conversion de Señales Analogicas A Digitales)Marian OlivaresBelum ada peringkat

- MODULO - ADC Del DsPICDokumen24 halamanMODULO - ADC Del DsPICOlesya SergeevaBelum ada peringkat

- Ejercicios Cap. 1 de Señales y SistemasDokumen3 halamanEjercicios Cap. 1 de Señales y SistemasArturo M.R.Belum ada peringkat

- Producto Academico DosDokumen5 halamanProducto Academico DosFABIO LUJAN RODAS100% (1)

- Felipe Leon Grupo40 Tarea2Dokumen7 halamanFelipe Leon Grupo40 Tarea2AndresFelipeLeonBelum ada peringkat

- 10 Ateos Cambian de AutobúsDokumen62 halaman10 Ateos Cambian de AutobúsFidel Angel Rafael AlonsoBelum ada peringkat

- GUÍA DE LABORATORIO 1 Introd A Code Composer y Generacion de Señales C6711. Univ Federico SantamariaDokumen19 halamanGUÍA DE LABORATORIO 1 Introd A Code Composer y Generacion de Señales C6711. Univ Federico SantamariaalexloperBelum ada peringkat

- Clase Interpolacion Trigonometrica DFT FFT 2016 PDFDokumen36 halamanClase Interpolacion Trigonometrica DFT FFT 2016 PDFAnonymous IWpXYQfH3Belum ada peringkat

- EL 3005 Cap3Dokumen210 halamanEL 3005 Cap3felres87Belum ada peringkat

- Análisis de Señales en Tiempo Discreto y Sistemas LinealesDokumen50 halamanAnálisis de Señales en Tiempo Discreto y Sistemas LinealesAlejandro MackayaBelum ada peringkat

- Ejercicio3.7 Com AnalogicaDokumen5 halamanEjercicio3.7 Com Analogicajudox HuamanBelum ada peringkat

- DSP I - Laboratorio IDokumen19 halamanDSP I - Laboratorio IJohan Andres Herrera ReyesBelum ada peringkat

- Una Señal Continua de ElectrocardiogramaDokumen3 halamanUna Señal Continua de ElectrocardiogramaGeorvi VinicioBelum ada peringkat

- Filtros DiscretosDokumen24 halamanFiltros DiscretosMarianaArellanoBelum ada peringkat

- Informe Previo 4Dokumen17 halamanInforme Previo 4walterBelum ada peringkat

- Convolución DiscretaDokumen5 halamanConvolución DiscretaHumberto Ramírez GascaBelum ada peringkat

- Corona Receptor RP8D1Dokumen5 halamanCorona Receptor RP8D1AnDres F. SilVestreBelum ada peringkat

- Procesamiento Digital de SeñalesDokumen2 halamanProcesamiento Digital de SeñalesAnonymous 5qQ7p62J7Belum ada peringkat

- Procesamiento Digital de SeñalesDokumen7 halamanProcesamiento Digital de SeñalesJordi PGBelum ada peringkat