EC Lab Manual

Diunggah oleh

Mohan KumarDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

EC Lab Manual

Diunggah oleh

Mohan KumarHak Cipta:

Format Tersedia

ELECTRONIC CIRCUITS LABORATARY

10CSL38

1a. CLIPPING AND CLAMPING CIRCUITS

AIM : To study the working of positive clipper, double ended clipper and positive clamper using diodes. COMPONENTS REQUIRED : Diode (BY-127 / 1N4007), Resistors-10 K & 3.3k, DC regulated power supply (for Vref), Signal generator (for Vi) and CRO. CIRCUIT DIAGRAM OF POSITIVE CLIPPER

Fig.1 a Positive clipper Circuit

b. Transfer Characteristics

Clippers clip off a portion of the input signal without distorting the remaining part of the waveform. In the positive clipper shown above the input waveform above Vref is clipped off. If Vref = 0V, the entire positive half of the input waveform is clipped off. Plot of input Vi (along X-axis) versus output Vo (along Y-axis) called transfer characteristics of the circuit can also be used to study the working of the clippers. Choose R value such that R = R f Rr where Rf = 100 and Rr = 100K are the resistances of the forward and reverse diode respectively. Hence R = 3.3K. Let the output resistance RL = 10K. The simulations can be done even without RL. PROCEDURE: 1. Before making the connections check all components using multimeter. 2. Make the connections as shown in circuit diagram. 3. Using a signal generator (Vi) apply a sine wave of 1KHz frequency and a peak-topeak amplitude of 10V to the circuit. (Square wave can also be applied.) 4. Keep the CRO in dual mode, connect the input (Vi) signal to channel 1 and output waveform (Vo) to channel 2. Observe the clipped output waveform which is as shown in fig. 2. Also record the amplitude and time data from the waveforms. 5. Now keep the CRO in X-Y mode and observe the transfer characteristic waveform. Note: 1. Vary Vref and observe the variation in clipping level. For this use variable DC power supply for Vref. 2. Change the direction of diode and Vref to realize a negative clipper. 3. For double-ended clipping circuit, make the circuit connections as shown in fig.3 and the output waveform observed is as shown in figure 5. 4. Adjust the ground level of the CRO on both channels properly and view the ouput in DC mode (not in AC mode) for both clippers and clampers. Page 1

Dept. of CSE, SJBIT

ELECTRONIC CIRCUITS LABORATARY

10CSL38

WAVEFORMS

Fig. 2. Input and output waveform for positive Clipper

DOUBLE ENDED CLIPPER

Fig.3 Double ended clipper Circuit

b. Transfer Characteristics

Fig. 4. Input and output waveform for double-ended clipping circuit Note: The above clipper circuits are realized using the diodes in parallel with the load (at the output), hence they are called shunt clippers. The positive (and negative) clippers can also be realized in the series configuration wherein the diode is in series with the load. These circuits are called series clippers. Page 2

Dept. of CSE, SJBIT

ELECTRONIC CIRCUITS LABORATARY

10CSL38

POSITIVE CLAMPER

COMPONENTS REQUIRED: Diode (BY-127), Resistor of 200 K, Capacitor - 0.1 F, DC regulated power supply, Signal generator, CRO

Fig. 5 Positive Clamper The clamping network is one that will clamp a signal to a different DC level. The network must have a capacitor, a diode and a resistive element, but it can also employ an independent DC supply (Vref) to introduce an additional shift. The magnitude of R and C must be chosen such that time constant =RC is large enough to ensure the voltage across capacitor does not discharge significantly during the interval of the diode is non-conducting. DESIGN: Say for = 20msec (corresponding to a frequency of 50 Hz), then for RC >> , let C=0.1F, then R 200K. PROCEDURE : 1. Before making the connections check all components using multimeter. 2. Make the connections as shown in circuit diagram (fig. 5). 3. Using a signal generator apply a square wave input (Vi) of peak-to-peak amplitude of 10V (and frequency greater than 50Hz) to the circuit. (Sine wave can also be applied) 4. Observe the clamped output waveform on CRO which is as shown in Fig. 6. Note: 1. For clamping circuit with reference voltage Vref, the output waveform is observed as shown in Fig. 7. For without reference voltage, Keep Vref = 0V. 2. CRO in DUAL mode and DC mode. Also the grounds of both the channels can be made to have the same level so that the shift in DC level of the output can be observed. 3. For negative clampers reverse the directions of both diode and reference voltage.

Fig. 6 Input and Output waveform for positive clamper without reference voltage. Dept. of CSE, SJBIT Page 3

ELECTRONIC CIRCUITS LABORATARY

10CSL38

Fig. 7 Input and output waveform for positive clamper circuit with reference voltage = 2V

Dept. of CSE, SJBIT

Page 4

ELECTRONIC CIRCUITS LABORATARY

10CSL38

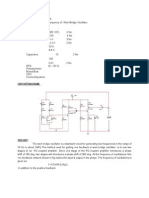

2a. CE AMPLIFIER

AIM: To determine the frequency response, input impedance, output impedance and bandwidth of a CE amplifier. COMPONENTS REQUIRED: Transistor SL-100, Resistors -16 K, 3.9 K, 820, 220 , Capacitors - 0.47 F, 100 F, DC regulated power supply, Signal generator, CRO PROCEDURE : 1. Before making the connections check all components using multimeter. 2. Make the connections as shown in circuit diagram. 3. Using a signal generator apply a sinusoidal input waveform of peak-to-peak amplitude 20mV ( = Vin) to the circuit and observe the output signal on the CRO. 4. Vary the frequency of input from 50Hz to 1MHz range and note down corresponding output voltage VO in the tabular column. Note: When the input frequency is being changed the input amplitude (i.e., around 20 mV) should remain constant. Adjust the amplitude of Vin (in mV) such that the output Vo does not get clipped (i.e., saturated) when the frequency is in the mid range say 1kHz. 5. After the frequency has been changed from 50 Hz to 1MHz and the readings are tabulated in a tabular column, calculate gain of the amplifier (in dB) using the formula, Gain in dB = 20 log 10 (Vo/Vin) 6. Plot the graph of gain versus frequency on a semilog sheet and hence determine the bandwidth as shown in Fig. 3. Bandwidth = B = f2-f1 To find input impedance, set the input DRBI to a minimum value and DRBO to a maximum value (say, 10k) as shown in figure 2. Now apply an input signal using signal generator, say a sine wave whose peak-to-peak amplitude is 50mV with a frequency of 10 KHz. Observe the output on CRO. Note this value of output with DRBI = 0 as Vx. Now increase the input DRBI value till the output voltage Vo = (1/2) Vx. The corresponding DRBI value gives input impedance. To find output impedance, set DRBO which is connected across the output to a maximum value as shown in figure 2, with the corresponding DRBI at the minimum position. Apply the input signal using signal generator, say a sine wave whose peak-topeak amplitude is 50mV with a frequency of 10 KHz. Observe the output on CRO. Note this value of output with DRBI = 0 as Vx. Now decrease the DRBO value till the output voltage Vo = (1/2) Vx. The corresponding DRBO value gives output impedance. Note: DRBI is connected between the signal generator and the input coupling capacitor. DRBO is connected across the output (across the CRO terminals). The ground symbol in the circuit diagram implies a common point. In some of the power supplies, there will be three terminals - +(plus), -(minus) and GND (ground). Never connect this GND terminal to the circuit.

Dept. of CSE, SJBIT

Page 5

ELECTRONIC CIRCUITS LABORATARY TABULAR COLUMN f in Hz 50 Hz --1 MHz V0 P-P volts

10CSL38

Vi = 50 mV (P-P) Power Gain = 20 log10 Av V AV = 0 in dB V

i

Values R 1 = 18k R2 = 3.9k RC = 820 RE = 220 R L = 10k CC1 = CC2 =0.47F CE=100F Fig. 1 : Transistor as a CE amplifier circuit diagram and actual connections (does not show RL)

Dept. of CSE, SJBIT

Page 6

ELECTRONIC CIRCUITS LABORATARY

10CSL38

Fig. 2: CE Amplifier with DRBs connected at both input and output WAVEFORMS:

FREQUENCY RESPONSE:

Fig. 3 Frequency response plotted on semilog graph (X-axis is log scale) Page 7

Dept. of CSE, SJBIT

ELECTRONIC CIRCUITS LABORATARY

10CSL38

1. BANDWIDTH = Hz 2. INPUT IMPEDANCE = 3. OUTPUT IMPEDANCE = Note: Maximum gain occurs in mid frequency region. This is also called mid band gain. Gain-bandwidth product = Midband gain x Bandwidth THEORY: The frequency response of an amplifier is the graph of its gain versus the frequency. Fig. 3 shows the frequency response of an ac amplifier. In the middle range of frequencies, the voltage gain is maximum. The amplifier is normally operated in this range of frequencies. At low frequencies, the voltage gain decreases because the coupling (CC in Fig.1) and bypass (CE) capacitors no longer act like short circuits; instead some of the ac signal voltage is attenuated. The result is a decrease of voltage gain as we approach zero hertz. At high frequencies, voltage gain decreases because the internal (parasitic) capacitances across the transistor junctions provide bypass paths for ac signal. So as frequency increases, the capacitive reactance becomes low enough to prevent normal transistor action. The result is a loss of voltage gain. Cutoff frequencies (f1 & f2 in Fig. 3) are the frequencies at which the voltage gain equals 0.707 of its maximum value. It is also referred to as the half power frequencies because the load power is half of its maximum value at these frequencies. DESIGN: Given: VCC = 10V , I C = 5mA & = 100 1 To find RE, let VRE = I E RE = VCC = 1V , and I E I C 10 VRE VRE 1 Hence RE = = = = 200 . Choose RE = 220. IE IC 5m To find RC, RC determines the Q-point. Choose RC such that VCE = VCC/2 = 5V Applying KVL to the CE loop (in Fig. 1), VCC I C RC VCE VRE = 0 . Substituting all the values we get RC = 800. Choose RC = 820(standard resistor value) I 5m To find R1: We have VB = VBE + VRE = 0.7 + 1 = 1.7V and I B = C = = 50 A 100 Assuming that the biasing network (R1 & R2) is designed such that 10IB flows through R1, we have VR1 = 10 I B R1 = VCC VB . Substituting the values of Vcc, VB & IB, R1 = 16.6k . Next to find R2, we have VR2 = 9IBR2 =VB. Hence R2 =

RESULT:

R1= 18k and choose R2 =3.9k To find the bypass capacitor CE: Let XCE = RE/10 at f = 100 Hz (remember CE & RE are in R 1 parallel). Hence X CE = = E . Substituting all the values, CE = 72.3 F. 2fC E 10 Choose CE =100 F and the coupling capacitors CC1 = CC2 = 0.47 F.

VB 1.7 = = 3.7 K . Choose 9 I B 9 50 A

Dept. of CSE, SJBIT

Page 8

ELECTRONIC CIRCUITS LABORATARY

10CSL38

3a. CHARACTERISTICS OF AN ENHANCEMENT MODE MOSFET

AIM : To determine the drain characteristics and transconductance characteristics of an enhancement mode MOSFET. COMPONENTS REQUIRED: MOSFET (IRF 740), Resistor (1k), Voltmeters (030V range and 0-10V range), Ammeter (0- 25mA range) and Regulated power supply (2 nos. variable power supply) CIRCUIT DIAGRAM:

Fig.1a.Depletion mode(negative gate voltage) & b.Enhancement mode (positive gate voltage) Sample Characteristics to be obtained

Fig. 2a. Drain Characteristics and b. Transconductance (or mutual/transfer) characteristics PROCEDURE : 1. Make the connections as shown in the corresponding circuit diagram. Special care to be taken in connecting the voltmeters and ammeters according to the polarity shown in circuit diagram figures. 2. Repeat the procedure for finding drain and transconductance characteristics for both modes, that is for both depletion and enhancement modes. 3. Tabulate the readings in separate tabular columns as shown below. 4. Plot the drain characteristics (ID versus VDS for different values of gate voltages VGS) of both modes (that is, depletion and enhancement) in one plot as shown below. (Take ID along the Y-axis and VDS along the X-axis in the plot) VDS 5. From this plot of drain characteristics find the drain resistance rd = , which is I D shown in Fig. 2a. Page 9

Dept. of CSE, SJBIT

ELECTRONIC CIRCUITS LABORATARY

10CSL38

6. Similarly plot the transconductance characteristics of both modes in one plot, with ID along the Y-axis and VGS along the X-axis in the graph for one value of VDS, say VDS = 5V. I D 7. From this plot find the mutual conductance or transconductance g m = (Fig. 2b). VGS 8. Lastly find the amplification factor, =r d g m Procedure for finding the Transconcuctance Characteristics in both modes: 1. Switch on the power supplies, with both V2 and V1 at zero voltage. 2. Initially set V1 =VGS = 0V. Now set V2 = VDS = 5V (say). Vary the power supply V1 i.e., VGS and note down the corresponding current ID (in mA) (Simultaneously note down the VGS value from the voltmeter connected at the gate terminal). 3. Repeat the above procedure for a different value of VDS, say 10V. Note: In the above procedure VDS (i.e., the power supply V2) is kept constant and the power supply V1 (=VGS) is varied. Drain Characteristics : 1. Initially set V1 = VGS =3.5V (say), slowly vary V2 and note down the corresponding current ID. Simultaneously note down in the tabular column the voltmeter reading VGS. 2. Repeat the above procedure for different values of VGS and note down the current ID for corresponding V1 = VDS. 3. Plot the graph of ID versus VDS for different values of gate voltages. Note: In the above procedure VDS (i.e., the power supply V2) is varied and the power supply V1 (=VGS) is kept constant. READINGS TABULATED IN TABULAR COLUMN Depletion mode (Note: In this mode VGS values are all negative and the minus sign to be appended to the readings, though the voltmeter at the gate terminal shows the deflection in the same way for both modes) Drain Characteristics Transconductance Characteristics

Enhancement mode readings Drain Characteristics

Transconductance Characteristics

Dept. of CSE, SJBIT

Page 10

ELECTRONIC CIRCUITS LABORATARY

10CSL38

4 a. SCHMITT TRIGGER

AIM : To design and implement a Schmitt trigger circuit using op-amp for the given UTP and LTP values. COMPONENTS REQUIRED : IC A 741, Resistor of 10K, 90K, DC regulated power supply, Signal generator, CRO DESIGN : From theory of Schmitt trigger circuit using op-amp, we have the trip points, RV RV UTP = 1 ref + 2 sat where Vsat is the positive saturation of the opamp = 90% of Vcc R1 + R2 R1 + R2

& LTP = R1Vref R1 + R2 R2Vsat R1 + R2 - - - - - -(1)

Hence given the LTP & UTP values to find the R1 , R2 & Vref values, the following design is used. UTP + LTP = UTP LTP = 2 R1Vref R1 + R2

2 R1Vsat - - - - - -(2) R1 + R2

Let Vsat = 10V, UTP = 4V & LTP = 2V, then equation (2) yields R1 = 9 R2 Let R2 = 10 K, then R1 = 90 K From equation (1) we have Vref = (UTP + LTP )( R1 + R2 ) = 3.33V 2 R1

PROCEDURE : 1. Before doing the connections, check all the components using multimeter. 2. Make the connection as shown in circuit diagram. 3. Using a signal generator apply the sinusoidal input waveform of peak-to-peak amplitude of 10V, frequency 1kHz. 4. Keep the CRO in dual mode; apply input (Vin) signal to the channel 1 and observe the output (Vo) on channel 2 which is as shown in the waveform below. Note the amplitude levels from the waveforms. 5. Now keep CRO in X-Y mode and observe the hysteresis curve.

Circuit Diagram and actual connections of Schmitt Trigger Circuit Page 11

Dept. of CSE, SJBIT

ELECTRONIC CIRCUITS LABORATARY

10CSL38

Waveforms:

CRO in DUAL mode

CRO in X-Y mode showing the Hysteresis curve THEORY: Schmitt Trigger converts an irregular shaped waveform to a square wave or pulse. Here, the input voltage triggers the output voltage every time it exceeds certain voltage levels called the upper threshold voltage VUTP and lower threshold voltage VLTP. The input voltage is applied to the inverting input. Because the feedback voltage is aiding the input voltage, the feedback is positive. A comparator using positive feedback is usually called a Schmitt Trigger. Schmitt Trigger is used as a squaring circuit, in digital circuitry, amplitude comparator, etc.

Dept. of CSE, SJBIT

Page 12

ELECTRONIC CIRCUITS LABORATARY

10CSL38

AIM : To design and implement a rectangular waveform generator (op-amp relaxation oscillator) for a given frequency. COMPONENTS REQUIRED: Op-amp A 741, Resistor of 1K, 10K, 20 k Potentiometer, Capacitor of 0.1 F, Regulated DC power supply, CRO DESIGN :

5a. OP-AMP AS A RELAXATION OSCILLATOR

1+ The period of the output rectangular wave is given as T = 2 RC ln 1 R1 Where, = is the feedback fraction R1 + R2 If R1 = R2, then from equation (1) we have T = 2RC ln(3)

-------(1)

Another example, if R2=1.16 R1, then T = 2RC ----------(2) 1 1 Example: Design for a frequency of 1kHz (implies T = = 3 = 10 3 = 1ms ) f 10 Use R2=1.16 R1, for equation (2) to be applied. Let R1 = 10k, then R2 = 11.6k (use 20k potentiometer as shown in circuit figure) Choose next a value of C and then calculate value of R from equation (2). T 10 3 Let C=0.1F (i.e., 10-7), then R = = = 5 K 2C 2 10 7 R1 The voltage across the capacitor has a peak voltage of Vc = Vsat R1 + R2 PROCEDURE : 1. Before making the connections check all the components using multimeter. 2. Make the connections as shown in figure and switch on the power supply. 3. Observe the voltage waveform across the capacitor on CRO. 4. Also observe the output waveform on CRO. Measure its amplitude and frequency.

Circuit Diagram & actual connections

Values C=0.1F R1 = 10k, R2 = 11.6 k,R = 4.7k/5.1k Page 13

Dept. of CSE, SJBIT

ELECTRONIC CIRCUITS LABORATARY

10CSL38

WAVEFORMS

RESULT: The frequency of the oscillations = ___ Hz. THEORY: Op-Amp Relaxation Oscillator is a simple Square wave generator which is also called as a Free running oscillator or Astable multivibrator or Relaxation oscillator. In this figure the op-amp operates in the saturation region. Here, a fraction (R2/(R1+R2)) of output is fed back to the noninverting input terminal. Thus reference voltage is (R2/(R1+R2)) Vo. And may take values as +(R2/(R1+R2)) Vsat or - (R2/(R1+R2)) Vsat. The output is also fed back to the inverting input terminal after integrating by means of a low-pass RC combination. Thus whenever the voltage at inverting input terminal just exceeds reference voltage, switching takes place resulting in a square wave output.

Dept. of CSE, SJBIT

Page 14

ELECTRONIC CIRCUITS LABORATARY

10CSL38

6. ASTABLE MULTIVIBRATOR USING 555 TIMER

AIM : To design and implement an astable multivibrator using 555 Timer for a given frequency and duty cycle. COMPONENTS REQUIRED: 555 Timer IC, Resistors of 3.3K, 6.8K, Capacitors of 0.1 F, 0.01 F, Regulated power supply, CRO DESIGN : Given frequency (f) = 1KHz and duty cycle = 60% (=0.6) The time period T =1/f = 1ms = tH + tL Where tH is the time the output is high and tL is the time the output is low. From the theory of astable multivibrator using 555 Timer(refer Malvino), we have tH = 0.693 RB C ------(1) tL = 0.693 (RA + RB)C ------(2) T = tH + tL = 0.693 (RA +2 RB) C Duty cycle = tH / T = 0.6. Hence tH = 0.6T = 0.6ms and tL = T tH = 0.4ms. Let C=0.1F and substituting in the above equations, RB = 5.8K (from equation 1) and RA = 2.9K (from equation 2 & RB values). The Vcc determines the upper and lower threshold voltages (observed from the capacitor 2 1 voltage waveform) as VUT = VCC & VLT = VCC . 3 3 Note: The duty cycle determined by RA & RB can vary only between 50 & 100%. If RA is much smaller than RB, the duty cycle approaches 50%. Example 2: frequency = 1kHz and duty cycle =75%, RA = 7.2k & RB =3.6k, choose RA = 6.8k and RB = 3.3k.

Circuit Diagram and actual connections PROCEDURE : 1. Before making the connections, check the components using multimeter. 2. Make the connections as shown in figure and switch on the power supply. Dept. of CSE, SJBIT

Page 15

ELECTRONIC CIRCUITS LABORATARY

10CSL38

3. Observe the capacitor voltage waveform at 6th pin of 555 timer on CRO. 4. Observe the output waveform at 3rd pin of 555 timer on CRO (shown below). 5. Note down the amplitude levels, time period and hence calculate duty cycle. RESULT: The frequency of the oscillations = ___ Hz.

WAVEFORMS

THEORY: Multivibrator is a form of oscillator, which has a non-sinusoidal output. The output waveform is rectangular. The multivibrators are classified as: Astable or free running multivibrator: It alternates automatically between two states (low and high for a rectangular output) and remains in each state for a time dependent upon the circuit constants. It is just an oscillator as it requires no external pulse for its operation. Monostable or one shot multivibrator: It has one stable state and one quasi stable. The application of an input pulse triggers the circuit time constants. After a period of time determined by the time constant, the circuit returns to its initial stable state. The process is repeated upon the application of each trigger pulse. Bistable Multivibrators: It has both stable states. It requires the application of an external triggering pulse to change the output from one state to other. After the output has changed its state, it remains in that state until the application of next trigger pulse. Flip flop is an example.

Dept. of CSE, SJBIT

Page 16

ELECTRONIC CIRCUITS LABORATARY

10CSL38

Experiments Using PSPICE SOFTWARE

SERIES CLIPPER

D1

D1N4002

V

R1 10k V3

V

VO F F = 0 VAMPL = 5 FREQ = 1k

V1

Type of analysis: TIME DOMAIN (TRANSIENT)

Run to time: 5msec step size:0.01msec

Dept. of CSE, SJBIT

Page 17

ELECTRONIC CIRCUITS LABORATARY SHUNT CLIPPING

R4 10k

V

10CSL38

D2

V

V4 VO F F = 0 VAMPL = 5 FREQ = 1k

D1N4002

1.5

V5

Type of analysis: TIME DOMAIN (TRANSIENT)

Run to time: 5msec step size:0.01msec

Dept. of CSE, SJBIT

Page 18

ELECTRONIC CIRCUITS LABORATARY DOUBLE ENDED CLIPPER

R5 10k D5

V V

10CSL38

D6 D1N4002

D1N4002

VO F F = 0 VAMPL = 5V F RE Q = 1 K HZ

V2 V1 2 V1 1 3

Type of analysis: TIME DOMAIN (TRANSIENT)

Run to time: 5msec step size:0.01msec

Dept. of CSE, SJBIT

Page 19

ELECTRONIC CIRCUITS LABORATARY POSITIVE CLAMPER WITHOUT REFERENCE VOLTAGE

C1 0.1uF V1 = 2.5v V2 = -2.5v TD = 0.01ms TR = 0.01us TF = 0.01us PW = 0.5ms PER = 1ms

V

10CSL38

V1

D7 D1N4002

R6 V 200K

Type of analysis: TIME DOMAIN (TRANSIENT)

Run to time: 5msec step size:0.01msec

Dept. of CSE, SJBIT

Page 20

ELECTRONIC CIRCUITS LABORATARY

WITH REFERENCE VOLTAGE

C2 0. 1uF D 1N 4002 D8

V V

10CSL38

V1 = 2. 5v V2 = -2. 5v TD = 0. 01m s TR = 0. 01us TF = 0. 01us PW = 0. 5m PER = 1m s

V2

V17 1v

R7 200K

POSITIVE CLAMPER WITH REFERENCE

Type of analysis: TIME DOMAIN (TRANSIENT)

Run to time: 5msec step size:0.01msec

V4

CE AMPLIFIER

10v

cval = 1

PARAMETERS:

R5 C5 {cval} 50mv 0Vdc

V1

V

R4 16k

Q2

820 Q2N2222

C6 0.47uF R2

V

R6 3.9K

R7 220

C7 100uF

1k

Dept. of CSE, SJBIT

Page 21

ELECTRONIC CIRCUITS LABORATARY

10CSL38

Type of analysis: Ac Sweep

Sweep type:logrithemic

Start frequency:10hz End frequency:10meg points per decade:40 ---------------------------------------------------------------------------------------------------------------CMOS INVERTER

MbreakP M1 V1

0

5v

V1 = 5v V2 = 0v TD = 0.01ns TR = 1ns TF = 1ns PW = 20us PER = 40us

V2

V V

M2 MbreakN R2 100k

Dept. of CSE, SJBIT

Page 22

ELECTRONIC CIRCUITS LABORATARY

10CSL38

Type of analysis: TIME DOMAIN (TRANSIENT)

Run to time: 100usec step size:0.1usec ---------------------------------------------------------------------------------------------------------------------------------------

ASTABLE MULTIVIBRATOR USING 555 TIMER

0

V1 10 8 R1 2.9k 2 4 5 6 7 V CC TRIGGER RESET OUTPUT CONTROL THRESHOLD G ND DISCHARGE 1 C2 0.01uf 555D 3 R3 V 10meg X1

R2 5.8k C1 V

0.1u

Dept. of CSE, SJBIT

Page 23

ELECTRONIC CIRCUITS LABORATARY

10CSL38

Type of analysis: TIME DOMAIN (TRANSIENT)

Run to time: 5msec step size:0.01msec ---------------------------------------------------------------------------------------------------------------------------------------

0

V4 3.3v

10k

R2

R1 90k V1 7 10v V+ O S2 O UT 5 6 1

V

SCHMITT TRIGGER

U1 +

VOFF = 0v VAMPL = 10v FREQ = 50hz

V3

V

2 uA741

V- OS1 V2

10v

Dept. of CSE, SJBIT

Page 24

ELECTRONIC CIRCUITS LABORATARY

10CSL38

Type of analysis: TIME DOMAIN (TRANSIENT)

Run to time: 40msec step size:0.1msec

Dept. of CSE, SJBIT

Page 25

ELECTRONIC CIRCUITS LABORATARY

0

R3 10k R2 10k

10CSL38

RELAXATION OSCILLATOR

0

V1 7 V+ 12v OS2 5 6 1

V

U1 +

OUT 2

V uA741

V-

OS1 V2 12v

C1 .1 u f

0 0

R1 1k

TYPE OF ANALYSIS : TIME DOMAIN RUN TO TIME : 4ms MAXIMUM STEP SIZE : 0.01ms

Dept. of CSE, SJBIT

Page 26

ELECTRONIC CIRCUITS LABORATARY REGULATED POWER SUPPLY

R1 D4 D 1N 4002 V1

V F R EQ = 60H z

10CSL38

D2 D 1N 4002

220

C1 47uf

D1 D 1N 750

R2 1K

VAMPL = 10V VOF F = 0V

D5 D 1N 4002

D3 D 1N 4002

TYPE OF ANALYSIS : TIME DOMAIN RUN TO TIME : 100ms MAXIMUM STEP SIZE : 0.1ms

Dept. of CSE, SJBIT

Page 27

Anda mungkin juga menyukai

- Ele Lab ReportDokumen42 halamanEle Lab ReportDik Man RyBelum ada peringkat

- Analog Electronics Lab ManualDokumen68 halamanAnalog Electronics Lab ManualZealWolfBelum ada peringkat

- Ec FinalDokumen46 halamanEc FinalManjunath YadavBelum ada peringkat

- EC Lab ManualDokumen29 halamanEC Lab ManualAshwath NadahalliBelum ada peringkat

- Mit Aec Labmanula 10esl37Dokumen45 halamanMit Aec Labmanula 10esl37anon_70724250Belum ada peringkat

- RC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentDokumen8 halamanRC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentMani BharathiBelum ada peringkat

- Common Emitter Amplifier: S.No Name of The Component/ Equipment Specifications QtyDokumen0 halamanCommon Emitter Amplifier: S.No Name of The Component/ Equipment Specifications Qtyagama1188Belum ada peringkat

- Physics Investigatory ProjectsDokumen36 halamanPhysics Investigatory ProjectsTushar Kush100% (4)

- AEC LabManualDokumen30 halamanAEC LabManualPrateek PaliwalBelum ada peringkat

- Design A RC Coupled CE Transistor AmplifierDokumen7 halamanDesign A RC Coupled CE Transistor AmplifierSudeep Nayak100% (1)

- Lab10 2011Dokumen5 halamanLab10 2011Venkat RamananBelum ada peringkat

- Ec Manual NewDokumen59 halamanEc Manual NewWasz MujthabaBelum ada peringkat

- AEC Lab ManualDokumen70 halamanAEC Lab ManualRohan BoseBelum ada peringkat

- 01 - Experiment Diode j09Dokumen19 halaman01 - Experiment Diode j09Ahmed Sobhy KhattabBelum ada peringkat

- EC &LD-Lab ManualDokumen50 halamanEC &LD-Lab Manualdevirpasad100% (1)

- Operational Amplifier LAbDokumen17 halamanOperational Amplifier LAbAhmad DboukBelum ada peringkat

- AEC NotesDokumen271 halamanAEC Notes1DS19EC726- Pankaj Ashok M.Belum ada peringkat

- EDC Lab ManualDokumen46 halamanEDC Lab ManualMOUNIRAGESHBelum ada peringkat

- EXPERIMENT #2 Frequency Response of Common Emitter AmplierDokumen6 halamanEXPERIMENT #2 Frequency Response of Common Emitter AmplierGhabriel Javier SembranoBelum ada peringkat

- Analog Electronics Lab ManualDokumen49 halamanAnalog Electronics Lab ManualReddyvari VenugopalBelum ada peringkat

- ADE Lab Manual - Analog Part PDFDokumen21 halamanADE Lab Manual - Analog Part PDFJk RinkuBelum ada peringkat

- TransistorDokumen8 halamanTransistorwei.cheng.auBelum ada peringkat

- ST - Joseph College of Engineering: SriperumbudurDokumen45 halamanST - Joseph College of Engineering: SriperumbudurSuryaBelum ada peringkat

- Design and Analysis of Multistage Amplifier Configurations: ObjectiveDokumen12 halamanDesign and Analysis of Multistage Amplifier Configurations: ObjectivePreet PatelBelum ada peringkat

- ECII & Sim LabDokumen49 halamanECII & Sim LabSivan LoveBelum ada peringkat

- RC Coupled Transistor AmplifierDokumen7 halamanRC Coupled Transistor AmplifierIshratBelum ada peringkat

- Design and Analysis of Multistage Amplifier Configurations: ObjectiveDokumen19 halamanDesign and Analysis of Multistage Amplifier Configurations: ObjectivePreet PatelBelum ada peringkat

- Adc Lab Manual PDFDokumen74 halamanAdc Lab Manual PDFJega Deesan75% (4)

- Inverting and Non-Inverting Amplifiers: Pre-Lab QuestionsDokumen13 halamanInverting and Non-Inverting Amplifiers: Pre-Lab QuestionsBereket TsegayeBelum ada peringkat

- Lab ManualDokumen38 halamanLab ManualsivaBelum ada peringkat

- Experiment 3 Time and Frequency Response of RC and RL CircuitsDokumen3 halamanExperiment 3 Time and Frequency Response of RC and RL CircuitsShashank Singh100% (1)

- Experiment #2 Diode Clipping and Clamping Circuits: Limiter (ClippeDokumen7 halamanExperiment #2 Diode Clipping and Clamping Circuits: Limiter (ClippeSumeet KumarBelum ada peringkat

- Objectives:: Electronics I Laboratory - EXPERIMENT 10 Common Emitter AmplifierDokumen6 halamanObjectives:: Electronics I Laboratory - EXPERIMENT 10 Common Emitter AmplifierRabindraMaharanaBelum ada peringkat

- Experiment 5 Integrator, Differentiator and Non-Linear Properties of OpampsDokumen7 halamanExperiment 5 Integrator, Differentiator and Non-Linear Properties of OpampsEnes AyduranBelum ada peringkat

- Assignment 4Dokumen7 halamanAssignment 4Niraj Prasad YadavBelum ada peringkat

- ADC Lab ManualDokumen46 halamanADC Lab ManualDinesh Kumar A RBelum ada peringkat

- Experiment 3 Time and Frequency Response of RC and RL CircuitsDokumen3 halamanExperiment 3 Time and Frequency Response of RC and RL CircuitsSai SaurabBelum ada peringkat

- Expt 6Dokumen3 halamanExpt 6sabitavabiBelum ada peringkat

- Ec8351 Electronic Circuits 1 Unit 2 Solved WMRDokumen11 halamanEc8351 Electronic Circuits 1 Unit 2 Solved WMRSaravanan MurugaiyanBelum ada peringkat

- Experiment No 1: Wiring of RC Coupled Single Stage AmplifierDokumen7 halamanExperiment No 1: Wiring of RC Coupled Single Stage AmplifierShweta GadgayBelum ada peringkat

- 20IM10045 - Sahil Agrawal - Exp 4Dokumen13 halaman20IM10045 - Sahil Agrawal - Exp 4Sahil AgrawalBelum ada peringkat

- The Operation Amplifier:: Level TranslatorDokumen8 halamanThe Operation Amplifier:: Level TranslatorPrafull BBelum ada peringkat

- EC1 Lab Exp3 PDFDokumen2 halamanEC1 Lab Exp3 PDFRitu RoyBelum ada peringkat

- EC1256-Lab ManualDokumen67 halamanEC1256-Lab Manualjeyaganesh86% (7)

- CMOS Comparator Design: TSMC 0.25 Um TechnologyDokumen15 halamanCMOS Comparator Design: TSMC 0.25 Um TechnologySharath_Patil_7623Belum ada peringkat

- Wein Bridge OscillatorDokumen6 halamanWein Bridge Oscillatorinspectornaresh100% (1)

- Sharmi ECE a-D-Circuits Lab ManualDokumen74 halamanSharmi ECE a-D-Circuits Lab ManualSharmila83Belum ada peringkat

- Full Wave Bridge Peak RectifierDokumen4 halamanFull Wave Bridge Peak RectifierMuhammad TehreemBelum ada peringkat

- Lab#7: Study of Common Emitter Transistor Amplifier CircuitDokumen6 halamanLab#7: Study of Common Emitter Transistor Amplifier CircuitLeandro ZamaroBelum ada peringkat

- Analog Communications Lab ManualDokumen61 halamanAnalog Communications Lab ManualSriLakshmi RaheemBelum ada peringkat

- 12-RC Phase Shift OscillatorDokumen5 halaman12-RC Phase Shift OscillatorBanty BabliBelum ada peringkat

- 12-RC Phase Shift OscillatorDokumen5 halaman12-RC Phase Shift OscillatorA054 Shubham fundayBelum ada peringkat

- Basic Electronics Lab (Experiment 2 Report) : Submitted By: Group: G7 Ashutosh Garg (2018MEB1213) Ashwin Goyal (2018MEB1214)Dokumen8 halamanBasic Electronics Lab (Experiment 2 Report) : Submitted By: Group: G7 Ashutosh Garg (2018MEB1213) Ashwin Goyal (2018MEB1214)Ashutosh GargBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- 110 Waveform Generator Projects for the Home ConstructorDari Everand110 Waveform Generator Projects for the Home ConstructorPenilaian: 4 dari 5 bintang4/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsDari EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsBelum ada peringkat

- Audio IC Circuits Manual: Newnes Circuits Manual SeriesDari EverandAudio IC Circuits Manual: Newnes Circuits Manual SeriesPenilaian: 5 dari 5 bintang5/5 (1)

- DescribingDokumen4 halamanDescribingIhsanNurulHabibBelum ada peringkat

- ES9038Q2M Datasheet v1.4Dokumen65 halamanES9038Q2M Datasheet v1.4Thắng NguyễnBelum ada peringkat

- EA ProjectsDokumen35 halamanEA ProjectsBIBHAS MANDALBelum ada peringkat

- 10 Simple Steps To Learn ToDokumen4 halaman10 Simple Steps To Learn ToYoussef EnnouriBelum ada peringkat

- PG 108 - Fig 3 - 12V Battery Absorb - Component Layout - Sep 15Dokumen1 halamanPG 108 - Fig 3 - 12V Battery Absorb - Component Layout - Sep 15Ryn YahuFBelum ada peringkat

- TCD 001 PDFDokumen1 halamanTCD 001 PDFQuang Pham DuyBelum ada peringkat

- Full Text 02Dokumen45 halamanFull Text 02xzcBelum ada peringkat

- Panasonic sc-ht355 PDFDokumen32 halamanPanasonic sc-ht355 PDFErin KapsBelum ada peringkat

- TV Grundig Chassis LM Com Suplemento1+Dokumen78 halamanTV Grundig Chassis LM Com Suplemento1+videosonBelum ada peringkat

- Sams Practical Transistor Theory 1964Dokumen132 halamanSams Practical Transistor Theory 1964BillBelum ada peringkat

- Urc 6210Dokumen112 halamanUrc 6210Antonio GonzalezBelum ada peringkat

- MOTOROLA Walkie Talkie Consumer Radio TLKR T80Dokumen2 halamanMOTOROLA Walkie Talkie Consumer Radio TLKR T80Sbnjkt aBelum ada peringkat

- ASSESSMENT G8 TLE q1Dokumen3 halamanASSESSMENT G8 TLE q1Maria Chelo AgosBelum ada peringkat

- National University of Science and Technology: Digital System Design (EE-421) Assignment #1Dokumen23 halamanNational University of Science and Technology: Digital System Design (EE-421) Assignment #1Tariq UmarBelum ada peringkat

- Syllabus (ELE 241)Dokumen3 halamanSyllabus (ELE 241)PhoyagerBelum ada peringkat

- Digital Modulation Techniques / MultiplexingDokumen3 halamanDigital Modulation Techniques / MultiplexingYzza Veah Esquivel100% (2)

- MRF0415 deDokumen184 halamanMRF0415 dePetros TsenesBelum ada peringkat

- Lecture 1-Introduction To CAD-VHDL-Ch2 - v3Dokumen20 halamanLecture 1-Introduction To CAD-VHDL-Ch2 - v3Abbas MahdiBelum ada peringkat

- Tutorial 1Dokumen3 halamanTutorial 1dfsdsdfsdfsdfsdfsdBelum ada peringkat

- Bird Antenna Cable Monitor ACM ACMI SeriesDokumen4 halamanBird Antenna Cable Monitor ACM ACMI SeriesGuilherme Alvarenga Dos SantosBelum ada peringkat

- 1T00918Dokumen2 halaman1T00918Clovis MachadoBelum ada peringkat

- Unit 7 Radar EquationDokumen94 halamanUnit 7 Radar EquationVinamra KumarBelum ada peringkat

- PVM1Dokumen4 halamanPVM1silverfurBelum ada peringkat

- IESL General Qualifying Examination SyllabusDokumen38 halamanIESL General Qualifying Examination SyllabusXiao ShadowlordBelum ada peringkat

- Hfe Yamaha Dsp-A595a Service PDFDokumen58 halamanHfe Yamaha Dsp-A595a Service PDFVictor NickBelum ada peringkat

- Design and Implementation of FPGA-Based Systems - ADokumen23 halamanDesign and Implementation of FPGA-Based Systems - Asavithri123anuragBelum ada peringkat

- EMT 359/3 Analog Electronic II: Op-Amp Applications & Frequency ResponseDokumen59 halamanEMT 359/3 Analog Electronic II: Op-Amp Applications & Frequency ResponsedharanikaBelum ada peringkat

- Yamaha mg10-2 (ET)Dokumen48 halamanYamaha mg10-2 (ET)facafBelum ada peringkat

- HDR ExplainedDokumen16 halamanHDR ExplaineddulishaBelum ada peringkat