SMD 357

Diunggah oleh

Marcoantonio AntonioDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

SMD 357

Diunggah oleh

Marcoantonio AntonioHak Cipta:

Format Tersedia

April 1997

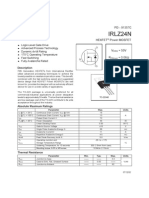

NDS351AN N-Channel Logic Level Enhancement Mode Field Effect Transistor

General Description

These N-Channel logic level enhancement mode power field effect transistors are produced using Fairchild's proprietary, high cell density, DMOS technology. This very high density process is especially tailored to minimize on-state resistance. These devices are particularly suited for low voltage applications in notebook computers, portable phones, PCMCIA cards, and other battery powered circuits where fast switching, and low in-line power loss are needed in a very small outline surface mount package.

Features

1.2A, 30 V. RDS(ON) = 0.25 @ VGS = 4.5 V RDS(ON) = 0.16 @ VGS = 10 V. Industry standard outline SOT-23 surface mount package using proprietary SuperSOTTM-3 design for superior thermal and electrical capabilities. High density cell design for extremely low RDS(ON). Exceptional on-resistance and maximum DC current capability. Compact industry standard SOT-23 surface mount

_________________________________________________________________________________

Absolute Maximum Ratings

Symbol VDSS VGSS ID PD TJ,TSTG Parameter Drain-Source Voltage

T A = 25C unless otherwise noted

NDS351AN 30 20

(Note 1a)

Units V V A

Gate-Source Voltage - Continuous Maximum Drain Current - Continuous - Pulsed Maximum Power Dissipation

(Note 1a) (Note 1b)

1.2 10 0.5 0.46 -55 to 150

Operating and Storage Temperature Range

THERMAL CHARACTERISTICS RJA RJC Thermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-Case

(Note 1a) (Note 1)

250 75

C/W C/W

1997 Fairchild Semiconductor Corporation

NDS351AN Rev. C

Electrical Characteristics (TA = 25C unless otherwise noted)

Symbol Parameter Conditions Min Typ Max Units OFF CHARACTERISTICS BVDSS IDSS IGSSF IGSSR VGS(th) RDS(ON) Drain-Source Breakdown Voltage Zero Gate Voltage Drain Current VGS = 0 V, ID = 250 A VDS = 24 V, VGS = 0 V TJ =125C Gate - Body Leakage, Forward Gate - Body Leakage, Reverse VGS = 20 VDS = 0 V VGS = -20 V, VDS = 0 V VDS = VGS, ID = 250 A TJ =125C Static Drain-Source On-Resistance VGS = 4.5 V, ID = 1.2 A TJ =125C VGS = 10 V, ID = 1.4 A ID(ON) gFS Ciss Coss Crss td(on) tr td(off) tf Qg Q gs Q gd On-State Drain Current Forward Transconductance VGS = 4.5 V, VDS = 5 V VDS = 5 V, ID= 1.2 A, VDS = 10 V, VGS = 0 V, f = 1.0 MHz 3.5 1.8 0.8 0.5 1.7 1.3 0.19 0.28 0.125 30 1 10 100 -100 V A A nA nA

ON CHARACTERISTICS (Note 2) Gate Threshold Voltage 2 1.5 0.25 0.37 0.16 A S V

DYNAMIC CHARACTERISTICS Input Capacitance Output Capacitance Reverse Transfer Capacitance

(Note 2)

125 100 90

pF pF pF

SWITCHING CHARACTERISTICS Turn - On Delay Time Turn - On Rise Time Turn - Off Delay Time Turn - Off Fall Time Total Gate Charge Gate-Source Charge Gate-Drain Charge

VDD = 10 V, ID = 1 A, VGS = 10 V, RGEN = 50

6 15 14 18

15 30 30 40 2.7

ns ns ns ns nC nC nC

VDS = 10 V, ID = 1.2 A, VGS = 4.5 V

1.9 0.5 0.9

NDS351AN Rev. C

Electrical Characteristics (TA = 25C unless otherwise noted)

Symbol Parameter Conditions Min Typ Max Units DRAIN-SOURCE DIODE CHARACTERISTICS AND MAXIMUM RATINGS IS ISM VSD

Notes: 1. RJA is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of guaranteed by design while RCA is determined by the user's board design. the drain pins. RJC is

Maximum Continuous Drain-Source Diode Forward Current Maximum Pulsed Drain-Source Diode Forward Current Drain-Source Diode Forward Voltage VGS = 0 V, IS = 1.2 A (Note 2) 0.8

0.42 5 1.2

A A V

P D (t ) =

R JA(t )

T J TA

TJ

TA

R JC+RCA(t )

= I 2 (t ) RDS(ON ) D

TJ

Typical RJA using the board layouts shown below on 4.5"x5" FR-4 PCB in a still air environment: a. 250oC/W when mounted on a 0.02 in2 pad of 2oz copper. b. 270oC/W when mounted on a 0.001 in2 pad of 2oz copper.

1a

1b

Scale 1 : 1 on letter size paper 2. Pulse Test: Pulse Width < 300s, Duty Cycle < 2.0%.

NDS351AN Rev. C

Typical Electrical Characteristics

5 1.8

V GS =10V

I D , DRAIN-SOURCE CURRENT (A)

4

6.0

R DS(on ) , NORMALIZED DRAIN-SOURCE ON-RESISTANCE

5.0 4.5 4.0

1.6 1.4 1.2 1 0.8 0.6 0.4

VGS = 3.5V

3.5

2

4.0 4.5 5.0 6.0 7.0 10

3.0

1

0 0 V

DS

, DRAIN-SOURCE VOLTAGE (V)

2 I D , DRAIN CURRENT (A)

Figure 1. On-Region Characteristics.

Figure 2. On-Resistance Variation with Drain Current and Gate Voltage.

1.8

1.8 DRAIN-SOURCE ON-RESISTANCE I D = 1.2A 1.6 1.4 1.2 1 0.8 0.6 0.4

DRAIN-SOURCE ON-RESISTANCE

1.6

VGS = 4.5 V

R DS(ON), NORMALIZED

V GS = 4.5V

TJ = 125C

1.4

RDS(on) , NORMALIZED

1.2

25C -55C

0.8

0.6 -50

-25

0 25 50 75 100 T , JUNCTION TEMPERATURE (C) J

125

150

2 I D, DRAIN CURRENT (A)

Figure 3. On-Resistance Variation with Temperature.

Figure 4. On-Resistance Variation with Drain Current and Temperature.

V DS = 5.0V

4

25C

Vth , NORMALIZED GATE-SOURCE THRESHOLD VOLTAGE

T = -55C J

1.2 1.1 1 0.9 0.8 0.7 0.6 -50

I D , DRAIN CURRENT (A)

125C

3

V DS= V GS I D = 250A

0 0.5

1.5 V

GS

2.5

3.5

4.5

-25

, GATE TO SOURCE VOLTAGE (V)

0 25 50 75 100 TJ , JUNCTION TEMPERATURE (C)

125

150

Figure 5. Transfer Characteristics.

Figure 6. Gate Threshold Variation with Temperature.

NDS351AN Rev. C

Typical Electrical Characteristics (continued)

1.12

DRAIN-SOURCE BREAKDOWN VOLTAGE

I , REVERSE DRAIN CURRENT (A)

I D = 250A

1.08

V GS = 0V

1

BV DSS , NORMALIZED

TJ = 125C

0.1

25C -55C

1.04

0.01

0.96

0.001

0.92 -50

-25

0 T

J

25

50

75

100

125

150

0.0001 0 0.2 0.4 0.6 0.8 1 V SD , BODY DIODE FORWARD VOLTAGE (V) 1.2

, JUNCTION TEMPERATURE (C)

Figure 7. Breakdown Voltage Variation with Temperature.

Figure 8. Body Diode Forward Voltage Variation with Source Current and Temperature.

400 , GATE-SOURCE VOLTAGE (V) 300 CAPACITANCE (pF)

10

I D = 1.2A

8

VDS = 5V

10V 15V

200 150

C iss

100 80

C oss f = 1 MHz V GS = 0V C rss

50 0.1

V 0.2 V 0.5

DS

GS

10

20

30

, DRAIN TO SOURCE VOLTAGE (V)

2 Q g , GATE CHARGE (nC)

Figure 9. Capacitance Characteristics.

Figure 10. Gate Charge Characteristics.

VDD

t d(on)

t on

t off tr

90%

t d(off)

90%

tf

V IN

D

RL V OUT

VOUT

10%

VGS

R GEN

10%

INVERTED

DUT 90% S

V IN

10%

50%

50%

PULSE WIDTH

Figure 11. Switching Test Circuit.

Figure 12. Switching Waveforms.

NDS351AN Rev. C

Typical Electrical Characteristics (continued)

, TRANSCONDUCTANCE (SIEMENS) 5 20

VDS = 5.0V

I D , DRAIN CURRENT (A) 4

10

1m s

N) S(O RD IT LIM

T J = -55C 25C

5 3 1 0.3 0.1 0.03 0.01 0.1

10m 100 1s ms

125C

V GS = 4.5V SINGLE PULSE R JA =See Note1b T = 25C A

0.2 0.5 V

DS

10s DC

FS

2 3 I , DRAIN CURRENT (A)

D

10

20 30

50

, DRAI N-SOURCE VOLTAGE (V)

Figure 13. Transconductance Variation with Drain Current and Temperature.

Figure 14. Maximum Safe Operating Area.

STEADY-STATE POWER DISSIPATION (W)

1

I , STEADY-STATE DRAIN CURRENT (A)

1.6

0.8

1.4

0.6

1b

1a

1.2

1a

0.4

1b

4.5"x5" FR-4 Board TA = 2 5 C Still Air VG S = 4 . 5 V

o

0.2

4.5"x5" FR-4 Board TA = 25 oC Still Air

0.8 0 0.1 0.2 0.3 2oz COPPER MOUNTING PAD AREA (in 2 ) 0.4

0.1 0.2 0.3 2oz COPPER MOUNTING PAD AREA (in 2 )

0.4

Figue 15. SuperSOTTM _ 3 Maximum Steady-State Power Dissipation versus Copper Mounting Pad Area.

Figure 16. Maximum Steady-State Drain Current versus Copper Mounting Pad Area.

1

r(t), NORMALIZED EFFECTIVE TRANSIENT THERMAL RESISTANCE

0.5 0.2 0.1 0.05 0.02 0.01 0.005 0.002 0.001 0.0001

D = 0.5 0.2 0.1 0.05 0.02 0.01 Single Pulse

R JA (t) = r(t) * R JA R JA = See Note 1b

P(pk)

t1

t2

TJ - TA = P * R JA (t) Duty Cycle, D = t1 /t2

0.001

0.01

0.1 t 1 , TIME (sec)

10

100

300

Figure 17. Transient Thermal Response Curve.

Note : Characterization performed using the conditions described in note 1b. Transient thermal response will change depending on the circuit board design.

NDS351AN Rev. C

Anda mungkin juga menyukai

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDari EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsBelum ada peringkat

- Irfp 260 NDokumen9 halamanIrfp 260 NJolaine MojicaBelum ada peringkat

- Irfb4020Pbf: Digital Audio MosfetDokumen8 halamanIrfb4020Pbf: Digital Audio Mosfetto_netiksBelum ada peringkat

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MDokumen11 halamanFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MKevin TateBelum ada peringkat

- Fdms0308Cs: N-Channel Powertrench SyncfetDokumen8 halamanFdms0308Cs: N-Channel Powertrench Syncfetdreyes3773Belum ada peringkat

- IRFP360LCDokumen8 halamanIRFP360LCΗρακλης ΖερκελιδηςBelum ada peringkat

- Irlz 24 NDokumen9 halamanIrlz 24 NRobson PontinBelum ada peringkat

- IRF8788Dokumen9 halamanIRF8788Robert KovacsBelum ada peringkat

- IRF540NDokumen7 halamanIRF540Nmichaelliu123456Belum ada peringkat

- Irf1405 DatasheetDokumen9 halamanIrf1405 DatasheetE Alejandro G. BenavidesBelum ada peringkat

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETDokumen9 halamanFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloBelum ada peringkat

- Irfz46n PDFDokumen9 halamanIrfz46n PDFYunier FernandezBelum ada peringkat

- IRF830A: Smps MosfetDokumen8 halamanIRF830A: Smps MosfetRICHIHOTS2Belum ada peringkat

- Irl 1004Dokumen9 halamanIrl 1004Luiz RvBelum ada peringkat

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Dokumen11 halamanN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TateBelum ada peringkat

- Fds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetDokumen12 halamanFds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetAlejandro DelgadoBelum ada peringkat

- International Rectifier IRFP2907Dokumen9 halamanInternational Rectifier IRFP2907scribd20110526Belum ada peringkat

- Irf 730 ADokumen9 halamanIrf 730 Ajose_mamani_51Belum ada peringkat

- IRFZ34N Datasheet - KDokumen8 halamanIRFZ34N Datasheet - KNairo FilhoBelum ada peringkat

- AO4800 Dual N-Channel Enhancement Mode Field Effect TransistorDokumen6 halamanAO4800 Dual N-Channel Enhancement Mode Field Effect Transistordreyes3773Belum ada peringkat

- NTD78N03 Power MOSFET: 25 V, 78 A, Single N Channel, DPAKDokumen7 halamanNTD78N03 Power MOSFET: 25 V, 78 A, Single N Channel, DPAKfercikeBelum ada peringkat

- Irfp2907Pbf: Typical ApplicationsDokumen9 halamanIrfp2907Pbf: Typical Applicationsrajeev_kumar_1231852Belum ada peringkat

- Irf 3205 ZPBFDokumen13 halamanIrf 3205 ZPBFOsman KoçakBelum ada peringkat

- FET 75N75 TransistorDokumen8 halamanFET 75N75 Transistorshahid iqbalBelum ada peringkat

- Dual N-Channel Enhancement Mode Phn210T Trenchmos TransistorDokumen8 halamanDual N-Channel Enhancement Mode Phn210T Trenchmos TransistorCristian ViolaBelum ada peringkat

- Irl 530 NDokumen9 halamanIrl 530 NEric Lenin Marin MoncadaBelum ada peringkat

- Generation V Technology Ultra Low On-Resistance Complimentary Half Bridge Surface Mount Fully Avalanche RatedDokumen10 halamanGeneration V Technology Ultra Low On-Resistance Complimentary Half Bridge Surface Mount Fully Avalanche RatedFidel ArroyoBelum ada peringkat

- FDS4435BZDokumen6 halamanFDS4435BZCornel PislaruBelum ada peringkat

- FDP 8896Dokumen11 halamanFDP 8896condejhonnyBelum ada peringkat

- FQB8N60C / FQI8N60C: 600V N-Channel MOSFETDokumen9 halamanFQB8N60C / FQI8N60C: 600V N-Channel MOSFETemelchor57Belum ada peringkat

- FQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETDokumen10 halamanFQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETJavier Ayerdis NarváezBelum ada peringkat

- Radiation Hardened Power Mosfet THRU-HOLE (T0-204AE) I R H 9 1 5 0 100V, P-CHANNELDokumen8 halamanRadiation Hardened Power Mosfet THRU-HOLE (T0-204AE) I R H 9 1 5 0 100V, P-CHANNELDeepa DevarajBelum ada peringkat

- Data Sheet IRFB42N20DDokumen8 halamanData Sheet IRFB42N20DvalubaBelum ada peringkat

- NDP6051 / NDB6051 N-Channel Enhancement Mode Field Effect TransistorDokumen6 halamanNDP6051 / NDB6051 N-Channel Enhancement Mode Field Effect TransistorHoàng Ngọc QuyềnBelum ada peringkat

- 2N60Dokumen8 halaman2N60vdăduicăBelum ada peringkat

- FDMS3604SDokumen12 halamanFDMS3604Sg_alinBelum ada peringkat

- IRF740B/IRFS740B: 400V N-Channel MOSFETDokumen11 halamanIRF740B/IRFS740B: 400V N-Channel MOSFETMistery of the souldBelum ada peringkat

- Irlhs 6242 PBFDokumen9 halamanIrlhs 6242 PBFSergiu HălăucăBelum ada peringkat

- Irfr3707Zpbf Irfu3707Zpbf: V R Max QGDokumen11 halamanIrfr3707Zpbf Irfu3707Zpbf: V R Max QGJared RobisonBelum ada peringkat

- IRFB4227Dokumen8 halamanIRFB4227Fco. Jefferson Ferreira de SáBelum ada peringkat

- Dual N-Channel, Notebook Power Supply MOSFET: June 1999Dokumen9 halamanDual N-Channel, Notebook Power Supply MOSFET: June 1999dreyes3773Belum ada peringkat

- IRF650B / IRFS650B: 200V N-Channel MOSFETDokumen10 halamanIRF650B / IRFS650B: 200V N-Channel MOSFETbinoelBelum ada peringkat

- Irfp 460 ADokumen8 halamanIrfp 460 AKasun Darshana PeirisBelum ada peringkat

- 2N7000 JfetDokumen8 halaman2N7000 JfetMichel RigaudBelum ada peringkat

- 13N60 Series: N-Channel Power MOSFET 13A, 600volts DescriptionDokumen8 halaman13N60 Series: N-Channel Power MOSFET 13A, 600volts DescriptionAndres AlegriaBelum ada peringkat

- IRF9540NDokumen8 halamanIRF9540Nhardik_patel182000Belum ada peringkat

- N 308 ApDokumen11 halamanN 308 Apdragon-red0816Belum ada peringkat

- N Mosfet Fdv303nDokumen4 halamanN Mosfet Fdv303nxlam99Belum ada peringkat

- Irfp 90 N 20 DDokumen9 halamanIrfp 90 N 20 DAndré Frota PaivaBelum ada peringkat

- Fdb045An08A0: N-Channel Powertrench MosfetDokumen12 halamanFdb045An08A0: N-Channel Powertrench MosfetRocio HernandezBelum ada peringkat

- Irfps 3810 PBFDokumen8 halamanIrfps 3810 PBFCrisan Radu-HoreaBelum ada peringkat

- IRF3710Dokumen8 halamanIRF3710Andrés MorochoBelum ada peringkat

- Advanced Power Electronics Corp.: AP4525GEMDokumen7 halamanAdvanced Power Electronics Corp.: AP4525GEMsontuyet82Belum ada peringkat

- Data SSMPS MOSFETheetDokumen8 halamanData SSMPS MOSFETheetwaqasmirBelum ada peringkat

- Irfz 34 NLDokumen10 halamanIrfz 34 NLguerrero_27Belum ada peringkat

- Radiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELDokumen8 halamanRadiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELbmmostefaBelum ada peringkat

- MosfetDokumen6 halamanMosfetfilibertooBelum ada peringkat

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesDari EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesPenilaian: 4.5 dari 5 bintang4.5/5 (7)

- E10.unit 3 - Getting StartedDokumen2 halamanE10.unit 3 - Getting Started27. Nguyễn Phương LinhBelum ada peringkat

- Business Maths Chapter 5Dokumen9 halamanBusiness Maths Chapter 5鄭仲抗Belum ada peringkat

- Digital Economy 1Dokumen11 halamanDigital Economy 1Khizer SikanderBelum ada peringkat

- Comparativa Microplex F40 Printronix P8220 enDokumen1 halamanComparativa Microplex F40 Printronix P8220 enangel ricaBelum ada peringkat

- SoC Showdown: Snapdragon 810 Vs Exynos 7420 Vs MediaTek Helio X10 Vs Kirin 935 - AndroidAuthority - PDDokumen19 halamanSoC Showdown: Snapdragon 810 Vs Exynos 7420 Vs MediaTek Helio X10 Vs Kirin 935 - AndroidAuthority - PDArpit SharmaBelum ada peringkat

- Biology Concepts and Applications 9th Edition Starr Solutions ManualDokumen9 halamanBiology Concepts and Applications 9th Edition Starr Solutions Manualscarletwilliamnfz100% (31)

- Inclusions in Gross IncomeDokumen2 halamanInclusions in Gross Incomeloonie tunesBelum ada peringkat

- 0apageo Catalogue Uk 2022Dokumen144 halaman0apageo Catalogue Uk 2022Kouassi JaurèsBelum ada peringkat

- Aui2601 Exam Pack 2016 1Dokumen57 halamanAui2601 Exam Pack 2016 1ricara alexia moodleyBelum ada peringkat

- Fashion Goes VirtualDokumen1 halamanFashion Goes VirtualJessica MichaultBelum ada peringkat

- PTEG Spoken OfficialSampleTest L5 17mar11Dokumen8 halamanPTEG Spoken OfficialSampleTest L5 17mar11Katia LeliakhBelum ada peringkat

- Transportation Engineering Unit I Part I CTLPDokumen60 halamanTransportation Engineering Unit I Part I CTLPMadhu Ane NenuBelum ada peringkat

- Case 1394 Moteur 1 2Dokumen36 halamanCase 1394 Moteur 1 2ionel ianosBelum ada peringkat

- NS1 UserManual EN V1.2Dokumen31 halamanNS1 UserManual EN V1.2T5 TecnologiaBelum ada peringkat

- MC0085 MQPDokumen20 halamanMC0085 MQPUtpal KantBelum ada peringkat

- Statistics 2Dokumen121 halamanStatistics 2Ravi KBelum ada peringkat

- A Study On Awareness of Mutual Funds and Perception of Investors 2Dokumen89 halamanA Study On Awareness of Mutual Funds and Perception of Investors 2Yashaswini BangeraBelum ada peringkat

- Amplifier Frequency ResponseDokumen28 halamanAmplifier Frequency ResponseBenj MendozaBelum ada peringkat

- Cpar Final Written Exam 1Dokumen3 halamanCpar Final Written Exam 1Jeden RubiaBelum ada peringkat

- Unknown 31Dokumen40 halamanUnknown 31Tina TinaBelum ada peringkat

- PDF Cambridge Experience Readers American English Starter A Little Trouble in California Sample Chapter PDF CompressDokumen11 halamanPDF Cambridge Experience Readers American English Starter A Little Trouble in California Sample Chapter PDF CompressSandra MacchiaBelum ada peringkat

- Lab 08: SR Flip Flop FundamentalsDokumen6 halamanLab 08: SR Flip Flop Fundamentalsjitu123456789Belum ada peringkat

- Topics For Oral PresentationDokumen6 halamanTopics For Oral PresentationMohd HyqalBelum ada peringkat

- FoodhallDokumen3 halamanFoodhallswopnilrohatgiBelum ada peringkat

- Consumer Price SummaryDokumen5 halamanConsumer Price SummaryKJ HiramotoBelum ada peringkat

- D-Dimer DZ179A Parameters On The Beckman AU680 Rev. ADokumen1 halamanD-Dimer DZ179A Parameters On The Beckman AU680 Rev. AAlberto MarcosBelum ada peringkat

- Upend RA Kumar: Master List of Approved Vendors For Manufacture and Supply of Electrical ItemsDokumen42 halamanUpend RA Kumar: Master List of Approved Vendors For Manufacture and Supply of Electrical Itemssantosh iyerBelum ada peringkat

- Urban LifestyleDokumen27 halamanUrban LifestyleNindy AslindaBelum ada peringkat

- Simple Fat Burning Exercises at Home or GymDokumen6 halamanSimple Fat Burning Exercises at Home or GymShirleyBelum ada peringkat

- 2062 TSSR Site Sharing - Rev02Dokumen44 halaman2062 TSSR Site Sharing - Rev02Rio DefragBelum ada peringkat