Wipro

Diunggah oleh

Sathya VigneshJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Wipro

Diunggah oleh

Sathya VigneshHak Cipta:

Format Tersedia

1612

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, VOL. 21, NO. 11, NOVEMBER 2011

Time Multiplexed VLSI Architecture for Real-Time Barrel Distortion Correction in Video-Endoscopic Images

Shih-Lun Chen, Hong-Yi Huang, Member, IEEE, and Ching-Hsing Luo, Member, IEEE

AbstractA low-cost very large scale integration (VLSI) implementation of real-time correction of barrel distortion for videoendoscopic images is presented in this paper. The correcting mathematical model is based on least-squares estimation. To decrease the computing complexity, we use an odd-order polynomial to approximate the back-mapping expansion polynomial. By algebraic transformation, the approximated polynomial becomes a monomial form which can be solved by Hornors algorithm. With the iterative characteristic of Hornors algorithm, the hardware cost and memory requirement can be conserved by time multiplexed design. In addition, a simplied architecture of the linear interpolation is used to reduce more computing resource and silicon area. The VLSI architecture of this paper contains 13.9-K gates by using a 0.18 m CMOS process. Compared with some existing distortion correction techniques, this paper reduces at least 69% hardware cost and 75% memory requirement. Index TermsBarrel distortion correction, Hornors algorithm, least-squares estimation, time multiplexed, videoendoscopic image.

I. Introduction IDEO-ENDOSCOPY plays an important role in clinical applications, such as gastrointestinal tract, respiratory tract, urology, gynecology, and surgical procedures. The camera with wide-angle lens (sh-eye lens) of clinical endoscope can capture a larger eld of interior body in a single image. Such a system enhances the capability of images. However, its outcome shows barrel-type spatial distortion which causes the image regions farther from the distortion center to be compressed more than those near the center by a non-linear distortion. Thus, the outer regions of the image are observed smaller than their actual size. Many researchers have proposed various mathematical models and algorithms to correct the endoscopic and wide-angle

Manuscript received July 16, 2010; revised November 2, 2010; accepted December 13, 2010. Date of publication March 17, 2011; date of current version November 2, 2011. This work was supported by the National Science Council, Taiwan, under Grants NSC-99-2221-E-006-109 and NSC-98-2220E-006-008. Also, this work made use of Shared Facilities supported by the Program of Top 100 Universities Advancement, Ministry of Education, Taiwan. This paper was recommended by Associate Editor Y.-K. Chen. S.-L. Chen and C.-H. Luo are with the Department of Electrical Engineering, National Cheng Kung University, Tainan 701, Taiwan (e-mail: chenshihlun@gmail.com; robin@ee.ncku.edu.tw). H.-Y. Huang is with the Graduate Institute of Electrical Engineering, National Taipei University, San Shia 237, Taiwan (e-mail: hyhuang@mail.ntpu.edu.tw). Color versions of one or more of the gures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identier 10.1109/TCSVT.2011.2129850

camera distorted images [1][10]. These studies provide novel technologies to correct the distorted images by some efcient algorithms. However, the proposed software solutions do not meet the high speed demand for real-time videoendoscopic applications. For example, a biomedical videoendoscopic real-time system is designed with a 1024 1024 wide-angle lens and it requires capturing 30 frames/s. By this specication, this system needs to correct more than 30 Mega (1024 1024 30) distorted pixels per second. Since each correcting procedure for each distorted pixel consumes more than a few instruction cycles, the software solutions are hard to meet the requirement of real-time video-endoscopic applications. Several studies concerning very large scale integration (VLSI) architectures of real-time barrel distortion correction have been presented recently. Asari presented an efcient VLSI architecture to correct wide-angle camera images by mapping the algorithmic steps onto a linear array [11]. Pipelined architecture is presented in [12]. In this literature, high performance pipelined architecture for correction of barrel distortion in wide-angle camera images is proposed. A pipelined coordinate rotation digital computer (CORDIC) is used in this paper for improving the efciency of coordinate transformation. In addition, a low-cost high-speed 21-stage pipelined VLSI architecture for barrel distortion correction is presented in [13]. Angle calculation elimination and odd-order back-mapping polynomial are used to improve performance and reduce hardware cost. The methods of the previously proposed technologies were based on the least-square estimation scheme presented by Asari [3]. In video-endoscopic applications, the barrel distortion correction circuit is integrated into medical instrument. Thus, since lower hardware cost and high performance become important parameters in most biomedical applications, prudent implementation should be considered. In this paper, we present a low-cost VLSI architecture for real-time distortion correction circuit. The correction mathematical model is based on leastsquares estimation method [3], [11]. After analyzing the correcting procedure, we found the most computing resources are concentrated on coordinate transformation, back-mapping, and linear interpolation. To lower the computing resources, rstly we used an odd-order polynomial to approximate the back-mapping expansion polynomial. After which, the odd-order back-mapping and polar to Cartesian coordinate

1051-8215/$26.00 c 2011 IEEE

CHEN et al.: TIME MULTIPLEXED VLSI ARCHITECTURE FOR REAL-TIME BARREL DISTORTION CORRECTION IN VIDEO-ENDOSCOPIC IMAGES

1613

transformation can be combined into a new polynomial. Since the new combined polynomial is based on the vector magnitude square, a square root and an arc-tangent calculation can be efciently removed. To reduce more hardware, we used algebraic transformation to replace all the vector magnitude square by a new variable. It makes the new combined polynomial becomes a monomial form. Therefore, Hornors algorithm [16] is able to efciently evaluate the results of back-mapping and polar to Cartesian coordinate transformation. This approach not only greatly decreases the calculation complexity of back-mapping but also provide a exible architecture for different designs by time multiplexed technique [17], [18]. To reduce more hardware costs and power consumption, we also implemented a low cost linear interpolation circuit by algebraic manipulation technique. It greatly eliminates the number of multipliers from eight to three. In this paper, we created a novel lowcost, low-power, and low memory requirement four-cycle time multiplexed distortion correction circuit for biomedical videoendoscopic or wide-angle camera applications. The organization of this paper is presented as follows. Section II introduces the proposed less complex distortion correction methodology. Section III describes the details of the proposed VLSI architecture. Section IV shows the comparisons and experimental results. And nally, in Section V, the conclusion is presented.

Each image pixel (u , v ) in DIS can be mapped into a new location (u, v) in CIS. The corresponding distance and angle from the correction center (uc , vc ) to (u, v) can be obtained by = (u uc )2 + (v vc )2 v vc u uc . (2a) (2b)

= arctan

The corresponding relationship between and can be dened by an expansion polynomial of degree N as

N

=

n=1

an ( )n =

(3a) (3b)

where an is expansion coefcient which can be obtained by the least-squares estimation method [3]. Since it is assumed that the distortion is purely radial about the distortion center, the angle is the same as . The new location (u, v) in CIS can be calculated as u = uc + cos v = vc + sin. B. Back-Mapping Procedure Coordinate Transformation and Polar to (4a) (4b) Cartesian

II. Proposed Low-Complexity Distortion Correction Technique In this section, the proposed low-complexity distortion correction technique based on least-square estimation method is presented. In the beginning of this section, a transformation mapping from Cartesian coordinate to polar coordinate for all pixels is introduced. Then, a simplifying procedure is introduced to decrease the computing resource of backmapping and polar to Cartesian coordinate steps by eliminating the angle and reducing the square root operation for . Then, Hornors algorithm is adopted to reduce more computing resource of the simplied one. Finally, a basic algebraic manipulation is used to decrease the arithmetic resource of the linear interpolation. A. Cartesian to Polar Coordinate Transformation The rst step of the proposed distortion correction technique is transforming all pixels in the distorted image space (DIS) onto the corrected image space (CIS). The distortion center is (u c , v c ) in DIS and the correction center is (uc , vc ) in CIS. In DIS, (u , v ) is the Cartesian coordinate and ( , ) is the polar coordinate. The distance from distortion center (u c , v c ) to an image pixel (u , v ) and the angle between the pixel and distortion center are given by = (u uc )2 + (v vc )2 v vc u uc . (1a) (1b)

After transforming the image pixels from Cartesian coordinate to polar coordinate, the back-mapping module maps the pixel (, ) in CIS into the corresponding location ( , ) in DIS. As presented in [3] and [12], the back-mapping procedure can be dened by a back-mapping expansion polynomial of degree N as

N

=

n=1

bn n

(5a) (5b)

where bn is the back-mapping coefcient which can be obtained by the least-squares estimation method. The angles and are the same since the distortion is assumed to be purely radial about the distortion center. C. Polynomial Approximating Analysis The back-mapping expansion polynomial can be approximated to odd-order or even-order polynomial by (5a) as = co0 + co1 3 + co2 5 + co3 7 . . . = ce0 2 + ce1 4 + ce2 6 + ce3 8 . . . (6a) (6b)

= arctan

where co0 , co1 , co2 , co3 . . . or ce0 , ce1 , ce2 , ce3 . . . are oddorder or even-order coefcients of the odd-order or even-order back-mapping polynomial. To be able to analyze the qualities of the odd-order and even-order approximating polynomials, ten sample images, some of which were used as test images in

1614

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, VOL. 21, NO. 11, NOVEMBER 2011

TABLE I Comparison of Approximated Rates of Odd-Order and Even-Order Polynomials with Back-Mapping Expansion Polynomial Odd-Order PSNR Approximated Rate (%) 23.84 97.49 22.21 95.75 23.20 97.52 24.19 98.14 25.25 97.09 24.97 96.75 21.76 97.29 22.79 96.57 23.38 96.27 25.98 98.45 23.76 97.13 Even-Order PSNR Approximated Rate (%) 10.79 59.28 10.22 51.11 10.24 66.77 9.60 55.27 10.56 50.53 10.73 49.56 10.79 75.23 10.14 56.04 11.38 61.00 10.14 60.56 10.46 58.53

Thus, the cos and sin can be obtained as cos = cos = sin = sin = u uc v vc . (8a) (8b)

Test Image Lena Peppers Airplane Mandrill Girl Cameraman Pirate Sailboat Splash House Average

Based on the odd-polynomial technique by (7) and eliminating the calculation of angle by (8a), (8b), the back-mapping and polar to Cartesian coordinate steps can be simplied as u = uc + u uc

= uc + (c0 + c1 3 + c2 5 + c3 7 + c4 9 + ...)

u uc = uc + (c0 + c1 2 + c2 4 + c3 6 + c4 8 + ...) (u uc ) (9a) v vc

v = vc + previous papers dealing with image processing, were selected as a test set. To obtain the qualities of the back mapping approximating by odd-order and even-order, the PSNR values and approximated rates are used to evaluate. First, the ten test images were distortion corrected by the back mapping expansion polynomial, as shown in (5a), and the obtained result images are stored as golden patterns. After which, we used odd-order and even-order polynomials, as shown in (6a) and (6b), to correct the ten test images and then stored the result images as comparison patterns. Finally, the results can be obtained by computing the PSNR values and approximated rates between the comparison and golden patterns. Table I lists the PSNR values and the percentages of approximated rates of the ten testing images by odd-order and even-order polynomials with the back mapping expansion polynomial. The results show that the odd-order polynomial achieves 97.13% average approximation to the back mapping expansion polynomial, which is much better than even-order one by 58.53%. D. Simplied Back-Mapping Procedure As mentioned above, the odd-order polynomial is highapproximation to the back mapping expansion polynomial. According to previous techniques [13][15], the back-mapping expansion polynomial can be approximated to odd-order polynomial as = c0 + c1 3 + c2 5 + c3 7 + . . . (7)

= vc + (c0 + c1 3 + c2 5 + c3 7 + c4 9 + ...)

v vc = vc + (c0 + c1 2 + c2 4 + c3 6 + c4 8 + ...) (v vc ). (9b)

After the simplication process, the u and v can be obtained by simple arithmetic operations without the need of square root and the value of 2 can be calculated by 2 = (u uc )2 + (v vc )2 . (10)

E. Hornors Algorithm The purpose of Horners algorithm [16] is to efciently evaluate the polynomials in monomial form. For example, a typical polynomial equation is represented as

n

f (x) =

i=0

ci xi = c0 + c1 x + c2 x2 + c3 x3 + ... + cn xn (11)

where c1 , c2 , c3 , . . . are real numbers, and the polynomial is necessary to be evaluated at the appointed value of x = x0 . In usual method, to evaluate the polynomial f (x0 ) is to evaluate i each product of Cix separately and then sum all products. It spends large computing resource to evaluate any power of x. By rewriting (11), the polynomial can be described as f (x) = c0 +x(c1 +x(c2 +x(c3 +x(. . .+x(cn1 +cn x) . . .)))). (12) The purpose of Horners algorithm is to evaluate the polynomial at a specic value of x = x0 . Thus, we dened a new sequence of constants set an as an = cn an1 = cn1 + an x0 an2 = cn2 + an1 x0 : a0 = c0 + a1 x0

where c0 , c1 , c2 , c3 . . . are back-mapping coefcients of the odd-order back-mapping polynomial. In fact, the is the square root of the sum of (u uc )2 and (v vc )2 as shown in (2a). It cannot be calculated by simple arithmetic operations. In literature [12], the CORDIC module is implemented with huge hardware cost to obtain the value of . There are two steps to reduce the computing resources of back-mapping procedure. The rst is eliminating the calculation of [13]. According to (5b), the and are the same.

CHEN et al.: TIME MULTIPLEXED VLSI ARCHITECTURE FOR REAL-TIME BARREL DISTORTION CORRECTION IN VIDEO-ENDOSCOPIC IMAGES

1615

TABLE II Comparison of Equations and Computing Resource with Previous Technologies [12], [13]

where c1 , c2 , c3 , . . . cn1 , cn are the combined mapping coefcients of the polynomial. The computing resource of the back-mapping and polar to Cartesian coordinate steps can f (x)=c0 + x0 (c1 + x0 (c2 + x0 (c3 + x0 (. . . + x0 (cn1 + an x0 ) . . .)))) be efciently decreased by only computing 2 . The most = c0 + x0 (c1 + x0 (c2 + x0 (c3 + x0 (. . . + x0 (an1 ) . . .)))) complexity of computing the power values of 2 (4 , 6 , 8 . . .) can be efciently reduced by Hornors algorithm. : = c0 + x0 (a1 ) = a0 . As described above, the polynomial can be rewritten by an iteration function. The function f n which is the nth iteration of f can be represented as f f n1 and it is dened as f n = f f n1 . (13) F. Simplied Linear Interpolation In previous literatures, [12], [13], the linear interpolation is directly implemented by the linear interpolation equation as I(u, v) = I (x, y) (1 dx) (1 dy) + I (x + 1, y) dx (1 dy) + I (x, y + 1) (1 dx) dy + I (x + 1, y + 1) dx dy (16) where I (x, y), I (x+1, y), I (x, y+1), and I (x+1, y+1) are the intensity values of the four neighboring pixels at the location of (x, y), (x + 1, y), (x, y + 1), and (x + 1, y + 1). Hence, the computing resource of linear interpolation costs at least eight multiply and three add operations. It also means that eight multipliers and three adders are necessary when implementing a VLSI circuit. For this reason, we used the algebraic manipulation to decrease the computing resource as well as hardware cost for the linear interpolation. Equation (17) shows the general arithmetic function of linear interpolation combined by (16). By the algebraic manipulation, the arithmetic function of the linear interpolation can be simplied as (17d). The simplication procedure is illustrated from (17a) through (17b) and (17c) to (17d). Besides, the function of (I (x, y+1)I (x, y)) dy + I (x, y) is obtained in (17d) twice, which means that one calculation of this function will be reduced. As mentioned above, the computing resource of linear interpolation can be simplied as three multiplication and six addition operations. Thus, this simplied arithmetic function of the linear interpolation provides a low-cost and low-power element for VLSI circuit. Table II lists the comparison of the equations and computing resource of previous techniques [12], [13] with this paper. Obviously, the complexity and computing resource of this paper are lower than others.

To replace x0 by x and iteratively substitute constants set an into (12). The polynomial can be represented as

To rewrite the polynomial as iteration function, the evaluation of the polynomial at the appointed value of x = x0 can be represented as f n (x0 ) = (cn1 + cn x0 f n1 (x0 ). (14)

The purpose of evaluating the polynomial is to compute f (x0 ) where x0 is a constant. The Hornors algorithm [16] supports an efcient method and it works as follows. Hornors Algorithm Step 1. Set u n (where n is the degree of the polynomial) Step 2. Set Result Cn . Step 3. If u = 0 stop. Answer is Result. Step 4. Compute Result Result x0 + Cu1 . Step 5. u u 1. Step 6. Go to step 3. By Hornors algorithm, the computing complexity of the evaluating polynomial can be efciently decreased. The complexity of back-mapping and polar to Cartesian coordinate steps can be reduced in the same way. Equations (9a) and (9b) can be rewritten as u = uc + (cn1 + cn 2 f n1 (2 )) (u uc ) v = vc + (cn1 + cn 2 f n1 (2 )) (v vc ) (15a)

(15b)

1616

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, VOL. 21, NO. 11, NOVEMBER 2011

TABLE III Combined Mapping Coefficients c0 c1 c2 c3 c4 Fig. 1. Block diagram of the architecture for proposed distortion correction VLSI circuit. 0 5.559280514717 103 1.11027 1010 3.3928353570171216 1017 2.173691884067 1023

III. VLSI Architecture As mentioned in Section III, the distortion correction methodology can be simplied into two main parts: 1) combined mapping unit, and 2) simplied linear interpolation unit. The combined unit is not only reduced in computing resource by Hornors algorithm but also reduced more in hardware cost by time multiplexed technique. Fig. 1 shows the I(u, v) = I (x, y) (1 dx) (1 dy) +I (x + 1, y) dx (1 dy) + I (x, y + 1) (1 dx) dy + I (x + 1, y + 1) dx dy (17a)

lists the set of the ve combined mapping coefcients obtained in the present experiment. To shorten the word length of the hardware architecture, the main operations of (18a) and (18b) can be rewritten as c0 + 2 (c1 + 2 (c2 + 2 (c3 + 2 c4 ))) = c0 + (2 216 ) {(c1 216 )+(2 216 )[(c2 232 ) + (2 216 )((c3 248 ) +(2 216 ) (c4 264 ))]} = c0 + (2 216 ) (c1 216 ) + (4 232 ) (c2 232 ) +(6 248 ) (c3 248 ) + (8 264 ) (c4 264 ).

4

(19)

= dx [I (x, y) (1 dy) + I (x + 1, y) (1 dy) +(I (x, y + 1) + I (x + 1, y + 1)) dy] + I (x, y) (17b) (1 dy) + I (x, y + 1) dy = dx {dy [I (x + 1, y + 1) I (x, y + 1) I (x + 1, y) + I (x, y)] + I (x + 1, y) I (x, y)} +dy [I (x, y + 1) I (x, y)] + I (x, y) = dx {[I (x + 1, y + 1) I (x + 1, y)] dy +I (x + 1, y) (I (x, y + 1) I (x, y)) dy +I (x, y)} + (I (x, y + 1) I (x, y)) dy + I (x, y) (17d) block diagram of the architecture of the proposed distortion correction VLSI circuit. The details of each part will be described in the following subsections. A. Combined Mapping Unit For the function of the combined mapping, each pixel (u , v ) in DIS can be calculated by the pixel (u, v). By the oddorder approximated polynomial and Hornors algorithm, the back-mapping results u and v can be obtained by expanding (15) as u = uc + (c0 + 2 (c1 + 2 (c2 + 2 (c3 + 2 c4 )))) (u uc ) (18a) v = vc + (c0 + 2 (c1 + 2 (c2 + 2 (c3 + 2 c4 )))) (v vc ) (18b) where c0 , c1 , c2 , c3 and c4 are combined mapping coefcients. Since c1 , c2 , c3 and c4 are the coefcients of the terms 2 , 4 , 6 and 8 , the values of them are much less than 1. Table III (17c)

By this manipulation, not only the values of the terms 2 , , 6 and 8 are scaled down but also the word length of the coefcients c1 , c2 , c3 and c4 are limited. Both of the terms and coefcients are represented with 24-bit word which includes 9-bit integer and 15-bit fraction. Accordingly, the results of the terms times the coefcients are composed of 18bit integer and 30-bit fraction. With the consideration of the word length in architecture, the top 9-bit and the bottom 15-bit are reduced. For this reason, the data format of the multiplied result is compatible with the data format of the coefcient, by which the next add operation can be computed without transformation. Fig. 2 shows the architecture of the combined mapping unit, in which a 20-stage pipelined architecture of the combined mapping unit is proposed for mapping pixels. As the discussion of [12], [13], most multipliers are 24-bit wide with a propagation delay of a 24-bit multiplier long. Thus, each multiplier is designed with a pipelined architecture to complete a multiply operation in two cycles. Since the input data formats of u and v are both 16-bit integers, the hardware resources of (u uc ) (uuc ) and (vvc ) (vvc ) in states 34 are consisted of two pipelined 16 16 multipliers. In the gure, the multipliers are two-stage pipelined multipliers and the shadowed rectangles are registers. The critical path of the combined mapping unit design can be shortened with the 20-stage pipelined architecture. B. Simplied Linear Interpolation Unit The purpose of linear interpolation is to obtain the intensity value I(u, v) of location (u , v ) from the intensity values of four neighboring pixels: I(x, y), I(x + 1, y), I(x, y + 1), and I(x +1, y +1). The function of linear interpolation is simplied by the algebraic manipulation as shown in (17). Fig. 3 shows the architecture of the simplied linear interpolation unit with the proposed 11-stage pipelined architecture of the simplied linear interpolation unit. In the gure, the multipliers are two-stage pipelined multipliers and the shadowed rectangles represent registers.

CHEN et al.: TIME MULTIPLEXED VLSI ARCHITECTURE FOR REAL-TIME BARREL DISTORTION CORRECTION IN VIDEO-ENDOSCOPIC IMAGES

1617

Fig. 3.

Architecture of the simplied linear interpolation unit.

Fig. 2.

Architecture of the combined mapping unit.

Fig. 4. Architecture of neighboring pixels reading and fractions obtaining circuit.

Fig. 4 shows the architecture of neighboring pixels reading and fractions obtaining circuit. The u and v are obtained from stage 20 of the combined mapping unit. The length of u and v is 24-bit, and the highest 16 of 24 bits are integer parts and the lowest 8 of 24 bits are fractional parts. Thus, the register value of x or y vector can be obtained directly by connecting wires with the highest 16-bit of the u or v register. The register value of dx or dy can be obtained from the lowest 8-bit of the u or v register in the same way. The size of each DIS RAM is the same as the size of the input image and the four intensity values of I(x, y), I(x + 1, y), I(x, y + 1), and I(x + 1, y + 1) can be read simultaneously from the four DIS RAMs. C. Time Multiplexed Architectures As mentioned in Section III, the back-mapping step demands the most computing resource of the distortion correcting procedure. Although the computing complexity of the back-mapping step is efciently decreased by Hornors algorithm, implementation of the distortion correcting circuit

presents a limitation on hardware cost. As shown in (13a), (13b), the evaluation of polynomial can be described as an iteration function, which provides exibility in implementing the back-mapping circuit with different architecture by time multiplexed technique [17], [18]. Fig. 5 shows three architectures of the back-mapping circuit. Since the back-mapping step can be described as an iteration function as shown in (18a) and (18b), the hardware architecture can be implemented as one-cycle, two-cycle, or four-cycle to complete the back-mapping procedure. Fig. 5(a) shows the one-cycle architecture of back-mapping circuit, the same as the stages from 6 to 17 of the combined mapping unit in Fig. 2, which costs four pipelined multipliers and four adders. It can obtain one back-mapping result during each clock cycle with 12-stage pipelined architecture. However, the hardware cost and memory requirement are quite a few. Fig. 5(b) and (c) shows the two-cycle and four-cycle architectures of backmapping circuit, respectively. The hardware costs of these

1618

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, VOL. 21, NO. 11, NOVEMBER 2011

TABLE IV Hardware Resources of Various Distortion Correction Architectures [12] [13] Square root Arc-tangent 24 24 multiplier 16 24 multiplier 16 16 multiplier 8 8 multiplier Adder 1 1 7 0 0 8 10 0 0 7 2 2 8 14 This Paper One-Cycle Two-Cycles Four-Cycles 0 0 0 0 0 0 4 2 1 2 2 2 2 2 2 3 3 3 17 15 14

TABLE V Comparison of Distortion Correcting Circuit with One-Cycle, Two-Cycle, and Four-Cycle Back-Mapping Designs Distortion Correction One-cycle 0.18 m CMOS 28 622 200 MHz 4 45.68 mW 160 Mpixels/s 2560 2048 30 frame/s 2.06 Distortion Correction Two-cycles 0.18 m CMOS 15 895 200 MHz 2 24.97 mW 80 Mpixels/s 1920 1080 30 frame/s 1.14 Distortion Correction Four-cycles 0.18 m CMOS 13 917 200 MHz 1 16.81 mW 40 Mpixels/s 1024 1024 30 frame/s 1

Fig. 5. Architectures of back-mapping circuit with (a) one-cycle, (b) twocycles, (c) four-cycle to complete a back-mapping procedure.

Back-mapping circuit cycle Process Gate counts Frequency DIS RAM Power Throughput Quality support Normalized area

Fig. 6. Architecture of memory reading circuit with (a) one-cycle, (b) twocycle, (c) four-cycle to complete reading four neighboring pixel values.

architectures are less than that of one-cycle. Nevertheless, the execution time to get one back-mapping result needs two or four cycles. Fig. 6 shows the three architectures of the memory reading circuit for reading the identity values of four neighboring pixels of location (u , v ). Fig. 6(a) shows the one-cycle architecture which can read four identity values during each clock cycle and provide a high-speed circuit for parallel

memory read. However, it demands four input image size of DIS RAMs. Fig. 6(b) and (c) shows the two-cycle and fourcycle architectures of memory reading circuit. Obviously, the memory requirement of two-cycle or four-cycle architectures is only two or one of DIS RAMs. Table IV shows detailed comparisons between the hardware resources of various architectures of distortion correction designs. According to the table, Ngo et al.s [12] does not contain any 16 24 and 16 16 multipliers, which is less than other architectures. However, the hardware implementation of square root by CORDIC module in [12] and [19] consumes a huge hardware cost. Comparing the hardware resources of [12] and [13], and the three architectures of this paper, we can clearly nd the contribution of each technique used in this paper. The results show that the algebraic manipulation of linear interpolation by this paper contributes reducing 62.5% (ve of eight) 8 8 multipliers from [12] and [13]. Observing the number of 24 24 multipliers in Table IV, the one-cycle architecture of this paper consists of four 2424 multipliers as compared to the 24 24 multipliers in [12] and [13] which have seven. As mentioned above, the Hornors algorithm technique contributes decreasing 37.5% (three of seven) 24 24 multipliers from [12] and [13]. Furthermore, the Hornors algorithm technique not only directly conserves hardware cost by lessening the requirements of multipliers but also provides a exible architecture for the time multiplexed design. To compare the four-cycle and one-cycle architectures

CHEN et al.: TIME MULTIPLEXED VLSI ARCHITECTURE FOR REAL-TIME BARREL DISTORTION CORRECTION IN VIDEO-ENDOSCOPIC IMAGES

1619

TABLE VI Comparisons of This paper With Other Previous Low-Complexity Designs [12] [13] This Paper [13] This Paper Altera Altera Altera 0.18 m 0.18 m EP20K600EBC652-1X EP20K600EBC652-1X EP20K600EBC652-1X CMOS CMOS Total logic elements 18 344 7163 1686 N/A N/A Flip-ops 15 355 2811 770 N/A N/A Gate counts N/A N/A N/A 44 992 13 917 Memory requirements 4 4 1 4 1 (size of input image) (1024 1024 byte) (1024 1024 byte) (1024 1024 byte) (1024 1024 byte) (1024 1024 byte) Frequency 40 MHz 56.98 MHz 59.93 MHz 200 MHz 200 MHz Throughput 30 Mpixels/s 40 Mpixels/s 14 Mpixels/s 140 Mpixels/s 40 Mpixels/s Normalizedlogic elements/gate counts 10.88 4.25 1 3.23 1 FPGA device/ ASIC Library

of this paper in Table IV, there are three 24 24 multipliers are saved. Accordingly, the time multiplexed technique contributes reducing 75% (three of four) 24 24 multipliers from the architecture without time multiplexed design. The results show that the proposed three architectures consume the less hardware resources than [12] and [13] especially multipliers. The proposed four-cycle architecture achieves reducing hardware resources of 46.6% or 57.9% multipliers than [12] or [13]. Table V lists the comparison of the distortion correcting circuit with one-cycle, two-cycle, or four-cycle back-mapping circuit design. Since time multiplexed design, the two-cycle and four-cycle architecture decrease the throughput from 160 to 80 and 40 mega pixels per second (Mpixels/s). Although the throughputs of two-cycle and four-cycle architectures are much less than one-cycle design, other parameters such as hardware cost, memory requirements, and power consumptions have shown superiority as compared to one-cycle architecture. To summarize, the selection of back-mapping architecture should depend on the demand of image quality. For example, if the quality of the distortion image is the resolution of high denition multimedia interface of QSXGA (2560 2048) at 30 frames/s, only one-cycle architecture can be selected to meet the demand of throughput. In contrast, if the quality of image demands no more than the size of 1024 1024 at 30 frames/s, the four-cycle architecture is applicable due to low-cost and power consumption. As suggested above, we select the four-cycle time multiplexed architecture as our distortion correcting circuit for biomedical endoscopic applications. IV. Experimental Results The VLSI architecture of this paper was implemented by Verilog HDL. Based on a 0.18 m CMOS standard cells, this design was synthesized by using SYNOPSYS Design Vision. The layout of this design was generated by the auto placement and routing tool SYNOPSYS Astro. Synthesis results show that the distortion-correction circuit contains 13 917 gates, and its chip area is 139 175 m2 . The power consumption is 16.81 mW at 200 MHz operation frequency with 1.8 V supply voltage. Furthermore, we also implemented this design for emulation by a FPGA verication board. The Quartus II was used to synthesize this design based on Altera EP20K600EB FPGA and it consumes 1686 logic elements.

Fig. 7. Hardware emulation image results of correcting barrel distortion in wide-angle camera and endoscopic images. (a) Distorted black-point images. (b) Corrected black-point image by this paper. (c) Gastrointestinal image captured by video-endoscope. (d) Corrected gastrointestinal image by this paper. (e) Gastrointestinal image captured by video-endoscope. (f) Corrected gastrointestinal image by this paper. (g) Gastrointestinal image with grid. (h) Corrected grid gastrointestinal image by this paper.

1620

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, VOL. 21, NO. 11, NOVEMBER 2011

Table VI lists the implemented results of this paper with previous low-complexity designs [12], [13]. The logic elements in FPGA and gates in silicon chip of this paper are both less than the others. It achieves the reductions of 90.8% or 76.4% logic elements in FPGA than [12] or [13], and 69% gates than [13]. The critical path of this design is 5 ns, which results in the operation clock frequency up to 200 MHz. Although the time multiplexed design limits the throughput due to obtaining one result per four cycles, the throughput of this paper achieves 40 Mpixels/s. It is more than the value of (10241024+31)30, which includes 31 stages of pipeline delays to obtain the rst result for each frame. Accordingly, this paper is fast enough to real-time correcting high quality biomedical endoscopic image (1024 1024) at 30 frames/s. Therefore, this design satises the requirement of biomedical video-endoscopy applications. Fig. 7 shows the distorted and corrected images resulting in wide-angle camera and endoscopic images. The distorted black-point image taken by a wide-angle camera is shown in Fig. 7(a) and the corrected image result by this paper is shown in Fig. 7(b). A typical gastrointestinal image captured by an endoscope [20] is shown in Fig. 7(c) or (e), and the corresponding corrected image result is shown in Fig. 7(d) or (f). Fig. 7(g) shows a gastrointestinal image captured by an endoscope with grid. The correcting effect can be obtained by comparing the corrected image result, as shown in Fig. 7(h), by this paper with the corresponding gastrointestinal image with grid.

V. Conclusion In this paper, a low-cost, low-power, and low memory requirement VLSI architecture of distortion correcting circuit was presented for biomedical endoscope applications. The computing complexity of correcting functions is decreased by Hornors algorithm and the algebraic manipulation of the linear interpolation. Moreover, the time multiplexed design provides different architectures for satisfying different applications. With reference to other low-complexity architectures, this paper reduces at least 69% hardware cost and 75% memory requirement than other VLSI correcting designs.

Acknowledgment The authors would like to thank the Center for Micro/Nano Technology Research and the Center of Bioscience and Technology, National Cheng Kung University, Tainan, Taiwan.

[2] H. Hideaki, Y. Yagihashi, and Y. Miyake, A new method for distortion correction of electronic endoscope images, IEEE Trans. Med. Imaging, vol. 14, no. 3, pp. 548555, Mar. 1995. [3] K. V. Asari, S. Kumar, and D. Radhakrishnan, A new approach for nonlinear distortion correction in endoscopic images based on least squares estimation, IEEE Trans. Med. Imaging, vol. 18, no. 4, pp. 345 354, Apr. 1999. [4] J. P. Helferty, C. Zhang, G. McLennan, and W. E. Higgins, Videoendoscopic distortion correction and its application to virtual guidance of endoscopy, IEEE Trans. Med. Imaging, vol. 20, no. 7, pp. 605617, Jul. 2001. [5] J. Weng, P. Cohen, and M. Herniou, Camera calibration with distortion models and accuracy evaluation, IEEE Trans. Pattern Anal. Mach. Intell., vol. 14, no. 10, pp. 965980, Oct. 1992. [6] Y. Nomura, M. Sagara, H. Naruse, and A. Ide, Simple calibration algorithm for high-distortion-lens camera, IEEE Trans. Pattern Anal. Mach. Intell., vol. 14, no. 11, pp. 10951099, Nov. 1992. [7] R. Swaminathan and S. K. Nayar, Non-metric calibration of wide-angle lenses and polycameras, IEEE Trans. Pattern Anal. Mach. Intell., vol. 22, no. 10, pp. 11721178, Oct. 2000. [8] J. Kannala and S. S. Brandt, A generic camera model and calibration method for conventional, wide-angle, and sh-eye lenses, IEEE Trans. Pattern Anal. Mach. Intell., vol. 28, no. 8, pp. 13351340, Aug. 2006. [9] R. Hartley and S. B. Kang, Parameter-free radial distortion correction with center of distortion estimation, IEEE Trans. Pattern Anal. Mach. Intell., vol. 29, no. 8, pp. 13091321, Aug. 2007. [10] J. Park, S. C. Byun, and B. U. Lee, Lens distortion correction using ideal image coordinates, IEEE Trans. Consumer Electron., vol. 55, no. 3, pp. 987991, Aug. 2009. [11] V. K. Asari, Design of an efcient VLSI architecture for non-linear spatial warping of wide-angle camera image, J. Syst. Architec., vol. 50, pp. 743755, Aug. 2004. [12] H. T. Ngo and V. K. Asari, A pipelined architecture for real-time correction of barrel distortion in wide-angle camera images, IEEE Trans. Circuits Syst. Video Technol., vol. 15, no. 3, pp. 436444, Mar. 2005. [13] P. Y. Chen, C. C. Huang, Y. H. Shiau, and Y. T. Chen, A VLSI implementation of barrel distortion correction for wide-angle camera images, IEEE Trans. Circuits Syst. II Express Briefs, vol. 56, no. 1, pp. 5155, Jan. 2009. [14] M. T. El-Melegy and A. A. Farag, Nonmetric lens distortion calibration: Closed-form solutions, robust estimation and model selection, in Proc. IEEE Int. Conf. Comput. Vis., vol. 1. Oct. 2003, pp. 554559. [15] M. Marder, Comparison of calibration algorithms for a low-resolution, wide angle, 3-D camera, M.S. thesis, Electr. Eng. Dept., KTH, Roy. Inst. Technol., Stockholm Univ., Stockholm, Sweden, Mar. 2005. [16] W. G. Horner, A new method of solving numerical equations of all orders, by continuous approximation, Philos. Trans. Royal Soc. London, pp. 308335, Jul. 1819. [17] P. Tummeltshammer, C. Hoe, and M. Puschel, Time-multiplexed multiple-constant multiplication, IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., vol. 26, no. 9, pp. 15511563, Sep. 2007. [18] Y. S. Kwon and C. M. Kyung, Performance-driven event-based synchronization for multi-FPGA simulation accelerator with event timemultiplexing bus, IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., vol. 24, no. 9, pp. 14441456, Sep. 2005. [19] J. D. Bruguera, N. Guil, T. Lang, J. Villalba, and E. L. Zapata, CORDIC based parallel/pipelined architecture for the Hough transform, J. VLSI Signal Process., vol. 12, no. 3, pp. 207221, Jun. 1996. [20] Gastroenterologist Hospital. El Salvador Atlas of Gastrointestinal Video Endoscopy [Online]. Available: http://www.gastrointestinalatlas.com

References

[1] W. E. Smith, N. Vakil, and S. A. Maislin, Correction of distortion in endoscopic images, IEEE Trans. Med. Imaging, vol. 11, no. 1, pp. 117122, Jan. 1992.

Shih-Lun Chen received the B.S. and M.S. degrees in electrical engineering from National Cheng Kung University, Tainan, Taiwan, in 2002 and 2004, respectively. He is currently pursuing the Ph.D. degree from the Department of Electrical Engineering, National Cheng Kung University. His current research interests include very large scale integration chip design, image processing, biomedical signal processing, wireless sensor networks, and recongurable architecture.

CHEN et al.: TIME MULTIPLEXED VLSI ARCHITECTURE FOR REAL-TIME BARREL DISTORTION CORRECTION IN VIDEO-ENDOSCOPIC IMAGES

1621

Hong-Yi Huang (S89M94) was born in Taiwan, in 1965. He received the B.S. degree in nuclear engineering from National Tsing-Hua University, Hsinchu, Taiwan, in 1987, and the M.S. and Ph.D. degrees from the Institute of Electronics, National Chiao-Tung University, Hsinchu, in 1989 and 1994, respectively. He was with the Industrial Technology Research Institute, Hsinchu, from 1994 to 1999, engaged in mixed-signal integrated circuits design. He has been with the Department of Electronic Engineering, Fu-Jen Catholic University, New Taipei, Taiwan, since 1999. He has been an Associate Professor with the Graduate Institute of Electrical Engineering, National Taipei University, San Shia, Taiwan, since 2006. He has authored and co-authored over 60 research papers and 30 patents. His current research interests include bio-circuits and systems, high-speed and low-power lowvoltage integrated circuits and systems, embedded memory, analog, and communication integrated circuits.

Ching-Hsing Luo (M05) received the B.S. degree in electrophysics from National Chiao Tung University, Hsinchu, Taiwan, the M.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, in 1982, the M.S. degree in biomedical engineering from Johns Hopkins University, Baltimore, MD, in 1987, and the Ph.D. degree in biomedical engineering from Case Western Reserve University, Cleveland, OH, in 1991. He has been a Distinguished Professor with the Department of Electrical Engineering, National Cheng Kung University, Tainan, Taiwan, since 2005. His current research interests include biomedical instrumentation-on-a-chip, assistive device and agent systems, cell modeling, signal processing, radio frequency integrated circuits, implantable wireless biosensing chips, genome simulation, and pulse diagnosis platform in traditional Chinese medicine.

Anda mungkin juga menyukai

- Princeton Sop Arnab SinhaDokumen2 halamanPrinceton Sop Arnab SinhaSathya VigneshBelum ada peringkat

- Vlsi Lab ManualDokumen2 halamanVlsi Lab ManualSathya VigneshBelum ada peringkat

- Test Pattern GenerationDokumen23 halamanTest Pattern GenerationSathya VigneshBelum ada peringkat

- Digital DesignDokumen2 halamanDigital DesignsakthikothandapaniBelum ada peringkat

- 19 MlintroDokumen29 halaman19 MlintroSathya VigneshBelum ada peringkat

- Princeton Sop Arnab SinhaDokumen2 halamanPrinceton Sop Arnab SinhaSathya VigneshBelum ada peringkat

- WIPRO Placement Sample Paper 1Dokumen11 halamanWIPRO Placement Sample Paper 1Pratik PawarBelum ada peringkat

- Chap 1 2 PDFDokumen12 halamanChap 1 2 PDFSathya VigneshBelum ada peringkat

- F 090120 B Figure BDokumen1 halamanF 090120 B Figure BSathya VigneshBelum ada peringkat

- WiproDokumen12 halamanWiproSathya VigneshBelum ada peringkat

- 06046696Dokumen6 halaman06046696Sathya VigneshBelum ada peringkat

- TCS PatternsDokumen29 halamanTCS Patternssubhojit007Belum ada peringkat

- Nice Aptitude Problems With AnswersDokumen45 halamanNice Aptitude Problems With Answersratnesht87100% (2)

- Microsoft Word - Venn Diagrams - Basics, Problems, Maxima and Minima - 4Dokumen8 halamanMicrosoft Word - Venn Diagrams - Basics, Problems, Maxima and Minima - 4api-19746201100% (1)

- 1 Jyoti & Pritee - Advance Applications of (PP 1-4)Dokumen4 halaman1 Jyoti & Pritee - Advance Applications of (PP 1-4)Sathya VigneshBelum ada peringkat

- Set TheoryDokumen2 halamanSet Theoryapi-3827626Belum ada peringkat

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Daewoo DLX32D1SMSB Manual de Servicio LCDDokumen40 halamanDaewoo DLX32D1SMSB Manual de Servicio LCDAlexis ColmenaresBelum ada peringkat

- AE461 ARM SYSTEM ARCHITECTURE (Careeryuga) PDFDokumen2 halamanAE461 ARM SYSTEM ARCHITECTURE (Careeryuga) PDFAbhijith SreekumarBelum ada peringkat

- Nishikant Power System Internship Report Docs 1Dokumen23 halamanNishikant Power System Internship Report Docs 1Darshan PawarBelum ada peringkat

- 300Mbps Wireless N PCI Adapter: TL-WN851NDDokumen2 halaman300Mbps Wireless N PCI Adapter: TL-WN851NDRiyan LesmanaBelum ada peringkat

- JBL Tune 125tws Manual OriginalDokumen2 halamanJBL Tune 125tws Manual OriginalMacBBelum ada peringkat

- Marshalling KioskDokumen4 halamanMarshalling KioskThant Zin100% (1)

- 873P Ultrasonic Sensors With Dual Discrete/Single Analog OutputsDokumen4 halaman873P Ultrasonic Sensors With Dual Discrete/Single Analog Outputsmanduca matthewBelum ada peringkat

- PSEN Ma1 4p-50 Operat Manual 22126-EN-06Dokumen21 halamanPSEN Ma1 4p-50 Operat Manual 22126-EN-06Doganay KalguBelum ada peringkat

- ARK-3420 User Manual Ed.1Dokumen82 halamanARK-3420 User Manual Ed.1juanfdominguezBelum ada peringkat

- Final DCN Spring 2020 PDFDokumen2 halamanFinal DCN Spring 2020 PDFMUHAMMAD AHMEDBelum ada peringkat

- SMPS Trainer Kit ComputersDokumen1 halamanSMPS Trainer Kit ComputersChandrakant ChatterjeeBelum ada peringkat

- List of EquipmentDokumen32 halamanList of EquipmentsutanuprojectsBelum ada peringkat

- OBD II Pro PlusFordDokumen50 halamanOBD II Pro PlusFordkamaleon doradoBelum ada peringkat

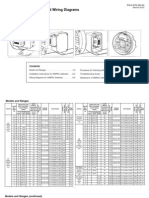

- Installation Instructions and Wiring Diagrams For All Models and RangesDokumen8 halamanInstallation Instructions and Wiring Diagrams For All Models and RangesMaria MusyBelum ada peringkat

- Atasheet en 201508 T58I-E-02 Rev3 2Dokumen17 halamanAtasheet en 201508 T58I-E-02 Rev3 2deri mardiBelum ada peringkat

- The Long and Short of Wires: Background KnowledgeDokumen2 halamanThe Long and Short of Wires: Background KnowledgeNilar SanBelum ada peringkat

- XFX 750W Black Edition PSU Modular True Power Power SupplyDokumen5 halamanXFX 750W Black Edition PSU Modular True Power Power SupplyPenyelongkar KonspirasiBelum ada peringkat

- Equinox Lipo Cell Balancer-ManualDokumen6 halamanEquinox Lipo Cell Balancer-ManualKin TiriyasBelum ada peringkat

- JLN-550 Instruction ManualDokumen48 halamanJLN-550 Instruction ManualAdi Prasetyo100% (1)

- MTS4 Base StationDokumen4 halamanMTS4 Base Stationrachit2712Belum ada peringkat

- Functional Design Specification - Automation SystemDokumen52 halamanFunctional Design Specification - Automation SystemHari Prashanna83% (6)

- Keller: P T T S 21 RDokumen2 halamanKeller: P T T S 21 RAmal AntonyBelum ada peringkat

- Bender New Product - Overview - HK - en - 2020 PDFDokumen32 halamanBender New Product - Overview - HK - en - 2020 PDFDipankar SahaBelum ada peringkat

- Analog Communication Exam Paper T2 PDFDokumen7 halamanAnalog Communication Exam Paper T2 PDFvavaBelum ada peringkat

- 2008-06-04 124629 Corolla Tsib 5Dokumen3 halaman2008-06-04 124629 Corolla Tsib 5nuwan_nisha100% (2)

- Line Follower RobotDokumen10 halamanLine Follower Robotvishal groverBelum ada peringkat

- ML Maximum Power Point Tracking (MPPT) Series Ml4860: User ManualDokumen13 halamanML Maximum Power Point Tracking (MPPT) Series Ml4860: User ManualReymark EmbateBelum ada peringkat

- 37PFL5332 LC7 (1) .1LDokumen114 halaman37PFL5332 LC7 (1) .1LWall BrysonBelum ada peringkat

- EL5000 Hardware IntroductionDokumen39 halamanEL5000 Hardware Introductionapi-3855014Belum ada peringkat

- Woodward Egcp-2 DatasheetDokumen4 halamanWoodward Egcp-2 DatasheetbambangBelum ada peringkat