Methodology To Achieve Ride-Through of An Adjustable Speed Drives (ASD's) Using Supercapacitors During Voltage Sag

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Methodology To Achieve Ride-Through of An Adjustable Speed Drives (ASD's) Using Supercapacitors During Voltage Sag

Hak Cipta:

Format Tersedia

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

Methodology to Achieve Ride-Through of an Adjustable Speed Drives (ASDs) Using Supercapacitors during Voltage Sag

S.S.Deswal1, Rajveer Mittal2, Ratna Dahiya3 and D.K.Jain4

1 2

Assoc. Prof., Department of Electrical Engg., Maharaja Agrasen Institute of Technology, Sec-22, Rohini, Delhi Assoc. Prof., Department of Electrical Engg., Maharaja Agrasen Institute of Technology, Sec-22, Rohini, Delhi

3 4

Professor, Department of Electrical Engg., NIT, Kurukshetra, Haryana

Professor, Department of Electrical Engg., DCRUST, Murthal, Haryana

ABSTRACT

During the voltage unbalance, the resulting adverse effects on equipments such as induction motors and power electronic converters and drives on ASDs have been described. It has been observed that during unsymmetrical fault, the input rectifier slips into the single phase operation and draw heavy currents which may actuate the overload protection and trip the ASDs. The application of supercapacitors bank with boost converter to inject energy at DC-Link under voltage unbalance condition has been incorporated. The supercapacitor provides ride-through and reduces the current overshooting by injecting energy at DCLink. Based on the designed topology, simulation model in MATLAB 7.5 (Sim Power Block set) has been developed for voltage unbalance conditions with supercapacitor as an energy storage device. The designed control technique is modeled, simulated and successfully implemented in the laboratory. The extensive simulation results supported by experimental results were provided to validate the proposed system .

Keywords: Adjustable Speed Drives, Electric Power Quality, Ride-through Capabilities, Energy Storage Devices, Supercapacitors

1. INTRODUCTION

The greatest effect of voltage unbalance is on three-phase induction motors. Three-phase induction motors are one of the most common loads on the network and are found in large numbers especially in industrial environments. When a three-phase induction motor is supplied by an unbalanced system the resulting line currents show a degree of unbalance that is several times the voltage unbalance. An excessive level of voltage unbalance can have serious impacts on mains connected induction motors. Although induction motors are designed to tolerate a small level of unbalance they have to be derated if the unbalance is excessive. Voltage unbalance also has an impact on ac variable speed drive systems where the front end consists of three-phase rectifier systems. The triplen harmonic line currents that are uncharacteristic to these rectifier systems can exist in these situations leading to unexpected harmonic problems. Although it is practically impossible to eliminate voltage unbalance it can be kept under control at both utility and plant level by several practical approaches. Voltage unbalance is regarded as a power quality problem of significant concern at the electricity distribution level. Although the voltages are quite well balanced at the generator and transmission levels the voltages at the utilization level can become unbalanced due to the unequal system impedances and the unequal distribution of single-phase loads. The level of current unbalance that is present is several times the level of voltage unbalance. Such an unbalance in the line currents can lead to excessive losses in the stator and rotor that may cause protection systems to operate causing loss of production. [1-5] Three-phase diode rectifier systems are an essential part of conventional Adjustable Speed Drives as shown in . 1 and uninterruptible power supplies. These rectifier systems draw non-sinusoidal current waveforms from the ac mains. If the ac supply system is balanced the line current waveform may take the double pulse per half cycle shape that contains characteristic harmonic orders given by:

h kq 1

(1)

where h = harmonic order ,k = 1, 2,.and q=number of pulses of the rectifier system giving only 5th ,7th , 11th, 13th order harmonics.

Volume 2, Issue 1, January 2013

Page 29

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

Figure 1 Typical adjustable speed drives (ASDs) system As the supply system becomes unbalanced the line current waveform deviates away from the double pulse formation to single pulse formation leading to uncharacteristic triplen harmonics. Supply voltage unbalance can lead to tripping of drive systems that is caused by excessive ac line currents on some phases and under voltage on the DC-Link. This can also lead to excessive thermal stress on diodes and dc link capacitor. Increase in the unwanted triplen harmonic currents can also lead to undesirable harmonic problems in the supply system. The different ride-through require energy storage devices injecting power at the DC-link during voltage sags as described in the literature[7-15]. They are based around software control (such as kinetic and magnetizing energy recovery), hardware (such as increasing the DC-Link capacitor size), or a combination (such as a boost converter) [6, 19]. Most of the mitigation techniques are based on the injection of active power, thus compensating the loss of active power supplied by the system [10-13]. An important distinction between each of the possible ride-through approaches is their ability to provide full-power ride-through, which is required by many applications. The conventional topology of a boost converter can be used to maintain the DC-Link voltage during voltage sag, and can either be integrated into new drives between the rectifier and the DC-Link capacitors or retrofitted as an add-on module. The add-on module is used to retrofit existing drives with ride-through capabilities. Besides energy storage systems, some other devices Constant voltage transformers (CVT), DVR may be used to solve Electric Power Quality problems [9-12]. The sensitivity of AC ASDs to voltage sags is presented in a voltage tolerance curve is defined by IEEE Std. 1346[5] as shown in Figure 2. It may be seen that the ASDs can withstand a reduction in the line voltage upto 85% of nominal value for an extended duration of time. For all points falling below the voltage tolerance curve, the drive will trip. SEMI F47-0200, Specification for Semiconductor Processing Equipment Voltage Sag Immunity [6], specifies the required voltage sag tolerance for semiconductor fabrication equipment. SEMI F47 requires that semiconductor processing equipment tolerate voltage sags connected onto their AC power line. They must tolerate sags to 50% of equipment nominal voltage for duration of up to 200 ms, sags to 70% for up to 0.5 seconds, and sags to 80% for up to 1.0 second.

Figure 2 Voltage tolerance curve of an ASDs as per IEEE Std.1346

Volume 2, Issue 1, January 2013

Page 30

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

It is observed from the literature survey that only theoretical analysis have been done by the different researchers in regards of providing ride-through to an Adjustable Speed Drives during voltage unbalance due to unsymmetrical fault conditions. Experimental work for improving upon the adverse effects of voltage unbalancing on Adjustable Speed Drives has not yet been proposed and implemented. Therefore in the present work, it is aimed to study the effectiveness of the supercapacitor as an energy storage device for providing ride-through to ASDs during symmetrical and unsymmetrical fault conditions [16-22].

2. ANALYSIS OF SYMMETRICAL AND UNSYMMETRICAL FAULTS

2.1 Symmetrical The classification of different types of voltage sags such as type A,B,C,D,E are described in [2]. Voltage sag of Type A occurs because of balanced three-phase faults or power failure. This type of voltage sag is the most severe. Voltage sags of type A are symmetrical, all phases experience the same retained voltage and phase-angle jump. It results in the reduction of the voltage on the DC-Link which is proportional to the AC source voltage. The under-voltage or over current protection on the DC-Link may trip the ASDs. The basic model for a distribution system [7] is shown in Figure 3.

Figure 3 Basic model for fault analysis For a symmetric three-phase fault the voltage at the Point-of-Common-Coupling (PCC) can be estimated using a simple voltage-divider model represented by the equation (2). In this case the fault impedance is not considered.

Feeder E Z 1 S Feeder

(2)

Here V is the retained voltage at PCC, E1 is the pre-fault voltage in phase A, ZFeeder is the feeder impedance and ZS is the source impedance. 2.2 Unsymmetrical Faults A phase to ground fault will result in a type B. A phase to phase fault results in a type C. If the voltage sag is of Type B or Type C, the circuit will behave as a single-phase rectifier. Even 10% voltage sag will result in a single-phase operation of the three-phase diode rectifier. The voltage between the two non faulted phases is unaffected and the DCLink voltage will not be reduced, however the current amplitude will increase. The same amount of energy must be transferred, but now in two pulses instead of six pulses. The peak value of the current will be 200% larger, and may cause an over-current or a current unbalance. The over-current or unbalance protection may trip the ASDs. A phase angle jump will affect the phase voltages and the DC-Link voltage. For sag magnitude of 50%, the DC-Link voltage does not drop below 70%, even for a small capacitance. This is because there is at least one phase that is still at 100% magnitude, and this phase stablizes the DC-Link voltage. If there is a transformer that removes the zero-sequence between the fault location and the load for phase to ground fault, the voltage sag will be of type D. The voltage sags of type E, F and G are due to a two phase to ground fault [1-5]. For sag magnitude 50% in Type D, there is no phase which has 100% magnitude and, therefore, the effect is more harmful on the DC-Link. In case of type B, C, D or E voltage sag, input rectifier passes into single-phase operations with the consequences such as input current distortion and DC voltage ripple increase with dominant component at double frequency and with average voltage reduction in C type voltage sag case. Consequently torque contains the second and fourth harmonic components along with the fundamental. The motor torque oscillatory component presence can leads to mechanical resonance exciting in coupled multi-motor drives besides noise increase, for e.g. in paper production machines. Thus, the unsymmetrical faults lead to three major negative effects that unbalanced input voltages can have on ASDs performance. [9-12] : a) Significant input current unbalances which stresses the diode bridge rectifiers and input protective devices such as fuses, contactors and circuit breakers. b) Injects a second harmonic voltage component on the DC-Link voltage which increases the electrical stresses on the DC-Link choke inductor (if used) and the DC-Link electrolytic capacitors. It potentially shortens the capacitor lifetime.

Volume 2, Issue 1, January 2013

Page 31

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

c) May give rise to ripple torque of magnitude double the fundamental frequency of induction machine which increases the mechanical and thermal stresses.

3. PROPOSED RIDE-THROUGH TOPOLOGIES

The objective of this section is to investigate the performance of an ASDs under three-phase symmetrical and unsymmetrical fault leading to balanced and unbalanced voltage sag at PCC. The proposed topology is designed by using supercapacitor as energy storage device along with boost converter across DC-Link as a ride-through alternative for ASDs. The performance of ASDs under various fault conditions has been simulated using MATLAB Simulink Power System Block set tool box. The functional block diagram is shown in Figure 4. A three-phase programmable voltage source feeds the power bus to PCC through series impedance (taken as resistance of 0.1 ohm assuming the length of line to be very small). Two independent feeders are connected at this PCC bus; one feeds the ASDs and the other is connected to the load. The faults are created at the load feeder to study the impact of voltage sags on the ASDs connected at the same PCC. The shunt impedance method has been used to generate voltage sags [22]. At the time of faults the fault current flows through the impedance leading to a voltage drop across it, thereby causing voltage sags at PCC.

Figure 4 Block Diagram of Proposed Technique The ASDs used is a scalar controlled induction motor of specifications 5 H.P, 415 volts (L-L), 3- Phase, 4 Poles, 50 Hz, 1444 rpm and is having a supercapacitors as an energy storage device at DC-Link. A buck-boost DC-DC converter converts the output of the connected energy storage device to the desired DC-Link voltage. The hardware set up is shown in Figure 5. It consists of: a) AC/DC converter section: This unit consists of uncontrolled three- phase diode bride rectifier. b) DC/AC inverter unit: This unit consists of MOSFET based inverter. c) Energy Storage Devices: The device is a supercapacitor bank of 12V modules. This 12V DC is converted to 220 V DC (for experimental purpose) with the help of buck-boost converter Voltage Sag Generator Unit: The various types of faults were created in the lab using shunt impedance method by actually grounding/shorting the line terminals in order to represent the true voltage sag conditions as shown in Figure 4.

Volume 2, Issue 1, January 2013

Page 32

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

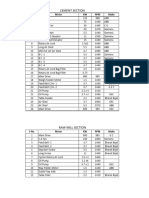

Figure 5 View of Designed Hardware 1. Waveform in LabVIEW 2. DAQ board 3. DC isolation circuit 4. Isolation transformer 5. Supercapacitor 6. 3-phase induction motor 7. Sag generator 8. 3-phase supply 9. AC/DC converter section 10.Capacitor bank(DC- link) 11. Adjustable speed drives 12. Boost convereter 13. DC- link 14. Function generator 15.3-phase Auto transformer 16. Battery

4. MODELING OF THE SYSTEM

4.1 Diode Rectifier Equations The basic equations of a three-phase uncontrolled rectifier with input impedance in derivative form are given as: pi (Vmax Vdc ) 2 Ls (3) d

pV (id io ) Co dc

(4)

where, id is supply current and io is the current drawn by the inverter section. The input AC currents of the rectifier are computed as follows. When VRY is maximum (Vmax) the current (id) flows from terminal R to Y through the concerned rectifier diode pair and the load. Where as for minimum value of VYR is maximum, the current flows from terminal Y to R. The current in line B is zero when these conditions exist. Likewise the currents flowing through the lines are computed when VYB and VBR satisfy these upper and lower voltage conditions. 4.2 Scalar Control of Induction Motor Drive An AC induction machine is scalar controlled, wherein, the ratio of stator voltage to frequency (V/F) is kept constant. 4.3 Modeling of Supercapacitor A supercapacitor can be modeled using some standard circuit components as shown in Figure6. The two variable capacitances are nonlinearly varying with the voltage that is applied across the circuit. The capacitance C is responsible for the most important phenomenon in the model. The amount of energy stored and the rate of energy level variations are both determined mainly by the capacitance value. The resistance R2 connected in parallel with the capacitor is meant to represent the self discharge effect. The series resistance R1 represents the losses during charge and discharge. The over voltage protection provided by R3 and the switch controlling its connection to the circuit is necessary to prevent damage to the capacitor elements by balancing the voltage level. The resistance Rp and the capacitance Cp are included in the circuit to model some of the fast dynamics in the behavior of the supercapacitor [11].

Volume 2, Issue 1, January 2013

Page 33

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

Figure 6 Basic circuit model of the supercapacitor Energy stored in the supercapacitor is given by the following equation:

E 1 2 CV 2

Usable Energy =

(5)

Where, C is the capacitance in farads, V is the voltage across C in volts; E is the energy stored in C in joules.

E 1 2 C V12 V2 2

(6)

Where, V1 is the rated charging voltage V2 is the rated minimum operating voltage of supercapacitors.

5.

CONTROL OF BUCK-BOOST DC-DC CONVERTER

The output voltage of the switch-mode DC-DC buck-boost converter is regulated to be within a specified range. There are two control methods for DC-DC converters: voltage mode control and current mode control respectively. The current mode control for a DC-DC buck boost converter has been employed in the proposed technique. It contains twoloop system as shown in Figure 4. An additional inner current loop is added to the voltage loop. The current loop monitors the inductor current and compares it with its reference value. The reference value for the inductor current is generated by the voltage loop. The key principle that drives the buck-boost converter is the tendency of an inductor to resist changes in current. When being charged it acts as a load and absorbs energy, when being discharged, it acts as an energy source. The voltage it produces during the discharge phase is related to the rate of change of current, and not to the original charging voltage, thus allowing different input and output voltages.

6. RESULTS AND DISCUSSION

The objective of this section is to investigate the performance of an ASDs under various power system faults. Figures. 7-10 show the performance of ASDs with the proposed scheme during balanced voltage sag and Figures. 11-14 during Double Line to Ground Faults (Type-E) with supercapacitor as ride-through. The simulations have been carried out to get the traces of three-phase source voltages (Vsry, Vsyb, Vsbr), three-phase source currents (Isr, Isy, Isb), Electromagnetic Torque(Te) , rotor speed (r) and DC-Link voltage (Vdc) respectively. Performance of ASDs during balanced voltage sag with supercapacitor as ride-through The simulation and hardware results during voltage sag due to symmetrical three-phase line to ground fault are shown in Figure 7 and Figure 8. The main characteristics of the voltage sag are magnitude and duration. The amplitude of line voltages drops to a value of about 60% of the pre-event voltage during 1.025 to 1.6 sec (about 28 cycles). During the symmetrical three phase fault the DC-Link voltage drops from 210V to 100 V. It can also observed from the same s that the Electromagnetic torque (Te) the speed (wr) decrease during fault period. The simulation and experimental results have been taken using supercapacitor as an energy storage device to provide ride-through to the ASDs as shown in Figure 9 and Figure 10. In this case the three-phase source voltage amplitude drops to a value of about 60% of the normal voltage during fault period i.e from 0.85 to 1.68 sec about 42 cycles. The transient response of the supercapacitor is fast enough to supply the current required by the ASDs during the sag. It has also been observed from the Figure 9 and Figure 10 that there is a marginal change in the DC-Link voltage during fault condition which fluctuates normally above the preset value of the DC-Link.

Volume 2, Issue 1, January 2013

Page 34

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

250 150 50 -50 -150 -250 250 150

sy b

( ) V () V V

sr y

50 -50 -150 -250 250 150

( ) V

sb r

50 -50 -150 -250

25 15 5

i ( ) A

s r

-5 -15 -25 25 15 5 -5 -15 -25 25 15 5 -5 -15 -25 400

( ) A ( ) A i v () V i

s b

s y

300

d c

200 100 0 0.9 1 0.95 1 1.05 1.1 1.15 1.2 1.25 1.3 1.35 1.4 1.45 1.5 1.55 1.6 1.65 1.7 1.75 1.8 1.85 1.9

time (s)

T( - ) N m

0.5 0

e

-0.5 -1 402 401.5 401 400.5 400 399.5 399 0.9

w( a / ) rd s

0.95

1.05

1.1

1.15

1.2

1.25

1.3

1.35

1.4

1.45

1.5

1.55

1.6

1.65

1.7

1.75

1.8

1.85

1.9

time (s)

Figure 7 Simulation Results showing three-phase source voltages, three-phase source currents, DC-Link voltage, Electromagnetic Torque and Rotor speed during symmetrical fault condition without providing any ride-through

Figure 8 Experimental Results showing three-phase source voltages, three-phase source currents, DC-Link voltage, Electromagnetic Torque and Rotor speed during symmetrical fault condition without providing any ride-through. Voltage scale: 100 V per division. Current scale: 2.25 A per division. DC-Link Voltage scale: 100 V per division

Volume 2, Issue 1, January 2013

Page 35

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

250

V () V

150

sy r

50 -50 -150 -250 250

() V

150

sb y

50 -50 -150 -250 250 150 50 -50 -150 -250

5

V () V

i () A

sr b

2.5

s r

0 -2.5 -5 5

i () A

2.5

s y

0 -2.5 -5 5

() A

2.5

s b

0 -2.5 -5 400

v () V

300

d c

200 100 0 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2 1.3 1.4 1.5 1.6 1.7 1.8 1.9 2

0.5

T( - ) N m

0.375

e

0.25 0.125 0 800

wr d ) (a/ s

600 400

r

200 0 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2 1.3 1.4 1.5 1.6 1.7 1.8 1.9 2

time (s)

Figure 9 Simulation Results showing three-phase source voltages, Currents, DC-Link voltage, Electromagnetic Torque, Rotor Speed during symmetrical fault condition with supercapacitor as ride-through alternative

Figure 10 Experimental Results showing three-phase source voltages, Currents, DC-Link voltage, Electromagnetic Torque, Rotor Speed during symmetrical fault condition with supercapacitor as ride-through alternative. Voltage scale: 100 V per division. Current scale: 2.25 A per division. DC-Link Voltage scale: 100 V per division

Volume 2, Issue 1, January 2013

Page 36

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

Performance of ASDs during Double Line to Ground Faults (Type-E) with supercapacitor as ride-through The simulation and hardware results during double line to ground fault are shown in Figure 11 to Figure 14. Simulated results shows that the amplitude of line voltage ry drops to a value of about 40% of the pre-event voltage and that of yb and br drops to 80% of the pre-event voltage during 1.32 to 1.48 sec about 8 cycles. During the fault period the three-phase uncontrolled rectifier operates in unbalanced mode and draws unbalanced peaky currents The DC-Link voltage drops from 195V to 155 V which is below the threshold setting at the DC-Link which may actuate the under voltage protection and trips the ASDs. The electromagnetic torque (Te) and the speed (wr) drop slightly as shown in Figure 11 and Figure12. It can be observed that the effective motor current during the fault period increases so as to maintain the desired torque. The simulation and hardware results under unsymmetrical fault condition are shown in Figure 13 and Figure 14 with supercapacitor as a ride-through capability connected across DC-Link using a buck-boost Converter. It is clearly seen from Figure 13 and Figure 14, the supercapacitor bank provides ride-through during the fault as well as post fault; since there is no inrush current after fault recovery.

() V

250 150

sr y

50 -50 -150 -250 250 150

() V

sy b

50 -50 -150 -250 250

() V

150

sb r

50 -50 -150 -250

7.5

(A )

2.5

sr

i ( ) A

-2.5 -7.5 7.5 2.5

sr

i ( ) A

-2.5 -7.5 7.5 2.5

sr

i v (V )

d c

-2.5 -7.5 250 200 150 100 0.5 1 0.4 0.3 0.2

0.1 0

1.05

1.1

1.15

1.2

1.25

1.3

1.35

1.4

1.45

1.5

1.55

1.6

1.65

1.7

1.75

1.8

T (N ) -m w (r d ) a /s

e r

400.5 400.4 400.3 400.2 400.1 400 1

1.05

1.1

1.15

1.2

1.25

1.3

1.35

1.4

1.45

1.5

1.55

1.6

1.65

1.7

1.75

1.8

time(s)

Figure 11 Simulation results showing three-phase source voltages, currents, DC- Link voltage, electro-magnetic torque and rotor speed during DLG fault (Type-E) without providing any ride- through

Volume 2, Issue 1, January 2013

Page 37

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

Figure 12. Experimental results showing three-phase source voltages, currents, DC- Link voltage, electro-magnetic torque and rotor speed during DLG fault (Type-E) without providing any ride- through. Voltage scale: 100 V per division. Current scale: 2.25 A per division. DC-Link Voltage scale: 100 V per division

250 150 50 -50 -150 -250 250 150 50 -50 -150 -250 250 150 50 -50 -150 -250

5

() V () V () V

() A

v v v

sr b

sb y

sy r

2.5

s r

0 -2.5 -5 5

() A

2.5

s y

0 -2.5 -5 5

() A

2.5

s b

0 -2.5 -5

v () V

225

d c

200 1.2 0.5 1.3 1.4 1.5 1.6 1.7 1.8 1.9 2 2.1 2.2

T( - ) N m

0.4 0.3

e

0.2 0.1 0 800

wrd) (a s /

600 400

r

200 0 1.2 1.3 1.4 1.5 1.6 1.7 1.8 1.9 2 2.1 2.2

time(s)

Figure 13 Simulation results showing three-phase source voltages, currents, DC-Link voltage, electro-magnetic torque and rotor speed during DLG fault (Type-E) with supercapacitor as ride-through alternative

Volume 2, Issue 1, January 2013

Page 38

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

Figure 14 Experimental results showing three-phase source voltages, currents, DC-Link voltage, electro-magnetic torque and rotor speed during DLG fault (Type-E) with supercapacitor as ride-through alternative. Voltage scale: 100 V per division. Current scale: 2.25 A per division. DC-Link Voltage scale: 100 V per division

7. CONCLUSIONS

In this paper the supercapacitors as an energy storage device for providing ride- through to ASDs during symmetrical and unsymmetrical fault conditions have been presented. The proposed topology is capable of providing ride- through during both symmetrical and unsymmetrical voltage sags. The effectiveness of the proposed topology has been verified by means of simulations based on MATLAB and experimental results obtained on a laboratory prototype. From these results it is clear that the supercapacitors dynamic response is fast enough to respond to the load transient requirements and avoid the affects of the various power quality disturbances on the adjustable speed drives. The supercapacitor maintains the DC-Link voltage thereby reduces the input inrush current. The main emphasis of this paper is that, the supercapacitor as an energy storage device may be employed during unsymmetrical fault condition so as to avoid the nuisance tripping of the ASDs.

REFERENCES

[1] G.T. Heydt, Electric Power Quality, 2nd ed. WestLafayette, Stars in a Circle, 1994. [2] M. H. J. Bollen, Understanding Power Quality Problems: Voltage Sags and Interruptions, Series on Power Engineering. New York: IEEE Press, 2000. [3] Hingorani N, Gyugyi L, Understanding FACTS, Wiley IEEE Press, 1999. [4] IEEE Recommended Practices on Monitoring Electric Power Quality, IEEE Std.1159, 1995. [5] IEEE Recommended Practices for Evaluating Electric Power System Compatibility With Electronic Process Equipment, IEEE Std.1346, 1998. [6] SEMI F47-0200, Specification for Semiconductor Processing Equipment Voltage Sag Immunity. [7] A. Z. Van. R. Spee, A. Faveluke and S. Bhowmik, Voltage Sag Ride-Through for Adjustable-Speed Drives With Active Rectifiers, IEEE Trans. on Industry Applications, vol. 34, issue 6, pp. 1270 1277, Nov.-Dec. 1998. [8] A. Von, P.N. Enjeti, B. Banerjee, Assessment of Ride-Through Alternatives for Adjustable-Speed Drives, IEEE Trans. on Industry Applications, vol. 35, issue 4, pp. 908 - 916, July-Aug. 1999.

Volume 2, Issue 1, January 2013

Page 39

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

[9] J. L. D. Gomez, P.N. Enjeti, A. J. Von,An Approach to Achieve Ride-Through of an Adjustable-Speed Drive with Fly back Converter Modules Powered by Super Capacitors, IEEE Trans. on Industry Applications, vol. 38, issue 2, pp. 514-522, March-April 2002. [10] K. Lee, T.M. Jahns, D.W. Novotony, T.A. Lipo, W.E. Berkopec, and V. Blasko, Impact of Inductor Placement on the Performance of Adjustable-Speed Drives Under Input Voltage Unbalance and Sag Conditions, IEEE Trans. on Industry Applications, vol. 42, no. 5, pp. 1230-1240, Sept./Oct. 2006. [11] A. Sannino, M. G. Miller, M. H. J. Bollen, " Overview of Voltage Sag Mitigation, IEEE Power Engineering Society Winter Meeting, vol. 4, pp. 2872 2878, 2000. [12] M.H.J. Bollen, Characterization of Voltage Dips Experienced by Three-Phase Adjustable-Speed Drives, IEEE Trans. on Power Delivery, vol. 12, No. 4, pp. 1666-1671, October 1997 [13] K. Lee, T. M. Jahns, G. Venkataramanan,, Modeling Effects of Voltage Unbalances in Industrial Distribution Systems With Adjustable-Speed Drives, IEEE Trans. on Industry Appl., vol. 44 , Issue. 5 , pp. 1322 1332, 2008. [14] S. Z. Djokic, K. Stockman, J. V. Milanovic, J. J. M. Desmet and R. Belmans, Sensitivity of AC Adjustable Speed Drives to Voltage Sags and Short Interruptions, IEEE Trans. on Power Del, vol. 20, Issue. 1, pp. 494505, 2005. [15] M. H. J. Bollen, L. D. Zhang,Analysis of VoltageTolerance of AC Adjustable-Speed Drives for Three-Phase Balanced And Unbalanced Sags, IEEE Transactions on Industry Applications, vol. 36 , Issue. 3, pp. 904- 910, 2000. [16] J. Pedra, F. Corcoles, F. J. Suelves, Effects of Balanced and Unbalanced Voltage Sags on VSI-Fed AdjustableSpeed Drives, IEEE Transactions on Power Delivery, vol. 20, Issue. 1, pp. 224-233, 2005. [17] V. B. Bhavaraju and P. N. Enjeti, An Active Line Conditioner to Balance Voltages in a Three-Phase System, IEEE Trans. Industry Applications, vol. 32, no. 2, pp. 287-292, Mar./Apr. 1996. [18] P. N. Enjeti and S. A. Choudhury, A New Control Strategy to Improve the Performance of a PWM AC To DC Converter Under Unbalanced Operating Conditions, IEEE Trans. Power Electron., vol. 8, pp. 493-500, Oct. 1993. [19] L. Morn, P. D. Ziogas, and G. Joos, Design Aspects of Synchronous PWM Rectifier-Inverter Systems under Unbalanced Input Voltage Conditions, IEEE Trans. Industry Applications, vol. 28, no. 6, pp. 1286-1293, Nov./Dec. 1986. [20] W. E. Brumsickle, R. S. Schneider, G. A. Luckjiff, D. M. Divan, and M. F. McGranaghan, Dynamic Sag Correctors: Cost Effective Industrial Power Line Conditioning, IEEE Trans. Ind. Application, vol. 37, pp. 212 217, Jan./Feb. 2001. [21] Y. Jang, M. M Jovanovic, New Two- ductor Boost Converter with Auxiliary Transformer, IEEE Transactions on Power Electronics, vol. 19, Issue. 1, pp. 169-175, 2004. [22] Y. H. Chung, G. H. Kwon, T. B. Park, K. Y. Lim,Voltage Sag and Swell Generator for the Evaluation of Custom Power Devices,IEEE General Meeting of Power Engineering Society, vol. 4, 2003.

AUTHOR

S. S. Deswal received his B.Tech degree in Electrical Engineering from R.E.C, Kurukshetra , Kurukshetra University ,Haryana, India in 1998, the M.E degree in Electrical Engineering(Power Apparatus and Systems) from Delhi College of Engineering, Delhi University, Delhi, India in 2005, and Ph.D. degree from N.I.T, Kurukshetra a Deemed University, Haryana in Feb 2012. Currently, he is working as a Associate Professor in EEE Department with the Maharaja Agrasen Institute of Technology, Rohini, Delhi under GGSIP University, Delhi, India. His research interests include electric power quality, ASDs, electric motor drives, renewable energy sources. Rajveer Mittal received his B.E degree in Electrical Engineering from R.E.C, Kurukshetra , Kurukshetra University ,Haryana, India in 1987, the M.E degree in Electrical Engineering(Instrumentation & Control) from Delhi College of Engineering, Delhi University, Delhi, India in 2003, and is currently pursuing the Ph.D. degree in the research area of Power Quality Studies of Wind Energy Systems of Electrical Engineering from N.I.T, Kurukshetra a Deemed University, Haryana, India. Currently, he is working as Head of the EEE Department with the Maharaja Agrasen Institute of Technology, Rohini, Delhi under GGSIP University , Delhi, India.His research interests include power quality, motor drives, and Renewable energy. Ratna Dahiya received her B.Tech from GBU, Pant Nagar and M.Tech and Ph.D. degree degree in Electrical Engineering from R.E.C, Kurukshetra, Kurukshetra University, Haryana, India. Currently, she is working as Professor in Electrical Engineering Department with the NIT, Kurukshetra (Deemed University), Haryana, India. Her research interests include SMES, electric power system and electric power quality.

Volume 2, Issue 1, January 2013

Page 40

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 1, January 2013 ISSN 2319 - 4847

D. K. Jain received his B.Sc. (Engg), M.E (Electrical Engg.) and Ph.D. degree in Electrical Engineering from R.E.C, Kurukshetra, Kurukshetra University, Haryana, India. Currently, he is working as Professor in Electrical Engineering Department with the Deen Bandhu Chhotu Ram University of Science and Technology(DCRUST), Murthal, Haryana, India. His research interests include electric power quality, ASDs, electric motor drives, renewable energy sources.

Volume 2, Issue 1, January 2013

Page 41

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Experimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterDokumen7 halamanExperimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Detection of Malicious Web Contents Using Machine and Deep Learning ApproachesDokumen6 halamanDetection of Malicious Web Contents Using Machine and Deep Learning ApproachesInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- THE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSDokumen7 halamanTHE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- Customer Satisfaction A Pillar of Total Quality ManagementDokumen9 halamanCustomer Satisfaction A Pillar of Total Quality ManagementInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- An Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewDokumen9 halamanAn Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Analysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyDokumen6 halamanAnalysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Study of Customer Experience and Uses of Uber Cab Services in MumbaiDokumen12 halamanStudy of Customer Experience and Uses of Uber Cab Services in MumbaiInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Soil Stabilization of Road by Using Spent WashDokumen7 halamanSoil Stabilization of Road by Using Spent WashInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- Staycation As A Marketing Tool For Survival Post Covid-19 in Five Star Hotels in Pune CityDokumen10 halamanStaycation As A Marketing Tool For Survival Post Covid-19 in Five Star Hotels in Pune CityInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- THE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSDokumen7 halamanTHE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Study of Customer Experience and Uses of Uber Cab Services in MumbaiDokumen12 halamanStudy of Customer Experience and Uses of Uber Cab Services in MumbaiInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- Customer Satisfaction A Pillar of Total Quality ManagementDokumen9 halamanCustomer Satisfaction A Pillar of Total Quality ManagementInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Detection of Malicious Web Contents Using Machine and Deep Learning ApproachesDokumen6 halamanDetection of Malicious Web Contents Using Machine and Deep Learning ApproachesInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- Analysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyDokumen6 halamanAnalysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Experimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterDokumen7 halamanExperimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- An Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewDokumen9 halamanAn Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Mexican Innovation System: A System's Dynamics PerspectiveDokumen12 halamanThe Mexican Innovation System: A System's Dynamics PerspectiveInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Impact of Effective Communication To Enhance Management SkillsDokumen6 halamanThe Impact of Effective Communication To Enhance Management SkillsInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Design and Detection of Fruits and Vegetable Spoiled Detetction SystemDokumen8 halamanDesign and Detection of Fruits and Vegetable Spoiled Detetction SystemInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Challenges Faced by Speciality Restaurants in Pune City To Retain Employees During and Post COVID-19Dokumen10 halamanChallenges Faced by Speciality Restaurants in Pune City To Retain Employees During and Post COVID-19International Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- A Comparative Analysis of Two Biggest Upi Paymentapps: Bhim and Google Pay (Tez)Dokumen10 halamanA Comparative Analysis of Two Biggest Upi Paymentapps: Bhim and Google Pay (Tez)International Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- A Digital Record For Privacy and Security in Internet of ThingsDokumen10 halamanA Digital Record For Privacy and Security in Internet of ThingsInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Performance of Short Transmission Line Using Mathematical MethodDokumen8 halamanPerformance of Short Transmission Line Using Mathematical MethodInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Impact of Covid-19 On Employment Opportunities For Fresh Graduates in Hospitality &tourism IndustryDokumen8 halamanImpact of Covid-19 On Employment Opportunities For Fresh Graduates in Hospitality &tourism IndustryInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Anchoring of Inflation Expectations and Monetary Policy Transparency in IndiaDokumen9 halamanAnchoring of Inflation Expectations and Monetary Policy Transparency in IndiaInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Synthetic Datasets For Myocardial Infarction Based On Actual DatasetsDokumen9 halamanSynthetic Datasets For Myocardial Infarction Based On Actual DatasetsInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Advanced Load Flow Study and Stability Analysis of A Real Time SystemDokumen8 halamanAdvanced Load Flow Study and Stability Analysis of A Real Time SystemInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- A Deep Learning Based Assistant For The Visually ImpairedDokumen11 halamanA Deep Learning Based Assistant For The Visually ImpairedInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- Secured Contactless Atm Transaction During Pandemics With Feasible Time Constraint and Pattern For OtpDokumen12 halamanSecured Contactless Atm Transaction During Pandemics With Feasible Time Constraint and Pattern For OtpInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Predicting The Effect of Fineparticulate Matter (PM2.5) On Anecosystemincludingclimate, Plants and Human Health Using MachinelearningmethodsDokumen10 halamanPredicting The Effect of Fineparticulate Matter (PM2.5) On Anecosystemincludingclimate, Plants and Human Health Using MachinelearningmethodsInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- THREE-POLE CONTACTORS Series HR33-HR55 Up To 30 KW: Control Coil Codes (IH25) F G D U X C W B ZDokumen8 halamanTHREE-POLE CONTACTORS Series HR33-HR55 Up To 30 KW: Control Coil Codes (IH25) F G D U X C W B Zrachman hardianBelum ada peringkat

- Vibration Severity StandardDokumen2 halamanVibration Severity Standardnmgurav0% (1)

- Smart Ato ManualDokumen6 halamanSmart Ato ManualPerran TrevanBelum ada peringkat

- Torque de Trepanos Smith (PDC - Tricono) PDFDokumen1 halamanTorque de Trepanos Smith (PDC - Tricono) PDFPither ZuritaBelum ada peringkat

- Abs EdgeDokumen39 halamanAbs Edgecorporacion corprosinfro100% (3)

- MRF Tyre Guide:: All You Need To KnowDokumen1 halamanMRF Tyre Guide:: All You Need To KnowrhariprsathBelum ada peringkat

- Synchronous AlternatorDokumen228 halamanSynchronous AlternatorSuvra PattanayakBelum ada peringkat

- Ahv-Iv Articulated Hydrostatic VehiclesDokumen3 halamanAhv-Iv Articulated Hydrostatic Vehiclesdewan pratomoBelum ada peringkat

- Test CodeDokumen20 halamanTest Codeantonio vukeBelum ada peringkat

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Manual de Partes XAS 185 JDDokumen50 halamanManual de Partes XAS 185 JDjose luis juarezBelum ada peringkat

- Permanent Monitoring Catalog 20180815 PDFDokumen55 halamanPermanent Monitoring Catalog 20180815 PDFandiyuliusBelum ada peringkat

- Dodge Jeep and Chrysler Obd1 Codes ListDokumen4 halamanDodge Jeep and Chrysler Obd1 Codes ListalbertdBelum ada peringkat

- Yale GP080-120VX-BTGDokumen28 halamanYale GP080-120VX-BTGФедор СумовBelum ada peringkat

- Addressable Optical-Smoke Fire Detector FD7130: Technical DataDokumen1 halamanAddressable Optical-Smoke Fire Detector FD7130: Technical DatamohammadBelum ada peringkat

- 22A Manual TransaxleDokumen14 halaman22A Manual TransaxleRolly CebanesBelum ada peringkat

- Econ Level Gauges For Chemical Applications: Fig. 577: Knee Type Arms of Stainless Steel, Ws - No. 1.4571 (AISI - 316)Dokumen1 halamanEcon Level Gauges For Chemical Applications: Fig. 577: Knee Type Arms of Stainless Steel, Ws - No. 1.4571 (AISI - 316)ChristianGuerreroBelum ada peringkat

- Siemens 15KV RMU - HA 40 2 enDokumen76 halamanSiemens 15KV RMU - HA 40 2 enRamakrishnan PmpBelum ada peringkat

- Varia DorDokumen296 halamanVaria DorGabriel Esteban VenegasBelum ada peringkat

- Manual Balanceadora HunterDokumen19 halamanManual Balanceadora HunterAriel MercochaBelum ada peringkat

- 11.electric Motor DetailDokumen3 halaman11.electric Motor Detailrp63337651Belum ada peringkat

- 9FLYWHEELDokumen17 halaman9FLYWHEELNeil RubsBelum ada peringkat

- Q250 SM Pneumatic Spinning WrenchDokumen11 halamanQ250 SM Pneumatic Spinning WrenchH 8CBelum ada peringkat

- 225-227 WiringDokumen205 halaman225-227 WiringMohamedAl-gamalBelum ada peringkat

- MKW41Z512RMDokumen2.425 halamanMKW41Z512RMКомпания ЕЛАМЕД АО Елатомский приборный заводBelum ada peringkat

- Flex I-O Terminal Base UnitsDokumen16 halamanFlex I-O Terminal Base UnitsFrancisco Mones RuizBelum ada peringkat

- TL5000 RM - En674144Dokumen413 halamanTL5000 RM - En674144Алексей МироновBelum ada peringkat

- Gx160 Parts ManualDokumen11 halamanGx160 Parts Manualabelmonte_geotecniaBelum ada peringkat

- QuestionsDokumen2 halamanQuestionsRaghuBelum ada peringkat

- 33 KV SubstationDokumen19 halaman33 KV Substationraju chandanshiveBelum ada peringkat

- LOGIQ E9 R3.1.3 or Later Removable Trackball Cable Compatibility - IM - 5749846-100 - 2Dokumen2 halamanLOGIQ E9 R3.1.3 or Later Removable Trackball Cable Compatibility - IM - 5749846-100 - 2hakep112Belum ada peringkat

- Fundamentals of Data Engineering: Plan and Build Robust Data SystemsDari EverandFundamentals of Data Engineering: Plan and Build Robust Data SystemsPenilaian: 5 dari 5 bintang5/5 (1)

- ChatGPT Millionaire 2024 - Bot-Driven Side Hustles, Prompt Engineering Shortcut Secrets, and Automated Income Streams that Print Money While You Sleep. The Ultimate Beginner’s Guide for AI BusinessDari EverandChatGPT Millionaire 2024 - Bot-Driven Side Hustles, Prompt Engineering Shortcut Secrets, and Automated Income Streams that Print Money While You Sleep. The Ultimate Beginner’s Guide for AI BusinessBelum ada peringkat

- ChatGPT Side Hustles 2024 - Unlock the Digital Goldmine and Get AI Working for You Fast with More Than 85 Side Hustle Ideas to Boost Passive Income, Create New Cash Flow, and Get Ahead of the CurveDari EverandChatGPT Side Hustles 2024 - Unlock the Digital Goldmine and Get AI Working for You Fast with More Than 85 Side Hustle Ideas to Boost Passive Income, Create New Cash Flow, and Get Ahead of the CurveBelum ada peringkat

- Excel 2023 for Beginners: A Complete Quick Reference Guide from Beginner to Advanced with Simple Tips and Tricks to Master All Essential Fundamentals, Formulas, Functions, Charts, Tools, & ShortcutsDari EverandExcel 2023 for Beginners: A Complete Quick Reference Guide from Beginner to Advanced with Simple Tips and Tricks to Master All Essential Fundamentals, Formulas, Functions, Charts, Tools, & ShortcutsBelum ada peringkat

- Python for Beginners: A Crash Course Guide to Learn Python in 1 WeekDari EverandPython for Beginners: A Crash Course Guide to Learn Python in 1 WeekPenilaian: 4.5 dari 5 bintang4.5/5 (7)

- Kubernetes: The Updated Guide to Master Kubernetes for EveryoneDari EverandKubernetes: The Updated Guide to Master Kubernetes for EveryonePenilaian: 3 dari 5 bintang3/5 (3)