The Optimized Bridge-Leg Power Switch

Diunggah oleh

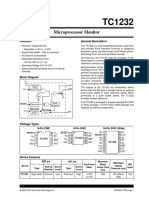

efremofeDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

The Optimized Bridge-Leg Power Switch

Diunggah oleh

efremofeHak Cipta:

Format Tersedia

The Optimized Bridge-Leg Power Switch

K. H. EDELMOSER, H. ERTL , F. C. ZACH Institute of Electrical Drives and Machines Technical University Vienna Gusshausstr. 27-29, A-1040 Wien AUSTRIA

Abstract: - Modern power electronic equipment (inverters, converters, switching mode amplifiers, etc.) mostly are based on switching technique realized by MOSFETs or IGBTs. The requirement of higher output signal quality, reduced size and weight as well as improved power density forces the design engineer to increase the switching frequency into the range of up to several hundred kilohertz, which only can be realized using optimized MOSFET topologies. Nevertheless, all these solutions deal with the disadvantage of the weak body diode of these components. To overcome this drawback, several solutions have been presented in the past. In this paper a novel method is presented which helps to avoid the known disadvantages of the body diode (reverse recovery current, recovery time). The application of an external switching diode (e.g. based on SiC-technology) permits switching frequency increased by a factor of more than two without additional losses. Key-Words: - Switching Stage, Inverter, Switching Mode Amplifier, PWM Stage

1 Introduction

Conventional switching mode PWM inverters and amplifiers today are industrial standard in the field of power conversion applications. The starting point of the presented research is a power switching stage with the goal of very high efficiency and switching speed operating from a 400V DC-link. Driving stages for high dynamic actuators and ultra fast inverters are another field of application. Furthermore, the proposed switching leg can also be used for high quality Class-D amplifiers in the field of audio applications. In this paper a novel circuit topology is proposed which gives an increased switching speed to meet high output voltage quality and improved power density (reduced converter weight and size). By avoiding the current peaks in the diode of the power switch during the reverse recovery process, the efficiency of the enhanced power stage can be kept in an acceptable range.

Fig. 1. Conventional switching stage equivalent circuit

The main drawback of conventional PWM-switching stages (cf. Fig. 1) operating from a 400V DC-link is the wide range of the duty cycle (up to 0..100%) to achieve a good output voltage utilization. A high output signal quality requires a very fine resolution of the PWM signal, while minimizing of all filter elements leads to a high switching frequency. Both demands lead to high PWM carrier frequencies (up to several hundreds of kilohertz) and minimal dead time in the control circuit (down to some ten of ns). Also the switching ripple in the output waveform has to be kept in an acceptable range even with small filters to satisfy the EMC requirements. In the past especially two solutions have been chosen to avoid the disadvantage of the high reverse current peak in the power components [6,7] (cf. Fig. 2). In Fig. 2a an asymmetric separation of the power paths for both current driving directions is shown. Due to the application of selected external high-speed switching diodes (D1, D2) the reverse current peak can be kept in an acceptable range. The solution presented in Fig. 2b uses a slightly modified topology. Here only a single main inductor (LFb) has to be used with the disadvantage of slightly reduced system benefits. The circuit is more difficult to be controlled in this way due to the dependency of the path separation on the leakage inductance [4].

Fig. 2. Improved power switching stages: a.) by path separation, b.) simplified low cost solution

2 The Improved Power Switch

Figure 3 shows the derivation of the proposed novel structure. This solution basically improves the power switch S itself in its switching behavior by forcing the inverse current to go trough an external diode D.

20 DSEI60-06A, 125C - a APT5020, 125C - b DSEI60-06A, 25C - c APT5020, 25C - d d 10 b a c

15 I(D),I(M) [A]

0 0.4

0.5

0.6

0.7 UF[V]

0.8

0.9

Fig. 4.b Current sharing of MOSFET APT5020 & Diode DSEI60-06A (cf. Fig. 3.a): By external active control of SH the conduction voltage of its body diode (operating initially as current separation diode) can be shorted leading to a considerable reduction of the conduction losses. Figure 4a depicts the current sharing between a modern CoolMOS (C3) MOSFET and a SiC-Diode without a pinch-off diode, compared to a system using a standard MOSFET and a fast recovery epitaxial diode (cf. Fig. 4.b.). One can see that the external diode conducts only a minor percentage of the MOSFETs current. With the novel solution given in Fig. 3.b. the current fully commutates into the external fast switching diode D.

c Fig. 3. Improved power switch (derivation): a. external diode connected in parallel to the switch b. standard solution with pinch-off of the MOSFET c. advanced solution with controlled pinch-off Diode The simplest solution (Fig. 3.a.) shows only a theoretical implementation. Due to the normally lower forward voltage of the MOSFETs (S) body diode as compared to the fast external diode D the free-wheeling current in the bridge leg will not commutate to D. To force current commutation, therefore usually an additional (Schottky) diode DS has to be added (cf. Fig. 3b). This well known solution forces the reverse current into the external diode D but shows also the drawback of additional conduction losses of the whole switch due to DS. This drawback, however, can be avoided by using the proposed novel topology depicted in Fig. 3c. Here, an additional (low voltage, m-RDS,ON) switch SH has been added which takes on the function of DS.

20 CDS20060, 125C - a SPW47N60C3, 125C - b CDS20060, 25C - c SPW47N60C3, 25C - d d I(D),I(M) [A] 10 b 5 c 0 0.5 a

3 Simulation Results

To demonstrate the improvements of the topologies given in Figs. 3a-c a circuit level based PSPICE simulation has been performed. Figure 5 depicts the basic simulation test circuitry.

C2 1u

SS ixfh32n50

K K1 K_Linear COUPLING = 1

R1 1

C1 1u

1

L2 1mH

R2 1

1

L1 2 1mH

D2 MUR105

R3 10k

D22 CSD20600

V1 = -15V V2 = +15V TD = 1us TR = 0.1us TF = 0.1us PW = 5us PER = 20us

V1

D1 MBR030

2

R7 0.001

R6 1e6

L3 1mH

1

C3 1u

D3 MUR105

R4 10k

D4 MBR1540

SH ixfk170n10

15

Fig. 5. PSPICE model of the switching stage To clarify the necessity of body diode clamping the circuit given in Fig. 5 is compared to a conventionally operated hard switched half bridge. The stage operates at 10kHz with 50% duty cycle. Fig. 6 shows the excessive current peaks resulting from hard switching based on the poor switching behavior of the MOSFET body diode. The resulting high switching losses lead to a substantial switching frequency limitation.

0.55

0.6

0.65 0.7 UF[V]

0.75

0.8

Fig. 4.a Current sharing of MOSFET SPW47N60C3 & Diode CSD20060 (cf. Fig. 3a).

400 I(S1), I(S2),IL 200 0 -200 0.08 0.06 P(S1) 0.04 IL I(S2) I(S1)

30 20 10 0 -10 500

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 x 10 1

-4

ID(S) VGS(S)

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9 x 10

1

-5

VDS(SS) 0 1 VF(D) 0 -1 1 W 0.5 0 0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9 x 10

1

-5

0.02 0 2 1.5 P(S2) 1 0.5 0 0 0.1 0.2 0.3 0.4 0.5 t[s] 0.6 0.7 0.8 0.9 x 10 1

-4

0 0.1 -3 x 10

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9 x 10

1

-4

0 10-3 0.1 x

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9 x 10

1

-5

W(S) W(SS) W(SH)

dW(D)=90uWs 0.3 0.4 0.5 t[s] 0.6 0.7 0.8 0.9 x 10 1

-5

0.1

0.2

Fig. 8. Switching leg (cf. Fig. 5) with SiC diode SDT12S60 and Schottky clamping diode MBR1530

30 20 10 0 -10 500 VDS(SS) 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 x 10 1

-5

Fig. 6. Half bridge switching leg losses (cf. Fig. 3a): S1 and S2 are operated alternatively, unidirectional load current (PS1 = 32mWs for test condition) To overcome the known drawbacks, a topology according to Fig. 3.b. has been tested where the inverter power stage largely is relieved from switching reverse current peaks. As indicated by Fig. 7 the losses are reduced by a remarkable factor.

100 I(S1), I(S2),IL 50 0 -50 6 4 2 0 6 4 P(S2) 2 0 IL I(S2) I(S1)

W

ID(S) VGS(S)

0 1 VF(D) 0 -1 1 0.5 0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9 x 10

1

-5

0 10-3 0.1 x

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9 x 10

1

-5

W(S) W(SS) W(SH)

dW(D)=18uWs 0.3 0.4 0.5 0.6 0.7 0.8 0.9 x 10 1

-5

0 0.1 -3 x 10

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9 x 10

1

-4

0.1

0.2

P(S1)

Fig. 9. Switching leg (cf. Fig. 5) with SiC diode SDT12S60 and active (MOSFET) clamping Table 1. System loss comparison (SW main switch, Sup. - supplementary element, rel.-relative performance)

Topology:

cf. Fig. 3.a IXFH32N50 cf. Fig. 3.b IXFH32N50 MBR1540 MUR3040 cf. Fig. 3.b IXFH32N50 MBR1540 CSD20060 cf. Fig. 3.c IXFH32N50 IXFK170N10 MUR3040 cf. Fig. 3.c IXFH32N50 IXFK170N10 CSD20060

0 0.1 -4 x 10

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9 x 10

1

-4

W(SW)

4.2mWs

W(Sup.)

W(tot)

4.2mWs 2.45mWs

rel.

100% 58%

2.2mWs 0.1mWs 0.15mWs 0.9mWs 0.8mWs 0.05mWs 0.05mWs 2.37mWs 2.2mWs 0.02mWs 0.15mWs 0.74mWs 0.7mWs 0.02mWs 0.02mWs 16% 56% 22%

0.1

0.2

0.3

0.4

0.5 t[s]

0.6

0.7

0.8

0.9 x 10

1

-4

Fig. 7. Half bridge switching leg losses (cf. Fig. 3b) S1 and S2 operated alternatively, unidirectional load current (PSS = 0.35mWs for test condition) To clarify the improvements of the active clamped body diode the different topologies are analyzed and compared in more detail. Fig. 8 shows the passive solution, while Fig. 9 uses a MOSFET operated as controlled diode. The switches SH and SS are controlled from the same source.

In Table 1 all simulation results are compared. It is clearly shown that the usage of a "passive" clamping method (Fig. 3.b in connection with a conventional highspeed Si-diode D) leads to about half of the original switching losses W(tot). The application of a modern SiC diode gives a further significant improvement. Especially for the latter case the proposed active clamping according to Fig. 3.c opens an interesting additional possibility to minimize the losses of the switching leg.

5 Conclusion

The proposed new solution reduces the disadvantage of hard-switched PWM power stages in conventional inverters based on MOSFET bridge-legs. Due to the separation of the different current paths, each component can be optimized separately. Furthermore, the problem of the weak body diode can be overcome. The result is a stage with significant lowered switching current peaks and improved EMC, especially if modern (e.g., SiC) diodes are used. As demonstrated Tables 3 and 4 the optimization of the power components gives a reduction of the losses of about 30% compared to the worst case of clamped solutions. The usage of modern SiC diodes can show here its full benefit. The proposed topology presented in this paper is a simple and effective solution for medium and high power applications when MOSFETs are used operating at higher switching frequencies. The concept is well-suited for high quality / high speed switching mode amplifiers, high dynamic power inverters, wind-, solar-, and renewable energy systems as well as for aerospace applications, where efficiency and switching speed is a major goal.

4 Measurement Results

To verify the simulation results a laboratory testing circuit has been built up (100kHz switching frequency, duty cycle of 0.5, 400V DC-link voltage, cf. Fig. 10).

Fig. 10. Test circuitry Table 2 Components

SS SH D RK_ RV DF, DK_ CV, CK_ IC APT5014 (140m type) STB140NF75 (7.5m) / MBR1540 DSEI60-06A / CSD20060 10k 1 SB140 1F IX6R11 (one halve)

References:

[1] P.J. Wolfs, A current-sourced DC-DC converter derived via the duality principle from the half-bridge converter, IEEE Transactions on Industrial Electronics, Volume 40, Issue 1, Feb. 1993, pp. 139-144. [2] V.J. Thottuvelil, G.C. Verghese, Analysis and control design of paralleled DC/DC converters with current sharing, IEEE Transactions on Power Electronics, Volume 13, Issue 4, July 1998, pp. 635-644. [3] A.Tuladhar, H. Jin, T. Unger, K. Mauch and Burnaby, B.C: "Control of Parallel Inverters in Distributed AC Power Supply with Consideration of the Line Impedance Effect", Applied Power Electronics Conference APEC '98, pp. 321-329, Anaheim, California. [4] K. H. Edelmoser: "Bi-directional DC-to-DC Converter for Solar Applications", Proceedings of the 6th IEEE International Conference on Circuits, Systems, Communications and Computers CSCC '03, July 7-10, 2003, Corfu, Greece, CD-ROM, ISBN: 960-8052-63-7, 457183.pdf. [5] K. H. Edelmoser: "High Efficiency DC-to-DC Power Inverter", Proceedings of the 6th IEEE International Conference on Circuits, Systems, Communications and Computers CSCC '04, July 12-15, 2004, Athen, Greece, CD-ROM, 487-206.pdf. [6] K. H. Edelmoser, F. A. Himmelsto: High Efficiency Inverter Switching Stage, Proceedings of the ACEMP 2004, May 26-28, 2004, Istanbul, Turkey, pp. 205-209. [7] K. H. Edelmoser: "Inverter Stage With High Small Signal Bandwidth", to be published in Proceedings of the international Power Conversion Conference PCIM'05, Nuremberg, Germany, June 7-9, 2005.

The topologies given in Figs. 3.b and 3.c are compared with two different free wheeling diodes (Si, SiC) and clamping components ("passive" Schottky-diode and "acive" MOSFET). The results are shown in Table 3. Table 3. Loss comparison (open-circuit operation)

Topology 3.b. Si-based 3.b. SiC based 3.c. Si-based 3.c. SiC based IIN 0.53A 0.19A 0.48A 0.15A Rel.: 350% 125% 320% 100%

Table 4. Loss comparison (15A peak load current)

Topology 3.b. Si-based 3.b. SiC based 3.c. Si-based 3.c. SiC based IIN 0.75A 0.25A 0.65A 0.2A Rel.: 375% 125% 325% 100%

In Table 4 the switching leg drives a high-Q resonant tank to determine the losses under load condition (losses of the resonant network are neglected).

Anda mungkin juga menyukai

- High Frequency Power Transformers - Design A High-Frequency Power Transformer Based On Flyback TopologyDokumen6 halamanHigh Frequency Power Transformers - Design A High-Frequency Power Transformer Based On Flyback TopologyShyam Bin JamilBelum ada peringkat

- Äñ Æ÷Éè Æ Ó ©Dokumen6 halamanÄñ Æ÷Éè Æ Ó ©Rachel RowlandBelum ada peringkat

- Fast, Faster, Fastest!: Optimized Diodes For Switching ApplicationsDokumen3 halamanFast, Faster, Fastest!: Optimized Diodes For Switching ApplicationsSrinivasa Rao PottaBelum ada peringkat

- High Efficiency DC-to-AC Power Inverter With Special DC InterfaceDokumen6 halamanHigh Efficiency DC-to-AC Power Inverter With Special DC InterfacestrahinjaBelum ada peringkat

- An-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpDokumen16 halamanAn-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpbmmostefaBelum ada peringkat

- IRF7807VD2: Fetky™ Mosfet / Schottky DiodeDokumen9 halamanIRF7807VD2: Fetky™ Mosfet / Schottky DiodeMartin TorresBelum ada peringkat

- Aggeler SmartEnergyStrategies2008 1Dokumen2 halamanAggeler SmartEnergyStrategies2008 1Akshay SathianBelum ada peringkat

- 325 Lab 10 ReportDokumen12 halaman325 Lab 10 Reportapi-241454978Belum ada peringkat

- Sepic Converter Design and Operation: by Gregory SharpDokumen21 halamanSepic Converter Design and Operation: by Gregory SharpSingam SridharBelum ada peringkat

- Ulta Stepup DC To DC Conveter With Reduced Switch StressDokumen21 halamanUlta Stepup DC To DC Conveter With Reduced Switch StressDRISHYABelum ada peringkat

- The International Conference On Renewable Energies: "ICRE-2010"Dokumen30 halamanThe International Conference On Renewable Energies: "ICRE-2010"M VetriselviBelum ada peringkat

- TDA2040Dokumen14 halamanTDA2040Victoria EsparzaBelum ada peringkat

- New Generalized Multilevel Current-Source PWM Inverter With No-Isolated Switching DevicesDokumen6 halamanNew Generalized Multilevel Current-Source PWM Inverter With No-Isolated Switching DevicesHugo LeónBelum ada peringkat

- AN521 Intoduction To IGBTDokumen10 halamanAN521 Intoduction To IGBTBuelnitaBelum ada peringkat

- Small-Signal Model of A 5kW High-Output Voltage Capacitive-Loaded Series-Parallel Resonant DC-DC ConverterDokumen7 halamanSmall-Signal Model of A 5kW High-Output Voltage Capacitive-Loaded Series-Parallel Resonant DC-DC ConverterAshok KumarBelum ada peringkat

- Lab MAnualDokumen40 halamanLab MAnualHintopiBelum ada peringkat

- Art3 - (S1), Florian Ion, 17-22Dokumen6 halamanArt3 - (S1), Florian Ion, 17-22camiloBelum ada peringkat

- Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial ApplicationsDokumen14 halamanWide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applicationsstrngr06Belum ada peringkat

- Bidirectional DC-DC Converter With Full-Bridge / Push-Pull Circuit For Automobile Electric Power SystemsDokumen5 halamanBidirectional DC-DC Converter With Full-Bridge / Push-Pull Circuit For Automobile Electric Power SystemsPaulo UchihaBelum ada peringkat

- Estimation and Analysis of VFTO in 420kV Gas Insulated SubstationDokumen8 halamanEstimation and Analysis of VFTO in 420kV Gas Insulated SubstationboopelectraBelum ada peringkat

- Three Bit Phase Shifter: MMIC Project Final Report EE525.787 Fall 2007Dokumen16 halamanThree Bit Phase Shifter: MMIC Project Final Report EE525.787 Fall 2007eesharifBelum ada peringkat

- Novel Sngle Phase ZCSDokumen7 halamanNovel Sngle Phase ZCSAntonio Hadade NetoBelum ada peringkat

- Reduction of Power MOSFET Losses in Hard-Switched ConvertersDokumen2 halamanReduction of Power MOSFET Losses in Hard-Switched ConvertersWesley de PaulaBelum ada peringkat

- Compensation Method Peak Current Mode Control Buck AN028 enDokumen13 halamanCompensation Method Peak Current Mode Control Buck AN028 ensadqazwsxBelum ada peringkat

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueDokumen9 halamanHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaBelum ada peringkat

- 3-Phase PFC KolarDokumen7 halaman3-Phase PFC KolarJayant SalianBelum ada peringkat

- A Low-Cost Solar Micro-Inverter With Soft-SwitchingDokumen6 halamanA Low-Cost Solar Micro-Inverter With Soft-Switchingmohamed parvezBelum ada peringkat

- Green-Mode PWM Controller: General Description FeaturesDokumen10 halamanGreen-Mode PWM Controller: General Description FeaturesLuis Luis GarciaBelum ada peringkat

- Eccentric Mass Dynamic Vibration Absorber - Vibrations - 2131Dokumen4 halamanEccentric Mass Dynamic Vibration Absorber - Vibrations - 2131southertontimothy100% (4)

- 35kW Active RectifierDokumen6 halaman35kW Active RectifierndcongBelum ada peringkat

- Design and Fabrication of A 2-Bit ComparatorDokumen23 halamanDesign and Fabrication of A 2-Bit ComparatorKendra KruegerBelum ada peringkat

- Performance Evaluation of The Single-Phase Split-Source Inverter Using An Alternative Dc-Ac ConfigurationDokumen4 halamanPerformance Evaluation of The Single-Phase Split-Source Inverter Using An Alternative Dc-Ac ConfigurationBrightworld ProjectsBelum ada peringkat

- 219 E603Dokumen4 halaman219 E603ptarwatkarBelum ada peringkat

- Choosing Power Switching Devices For SMPS Designs: Mosfets or Igbts?Dokumen6 halamanChoosing Power Switching Devices For SMPS Designs: Mosfets or Igbts?RubenG200Belum ada peringkat

- Voltage-Controlled Oscillator: ... The Analog Plus CompanyDokumen24 halamanVoltage-Controlled Oscillator: ... The Analog Plus CompanyMoltrevBelum ada peringkat

- A Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeDokumen3 halamanA Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeWang TianyangBelum ada peringkat

- Synthesized High-Frequency Thyristor For Dielectric Barrier Discharge Excimer LampsDokumen9 halamanSynthesized High-Frequency Thyristor For Dielectric Barrier Discharge Excimer Lampsdigital2000Belum ada peringkat

- Coping W Poor Dynamic Performance of Super-Junction MOSFET Body Diodes PDFDokumen6 halamanCoping W Poor Dynamic Performance of Super-Junction MOSFET Body Diodes PDFefremofeBelum ada peringkat

- Design and Simulation of RF Energy Extracting Circuits and SystemDokumen28 halamanDesign and Simulation of RF Energy Extracting Circuits and SystemHaresh SinghBelum ada peringkat

- Forward Design 300W STmicroelectronics App NoteDokumen10 halamanForward Design 300W STmicroelectronics App Notecristi7521Belum ada peringkat

- Irg 4 PF 50 WDokumen8 halamanIrg 4 PF 50 WQuickerManBelum ada peringkat

- CMOS Implemented VDTA Based Colpitt OscillatorDokumen4 halamanCMOS Implemented VDTA Based Colpitt OscillatorijsretBelum ada peringkat

- Analysis, Design, and Implementation of A High-Efficiency Full-Wave Rectifier in Standard CMOS TechnologyDokumen11 halamanAnalysis, Design, and Implementation of A High-Efficiency Full-Wave Rectifier in Standard CMOS TechnologymohsinmanzoorBelum ada peringkat

- AC I DC ChokeDokumen4 halamanAC I DC ChokeNedel LabileBelum ada peringkat

- A 32nm Fully Integrated Reconfigurable Switched-Capacitor DC-DC Converter Delivering 0.55W/mm2 at 81% EfficiencyDokumen3 halamanA 32nm Fully Integrated Reconfigurable Switched-Capacitor DC-DC Converter Delivering 0.55W/mm2 at 81% EfficiencyiMiklaeBelum ada peringkat

- Design and Analysis of Low Power Bandgap Voltage ReferenceDokumen8 halamanDesign and Analysis of Low Power Bandgap Voltage ReferencePraveen Kumar ReddyBelum ada peringkat

- A Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InverterDokumen10 halamanA Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InvertererdemsecenBelum ada peringkat

- Three-Phase Rectifier Using A Sepic DC-DC Converter in Continuous Conduction Mode For Power Factor CorrectionDokumen7 halamanThree-Phase Rectifier Using A Sepic DC-DC Converter in Continuous Conduction Mode For Power Factor CorrectionuakragunathanBelum ada peringkat

- 1 Low Vol TechDokumen6 halaman1 Low Vol TechChetan Singh ThakurBelum ada peringkat

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDokumen8 halamanN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical Datameroka2000Belum ada peringkat

- SiC UPS - A Cost Saving SolutionDokumen7 halamanSiC UPS - A Cost Saving Solutionumair_aeBelum ada peringkat

- Computer Aided Design of Snubber Circuit For DC/DC Converter With Sic Power Mosfet DevicesDokumen9 halamanComputer Aided Design of Snubber Circuit For DC/DC Converter With Sic Power Mosfet DevicesrauolBelum ada peringkat

- Design Concept For A Transformerless Solar Inverter: Renewable PowerDokumen3 halamanDesign Concept For A Transformerless Solar Inverter: Renewable Powerzeljkoc21Belum ada peringkat

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)Dari EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)Belum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Power Systems-On-Chip: Practical Aspects of DesignDari EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardBelum ada peringkat

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysDari EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysBelum ada peringkat

- sc120 PDFDokumen116 halamansc120 PDFefremofeBelum ada peringkat

- Mic 29752Dokumen40 halamanMic 29752efremofeBelum ada peringkat

- HP Pdp124pDokumen1 halamanHP Pdp124pefremofe100% (2)

- External PNP Transistor CircuitDokumen5 halamanExternal PNP Transistor Circuitefremofe100% (1)

- TC1232Dokumen24 halamanTC1232efremofeBelum ada peringkat

- TL77xxA SeriesDokumen32 halamanTL77xxA SeriesefremofeBelum ada peringkat

- BSS101Dokumen7 halamanBSS101efremofeBelum ada peringkat

- Coping W Poor Dynamic Performance of Super-Junction MOSFET Body Diodes PDFDokumen6 halamanCoping W Poor Dynamic Performance of Super-Junction MOSFET Body Diodes PDFefremofeBelum ada peringkat

- TRIAC Relay Contact Protection PDFDokumen1 halamanTRIAC Relay Contact Protection PDFefremofeBelum ada peringkat

- TRIAC Relay Contact Protection PDFDokumen1 halamanTRIAC Relay Contact Protection PDFefremofeBelum ada peringkat

- Andlv47011p DDokumen24 halamanAndlv47011p DefremofeBelum ada peringkat

- United States Patent: + T VCC CB (15 (16 H0 JVY/I - J:RDokumen16 halamanUnited States Patent: + T VCC CB (15 (16 H0 JVY/I - J:RefremofeBelum ada peringkat

- Ep 24889895Dokumen7 halamanEp 24889895efremofeBelum ada peringkat

- An1316 Application Note: Evaluation of The New High Voltage Mdmesh Versus Standard MosfetsDokumen9 halamanAn1316 Application Note: Evaluation of The New High Voltage Mdmesh Versus Standard MosfetsefremofeBelum ada peringkat

- Excel 500 600 Installation InstructionsDokumen44 halamanExcel 500 600 Installation InstructionsiwanBelum ada peringkat

- Solar 1Dokumen2 halamanSolar 1RAG6565Belum ada peringkat

- Fundamentals of 3 Phase Power MeasurementsDokumen5 halamanFundamentals of 3 Phase Power MeasurementsADITYAVISHNU 19EE002Belum ada peringkat

- IVRSDokumen18 halamanIVRSRaghvendra RaiBelum ada peringkat

- PCR Ev20mdtDokumen27 halamanPCR Ev20mdtiozsa cristianBelum ada peringkat

- Overvoltage Repair Manual SEPT 2015Dokumen143 halamanOvervoltage Repair Manual SEPT 2015Luis Humberto AguilarBelum ada peringkat

- Arc Flash Training PresentationDokumen106 halamanArc Flash Training Presentationalaa_saq100% (2)

- Eccm in RadarsDokumen89 halamanEccm in Radarsjumaah5234100% (4)

- Pioneer Deh p9300Dokumen6 halamanPioneer Deh p9300Eric SerticBelum ada peringkat

- Single Phase InverterDokumen7 halamanSingle Phase InverterBHALAJI BIRLABelum ada peringkat

- Ee8002 - Dem - Question Bank - Unit 1Dokumen8 halamanEe8002 - Dem - Question Bank - Unit 1DEVIBelum ada peringkat

- Jadual Pembahagian Penilaian Kerja Kursus (PKK) C261-001-3:2020-C03 Electronic Components and Boards Troubleshooting and SupervisionDokumen24 halamanJadual Pembahagian Penilaian Kerja Kursus (PKK) C261-001-3:2020-C03 Electronic Components and Boards Troubleshooting and SupervisionNURAFZABelum ada peringkat

- Product Manual: 1018 - Phidgetinterfacekit 8/8/8Dokumen21 halamanProduct Manual: 1018 - Phidgetinterfacekit 8/8/8Eduardo Piña Martínez100% (1)

- Video Camera Tube (Report)Dokumen12 halamanVideo Camera Tube (Report)Mohammad Rizwan Shaikh100% (1)

- The Barney Oliver Amplifier ManualDokumen34 halamanThe Barney Oliver Amplifier Manualkal elBelum ada peringkat

- Service Manual: NX-340, NX-340 (U)Dokumen42 halamanService Manual: NX-340, NX-340 (U)A&A LABORATORIOBelum ada peringkat

- Scoe - Bee - Unit 3 MCQDokumen5 halamanScoe - Bee - Unit 3 MCQnakul kamatkarBelum ada peringkat

- Service Manual: Compact Hifi Stereo SystemDokumen78 halamanService Manual: Compact Hifi Stereo SystemAngelica GómezBelum ada peringkat

- 3ADW000163R0201 - Technical Guide - e - B PDFDokumen28 halaman3ADW000163R0201 - Technical Guide - e - B PDFAhmed MoustafaBelum ada peringkat

- 6ES72266DA320XB0 Datasheet enDokumen3 halaman6ES72266DA320XB0 Datasheet enLucas Vinícius Costa0% (1)

- Mains S: Mc150-4 Typical InstallationDokumen1 halamanMains S: Mc150-4 Typical InstallationKhay SaadBelum ada peringkat

- Hydraulic System 994K Wheel Loader: Mrk1-UpDokumen14 halamanHydraulic System 994K Wheel Loader: Mrk1-Upfernando7jose7alcantBelum ada peringkat

- Electrochemistry: The Electrochemical Society of JapanDokumen7 halamanElectrochemistry: The Electrochemical Society of Japanayoubmh123Belum ada peringkat

- Colortran 2kW Focusing Scoop Spec Sheet 1995Dokumen2 halamanColortran 2kW Focusing Scoop Spec Sheet 1995Alan MastersBelum ada peringkat

- Kaise SK-20 22 30 ManualDokumen6 halamanKaise SK-20 22 30 ManualAdriano Trigo Lopes50% (2)

- Technical Data Sheet TR24-SRDokumen3 halamanTechnical Data Sheet TR24-SRManh TuanBelum ada peringkat

- User Manual Ex Es SsDokumen150 halamanUser Manual Ex Es Ssmoh300Belum ada peringkat

- FM2819Dokumen2 halamanFM2819Abdellah IbrahimBelum ada peringkat

- Chapter 16 Solutions To Exercises - Circuit Analysis and DesignDokumen71 halamanChapter 16 Solutions To Exercises - Circuit Analysis and Designmtsh212100% (1)

- RURG5060-D Ultrafast DiodeDokumen6 halamanRURG5060-D Ultrafast DiodeRAMESH JUNJUBelum ada peringkat