Lectura 3

Diunggah oleh

Ariel Brigido Lopez VillegasHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Lectura 3

Diunggah oleh

Ariel Brigido Lopez VillegasHak Cipta:

Format Tersedia

INGENIERA EN SISTEMAS COMPUTACIONALES

Lecturas para la materia Ingeniera del Hardware I

INGENIERA EN SISTEMAS COMPUTACIONALES

Unidad 6-7 Anlisis y Sntesis de Circuitos Secuenciales Sncronos

Cronogramas o diagramas de tiempo con biestables. Es uno de los mtodos ms usados para estudiar el comportamiento de las seales de un biestable ( estado interno, salidas, etc. ) y de cualquier circuito secuencial en general. En el se ve en un grfico seal-tiempo como evolucionan las seales al comps de la seal de reloj ( por flanco o nivel ) de una forma muy explcita. Circuitos secuenciales sincrnicos El comportamiento de los circuitos secuenciales se determina de las entradas, las salidas y los estados de los multivibradores (MVB). Ambas entradas y el estado siguiente son una funcin de las entradas y el estado presente. El anlisis de los circuitos secuenciales consiste en obtener una tabla o un diagrama de la secuencia de tiempos de las entradas, salidas y estados internos. Es posible escribir expresiones de Boole que describan el comportamiento de los circuitos secuenciales. Sin embargo, estas expresiones deben incluir la secuencia de tiempos necesaria directa o indirectamente. Un diagrama lgico secuencial se reconoce como un circuito si ste incluye multivibradores. Los MVB pueden ser de cualquier tipo y el diagrama lgico puede o no incluir compuertas combinacionales. Muchos circuitos lgicos contienen MVB, multivibradores monoestables y compuertas lgicas que se conectan para realizar una operacin especfica. Con frecuencia se usa una seal de reloj primaria para ocasionar que los niveles lgicos del circuito pasen a travs de una determinada secuencia de estados. En trminos generales, los circuitos secuenciales se analizan siguiendo el procedimiento que se describe a continuacin: 1. Examinar el diagrama del circuito y buscar estructuras como contadores o registros de corrimiento para su simplificacin. 2. Determinar los niveles lgicos que estn presentes en las entradas de cada multivibrador antes de la incidencia del primer pulso del reloj. 3. Utilizar estos niveles para determinar la forma en que cada multivibrador cambiar en respuesta al primer pulso de reloj. 4. Repetir los pasos 2 y 3 para cada pulso sucesivo de reloj. En la figura 3, se muestra un circuito secuencial utilizando multivibradores J-K con reloj.

INGENIERA EN SISTEMAS COMPUTACIONALES

Anlisis y diseo del Flip Flop Set Reset FF-SR El FF-SR es un dispositivo con dos entradas (Set y Reset) y una variable de estado o salida (Q) capaz de guardar un bit de informacin y funciona como sigue: Si su entrada Set se activa su estado Q se pone en Alto Si su entrada Reset se activa su estado Q se pone en Bajo Si no se activa ni Set ni Reset su estado no cambia Por supuesto, no se permite activar Set y Reset simultneamente. Diagrama de Bloques Aunque el FF-SR posee dos entradas (S y R) y slo una salida (Q), es comn la implementacin que provee adems de Q su versin complementada Q , como se muestra en la figura siguiente

Tabla de Funcionamiento Los fabricantes de los circuitos integrados usan una tabla de funcionamiento para describir la operacin de un circuito de una manera compacta, dicha tabla de funcionamiento no es otra cosa que una tabla de verdad como la usada para circuitos combinacionales, en la cual se ha introducido la informacin del tiempo que en el caso de circuitos secuenciales se vuelve esencial. Enseguida se ilustrar el uso de esta tabla para describir de manera compacta el funcionamiento del FF-SR.

En donde se ha utilizado la siguiente notacin: tn = instante en el cual se aplican las entradas. tn+1 = instante despus que el circuito responde. Qo = salida Q en el instante tn Q+ = salida en el instante tn+1 No es difcil notar que la tabla de funcionamiento es una tabla de verdad con la variable introducida Qo. Diagrama de Estado Clsico La misma informacin especificada por la tabla de funcionamiento puede ser representada de varias maneras diferentes, por ejemplo, el siguiente diagrama es una alternativa grfica que tiene la particularidad de enfatizar el nmero y nombre de los estados del circuito, por ello se le llama diagrama de estado o de estado clsico. As, para el FF-SR:

INGENIERA EN SISTEMAS COMPUTACIONALES

Obsrvese que el diagrama de estado clsico incluye informacin separada de la siguiente manera: - Nombres simblicos dados a los estados (opcional) - Nombres y valores que las variables de estado toman en cada estado. - Nombres y valores de las variables de entrada - Transiciones posibles de un estado a otro y condiciones (sobre las variables de entrada) para producir dicha transicin. - En algunas variantes de diagrama de estado se incluye tambin informacin sobre las variables de salida que no se muestran en el ejemplo, dado que para el FF-SR la variable de estado Q coincide con la variable de salida. Tabla de Excitacin La informacin que guarda el diagrama de estado clsico se puede representar en forma de tabla colocando todas las transiciones posibles de un estado a otro como variables independientes de la tabla y las entradas como variables dependientes, es decir, se genera un rengln de la tabla por cada transicin y anotando los valore s necesarios de las entradas para producir dicha transicin. As, para el ejemplo del FF-SR se obtiene

Tabla de Estado o Tabla Caracterstica Esta es otra manera de organizar en forma de tabla el comportamiento del circuito secuencial, Se trata bsicamente de la misma tabla de funcionamiento ya descrita, salvo que ahora no se introduce ninguna variable de manera que el estado presente (Qo) se trata como si fuera otra entrada. Para el ejemplo del FF-SR tendremos

INGENIERA EN SISTEMAS COMPUTACIONALES

Diagramas de tiempo Los diagramas de tiempo son representaciones grficas de la evolucin de los valores que toman las variables de inters en un circuito digital, de la manera como se podran ver en la pantalla de un osciloscopio. Los diagramas de tiempo no son una herramienta propia de los circuitos secuenciales, ya que estos tambin son tiles para circuitos combinacionales como se ilustr en los captulos anteriores, sin embargo, en el caso de los circuitos secuenciales, la informacin de tiempo es ms crucial por esto los diagramas de tiempo cobran una mayor importancia que en el caso combinacional. Es importante mencionar que estos diagramas no son nicos para un circuito dado, de hecho, pueden poseer informacin incompleta o en ocasiones redundante. As, para el ejemplo del FF-SR un posible diagrama de tiempo sera como en la siguiente figura.

Diseo de un circuito secuencial De acuerdo a las estructuras planteadas para los circuitos secuenciales se puede ver que stos se pueden disear con las herramientas descritas para los circuitos combinacionales, pero tomando en cuenta la retroalimentacin del estado presente. Diseo del Flip Flop Set Reset. Como ejemplo introductorio, consideraremos el problema de disear el Flip Flop-SR. En este caso la salida Q+ depende del estado anterior Qo y de las entradas S y R, es decir,

Q+ = f(Qo, S, R)

Es decir, el diseo lo plantearemos como si se tratara de un circuito combinacionale, pero considerando Qo como si fuera una entrada ms. Esta funcin la podemos plantear por medio de la siguiente tabla de verdad, obtenida de la tabla de estado descrita anteriormente:

INGENIERA EN SISTEMAS COMPUTACIONALES

El Mapa de Karnaugh correspondiente es el siguiente

De donde podemos obtener la expresin siguiente. (Aunque no es un procedimiento comn, la experiencia a demostrdo que se puede obtener una implementacin ms sencilla despreciando las condiciones sin cuidado), entonces Para implementar con slo compuertas NOR negamos dos veces la expresin para obtener Con lo cual podemos implementar el FF-SR con slo dos compuertas NOR, como sigue

Esta implementacin adems tiene la ventaja de que tambin produce la funcin negada Q a la salida de la primera compuerta NOR, de manera que una mejor manera de dibujar este circuito es como se muestra en la siguiente figura

Diagramas de Flujo de Estado Una herramienta alternativa para la representacin, anlisis y diseo de circuitos secuenciales son los Diagramas de Flujo de Estado, tambin conocidos como diagramas ASM (Algorithmic State Machine), los cuales no son ms que una manera diferente de dibujar un diagrama de estado clsico, con smbolos muy similares a los usados en los Diagramas de Flujo usados para especificar programas de computadora como los que se describen a continuacin Smbolos usados en los diagramas ASM Bloque de Estado.- El diagrama deber tener un bloque de estado por cada posible estado presente del circuito.

INGENIERA EN SISTEMAS COMPUTACIONALES

En este bloque se especifica una lista de las salidas que dependen de este estado (Salidas tipo Moore) y los valores que toman en dicho estado. Tambin se deber especificar a un lado del bloque los valores que toman las variables de estado.

Bloque de decisin.- Los bloques de decisin son los que establecen las condiciones para que ocurra un cambio de estado, es decir, definen las trayectorias posibles y las condiciones para pasar de un estado a otro. Dentro del bloque se deber especificar la expresin lgica (en trminos de las entradas) que decide cual es la trayectoria a seguir y en cada salida del bloque se deber especificar el valor de la expresin para seguir por dicha salida.

Bloque de Salida.- Este bloque siempre viene de un bloque de decisin para especificar salidas cuyo valor depende del estado y de las entradas de dicho bloque de decisin (Salidas tipo Mealy). Se especifica dentro de este bloque la lista de salidas que dependen del estado y de las entradas as como los valores que toman dichas salidas.

Ejemplo Para dibujar el diagrama de flujo de estado de un circuito secuencial es importante hacer una lista preliminar que contenga la siguiente informacin. (Los valores se especifican entre parntesis para el caso del FF-SR). - Nmero de Estados (2) - Nmero de variables de estado (1) - Nombres de las variables de Estado (Q), Entradas (S,R) y Salidas (Q) y tipo (Moore). Obsrvese que en el caso del FF-SR la nica salida corresponde a la nica variable de estado, por lo tanto es de tipo Moore. El nmero de estados indica directamente el nmero de bloques de estado, de manera que el diagrama queda como sigue 7

INGENIERA EN SISTEMAS COMPUTACIONALES

CONTADORES Los contadores son circuitos secuenciales capaces de recorrer una secuencia previamente especificada de estados. Reciben un tren de impulsos y responden con una sucesin de estados correspondientes a la representacin en binario del nmero de impulsos recibidos desde que se inici el ciclo. Tipos de contadores Asncronos.- Los flip flops que componen el contador no cambian de estado exactamente al mismo tiempo, dado que no comparten el mismo impulso de reloj. Sncronos.- Hay una relacin temporal fija entre s. Todos los flip flops que componen el contador reciben en el mismo instante la seal de reloj y por lo tanto cambian (si han de cambiar) en el mismo instante. Contadores asncronos Compuestos por Flip flops JK con J=K=1 de forma que la entrada de reloj entra en el primer FF (bit de menor peso) y el reloj del resto de los FF es la salida Q del anterior. Esto provoca el sentido asncrono del contador, ya que cuando entra el impulso de reloj al primer FF este empieza a cambiar, pero el siguiente no cambiar hasta que no lo haya hecho el anterior. Este efecto provoca una reaccin que se va aadiendo de FF a FF y por lo tanto el tiempo de cambio de un estado al otro puede ser el resultado de acumular los tiempos de transicin del nmero de FF que intervienen en dicho cambio.

INGENIERA EN SISTEMAS COMPUTACIONALES

Contadores descendentes Para configurar contadores con sentido descendente hay dos posibilidades: 1. Tomar un contador ascendente y tomar las salidas de la Q. 2. Tomar la entrada de reloj de cada FF de la salida Q del FF anterior.

1.- Para x=1 seleccionamos la entrada de reloj de cada FF de la salida Q del FF anterior, por lo tanto se comporta como un contador ascendente. 2.- Para x=0 seleccionamos la entrada de reloj de cada FF de la salida Q del FF anterior, por lo tanto se comporta como un contador descendente. 9

INGENIERA EN SISTEMAS COMPUTACIONALES

Contadores de diferentes bases y divisores de frecuencia (MOD) Hay dos formas de implementar contadores binarios de diferentes bases: 1. Reinicializar todo el contador cuando el nmero binario al que llega contando es el de la base que se quiere conseguir. Ello provoca la puesta a cero del contador y el inicio de un nuevo ciclo. 2. Poner a 1 todas los FF del contador mediante el Preset cuando se llega al nmero de la base al que se quiere llegar menos 1 (base-1). Ello provoca que el contador llega al mximo de su capacidad de cuenta y de esta manera con el siguiente impulso de reloj se provoca su puesta a 0 y consiguiente inicio de ciclo de cuenta. La implementacin de divisores de frecuencia bsicamente consiste en implementar contadores cuya base ser el nmero por el que se quiere dividir la frecuencia (contadores MOD). Contadores sncronos Inconvenientes de los contadores asncronos 1.- La frecuencia mxima de trabajo depende de la suma de los retardos que introducen los biestables que lo componen. 2.- Los estados estables no se alcanzan siempre al mismo tiempo. Estos inconvenientes se solucionan utilizando contadores sncronos, en los cuales el reloj de entrada se conecta a la entrada de reloj de todas los FF, de forma que la transicin de ellas se produce en funcin de los valores que se introduzcan en sus entradas de datos. De esta manera cuando el contador adquiere un estado (estable) posiciona las entradas de los FF antes de que se produzca la entrada del siguiente ciclo de reloj. Cuando esta aparezca todas, los FF comenzarn simultneamente el proceso de cambio (si es que se ha de producir segn los valores de sus entradas). A pesar de lo indicado se puede configurar un contador binario natural sncrono de una manera un tanto estandar. Se pueden implementar con FF JK con las dos entradas unidas a 1 (FF T) de forma que los relojes de todos los FF estn unidos entre s y a la seal del reloj de entrada. En el caso de un contador ascendente: cada una de las entradas JK de cada FF a una puerta AND de todas las salidas Q de los FF de pesos inferiores. En el caso de un contador descendente: cada una de las entradas JK de cada FF a unapuerta AND de todas las salidas Q de los FF de pesos inferior.

REGISTROS DE DESPLAZAMIENTO 10

INGENIERA EN SISTEMAS COMPUTACIONALES

Un registro es circuito digital con dos funciones bsicas: Almacenamiento de datos. Movimiento de datos. Con tales funciones una cuestin elemental es el modo de introducir y el modo de sacar dicha informacin. Teniendo en cuenta que hay dos maneras de manipular los datos: serie/paralelo; ello da lugar a tener diferentes configuraciones de registros en funcin de la entrada y la salida de dichos datos: Entrada serie / Salida serie. Entrada serie / Salida paralelo. Entrada paralelo / Salida serie. Entrada paralelo / Salida paralelo.

La implementacin de los registros parte de dos premisas elementales: 1) Estarn compuestos por tantos FF D como bits queramos almacenar o manipular. 2) Segn el modo de carga o desplazamiento: a) En el caso de una entrada paralelo, cada bit de entrada que queramos introducir se deber conectar a cada una de las entradas de cada FF del registro. b) En el caso de una entrada serie o un desplazamiento, cada entrada de cada FF deber ir conectada a la salida del FF inmediatamente inferior y de la cual deber recoger el bit que se quiere desplazar.

La figura anterior muestra un registro de desplazamiento con entrada serie y salida paralela 11

INGENIERA EN SISTEMAS COMPUTACIONALES

Funcionamiento de un registro de desplazamiento

La parte remarcada de la figura anterior indica el paso del registro de bit a bit, notese el desplazamiento que se va dando segn se origine un pulso a la entrada del reloj.

12

INGENIERA EN SISTEMAS COMPUTACIONALES

13

Anda mungkin juga menyukai

- Listas de CotejoDokumen5 halamanListas de CotejoAriel Brigido Lopez VillegasBelum ada peringkat

- Contrato de ComodatoDokumen3 halamanContrato de ComodatoAriel Brigido Lopez VillegasBelum ada peringkat

- OctalDokumen8 halamanOctalDiana GuamanBelum ada peringkat

- Lectura Complementaria Unidad 1Dokumen10 halamanLectura Complementaria Unidad 1Ariel Brigido Lopez VillegasBelum ada peringkat

- Lectura 2Dokumen13 halamanLectura 2Ariel Brigido Lopez VillegasBelum ada peringkat

- Seguimiento San PedroDokumen2 halamanSeguimiento San PedroAriel Brigido Lopez VillegasBelum ada peringkat

- Reproductor multimedia con disco duro manualDokumen55 halamanReproductor multimedia con disco duro manualAntonio EspinosaBelum ada peringkat

- Caso de Aplicacion VSM DiapoDokumen2 halamanCaso de Aplicacion VSM DiapoEnriique MartinBelum ada peringkat

- Manual Uso HeliosDokumen53 halamanManual Uso HeliosCesar A. Zarate Lozano0% (1)

- Osciladores de RFDokumen7 halamanOsciladores de RFW Omar Espejo RuedaBelum ada peringkat

- Control DigitalDokumen48 halamanControl DigitalEsgar Ivan Paucar JaboBelum ada peringkat

- Investigacion - Amplificadores Operacionales Con RetroalimentaciónDokumen10 halamanInvestigacion - Amplificadores Operacionales Con RetroalimentaciónMiguel Angel Hernandez CruzBelum ada peringkat

- Sistema de Incendio Eco FuturoDokumen6 halamanSistema de Incendio Eco FuturoPablo José Delgado CarrasquelBelum ada peringkat

- Práctica 5Dokumen6 halamanPráctica 5Andres OlmedoBelum ada peringkat

- Simbología - Luz Daniela López CadenaDokumen5 halamanSimbología - Luz Daniela López Cadenaluz daniela lopezBelum ada peringkat

- Guía Básica de Sistemas de Audio Por Radiofrecuencia - Javier G. IsequillaDokumen89 halamanGuía Básica de Sistemas de Audio Por Radiofrecuencia - Javier G. IsequillaAntonio Rodrigues LamarcaProAudioBelum ada peringkat

- Examen Teoric Tipo ARedes Convergentes Tercer CorteDokumen1 halamanExamen Teoric Tipo ARedes Convergentes Tercer Corteruben perezBelum ada peringkat

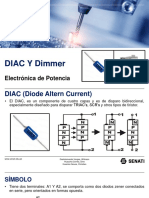

- Diac y DimmerDokumen13 halamanDiac y DimmerUlt DincyclistBelum ada peringkat

- Control de ErrantesDokumen39 halamanControl de Errantesrgaliano.rgBelum ada peringkat

- Microprocesadores (Silabo)Dokumen6 halamanMicroprocesadores (Silabo)Maldito SudacaBelum ada peringkat

- Previo Exo. 4 Ley de Tensiones de KirchhoffDokumen3 halamanPrevio Exo. 4 Ley de Tensiones de KirchhoffAnthony HuacachiBelum ada peringkat

- Cotiza 021 Dominus S.A.C.Dokumen4 halamanCotiza 021 Dominus S.A.C.Darwin JucBelum ada peringkat

- Convertidores analógico a digital: muestreo, cuantificación y codificaciónDokumen38 halamanConvertidores analógico a digital: muestreo, cuantificación y codificaciónDai'skar Romero100% (1)

- Practica 5 2-2021 ADokumen2 halamanPractica 5 2-2021 AMauricio PérezBelum ada peringkat

- Aplicaciones de Los Diodos y TransistoresDokumen5 halamanAplicaciones de Los Diodos y Transistoresjoel mosqueraBelum ada peringkat

- Circuitos de Interconexión Entre Dos Arduinos Con Adaptadores 485 2Dokumen20 halamanCircuitos de Interconexión Entre Dos Arduinos Con Adaptadores 485 2Frank LeonBelum ada peringkat

- ATX2Dokumen6 halamanATX2Falconx Blacks LordBelum ada peringkat

- Lab #3 Circuitos DigitalesDokumen4 halamanLab #3 Circuitos Digitalessergio perezBelum ada peringkat

- ABRITES - Commander - For - Nissan - Manual (1) .En - EsDokumen19 halamanABRITES - Commander - For - Nissan - Manual (1) .En - EsJose VeraBelum ada peringkat

- Tercera Entrega - Internet de Las CosasDokumen2 halamanTercera Entrega - Internet de Las CosasFernando Rodríguez Caro100% (3)

- 02 - Redes-Lan-Man-Wan-SanDokumen12 halaman02 - Redes-Lan-Man-Wan-SanArely Pierina Lizarraga OblitasBelum ada peringkat

- Expo Redes Industriales.Dokumen29 halamanExpo Redes Industriales.alfonsoBelum ada peringkat

- Protección de sistemas eléctricos de potencia y relés de sobrecorrienteDokumen55 halamanProtección de sistemas eléctricos de potencia y relés de sobrecorrienteFer LopezBelum ada peringkat

- Hardware - Wikipedia, La Enciclopedia LibreDokumen10 halamanHardware - Wikipedia, La Enciclopedia LibreKaaBelum ada peringkat

- Informe de Ensamblaje de PCDokumen6 halamanInforme de Ensamblaje de PCElvis Tarazona FloresBelum ada peringkat

- Gpi-Pr-232 Cambio de Transformado 1000kva PointerDokumen9 halamanGpi-Pr-232 Cambio de Transformado 1000kva PointerStephanie AnguloBelum ada peringkat