Tema 7

Diunggah oleh

Antonio TorresJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Tema 7

Diunggah oleh

Antonio TorresHak Cipta:

Format Tersedia

TECNOLOGA DE COMPUTADORES.

CURSO 2007/08 Inocente Snchez Ciudad

TEMA 7: SISTEMAS SECUENCIALES SNCRONOS.

7.1. Autmata de Estados Finitos.

Por definicin, un Autmata de Estados Finitos es una quntupla compuesta por 5 elementos: A = [E, Z, Q, , ] :Q x E-->Z :Q x E-->Q

donde E es un conjunto de entradas, Z es un conjunto de salidas, Q es un conjunto de estados, es una funcin de salida y es una funcin de transicin de estados. Un sistema secuencial es aqul cuyas salidas dependen de las entradas actuales (como los combinacionales), y, adems, de las entradas anteriores. Las entradas anteriores crean una situacin que se llama estado, con lo que un circuito secuencial ser tal que: 1) Sus salidas dependen de sus entradas y sus estados. 2) Los estados, a su vez dependen de las entradas y de los estados anteriores. Estado: situacin en la que est una cosa, en relacin con los cambios que influyen en ella.

7.2. Diagramas de estado.

Son unos diagramas que representan el cambio de estado en funcin del estado previo y de las entradas. La Figura representa el diagrama de transicin de estados y salidas, independientemente de cmo se codifiquen. En realidad, representa el comportamiento de un autmata finito. E={0,1} Z={0,1} Q={q0, q1, q2, q3} E/S

0/0

1/0 0/0

q0

1/0 1/1 1/0

q3

0/0

q1

0/1

q2

Tema 7: Sistemas Secuenciales Sncronos

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Tabla de transiciones de estados. ESTADO ACTUAL: Q(t) q0 q0 q1 q1 q2 q2 q3 q3 ENTRADA 0 1 0 1 0 1 0 1 PRXIMO ESTADO: Q(t+1) q0 q1 q2 q3 q3 q1 q3 q0 SALIDA 0 0 1 1 0 0 0 0

7.3. Autmatas de Moore y Mealy.

En el diagrama anterior, cada par (entrada, estado) puede generar cualquier salida y cualquier transicin a un estado determinado. A este tipo de autmata se le llama Autmata de Mealy. Las salidas estn asociadas con las transiciones.

Entradas COMBINACIONAL

Salidas

MEMORIA

Autmata de Mealy Por el contrario, hay autmatas en los que a cada estado le corresponde de forma inequvoca una salida determinada, es decir, estar en el estado qi supone que la salida ha salida una cierta Si. No puede ocurrir que alcanzando el estado qi la salida haya sido distinta de Si. A este autmata que tiene asociada una salida a un estado se les llama Autmata de Moore. En los autmatas de Moore no es necesario escribir la salida en la flecha de la transicin, puesto que la misma ser la que tenga asociada el estado al que se llega.

Entradas COMBINACIONAL MEMORIA

COMBINACIONAL

Salidas

Autmata de Moore Dado un autmata de Mealy siempre se puede encontrar un autmata de Moore equivalente. Veamos un ejemplo:

Tema 7: Sistemas Secuenciales Sncronos

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

a/1 b/0 a/0

q3

b/1

a/0

b/0

q1

q2

Autmata de Mealy. Las salidas estn asociadas a las transiciones. Al estado q1 se llega desde el estado q3 con entrada b o desde el propio q1 con entrada a, pero siempre dando salida 0. Podemos asociar al estado q1 la salida 0, es decir, si el estado es q1 la salida ha sido 0. No ocurre lo mismo con q2. Al estado q2 se llega desde el estado q1 con entrada b dando salida 1 o bien desde el propio q2 con entrada b dando salida 0. El hecho de estar en q2 no presupone conocer cul ha sido la salida. Lo mismo ocurre con q3. La forma de convertir un autmata de Mealy en uno de Moore es desdoblar aquellos estados que no tienen asociada una salida en tantos estados como salidas distintas tengan y de esta forma cada uno de los nuevos estados tiene asociada de forma inequvoca una salida. Para nuestro ejemplo quedara:

q3/1

b b

q2/0

a b

q3/0

b

q1/0

q2/1

Autmata de Moore. Las salidas estn asociadas a los estados.

Tema 7: Sistemas Secuenciales Sncronos

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

7.4. Anlisis de Sistemas Secuenciales Sncronos.

Consiste en ver cmo responde en funcin de sus entradas y estados actuales. Ejemplo.

La salida z(t) se puede expresar como

Z (t ) = X + Q2 (t ) + Q1 (t )

Las entradas de los biestables se pueden poner como:

J2 = X

J 1 = X + Q2 (t )Q1 (t )

K 2 = Q2 (t )

K1 = X

Los valores de Prximo estado y Salida se pueden obtener aplicando las ecuaciones booleanas o bien mirando para cada caso qu saldr del biestable en funcin de las entradas actuales y del estado actual, para lo cual hay que conocer cmo funciona el biestable.

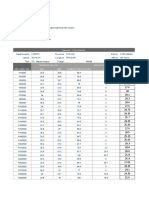

Entrada X 0 0 0 0 1 1 1 1

Estado actual Q2(t) Q1(t) 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1

Biestable 2 J2 K2 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1

Biestable 1 J1 K1 1 1 1 1 1 1 1 1 0 0 0 0 1 0 0 0

Prximo estado Q2(t+1) Q1(t+1) 0 1 0 0 0 1 0 0 1 0 1 1 0 1 0 1

Salida Z 0 0 0 0 0 1 0 0

Veamos un ejemplo de cronograma suponiendo que inicialmente los dos biestables estn a 0 y conociendo la evolucin temporal o cronograma completo de la seal de entrada X. Se ha supuesto que la entrada X est sincronizada con el reloj, pero con un desfase de medio perodo para que en el instante del flanco del reloj, la seal de entrada est estabilizada. Para obtener el cronograma se procede de la siguiente manera: 1) Conocida la entrada y el valor de los biestables (el primero de ellos debe ser conocido de antemano como dato inicial), se determinan los valores de las entradas a los biestables y la salida. 2) Conocidas las entradas a los biestables en el momento del flanco de subida, se calculan los prximos estados de todos los biestables, que junto con la prxima entrada permite repetir de forma cclica el punto anterior.

Tema 7: Sistemas Secuenciales Sncronos

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Como se observa en la Figura, en un autmata de Mealy las salidas pueden cambiar antes de que llegue el flanco activo del reloj si cambian las entradas, ya que la salida depende de la entrada directamente. Adems, las salidas y los estados cambian o pueden cambiar en el flanco activo del reloj. Por el contrario, en un autmata de Moore, tanto los estados como las salidas slo cambian cuando llega el flanco correspondiente del reloj.

7.5. Sntesis o Diseo de Sistemas Secuenciales Sncronos.

Si no se dice lo contrario, supondremos un autmata de Mealy con biestables sncronos por flanco. 1. Paso de las especificaciones verbales a diagrama de estados. Lo primero que hay que hacer es "traducir" el enunciado a diagrama de estados, es decir, distinguir estado, numerarlos, identificar entradas, determinar salidas, y en definitiva expresar el diagrama de estado de forma grfica. 2. Construccin de la tabla de estados y de excitacin. Se coloca en una tabla la entrada, el estado inicial, el prximo estado y la salida, y se pone la tabla de excitacin del biestable que resuelva el problema. 3. Minimizacin de las funciones de excitacin. Utilizando las tcnicas habituales: mapas de Karnaugh, mdulos combinacionales, etc... 4. Implementacin del circuito. Se construye el circuito.

Tema 7: Sistemas Secuenciales Sncronos

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

7.6. Ejemplos de diseo de sistemas secuenciales sncronos.

1. Diseo de un contador sncrono de 2 bits, ascendente. Autmata de Moore. Las salidas del circuito coinciden con las salidas de los biestables.

1. Paso de las especificaciones verbales a diagrama de estados. Definicin de Estados. q0: Cuenta 0. q1: Cuenta 1. q2: Cuenta 2. q3: Cuenta 3.

Diagrama de estados

q0 q3 q2

Codificacin de estados

q1

Q1 q0 q1 q2 q3 0 0 1 1

Q0 0 1 0 1

2. Construccin de la tabla de estados y de excitacin. ESTADO ACTUAL 0 0 1 0 0 1 0 1 ESTADO PRXIMO BIESTABLE 1 BIESTABLE 0

Q1(t) Q0(t) Q1(t+1)

0 1 1 0

Q0(t+1)

1 0 1 0

J1

0 1 X X

K1

X X 0 1

J0

1 X 1 X

K0

X 1 X 1

3. Minimizacin de las funciones de excitacin. Haciendo los MK sale:

J 1 = Q0

J0 = 1

K 1 = Q0

K0 = 1

Tema 7: Sistemas Secuenciales Sncronos

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

4. Implementacin del circuito.

J1 CK1 K1

Q1

00110

S1

/Q1

J0 CK0

Q0

01010

S0

1 CUENTA

2. Sumador serie.

K0

/Q0

Recibe los dos sumandos en serie, de menor a mayor peso, bit a bit en cada perodo de reloj. Al mismo tiempo genera las sumas parciales y los acarreos. La necesidad de memoria est en recordar si para la etapa siguiente hay o no acarreo. Lo mismo que cuando sumamos mentalmente recordamos si "nos llevamos una" o no, el estado que hay que recordar es si hay o no acarreo. Por tanto en circuito secuencial que implementa un sumador de 4 bits debe tener una tabla de verdad del siguiente tipo:

ENTRADAS Y ESTADO ACTUAL

SALIDA Y ESTADO PRXIMO

EXCITACIN BIESTABLE

E1

0 0 0 0 1 1 1 1

E2

0 0 1 1 0 0 1 1

Q0(t)

0 1 0 1 0 1 0 1

SUMA

0 1 1 0 1 0 0 1

Q0(t+1)

0 0 0 1 0 1 1 1

J0

0 X 0 X 0 X 1 X

K0

X 1 X 0 X 0 X 0

El circuito que resuelve esta situacin ser el siguiente, cuyas ecuaciones son:

J 0 = E1E 2

K 0 = E1E 2 = E1 + E 2

Q0 (t + 1) = E1E 2 + Q0 (t )( E1 + E 2) = J 0 + Q0 (t )K 0 SUMA = Q0 (t ) E1 E 2

Tema 7: Sistemas Secuenciales Sncronos

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

E1 SUMA E2

RELOJ

Ejemplo: sumar 22 + 11 E1: 000010110 E2: 000001011 SUMA: 000100001 Evolucin temporal del sumador serie de 1 bit

0 1

Inicial

t=0

1

ESTADO: SIN ACARREO

RELOJ 1 1 RELOJ 1 0 RELOJ

t=1

0

ESTADO: SIN ACARREO

Inicial

t=2

0

ESTADO: CON ACARREO

0 1 RELOJ

Inicial

t=3

0

ESTADO: CON ACARREO

1 0 RELOJ

Inicial

t=4

0

ESTADO: CON ACARREO

Tema 7: Sistemas Secuenciales Sncronos

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

3. Reconocedores de secuencias. Supongamos que se quiere detectar la subsecuencia 1101 dentro de una secuencia de bits de longitud indefinida. Vamos a hacerlo usando el diseo de circuitos secuenciales. Definicin de estados q0: estado inicial. Resto de estados. q1: se ha recibido un 1 en el ltimo bit. q2: se han recibidos dos 1's en los dos ltimos bits. q3: se ha recibido un 0 en el ltimo bit despus de que se hayan recibidos dos 1's en los dos anteriores bits.

Codificacin

Q1 q0: q1: q2: q3: 0 0 1 1

Q0 0 1 0 1

0/0 0/0

q0

1/0 0/0 1/0

q3

0/0

Tablas de transicin y excitacin

1/1

q1

1/0

q2

K1

X X 0 1 X X 0 1

E

0 0 0 0 1 1 1 1

Q1(t) Q0(t) Q1(t+1) Q0(t+1) J1

0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 1 0 0 1 1 0 0 0 1 0 1 0 0 0 0 0 X X 0 1 X X

J0

0 X 1 X 1 X 0 X

K0

X 1 X 1 X 1 X 1

S

0 0 0 0 0 0 0 1

Simplificacin

J 1 = E Q0 K 1 = Q0 J 0 = E Q1 K0 = 1 S = E Q1 Q0

Tema 7: Sistemas Secuenciales Sncronos

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

4. Generador de paridad par de 3 bits. Se trata de disear un generador secuencial de paridad par de cadenas de 3 bits serie. Por ejemplo, si la secuencia de entrada es X = 000110101... la salida deber ser Z = 0100010... Utilizar para ello biestables tipo D. 1. Paso de las especificaciones verbales al diagrama de estados Como puede apreciarse, para poder calcular cada paridad de una serie de tres bits es necesario conservar los dos ltimos bits, ms el bit que se introduce en la entrada. Es necesario por lo tanto que el circuito secuencial sea capaz de recordar cules fueron estos dos ltimos bits. De esta manera el nmero de estados diferentes ser 4, correspondientes a las cuatro posibles combinaciones de 2 bits (00, 01, 10 y 11). Una vez determinado el nmero de estados debe dibujarse el diagrama en el que se reflejan dos cosas: 1. La funcin de transicin, que permite el clculo del siguiente estado a partir del estado actual y la entrada, representada por las flechas que unen los diferentes estados. 2. La funcin de salida. Para cada transicin se indicar cul ser la salida del circuito. En nuestro caso el diagrama resultante ser el de la figura adjunta, en la que los diferentes estados q0 a q3 corresponden a la descripcin de la tabla adjunta. Estado q0 q1 q2 q3

Definicin de estados

Dos ltimos bits = 00 Dos ltimos bits = 01 0 penltimo 1 ltimo Dos ltimos bits = 10 1 penltimo 0 ltimo Dos ltimos bits = 11 0/0 q0 1/1 0/1 1/0 q3 1/0 0/0 q2 0/1 q1 1/1

Supongamos por ejemplo que nos hallamos en el estado q1, lo que significa que despus del ltimo clculo de paridad tenemos almacenada la secuencia 01. Como puede apreciarse en el diagrama, un 1 en la entrada dara lugar a la combinacin 1 + 10, cuya paridad es par. La salida por lo tanto ser 0, y el siguiente estado q3, puesto que ahora los dos ltimos bits sern 11. 2. Construccin de la tabla de estados Tomando el diagrama de estados de la figura anterior debe generarse la tabla de estados, en la que a partir de las entradas y el estado actual se obtendr el siguiente estado y la salida.

Tema 7: Sistemas Secuenciales Sncronos

10

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

x 0 0 0 0 1 1 1 1

Q1(t) 0 0 1 1 0 0 1 1

Q0(t) 0 1 0 1 0 1 0 1

Q1(t+1) 0 1 0 1 0 1 0 1

Q0(t+1) 0 0 0 0 1 1 1 1

z 0 1 1 0 1 0 0 1

Como se observa hay dos columnas diferentes dentro de las funciones a implementar. La primera (Q1(t+1) Q0(t+1)) indicara cul debe ser la funcin de transicin para el clculo del nuevo estado. La segunda (es la funcin de salida). Sin embargo, puesto que no se pueden manipular directamente q1 y q0, sino las entradas D1 y D0 de los biestables, es necesario calcular qu valores hay que colocar en las entradas D para obtener los estados deseados. Dicho de otra manera si estamos en el estado Q1(t) y quiero pasar a Q1(t+1), qu debemos colocar como entrada D en el biestable de la figura D Q

Q Para ello es necesario disponer de la tabla de excitacin del biestable (del D en este caso): Q(t) 0 0 1 1 Q(t+1) 0 1 0 1 D 0 1 0 1

A partir de esta tabla, conociendo Q(t) y Q(t+1) para ambos bits, podemos calcular los valores de entrada a los biestables D1 y D0. La nueva tabla quedar por tanto de la siguiente manera. x Q1(t) 0 0 1 1 0 0 1 1 Q0(t) Q1(t+1) Q0(t+1) 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 1 1 1 1 z D1 D0 0 1 0 1 0 1 0 1 0 0 0 0 1 1 1 1

0 0 0 0 1 1 1 1

0 1 1 0 1 0 0 1

3. Minimizacin de las funciones e implementacin del circuito Simplificando por Karnaugh obtendremos las funciones de entrada a los biestables (D1 y D0) para el clculo del nuevo estado, y la funcin de salida Z, implementadas en la figura.

D1 = Q0

D0 = x

Z = x Q1 Q0

Tema 7: Sistemas Secuenciales Sncronos

11

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

5. Contador especfico. A veces el diseo de un secuencia se reduce a disear un contador cuya secuencia de cuenta sea una especfica, que es funcin del propio enunciado. Veamos un ejemplo. Se dispone de 4 barras luminosas dispuestas y numeradas segn la figura. Se quiere disear una secuencia cclica de iluminacin controlada por una seal de reloj de frecuencia baja. La secuencia requerida es cclica y es la que se representa en la figura. Implementar un circuito digital que consiga realizar la secuencia descrita y que comience con todos los segmentos apagados, teniendo en cuenta que la iluminacin de un segmento se logra proporcionando un nivel lgico 1. Disponer de biestables tipo T, decodificador/es para implementar las entradas a los biestables, y puertas OR necesarias. Respetar la numeracin de los luminosos a la hora de codificar los estados.

0 3 2 1 Encendido apagado

1. Paso de las especificaciones verbales al diagrama de estados Como muestra la figura del enunciado, pueden presentarse 8 configuraciones diferentes en las barras luminosas, por lo que el nmero de estados necesario ser tambin 8, una para cada configuracin:

q0

q1

q3

q7

q4

q12

q13

q15

Como son 8 estados, podramos asignar un cdigo consecutivo del 000 al 111 y utilizar 3 bits para codificar cada uno de ellos. Sin embargo, como se ver en el circuito resultante puede resultar ms sencillo utilizar un biestable para controlar el encendido o apagado de cada barra. De esta manera utilizaramos 4 biestables. Aunque existen 16 posibles combinaciones, en realidad

Tema 7: Sistemas Secuenciales Sncronos

12

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

slo vamos a utilizar 8. El resto no se presentar nunca, por lo que pueden utilizarse como condiciones de no importa para simplificar las funciones resultantes. Vamos a realizar la codificacin de los estados, por lo tanto, de la siguiente manera. Tal y como muestra la figura, el biestable 0 controlar el encendido de la barra 0, el biestable 1 de la barra 1, y as sucesivamente.

Q0 0 Q3 3 2 1 Q1

Q2

De esta manera, por ejemplo, la primera configuracin corresponder a todos los bits a 0 (0000). La segunda, al caso en que Q0(t) sea 1 y el resto 0 (0001), la tercera a Q0(t) y Q1(t) a 1 y el resto a 0 (0011), etc. Si la codificacin se asigna de esta manera puede verse cmo las seales de activacin de las barras coinciden exactamente con los valores almacenados en los biestables (mquina de Moore). De otra manera habramos tenido que calcular una funcin de salida para cada barra, convirtiendo la codificacin de los tres biestables usados en las 4 lneas de salida de activacin de las luces correspondientes. As, la codificacin de los estados ser la siguiente:

Secuencia especfica de cuenta 0 1 3 7 15 13 12 4

2. Construccin de la tabla de estados

Codificacin y activacin de luces 0000 0001 0011 0111 1111 1101 1100 0100

Tomando el diagrama de estados de la figura anterior debe generarse la tabla de estados, en la que a partir de las entradas y el estado actual se obtendr el siguiente estado, y en la que a partir de ambos, y con ayuda de la tabla de excitacin se calcularn las entradas a los biestables (T en este caso).

Tema 7: Sistemas Secuenciales Sncronos

13

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Cuenta Q3(t) Q2(t) Q1(t) Q0(t) Q3(t+1) Q2(t+1) Q1(t+1) Q0(t+1) 0 1 3 4 7 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 X 0 0 X X 1 X X X X 0 1 X 1 0 0 X 1 0 X X 1 X X X X 1 1 X 1 0 1 X 1 0 X X 1 X X X X 0 0 X 0 1 1 X 1 0 X X 1 X X X X 0 0 X 1

T3 0 0 X 0 0 X X 1 X X X X 1 0 X 0

T2 0 0 X 1 1 X X 0 X X X X 0 0 X 0

T1 0 1 X 0 0 X X 0 X X X X 0 0 X 1

T0 1 0 X 0 0 X X 0 X X X X 0 1 X 0

12 15

3. Minimizacin de las funciones e implementacin del circuito Simplificando obtendremos las funciones de entrada a los biestables (T3, T2, T1 y T0) para el clculo del nuevo estado. La funcin de salida, como se ha comentado, consiste simplemente en conectar cada salida de los biestables a la seal de activacin de cada una de las 4 barras luminosas, tal y como se muestra en la figura.

T3 = m7 + m12 T2 = m3 + m 4 T1 = m1 + m15 T0 = m0 + m13

Puesto que el enunciado pide utilizar puertas OR y decodificadores, lo que haremos ser utilizar un decodificador 4X16, al que conectaremos las salidas de los biestables (Q3, Q2, Q1 y Q0), de manera que para la implementacin de T3, por ejemplo, slo tendremos que sumar las salidas 7 y 12 del decodificador.

Tema 7: Sistemas Secuenciales Sncronos

14

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

EJERCICIOS PROPUESTOS.

1) Disear un circuito secuencial con una entrada (E) y una salida (S), de manera que S tome el valor 1 cuando se hayan recibido por la entrada al menos dos ceros y al menos un uno, independientemente del orden de aparicin. Una vez que S sea 1 se mantendr este valor sea cual sea la entrada. Ejemplos: E: 011111001001 S: 000000111111 Se pide: 1. El diagrama de estados y la codificacin de los mismos (0,8 p). 2. La tabla de transicin de estados, teniendo en cuenta que el bit ms significativo del estado debe implementarse con un biestable tipo JK, el siguiente con un biestable tipo T y el ltimo (si lo hubiera) con un biestable tipo D. (1,2p).

E: 00000111 S: 000001...

2) Una mquina de bebidas refrescantes proporciona una lata por valor de 0,80 o 133 ptas. Slo admite una moneda de 25, 50 y 100 ptas y de 0,20 para adquirir la lata y no devuelve cambio. Si la cantidad introducida es mayor que la necesaria, proporciona la lata, poniendo a 1 la salida S y activa un panel luminoso que pone Gracias por renunciar al cambio poniendo a 1 la salida L. Si se introduce el precio exacto, slo proporciona la lata, sin activar el panel luminoso. No se puede cambiar el tipo de monedas con el que se empez (si se comenz con pesetas, se seguir con pesetas, y si se comenz con euros se seguir con euros) salvo que se alcance el valor de 100 ptas 0,60 , en cuyo caso se puede cambiar de moneda. Cada vez que entregue una lata, volver al estado inicial, preparada para funcionar de nuevo. Utilizar la siguiente codificacin de monedas de entrada: AB 00 01 10 11 Significado moneda de 25 ptas moneda de 50 ptas moneda de 100 ptas moneda de 0,20

NOTA: Recordar que el valor de 1 es de 166,386 ptas y que 100 ptas son exactamente 0,60 . Codificar los estados de forma que el valor numrico que indica el cdigo generado con los biestables de mayor a menor peso sea mayor cuanto mayor sea la cantidad de dinero introducida en la mquina hasta ese momento, independientemente de la moneda introducida. Se pide: 1) 2) 3) 4) Definicin y codificacin de estados (0,6 puntos). Diagrama de estados (0,7 puntos). Tabla de transicin y excitacin usando biestables T (0,7 puntos). Circuitera combinacional adicional que admitiendo como entradas las salidas de los biestables ponga a 1 dos salidas, una P que activa un panel luminoso que pone PESETAS y otra E, que activa un panel luminoso que pone EUROS indicndole al usuario qu tipo de moneda debe introducir. Es posible que en algn caso puede introducir dos, y se encendern ambos paneles poniendo a 1 sus respectivas entradas. Implementar P con un decodificador con salidas activas a nivel bajo y una puerta lgica con el mnimo nmero de entradas (0,3 puntos). Cul es la forma ms sencilla de obtener E? (0,2 puntos).

Tema 7: Sistemas Secuenciales Sncronos

15

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

3) El circuito de la Figura corresponde al sistema de apertura de una puerta de garaje controlada por un mando a distancia.

M S1 S2 F2 F1

El sensor M detecta la orden del mando, mientras que los sensores S1 y S2 indica si la puerta est completamente cerrada o completamente abierta, respectivamente. M toma el valor lgico 1 cuando recibe la orden del mando, y cero en caso contrario. Los sensores S1 y S2 toman el valor lgico 1 cuando la puerta est completamente cerrada o completamente abierta, respectivamente, mientras que su valor es 0 durante las operaciones de apertura o cierre. Las salidas F1 y F2 indican si est o no activado el motor de la puerta, y el sentido en caso de estar activado, respectivamente. Es decir, si F1 est activada (1 lgico) entonces el motor se pone en marcha, mientras que al desactivarla (0 lgico) ste se para. Mientras, F2 indica si el sentido del motor debe ser abrir (1 lgico) o cerrar (0 lgico). El circuito que gestiona la apertura de la puerta sigue los siguientes criterios: Cuando la puerta est cerrada y recibe una orden del mando (M) se pone en marcha la apertura de la puerta, que finalizar cuando el sensor S2 indique que est totalmente abierta (cuando tome el valor 1 lgico). Cuando la puerta est abierta y recibe una orden del mando (M) se pone en marcha el cierre de la puerta, que finalizar cuando el sensor S1 indique que est totalmente cerrada (cuando tome el valor 1 lgico). Si durante la apertura o cierre de la puerta, y antes de que se haya completado la operacin, se recibe una nueva orden del mando, sta ser ignorada. Para ello, se pide: Definir claramente los estados, entradas y salidas (0,5 puntos) Dibujar el diagrama de estados (1 puntos). Hacer la tabla de verdad del circuito (0,5 puntos). Si se quiere hacer que la puerta se cierre sola transcurridos 32 segundos desde que se abri totalmente y no habiendo recibido la orden del mando a distancia, qu circuitera se podra aadir al circuito anterior para conseguir este efecto (0,5 puntos)?

a) b) c) d)

4) Disear un sistema secuencial capaz de reconocer el patrn 001011. La entrada al circuito se realizar a travs de una seal de entrada E, de forma sncrona, y en serie (un nuevo bit cada ciclo de reloj). El circuito dispondr de una salida S que tomar el valor 1 en el instante en el que se reconozca el patrn en la secuencia de entrada, y ser 0 en todos los dems casos. NOTA: debe tenerse en cuenta que al recibir un bit fuera de secuencia no hay que desechar todos los valores recogidos hasta ese momento. Es posible que parte de la secuencia siga siendo vlida. Por ejemplo, si suponemos que se ha recibido la secuencia 00, y a continuacin llega un tercer 0, se considerar que los 2 ltimos ceros son parte de una secuencia correcta. Se pide: a) Identificacin y codificacin de estados (0.75 p). b) Diagrama de estados (1 p). c) Completar la tabla de verdad teniendo en cuenta que deben utilizarse biestables tipo JK, T y D (de ms a menos significativo) para la implementacin fsica del circuito (0.75 p).

Tema 7: Sistemas Secuenciales Sncronos

16

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

5) El sistema de apertura de una caja fuerte est compuesto por dos teclas A y B, un circuito secuencial a disear y un temporizador que mantiene la caja fuerte abierta durante 5 minutos cuando recibe un nivel lgico 1 desde el circuito secuencial. Este temporizador vuelve a cerrar la caja fuerte pasado dicho tiempo, independientemente del circuito secuencial. Cuando se pulsa la tecla A, se produce un nivel lgico 1 que entra al circuito secuencial, mientras que cuando se pulsa la tecla B se produce un nivel lgico 0 de entrada al circuito a disear. Mientras no se pulse ninguna tecla no se genera ningn nivel lgico de entrada al circuito secuencial.

A B C irc u ito s e c u e n c ia l C a ja fu e rte

T e m p o riz a d o r

Para abrir la caja fuerte, la combinacin secreta es: pulsar dos veces seguidas la tecla A, a continuacin pulsar una vez la tecla B, y finalmente pulsar una vez la tecla A. Si se hace de esta manera, el circuito secuencial dar una salida a nivel lgico 1, que actuar sobre el temporizador, permitiendo la apertura de la caja fuerte durante 5 minutos. Si en cualquier momento se introdujera un error al pulsar la secuencia secreta, en el siguiente ciclo de reloj todos los biestables se pondrn a cero (el sistema pasar al estado inicial), y la secuencia debe volver a introducirse desde el principio. A) Dibujar el diagrama de estados, explicando claramente en qu consiste cada estado.

B) Implementar el circuito secuencial a disear usando biestables JK y las puertas

necesarias. 6) Se pretende disear un sistema secuencial sncrono con dos entradas E1 y E0, y una salida S usando biestables D, de manera que proporcione salida alta slo cuando las dos entradas estn a nivel bajo habiendo estado tambin a nivel bajo ambas entradas en el ciclo de reloj anterior. Las transiciones se producen en el flanco de bajada del reloj. En los restantes ciclos de reloj, la salida debe ser baja. Las seales de entrada son peridicas, con un periodo 5 veces superior al perodo de reloj, y son las mostradas en la figura. NOTA: Observar que no se producen todas las transiciones posibles. a) Realizar el diagrama de transicin de estados, definiendo y codificando los estados y las entradas. b) Realizar la tabla de verdad que resuelve el problema. c) Encontrar el circuito.

7) Una fuente de agua posee tres focos luminosos (azul, rojo, verde) y una caja musical que tiene 7 canales digitales de entrada, cada uno de ellos para activar cada una de las 7 notas musicales. Por ejemplo, si se proporciona un 1 lgico por el canal de entrada de la nota "Mi" sonar esa nota durante un ciclo de reloj. Suponer que la secuencia que se quiere seguir en la iluminacin con los focos es: todos apagados, rojo, azul, rojo y azul, verde, verde y rojo, verde y azul, todos encendidos. Al mismo tiempo la secuencia de notas musicales debe ser: Re, Mi, Fa, Sol, Do, La, Si, La. Disear un circuito secuencial que implemente esta secuencia 5 veces y que termine con todos sus componentes apagados: luces y sonido.

1) Resolver el sistema de iluminacin tomando la codificacin ms adecuada al enunciado del problema. Mostrar el diagrama de estados, la codificacin de estados y la tabla de excitacin del sistema. Implementar este subsistema de la forma ms sencilla posible utilizando biestables JK. (1 punto). 2) Resolver el sistema digital, asociado al diseo anterior, que excite la caja musical segn la secuencia indicada. (1 punto). 3) Resolver el sistema de apagado de los dos sistemas anteriores. (1 punto). Utilizar en el diseo puertas lgicas (las imprescindibles), mdulos combinacionales y contadores.

Tema 7: Sistemas Secuenciales Sncronos

17

Anda mungkin juga menyukai

- Tema 4aDokumen19 halamanTema 4aRaul Martinez JadalBelum ada peringkat

- Lab 3 - Elect III - WilbertPizarroCastroDokumen19 halamanLab 3 - Elect III - WilbertPizarroCastrowilpizarroBelum ada peringkat

- MealyDokumen10 halamanMealyDaky Pintag Lema MalesBelum ada peringkat

- Capitulo Vi - Analisis y Sintesis de Circuitos Secuenciales SincronosDokumen72 halamanCapitulo Vi - Analisis y Sintesis de Circuitos Secuenciales Sincronosalex100% (1)

- Maquinas de EstadoDokumen12 halamanMaquinas de EstadoChris Castro0% (1)

- Secuenciales caja fuerteDokumen16 halamanSecuenciales caja fuerteWilmer Guaño100% (1)

- Máquinas de Turing y ejerciciosDokumen14 halamanMáquinas de Turing y ejerciciosAndres MartinezBelum ada peringkat

- Maquinas SecuencialesDokumen2 halamanMaquinas SecuencialesRuben DavidBelum ada peringkat

- AnÁlisis y DiseÑo de Circuitos SecuencialesDokumen32 halamanAnÁlisis y DiseÑo de Circuitos SecuencialesOscar Salazar0% (1)

- Teoria Maquinas de EstadoDokumen28 halamanTeoria Maquinas de EstadocarlosmorgadohdzBelum ada peringkat

- Diseño de Contadores SincronosDokumen12 halamanDiseño de Contadores Sincronosorlando_heredia7934Belum ada peringkat

- Teoría de MÁquinas de EstadoDokumen6 halamanTeoría de MÁquinas de EstadoIng Fernando RomeroBelum ada peringkat

- I. Resumen Teórico: A) Circuitos SecuencialesDokumen24 halamanI. Resumen Teórico: A) Circuitos SecuencialesAnonymous UI7JawqBelum ada peringkat

- Automatas y LenguajesDokumen18 halamanAutomatas y LenguajesCesar Augusto Alvis MuñozBelum ada peringkat

- Sistemas DigitalesDokumen69 halamanSistemas DigitalesMary Alarcon PalominoBelum ada peringkat

- Sistemas Secuenciales 1Dokumen86 halamanSistemas Secuenciales 1Enrique Santiago MaldonadoBelum ada peringkat

- Ejercicios PropuestosDokumen65 halamanEjercicios PropuestosSonia Aguilar HuichoBelum ada peringkat

- Informe Maquinas de EstadoDokumen10 halamanInforme Maquinas de EstadoEJ AlvarezBelum ada peringkat

- Wuolah-free-Ejercicios Resueltos de SecuencialesDokumen17 halamanWuolah-free-Ejercicios Resueltos de SecuencialesCayetanoBelum ada peringkat

- SOLUCION ExamenFCO Enero 2011Dokumen12 halamanSOLUCION ExamenFCO Enero 2011Adri SsBelum ada peringkat

- Ejercici - o Secuencia - LDokumen2 halamanEjercici - o Secuencia - LErickBelum ada peringkat

- Máquinas de Estados PDFDokumen13 halamanMáquinas de Estados PDFjosmarsonicBelum ada peringkat

- Reconocedor de Secuencia Modelo Mealy o MooreDokumen5 halamanReconocedor de Secuencia Modelo Mealy o MooreMaggie TecotlBelum ada peringkat

- Circuitos secuenciales UCSMDokumen86 halamanCircuitos secuenciales UCSMJuan Diego Márquez ChávezBelum ada peringkat

- Circuitos SecuencialesDokumen24 halamanCircuitos SecuencialesDaniel GarciaBelum ada peringkat

- Practica 06Dokumen14 halamanPractica 06guidoBelum ada peringkat

- Informe Final 5Dokumen16 halamanInforme Final 5Julio David Vilca PizarroBelum ada peringkat

- Teoria Maquinas de EstadoDokumen28 halamanTeoria Maquinas de EstadoRonald Eder Chavez PalominoBelum ada peringkat

- Aguilera Gonzalez Jorge ETCDokumen4 halamanAguilera Gonzalez Jorge ETCCarlos BurgosBelum ada peringkat

- Logica SecuencialDokumen23 halamanLogica SecuencialBryan Jaramillo100% (1)

- Circuito SecuencialDokumen86 halamanCircuito SecuencialHbr LpzBelum ada peringkat

- 2P EnI 15-16-SolucionDokumen8 halaman2P EnI 15-16-SolucionTheDoctor TheDoctorBelum ada peringkat

- Teoría de Autómatas SincronosDokumen23 halamanTeoría de Autómatas SincronosJorge D. NontolBelum ada peringkat

- Diseño de Sistema SecuencialDokumen32 halamanDiseño de Sistema SecuencialSergio RamirezBelum ada peringkat

- Sesion 14 - Analisis y SintesisDokumen21 halamanSesion 14 - Analisis y SintesisKevin B SánchezBelum ada peringkat

- FSM Teoría Máquinas EstadoDokumen4 halamanFSM Teoría Máquinas EstadoManuel SilvaBelum ada peringkat

- Contadores y RegistrosDokumen19 halamanContadores y RegistrosElymar91Belum ada peringkat

- Diagrama de Estado y Tabla de EstadoDokumen9 halamanDiagrama de Estado y Tabla de EstadoErick AlexanderBelum ada peringkat

- 2 - Contador - 20230718Dokumen8 halaman2 - Contador - 20230718fedemayol026Belum ada peringkat

- Circuito Secuencial Sincrono Puerta AutomaticaDokumen7 halamanCircuito Secuencial Sincrono Puerta Automaticajunmech100% (2)

- Secuencia de apertura de caja fuerte con circuito secuencialDokumen30 halamanSecuencia de apertura de caja fuerte con circuito secuencialWilliam DavidBelum ada peringkat

- Ecuaciones de estado para circuitos secuencialesDokumen10 halamanEcuaciones de estado para circuitos secuencialesEdwin GómezBelum ada peringkat

- 9 Diseño de Sistemas Secuenciales TeamsDokumen35 halaman9 Diseño de Sistemas Secuenciales TeamsPaola de LeonBelum ada peringkat

- Maquina Secuencial Elai-UpmDokumen43 halamanMaquina Secuencial Elai-Upmjjurado183Belum ada peringkat

- GrafosDokumen6 halamanGrafosMagii DiazBelum ada peringkat

- Ejercicios de Circuitos SecuencialesDokumen15 halamanEjercicios de Circuitos SecuencialesNicolas Rueda Gutierrez0% (1)

- Controlabilidad y ObservabilidadDokumen15 halamanControlabilidad y ObservabilidadAndrés Jiménez100% (1)

- SD SES010 Analis Sist SecDokumen32 halamanSD SES010 Analis Sist SecMiguel CuyaBelum ada peringkat

- Capitulo 6. Sistemas Secuenciales PDFDokumen24 halamanCapitulo 6. Sistemas Secuenciales PDFEfra IbacetaBelum ada peringkat

- Linealización de un sistema de tanques interconectadosDokumen4 halamanLinealización de un sistema de tanques interconectadosLukautomat100% (1)

- Ejercicios de Integrales de Línea, Superficie y VolumenDari EverandEjercicios de Integrales de Línea, Superficie y VolumenPenilaian: 4 dari 5 bintang4/5 (2)

- Proyecto Conexion VF y MotorDokumen110 halamanProyecto Conexion VF y MotorAntonio TorresBelum ada peringkat

- Articulo Variador de Velocidad SiemensDokumen2 halamanArticulo Variador de Velocidad SiemensLeonardo Alexis Calvo CerdaBelum ada peringkat

- SMD 1Dokumen9 halamanSMD 1Antonio TorresBelum ada peringkat

- OCW Tema 14 ErroresDokumen27 halamanOCW Tema 14 ErroresAntonio TorresBelum ada peringkat

- Clases 2.0Dokumen1 halamanClases 2.0Antonio TorresBelum ada peringkat

- Lengua PAGS AndalucíaDokumen4 halamanLengua PAGS AndalucíaAntonio TorresBelum ada peringkat

- Area Figuras Volumen CuerposDokumen6 halamanArea Figuras Volumen CuerposclaudiabcBelum ada peringkat

- Control AutomáticoDokumen3 halamanControl AutomáticoAntonio TorresBelum ada peringkat

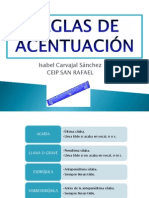

- Reglas de AcentuaciónDokumen15 halamanReglas de AcentuaciónAntonio TorresBelum ada peringkat

- Palabras colectivasDokumen1 halamanPalabras colectivasAntonio TorresBelum ada peringkat

- Diptongos y HiatosDokumen19 halamanDiptongos y HiatosVivian Hurtado100% (1)

- Leccion - 3 Razones y ProporcionesDokumen27 halamanLeccion - 3 Razones y ProporcionesCarlos Arrieta0% (1)

- Produccion y Empresa PDFDokumen11 halamanProduccion y Empresa PDFJavier VillanuevaBelum ada peringkat

- Qui MicaDokumen6 halamanQui MicaAna Lopez GarciaBelum ada peringkat

- 04 Operaciones Naturales DivisibilidadDokumen2 halaman04 Operaciones Naturales DivisibilidadPatricia AndersonBelum ada peringkat

- Tema 41Dokumen6 halamanTema 41Antonio TorresBelum ada peringkat

- Cervantes. Aula de LetrasDokumen10 halamanCervantes. Aula de LetrasCarmesinaBelum ada peringkat

- 1eso Cuaderno 2 CasDokumen13 halaman1eso Cuaderno 2 CasjohancarvalBelum ada peringkat

- Circuito Secuencial Sincrono Puerta AutomaticaDokumen7 halamanCircuito Secuencial Sincrono Puerta Automaticajunmech100% (2)

- Ejercicios Ecs de La RectaDokumen19 halamanEjercicios Ecs de La RectaAntonio TorresBelum ada peringkat

- Clases Desde Donde Tu Quieras - Ing y ArqDokumen1 halamanClases Desde Donde Tu Quieras - Ing y ArqAntonio TorresBelum ada peringkat

- Tesis Doctoral de Jose Luis Serrano SanchesDokumen416 halamanTesis Doctoral de Jose Luis Serrano SanchesmaestriaedcBelum ada peringkat

- ExamenParcial1 SolDokumen5 halamanExamenParcial1 SolAntonio TorresBelum ada peringkat

- Informe Manual de SeñalizaciónDokumen26 halamanInforme Manual de SeñalizaciónCristian MendozaBelum ada peringkat

- Traduccion Nace tm0173Dokumen11 halamanTraduccion Nace tm0173fernandez100% (2)

- Vdocuments - Es Maintenance Sandvik LH 410Dokumen87 halamanVdocuments - Es Maintenance Sandvik LH 410Francisco GutierrezBelum ada peringkat

- Análisis de la película Replicas y sus implicaciones éticasDokumen3 halamanAnálisis de la película Replicas y sus implicaciones éticasXiolin Rafael Ramirez GuzmanBelum ada peringkat

- Juegos de MesaDokumen19 halamanJuegos de Mesaeduardopineros100% (1)

- Hortus 20220707094447 FichaTecnicaTEBUSAC25EWTebuconazoleHortusDokumen3 halamanHortus 20220707094447 FichaTecnicaTEBUSAC25EWTebuconazoleHortusCharles Cipriano AvalosBelum ada peringkat

- Trabajo Hidro11Dokumen13 halamanTrabajo Hidro11Nelson AlarconBelum ada peringkat

- Cap+¡tulo6 NewmarkDokumen39 halamanCap+¡tulo6 NewmarkLuis EduardoBelum ada peringkat

- Actividad 2Dokumen8 halamanActividad 2Lourdes MadridBelum ada peringkat

- GeometriaDokumen24 halamanGeometriaJaime Sarmiento ZegarraBelum ada peringkat

- Actividad Determinación Del PrecioDokumen4 halamanActividad Determinación Del Precioalexander benavBelum ada peringkat

- Calcinacion Lab 2Dokumen7 halamanCalcinacion Lab 2Jimena Bautista VelardeBelum ada peringkat

- HybrdosDokumen94 halamanHybrdosmoises marquezBelum ada peringkat

- Tema 6Dokumen64 halamanTema 6johanita035Belum ada peringkat

- Brotzman Rehabilitacion en Ortopedia ClinicaDokumen629 halamanBrotzman Rehabilitacion en Ortopedia ClinicaLuis Rodriguez100% (1)

- Especificaciones Tecnicas para Aguas NegrasDokumen17 halamanEspecificaciones Tecnicas para Aguas NegrasmarioalonsofBelum ada peringkat

- Solucionaio I y II 1er P. 5toDokumen6 halamanSolucionaio I y II 1er P. 5toNataly PedrazaBelum ada peringkat

- Ergonomía Preventiva y CorrectivaDokumen2 halamanErgonomía Preventiva y CorrectivaHany86% (14)

- Quemados - Manejo Del Paciente PediátricoDokumen28 halamanQuemados - Manejo Del Paciente PediátricoDr. Francisco ZapataBelum ada peringkat

- EVIDENCIA Plan MaestroDokumen11 halamanEVIDENCIA Plan MaestroJuan Esteban AcostaBelum ada peringkat

- Velocidad de VientoDokumen16 halamanVelocidad de VientoNicolás Posada GalvisBelum ada peringkat

- Muerte y Duelo DefinitivaDokumen4 halamanMuerte y Duelo DefinitivaFarid TalgierBelum ada peringkat

- Determinación experimental de gamma del aireDokumen11 halamanDeterminación experimental de gamma del aireCristian Joaquin Zegarra100% (1)

- Curso de Elementos Finitos Aplicado A Analisis EstructuralDokumen2 halamanCurso de Elementos Finitos Aplicado A Analisis EstructuralDiana Alejandra Torres RoncancioBelum ada peringkat

- Evaluacion de La Inducción GeneralDokumen2 halamanEvaluacion de La Inducción GeneraldonaxtaBelum ada peringkat

- Barreras de La Creatividad PDFDokumen5 halamanBarreras de La Creatividad PDFAntonio Ramirez Arce100% (1)

- Criadero de ChinitasDokumen4 halamanCriadero de ChinitasMarcy Guzmán LastraBelum ada peringkat

- 5.manual Administracion Ranchos GanaderosDokumen223 halaman5.manual Administracion Ranchos GanaderosSalvador Acosta VenegasBelum ada peringkat

- Caretta CarettaDokumen4 halamanCaretta CarettaYajaira GuerreroBelum ada peringkat

- Hernandez Perez Jesus Ubaldo - Unidad 3 - La Izquierda MexicanaDokumen97 halamanHernandez Perez Jesus Ubaldo - Unidad 3 - La Izquierda MexicanaJesus Ubaldo Hernandez PerezBelum ada peringkat