AP Divisor de Frecuencia y Máquinas de Estado

Diunggah oleh

Ronny AuccapiñaDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

AP Divisor de Frecuencia y Máquinas de Estado

Diunggah oleh

Ronny AuccapiñaHak Cipta:

Format Tersedia

CIRCUITOS DIGITALES I

DIVISOR DE FRECUENCIA Y MAQUINAS DE ESTADO

INTEGRANTES: AUCCAPIA GALLEGOS, Ronny Profesor: SARCO MONTIEL, Armando Fecha De Realizacin: 17 de Mayo Fecha de Entrega: 24 de Mayo

2013

CIRCUITOS DIGITALESLAB 10

OBJETIVOS: 1. Disear sistemas secuenciales sncronos mediante los autmatas de Moore y Mealy mediante el uso de la tabla de transicin de FF, la tabla de diseo del circuito y los mapas de Karnaugh. 2. Usar eficazmente el software de simulacin para la comprobacin de los diseos. 3. Implementar circuitos secunciales sncronos. INTRODUCCIN TERICA: Los circuitos secunciales, de la misma forma que los combinacionales, estn constituidos por puertas lgicas, y como en estos ltimos, la escala de integracin de la mayora de los circuitos disponibles en catalogo es la MSI. Sin embargo, presentan unas caractersticas muy singulares que describiremos a continuacin. A diferencia de los circuitos combinacionales, en los secuenciales, los valores de las salidas en un momento dado no dependen exclusivamente de los valores aplicados en las entradas en ese instante, sino tambin de los que estuviesen presentes con anterioridad. Puede ocurrir, por lo tanto, que para iguales valores en las entradas se puedan obtener estados distintos en las salidas en momentos diferentes. La respuesta de un circuito de estas caractersticas, frente a una secuencia de valores aplicada a las entradas, depende de su constitucin fsica. Los circuitos secuenciales tienen capacidad para recordar o memorizar los valores de las variables de entrada. Esta operacin es imprescindible en los sistemas automticos construidos con circuitos digitales, sobre todo en los programables, de los cuales nos ocuparemos ms adelante. El almacenamiento o memorizacin de la informacin presente en la puerta del circuito se realiza gracias a la existencia de unas variables denominadas de estado interno, cuyo valor se ver afectado por los cambios producidos en la combinacin binaria aplicada a la entrada. Existen dos grandes tipos de circuitos secuenciales: a) Maquina de Mealy. En este tipo de circuitos, las salidas dependen, en cada instante de los valores de los elementos de memoria y de las entradas presentes en ese instante. Aqu, para cada estado, podemos tener tantas salidas como combinaciones tengamos en las entradas.

CIRCUITOS DIGITALESLAB 10

b) Maquina de Moore. Aqu las salidas en cada instante dependen exclusivamente de los estados de los elementos de memoria, y no dependen directamente de las entradas en ese instante. Los valores de las entradas, sirven para modificar las diversas transiciones entre estados.

ACTIVIDAD:

MULTIPLICADOR DE VELOCIDAD BINARIA 3.36.1 OBJETIVOS Estudiar un circuito que permite obtener una frecuencia cualquiera a partir de otra dada. 3.36.4 a) Montar el circuito de la figura. Poner todas las entradas J de los flip-flops a nivel alto. Conectar la entrada del clock y las entradas de programacin X1,X2 y X3 al Programador de Estado Lgico. b) Programando un valor en las entradas de programacin, comprubese el nmero de impulsos que se obtiene a la salida al 8 impulsos a la entrada del CLOCK. Se puede contar fcilmente, montando un contador asncrono a la salida que nos indique el resultado. Comprubese que el nmero de impulsos corresponde al valor 4.

X1 1 1 1 1 0 0 1

X2 0 1 0 1 1 1 1

X3 0 0 1 1 0 1 0

SALIDA 2pulsos 2 2 2 4 pulsos 4 4

CIRCUITOS DIGITALESLAB 10

1 0 0 1 1 1 X x

1 0 1 0 1 X 1 X

1 1 1 1 1 X X 1

4 8 pulsos 8 8 8 2 4 8

SEGUNDA PARTE: I. Disear un contador de tres bits que recorra la siguiente secuencia 000, 101, 010, 011, 100,000, 1. Dibuje el diagrama de estados requerido, incluya los estados no deseados al inicio de la cuenta. 2. Escriba la tabla de estados del circuito requerido. 3. Se usaran flip flops JK, escriba la tabla de excitaciones de los flip flops. 4. Escriba la tabla de diseo en la que deben aparecer, el estado presente, el estado siguiente y la entradas de los flip flops JK. 5. Disee los circuitos lgicos que generan los niveles requeridos en cada entrada JK y dibuje el circuito secuencial encontrado. Simule el circuito encontrado y verifique su funcionamiento.

CONTADOR DE 3 BITS:

tabla de Excitacin del flip flop JK

Q 0 0 1 1

Qn+

1

J 0 1 * *

K * * 1 0

0 1 0 1

CIRCUITOS DIGITALESLAB 10

000

101

10 0

01 1

0 1 0 1 0 1 0 1

01 0

0 1 0 0 1 0 1 1

PRESENTE 0 0 1 1 0 0 1 1

1 0 0 1 0 0 0 0

FUTURO 0 1 1 0 0 0 0 0

1 0 1 0 0 0 0 0

J1 1 * 0 1 * 0 * *

K1 * 1 * * 1 * 1 1

J2 0 1 * * 0 0 * *

K2 * * 0 1 * * 1 1

J3 1 * 1 * 0 * 0 *

K3 * 1 * 1 * 1 * 1

J1= Q2.Q3 +Q2.Q3 J2= Q1.Q3 J3= Q1

K1=1 K2=Q3+Q1 K3=1

II. Disee un contador sncrono ascendente/ descendente de dos bits; las salidas del contador son QAQB, tiene una entrada de control up/Down que permite seleccionar si el contador cuenta en forma ascendente o descendente.

CIRCUITOS DIGITALESLAB 10

por lo tanto Y= UP/Down Y=1 UP Y=0 Down 1. 2. 3. 4. Dibuje el diagrama de estados requerido. Escriba la tabla de estados del circuito requerido. Se usaran flip flop JK, escriba la tabla de excitacin de los flip flops. Escriba la tabla de diseo en la que deben aparecer, el estado presente, el estado siguiente y las entradas de los flip flops JK. 5. Disee los circuitos lgicos que generan los niveles requeridos en cada entrada JK y dibuje el circuito secuencial encontrado.

tabla de Excitacin del flip flop JK

01 00

10

01 00

10 11

Q 0 0 1 1

Qn+

1

J 0 1 * *

K * * 1 0

11

0 1 0 1

I 0 0 0 0 1

PRESENTE Q1 Q0 0 0 0 1 1 0 1 1 0 0

FUTURO Q1 Q0 0 1 1 0 1 1 0 0 1 1

J1 0 1 * * 1

K1 * * 0 1 *

J0 1 * 1 * 1

K0 * 1 * 1 *

CIRCUITOS DIGITALESLAB 10

1 1 1

0 1 1

1 0 1

0 0 1

0 1 0

0 * *

* 1 0

* 1 * 1

1 * 1 1

CIRCUITOS DIGITALESLAB 10

Anda mungkin juga menyukai

- Diseño de Un Contador Sincronico Con Flip PDFDokumen8 halamanDiseño de Un Contador Sincronico Con Flip PDFFrancisco Flores LunaBelum ada peringkat

- Un Circuito Secuencial Puede Entenderse Simplemente Como Un Circuito Combinacional en El Cuallas Salidas Dependen Tanto de Las Entradas Como de Las Salidas en Instantes AnterioresDokumen5 halamanUn Circuito Secuencial Puede Entenderse Simplemente Como Un Circuito Combinacional en El Cuallas Salidas Dependen Tanto de Las Entradas Como de Las Salidas en Instantes AnterioresNeiry FrancoBelum ada peringkat

- Los Flip FlopDokumen18 halamanLos Flip FloproxanaBelum ada peringkat

- Contador de CajasDokumen3 halamanContador de CajasMundoRo ComiPaBelum ada peringkat

- Electronica Diagramas Circuitos - Cargador para Baterías NiMH de FloteDokumen2 halamanElectronica Diagramas Circuitos - Cargador para Baterías NiMH de FloteCarlos RamosBelum ada peringkat

- PracticaDokumen12 halamanPracticaIsa RochaBelum ada peringkat

- Fli-Flops, Registros y ContadoresDokumen15 halamanFli-Flops, Registros y ContadoresOmar XocaBelum ada peringkat

- Flip FlopDokumen4 halamanFlip FlopErick Esteban NarvaezBelum ada peringkat

- Contadores MonolíticosDokumen15 halamanContadores MonolíticosJean Carlo ArrietaBelum ada peringkat

- 2 Contador de 0-99 7segDokumen6 halaman2 Contador de 0-99 7segJalapa Lug GuatemalaBelum ada peringkat

- Implementacion Del Minesweeper Con Un Tablero de LedsDokumen16 halamanImplementacion Del Minesweeper Con Un Tablero de LedsRenzo Moscoso BasalduaBelum ada peringkat

- Divisor de Frecuencia y Contador de RizoDokumen2 halamanDivisor de Frecuencia y Contador de RizoEddy Fernando Queca CadizBelum ada peringkat

- Cómo Funciona Un Chip 7490Dokumen1 halamanCómo Funciona Un Chip 7490Leo AriasBelum ada peringkat

- Informe Flip FlopsDokumen11 halamanInforme Flip FlopsLeonardo López Avila100% (1)

- Flip Flops UNLaMDokumen37 halamanFlip Flops UNLaMAnonymous dsefX2Jhm8Belum ada peringkat

- Mapas de KarnaughDokumen7 halamanMapas de KarnaughNathaly Freire LopezBelum ada peringkat

- Maquinas MooreDokumen35 halamanMaquinas MooreDaniel GuerraBelum ada peringkat

- Secuenciales - Sincronicos - AnalisisFRA - v3 Unidad 9 PDFDokumen35 halamanSecuenciales - Sincronicos - AnalisisFRA - v3 Unidad 9 PDFJonatanArtalBelum ada peringkat

- Practica 8G2 Contador Sincrono FlipFlop DLDokumen4 halamanPractica 8G2 Contador Sincrono FlipFlop DLAlexander Robles CaicedoBelum ada peringkat

- Lab07 Flip FlopsDokumen12 halamanLab07 Flip FlopsAlejandro Martin Leon CernaBelum ada peringkat

- Proyectos Con PICsDokumen8 halamanProyectos Con PICsArmando CajahuaringaBelum ada peringkat

- Práctica 5 - Flip-Flops, Contadores Síncronos - 1Dokumen2 halamanPráctica 5 - Flip-Flops, Contadores Síncronos - 1Juan Camilo GonzalesBelum ada peringkat

- Recopilacion Aportes Proyecto Final..Dokumen28 halamanRecopilacion Aportes Proyecto Final..JoseSalamancaPlazasBelum ada peringkat

- Guia 4 SDI115Dokumen6 halamanGuia 4 SDI115Carlos_29Belum ada peringkat

- TP09 Circuitos Secuenciales Sincronicos 2019Dokumen5 halamanTP09 Circuitos Secuenciales Sincronicos 2019JonatanArtalBelum ada peringkat

- Circuitos DigitalesDokumen11 halamanCircuitos DigitalesShirley Beleño BarriosBelum ada peringkat

- Contador de MooreDokumen6 halamanContador de MooreErnesto VásquezBelum ada peringkat

- El Flip FlopDokumen17 halamanEl Flip FlopLuigi Jair Torres MirandaBelum ada peringkat

- Práctica 01 E5 B 3Dokumen5 halamanPráctica 01 E5 B 3Cristian HernandezBelum ada peringkat

- Báscula RSDokumen3 halamanBáscula RSCarlos Raul Gomez Frayre100% (1)

- Practica1 Instrumentacion IDokumen2 halamanPractica1 Instrumentacion Ianderson “proxy”Belum ada peringkat

- P09 Interface I2C PIC18FDokumen7 halamanP09 Interface I2C PIC18FOscar A. PomaBelum ada peringkat

- Laboratorio 5 Mapas de KarnaughDokumen6 halamanLaboratorio 5 Mapas de KarnaughYesenia Jaime RoaBelum ada peringkat

- Prueba 1 IB RúbricaDokumen1 halamanPrueba 1 IB RúbricaEstefani columbaBelum ada peringkat

- 74 Ls 161Dokumen3 halaman74 Ls 161Angel Rogelio Minta Toapanta0% (1)

- Control de Motor Paso A Paso Con PicDokumen1 halamanControl de Motor Paso A Paso Con PicGoti TorcalBelum ada peringkat

- Práctica Microondas Electrónica DigitalDokumen18 halamanPráctica Microondas Electrónica DigitalEduardo Canto0% (1)

- P05 Programacion en MikroBasicDokumen6 halamanP05 Programacion en MikroBasicJorge Luis Castillo GuarachiBelum ada peringkat

- Contador Con Flip-FlopDokumen2 halamanContador Con Flip-Floptubi vok3100% (3)

- El Flip Flop y Los Circuitos SecuencDokumen26 halamanEl Flip Flop y Los Circuitos Secuencb4tipibeBelum ada peringkat

- Siste Digit Previo 3Dokumen6 halamanSiste Digit Previo 3DiegoBelum ada peringkat

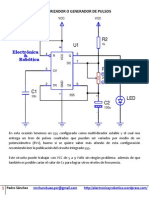

- Temporizador o Generador de PulsosDokumen2 halamanTemporizador o Generador de PulsosPedro SánchezBelum ada peringkat

- Modulo 3: Puerto Serie. Introducción Al Lenguaje CDokumen51 halamanModulo 3: Puerto Serie. Introducción Al Lenguaje CJuan Gonzalez Gomez100% (1)

- Cuadro Comparativo Tipos de ContadoresDokumen4 halamanCuadro Comparativo Tipos de ContadoresYousei Ruki Uruha Teikoku IshtarBelum ada peringkat

- Pic Basic DisplayDokumen10 halamanPic Basic DisplayManuel Eduardo Estrella PolancoBelum ada peringkat

- Examen de Sistemas DigitalesDokumen11 halamanExamen de Sistemas DigitalesMax cuadrosBelum ada peringkat

- Informe Latch y Flip FlopDokumen11 halamanInforme Latch y Flip FlopAlex Vin0% (1)

- Contadores y MemoriasDokumen26 halamanContadores y MemoriasHector ValdiviaBelum ada peringkat

- Bies TableDokumen37 halamanBies TableLuz Karina Lopez SaavedraBelum ada peringkat

- Contador Con Flip-FlopDokumen19 halamanContador Con Flip-FlopMiguel Angel CasiqueBelum ada peringkat

- Practica 2 DAC0808Dokumen15 halamanPractica 2 DAC0808javier_valdivia_42Belum ada peringkat

- Multiplicador or Decodificador Codificador MultiplexorDokumen10 halamanMultiplicador or Decodificador Codificador MultiplexorJCesar Cusi AlvaradoBelum ada peringkat

- Laboratorio 4 de Sistemas Digitales - Fiee UnacDokumen13 halamanLaboratorio 4 de Sistemas Digitales - Fiee UnacJose Antonio Jara Chavez100% (2)

- Info 4 - Contadores...Dokumen8 halamanInfo 4 - Contadores...EJ AlvarezBelum ada peringkat

- Contador 4 BitsDokumen19 halamanContador 4 BitsAlvaro Gómez RubioBelum ada peringkat

- Maquinas Secuenciales EjemplosDokumen12 halamanMaquinas Secuenciales EjemplosDanny Perez100% (1)

- Circuitos SecuencialesDokumen7 halamanCircuitos SecuencialesMaria StewartBelum ada peringkat

- Electronica DigitalDokumen9 halamanElectronica Digitalanthony361989Belum ada peringkat

- LABORATORIO 09 (Máquinas de Estado)Dokumen15 halamanLABORATORIO 09 (Máquinas de Estado)julio enriqueBelum ada peringkat

- Practica 5Dokumen9 halamanPractica 5vagprogrammerBelum ada peringkat

- 1 Control CascadaDokumen35 halaman1 Control CascadaRonny AuccapiñaBelum ada peringkat

- 4 Simbología y Diagramas de InstrumentaciónDokumen21 halaman4 Simbología y Diagramas de InstrumentaciónRonny AuccapiñaBelum ada peringkat

- Preguntas Practica 1Dokumen2 halamanPreguntas Practica 1Ronny AuccapiñaBelum ada peringkat

- TrifasicoDokumen13 halamanTrifasicoConti ContiBelum ada peringkat

- 5 DR20 PWMDokumen3 halaman5 DR20 PWMRonny AuccapiñaBelum ada peringkat

- Tratamiento de Desinfección Del Agua Potable PDFDokumen132 halamanTratamiento de Desinfección Del Agua Potable PDFJesus Gomez PolancoBelum ada peringkat

- Sensores TemperaturaDokumen51 halamanSensores TemperaturaDarwin ChaleBelum ada peringkat

- PIC16F877 ResumenDokumen22 halamanPIC16F877 ResumenCarlosperezmBelum ada peringkat

- 5 DR20 PWMDokumen3 halaman5 DR20 PWMRonny AuccapiñaBelum ada peringkat

- Resolver Cubo Rubik Rev8Dokumen3 halamanResolver Cubo Rubik Rev8Daniel Alejandro RodriguezBelum ada peringkat

- Programación Del PICDokumen6 halamanProgramación Del PICRonny AuccapiñaBelum ada peringkat

- Controlador PID AnalogicoDokumen2 halamanControlador PID AnalogicoJuan Garcia VillaBelum ada peringkat

- 5 DR20 PWMDokumen3 halaman5 DR20 PWMRonny AuccapiñaBelum ada peringkat

- Edicion de Problemas NeumaticosDokumen18 halamanEdicion de Problemas NeumaticosRonny AuccapiñaBelum ada peringkat

- Cont Aut 1 Laplace EjmDokumen28 halamanCont Aut 1 Laplace EjmArturo TapiaBelum ada peringkat

- Lab 13311Dokumen5 halamanLab 13311Ronny AuccapiñaBelum ada peringkat

- Primeras Paginas HablaDokumen7 halamanPrimeras Paginas HablaJorge MoraBelum ada peringkat

- 02 - Circuitos Combinacionales en VHDLDokumen44 halaman02 - Circuitos Combinacionales en VHDLRonny AuccapiñaBelum ada peringkat

- Practica3 Arqui1Dokumen20 halamanPractica3 Arqui1Omar BalamBelum ada peringkat

- Texto 3Dokumen30 halamanTexto 3Ronny AuccapiñaBelum ada peringkat

- PC 2.doc Neumatica 2Dokumen5 halamanPC 2.doc Neumatica 2Ronny AuccapiñaBelum ada peringkat

- Matrices de LedsDokumen10 halamanMatrices de LedsRonny AuccapiñaBelum ada peringkat

- 02 - Circuitos Combinacionales en VHDLDokumen44 halaman02 - Circuitos Combinacionales en VHDLRonny AuccapiñaBelum ada peringkat

- Lab 01 AlgoritmosDokumen20 halamanLab 01 AlgoritmosRonny AuccapiñaBelum ada peringkat

- Texto 1Dokumen24 halamanTexto 1Ronny AuccapiñaBelum ada peringkat

- Controlador PID AnalogicoDokumen2 halamanControlador PID AnalogicoJuan Garcia VillaBelum ada peringkat

- Modelo de Lab01Dokumen13 halamanModelo de Lab01Ronny AuccapiñaBelum ada peringkat

- Texto 1Dokumen32 halamanTexto 1Diago Trigoso BernalBelum ada peringkat

- Texto 2Dokumen34 halamanTexto 2Ronny AuccapiñaBelum ada peringkat

- Productos NotablesDokumen22 halamanProductos NotablesUlises Gonzalez MoralesBelum ada peringkat

- Cuestionario Fisiología Animal 2bguDokumen7 halamanCuestionario Fisiología Animal 2bguAriel CondoyBelum ada peringkat

- KOOKTAE - Perfectly WrongDokumen17 halamanKOOKTAE - Perfectly WrongZumo De Limón :3100% (1)

- Unidad 3 Computación-Power Point 2016Dokumen47 halamanUnidad 3 Computación-Power Point 2016VICBelum ada peringkat

- El MaridajeDokumen8 halamanEl MaridajeLaleska Salinas FallaBelum ada peringkat

- Act2.1 AparicioMendoza 108 CoCoDokumen3 halamanAct2.1 AparicioMendoza 108 CoCoAntonio MendozaBelum ada peringkat

- Gramática Elemental Del Sánscrito Imprimir EmpastarDokumen187 halamanGramática Elemental Del Sánscrito Imprimir Empastaresco_maria100% (1)

- Resumen EstadisticaDokumen7 halamanResumen EstadisticaJhon SáenzBelum ada peringkat

- Toma de Decisiones Bajo ConflictoDokumen11 halamanToma de Decisiones Bajo ConflictoJuliette Aguilar100% (1)

- Labs - 3 y 4 Separación y Cuantificación de CaseinaDokumen5 halamanLabs - 3 y 4 Separación y Cuantificación de CaseinaRodrigo Alejandro Hurtado ValdiviaBelum ada peringkat

- Tesis Doctoral - Claudia MolinaDokumen343 halamanTesis Doctoral - Claudia MolinaLuis Gerardo Ponciano EstradaBelum ada peringkat

- Manaties Dugongos PDFDokumen1 halamanManaties Dugongos PDFJessica Aurora Fernández AguileraBelum ada peringkat

- Lectura Comprensiva Q&ADokumen74 halamanLectura Comprensiva Q&AGabriela Espín AlbánBelum ada peringkat

- Principios Baìsicos de HermeneìuticaDokumen2 halamanPrincipios Baìsicos de HermeneìuticagcdivadBelum ada peringkat

- Orthogonal Projection Onto Subspace Generated by Orthogonal List of Vectors Es PDFDokumen3 halamanOrthogonal Projection Onto Subspace Generated by Orthogonal List of Vectors Es PDFCarlos GarcíaBelum ada peringkat

- ExamenDokumen9 halamanExamenJesus Muñoz BalamBelum ada peringkat

- Sesión 5 - Concreto 1Dokumen19 halamanSesión 5 - Concreto 1Cinthya MegoBelum ada peringkat

- Modelo Informe SemestralDokumen4 halamanModelo Informe SemestralYanina Barriola Abad0% (1)

- An. Instr. II Informe 3 Validación de Un Método PotenciométricoDokumen6 halamanAn. Instr. II Informe 3 Validación de Un Método PotenciométricoPaul VargasBelum ada peringkat

- Manual TRASTORNOS DE APRENDIZAJEDokumen17 halamanManual TRASTORNOS DE APRENDIZAJELupitta AlonsoBelum ada peringkat

- Sintesis de FarmacosDokumen114 halamanSintesis de FarmacosRichard BarrenecheaBelum ada peringkat

- Teoría ArqueológicaDokumen10 halamanTeoría ArqueológicaRicardo Hernández SanchezBelum ada peringkat

- TESIS - Gestión para La Administración de La Materia Prima en El Área de Producción de La Industria GráficaDokumen87 halamanTESIS - Gestión para La Administración de La Materia Prima en El Área de Producción de La Industria GráficaINTELIGENCIA EDUCATIVABelum ada peringkat

- Nutricion Vegetariana Salud E - Ingrid PegueroDokumen36 halamanNutricion Vegetariana Salud E - Ingrid PegueroantonioBelum ada peringkat

- La Diosa InannaDokumen479 halamanLa Diosa InannaReina Sara Sanchez JimenezBelum ada peringkat

- Definicion de EmbriónDokumen4 halamanDefinicion de EmbriónCelso HernandezBelum ada peringkat

- Formato Guia de Componente Práctico Biologia AmbientalDokumen9 halamanFormato Guia de Componente Práctico Biologia AmbientalanthonyBelum ada peringkat

- Primera y Segunda Entrega Liderazgo 1Dokumen52 halamanPrimera y Segunda Entrega Liderazgo 1dexyBelum ada peringkat

- Biologia Coe2 2°medioDokumen6 halamanBiologia Coe2 2°medioTamara SepúlvedaBelum ada peringkat

- Unidad 1 La Ecología y Su Objeto de EstudioDokumen23 halamanUnidad 1 La Ecología y Su Objeto de EstudioGretser José Orellana MéndezBelum ada peringkat