31.Multi-Level Inverter Capable of Power Factor Control

Diunggah oleh

Venkatesan SwamyHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

31.Multi-Level Inverter Capable of Power Factor Control

Diunggah oleh

Venkatesan SwamyHak Cipta:

Format Tersedia

Multi-level Inverter Capable of Power Factor Control with DC Link Switches

Ho-Dong Sun1, Honnyong Cha1, Heung-Geun Kim1, Tae-Won Chun2, Eui-Cheol Nho3

1

Kyungpook National University, Daegu, Republic of Korea. 2 University of Ulsan, Ulsan, Republic of Korea. 3 Pukyong National University, Busan, Republic of Korea.

Abstract This paper proposes a new multi-level inverter topology based on a H-bridge structure with four switches connected to the dc-link. Based on a POD (Phase opposition disposition) modulation method, a new PWM method which requires only one carrier signal is suggested. The switching sequence to balance the capacitor voltage is also considered. In addition to these, the proposed topology requires minimum number of component count to increase the number of voltage level. Operating principle of the proposed inverter is verified through simulation and experiment.

TA1+ C1 TA2+

TB1+ TB2+

VDC + TA1C2 TA2(a) TA1+ C1 TA2+ TB2+ C4 TA1C2 TA2(b) TB2TB1TB1+ TB2TB1-

vo

_

I.

INTRODUCTION

Due to the increasing demand on the renewable energy sources, grid connected inverter systems are becoming more and more important than ever before [1,2]. For grid connected operation, the inverter should meet the following requirements. 1. The inverter has to generate a pure sinusoidal output voltage. 2. The inverter output current should have low total harmonic distortion (THD). Traditionally, two-level PWM inverter is used for grid-tied operation. In case of a two-level inverter, the switching frequency should be high or the inductance of the output filter inductor need to be big enough to satisfy the required THD. To cope with the problems associated with the two-level inverter, multi-level inverters (MLIs) are introduced for gridconnected inverter. Several MLI topologies have been suggested so far and they can be mainly classified as three types in Fig. 1; neutral point clamped (NPC), flying capacitor (FC), and cascaded type [3-5]. Advantage of the MLIs is that their switching frequency and device voltage rating can be much lower than those of a traditional two-level inverter for the same output voltage. Therefore, IGBT switching loss can be reduced significantly and thus the inverter system efficiency can be increased [6-8]. In this paper, a circuit based on a H-bridge topology with four switches connected to the dc-link is proposed as a MLI topology. Fig. 2 shows the proposed MLI. Also it is simple because the proposed PWM method uses one carrier signal for generating PWM signals. In addition, the switching sequence considering the voltage balance of dc-link was proposed. Finally, the proposed topology of the multi-level inverter is verified by showing the feasibility through the simulation and the experiment.

VDC

C3

vo

_

VDC/2 + -

S11

S13

+

S12 S14

vo

_

VDC/2 + -

S21

S23

S22

S24

(c)

Fig. 1. Topologies of multi-level inverters. (a) neutral point clamped (NPC) type. (b) Flying capacitor (FC) type. (c) Cascade type.

978-1-4577-1216-6/12/$26.00 2012 IEEE

1639

II.

PROPOSED MULTI-LEVEL INVERTER

A. Topology of multi-level inverter As shown in Fig. 2, the proposed MLI is composed of two dc-link capacitors (C1, C2) and four switching devices (TA+, TA-, TB+, TB-) comprising a H-bridge, and four active switches (TP+, TP-, TN+, TN-) located between dc-link and H-bridge. The voltage across the switching devices in the dc-link (TP+, TP-, TN+, TN-) is VDC/2 and operated at a switching frequency. Whereas, voltage across the switching devices in the H-bridge (TA+, TA-, TB+, TB-) is VDC and the switches (TA+, TA-, TB+, TB-) are switched at a frequency of the fundamental component of the output voltage (e.g. 50 or 60 Hz). Thus, the dc-link switches (TP+, TP-, TN+, TN-) and the Hbridge switches (TA+, TA-, TB+, TB-) can be strategically selected based on the rated power of the inverter system in order to reduce system cost and increase efficiency. Table I shows the output voltage according to the switching states.

B. Operating modes and proposed PWM strategy The output voltage of the proposed MLI shown in Fig. 2 has five levels (VDC, VDC/2, 0, -VDC/2, -VDC) according to the switching states of the inverter. There are four operation modes depending on the instantaneous value of the reference voltage, vref and the maximum value of the carrier signal, VC(see Fig. 4). Table II shows the possible inverter output voltage level according to the operating mode. In case of the N-level NPC type multi-level inverter, N-1 triangular carrier signals with the same frequency and amplitude are used so that they fully occupy contiguous bands over the range +VDC to -VDC. A single sinusoidal reference is compared with each carrier signal to determine the output voltage for the inverter. Three dispositions of the carrier signal are considered to generate the PWM signal [9-11]. 1) Phase disposition (PD); where all carriers are in phase. 2) Alternative phase opposition disposition (APOD); where each carrier is phase shifted by 180 degree from its adjacent carrier. Phase opposition disposition (POD); where the carriers above zero voltage are 180 degree out of phase with those below zero voltage.

C1

TP+ TPTN

+

TA+

TB+

3)

VDC

vo

_

TATB-

C2

T N-

Fig. 3 shows the reference signal and the carrier signal arrangements for PD modulation, POD modulation, and APOD modulation. A new PWM strategy based on POD modulation which requires only a single carrier signal (vcarrier) is proposed and the detailed PWM strategy is depicted in Fig. 4. If the

2Vc

Fig. 2. Proposed single-phase multi-level inverter topology.

vref

Vc

Output voltage (Vo) VDC VDC /2 0 -VDC /2 -VDC

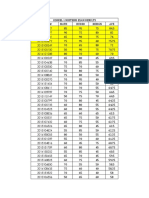

TABLE I Output voltage according to switching states Switching condition

TP+ ON OFF ON OFF OFF OFF ON ON TPOFF ON OFF ON ON ON OFF OFF TN+ OFF OFF ON ON ON OFF ON OFF TNON ON OFF OFF OFF ON OFF ON TA+, TBON ON ON ON OFF OFF OFF OFF TA-, TB+ OFF OFF OFF OFF ON ON ON ON

0

Vc

2Vc

2Vc Vc

vref

(a)

0

Vc

2Vc

2Vc Vc

(b)

vref

TABLE II Operating mode of the proposed MLI Operating mode Reference voltage range Output voltage Mode 1 Mode 2 Mode 3 Mode 4 Vcvref<2Vc 0vref<Vc -Vcvref<0 -2Vcvref<-Vc VDC/2 or VDC 0 or VDC -VDC/2 or 0 -VDC or -VDC/2

0

Vc

(c ) Fig. 3. Carrier and reference signal arrangements for: (a) Phase disposition (PD). (b) Alternative phase opposition disposition (APOD). (c) Phase opposition disposition (POD).

2Vc

1640

reference signal is positive, then the switch pair (TA+, TB-) are turned on, and if it is negative, then the switch pair (TA-, TB+) are turned on. Thus the switches composing the H bridge inverter turned on and turned off once during the period of the reference signal. The voltage across the switch at blocking state is VDC. The switches (TP-, TN+) are operated complementally to the switches (TP+, TN-). The generation of the PWM signal for dc-link switches (TP+, TN-) can be explained as follows. Mode 1: a signal subtracted from the reference signal by Vc is compared with the carrier signal. If vref -Vc> vcarrier, then all switches TP+ and TN- are turned on. If vref -Vc< vcarrier, then the switch TP+ or TN- is turned off alternately. Mode 2: the reference signal is directly compared with a carrier signal. If vref > vcarrier, then the switch TP+ or TN- is turned on alternately. If vref < vcarrier, then all switches TP+ and TN- are turned off. Mode 3: -vref is directly compared with a carrier signal. If -vref > vcarrier, then the switch TP+ or TN- is turned on alternately. If -vref < vcarrier, then all switches TP+ and TN- are turned off. Mode 4: a signal subtracted from -vref by Vc is compared with the carrier signal. If If -vref -Vc> vcarrier, then all switches TP+ and TN- are turned on. If -vref -Vc< vcarrier, then the switch TP+ or TN- is turned off alternately. Only one carrier signal is used to generate eight PWM signals in the proposed PWM method. Thus it is quite simple.

C. Voltage balancing of dc-link capacitor One of the important issues about multi-level inverter is the voltage balance of the dc-link capacitor. The voltage of capacitor C1 and C2 should be equally balanced to VDC/2. However the midpoint voltage fluctuates when C1 and C2 charge and discharge continuously. If the capacitor voltage is unbalanced, the output voltage becomes unsymmetrical and it results in a high harmonic content in the load current. To solve this problem, the switching state should be selected appropriately in Fig. 5. If only one switch in a dclink is turned on, the output voltage becomes VDC/2. In order to balance the voltage of dc-link capacitor, dc-link switches (TP+ , TN-) are alternately turned on at mode 2, and alternately turned off at mode 1. And switches (TP-, TN+) are operated complementally to switches (TP+ , TN-). Therefore, the switching sequence of mode 1 is (a)-(b)-(a)-(c), and the switching sequence of mode 2 is (d)-(b)-(d)-(c). The switching sequence of mode 3 and mode 4 are similar that of mode 1 and mode 2. The switching sequence of mode 3 is (h)-(f)-(h)(g), and the switching sequence of mode 4 is (e)-(f)-(e)-(g).

TP+ TP TN + TNT ATBTA + TB+ TP+ TP TN+ TNT ATBT A+ TB+

C1

C1

VDC +

v _o

VDC +

v _o

C2

C2

(a)

C1 TP+ TP TN TN+

(b)

TB+ C1 T P+ TP TN C2 TN+

TA +

VDC +

v _o

T ATB-

TA+

TB+

VDC +

v _o

TA T B-

C2

(c)

C1 TP+ TP TN C2 TN+

(d)

TB+ C1 TP+ TP TN TN+

TA +

VDC

v _o

TA

-

TA +

TB+

VDC

v _o

TA TB-

C2 TB-

(e)

C1 TP+ TP TN + C2 TNTA TBTA + TB+ C1 TP+ TP TN + TN-

(f)

TA + TB+

VDC +

v _o

VDC +

v _o

T ATB-

C2

(g)

(h)

Fig. 5. Switching states of the proposed inverter in one cycle.(a) state 1 : vo = 0. (b) state 2 : vo = VDC/2. (c) state 3 : vo = VDC/2. (d) state 4 : vo = VDC. (e) state 5 : vo = 0. (f) state 6 : vo = -VDC/2. (g) state 7 : vo = VDC/2. (h) state 8 : vo = VDC.

Fig. 4. PWM strategy based on POD with single carrier signal

1641

+ C11 TTP

TTPTA+ TB+

V1 -

+ TTN+

io

C12 TTN

+

vo

(a)

+ C21 TBP

TBPTATB-

V2 + TBN+ C22 TBN-

(b)

Fig. 6. Proposed 9-level inverter topology

D. Extension to 9-level inverter It should be noted that although the number of the switching devices in the proposed 5-level inverter (shown in Fig. 2) is the same as that of the conventional cascaded H-bridge MLI, the switches (TA+, TA-, TB+, TB-) in the proposed MLI are switched at a low frequency(60 Hz). Moreover, unlike the cascaded H-bridge MLI, the proposed 5-level inverter requires only one isolated voltage source, VDC. In order to maximize the effectiveness of the proposed MLI, 9-level inverter which was extended from 5-level inverter shown in Fig. 2 is also proposed in this paper and the overall circuit diagram is shown in Fig. 6. As shown in Fig. 6, in case of 9-level inverter, the proposed inverter requires less active devices than 9-level cascaded H-bridge MLI. Therefore, number of switching devices in the proposed MLI can be reduced significantly as the number of voltage level increases. III. SIMULATION AND EXPERIMENTAL RESULTS

(c) Fig. 7. Waveforms of 5-level inverter (Load : R = 9.3 ). (a) Output voltage of the inverter. (b) load voltage. (c) load current.

(a)

(b)

The proposed 5-level inverter is tested to verify the operating principle of the proposed MLI. The LC filter is inserted between the output of the inverter and the load. Electrical specifications of the proposed inverter are summarized in Table III. Fig. 7 and 8 show simulation waveforms of the proposed inverter in 5-level. Fig. 7 shows the waveforms of the inverter output voltage, load voltage and the load current when the power factor becomes unity. Fig. 8 shows the waveforms of the inverter output voltage, load voltage and the load current during the lagging power factor.

TABLE III Electrical specifications of the proposed single-phase 5-level inverter dc-link voltage 200V Output voltage dc-link capacitor Filter inductor (Lf) Filter capacitor (Cf) Switching frequency (fsw) Output frequency (fo) 110 Vrms 2200 uF 300 uH 150 uF 5 kHz 60 Hz

(c) Fig. 8. Waveforms of 5-level inverter (Load : R = 9.3 , L = 14.9mH). (a) Output voltage of the inverter. (b) load voltage. (c) load current.

Based on the simulation results, the experiment was conducted. Rating and the parameters of the system which was used in the experiment are the same with those of the simulation. Configuration for the experiment is shown in Fig. 9. Fig. 10 shows that the capacitor voltages (VC1, VC2) are controlled constantly. The capacitor voltages (VC1, VC2) are well balanced at the voltage of 100[V]. Fig. 11 shows the waveforms of the inverter output voltage, load voltage and the load current. The inverter output voltage is 5-level voltage and the load current and the load voltage waveforms are closer to the sinusoidal waveform. Experimental output waveforms can be found consistent with the simulation result.

1642

Cdc2

Lf

Cf

Load

Cdc1

Cdc3

1. Number of devices of the proposed multi-level inverter is fewer than that of the conventional multi-level inverters. Therefore, the proposed system is more reliable and cost competitive than the conventional two-level and multilevel inverters. 2. The four switches (TA+, TA-, TB+, TB-) in the H-bridge are switched at a low frequency (e.g. 60 Hz). Therefore, switching loss of The four switches (TA+, TA-, TB+, TB-) is almost negligible. 3. Only one carrier signal is required to generate the PWM signals for 4 switching devices (TP+, TP-, TN+, TN-). 4. The proposed topology can be easily extended to 9-level or higher level with minimized active device component count.

Source

Vdc

DC-link Switch signal PWM

Inverter Switch signal

i e

Controller

Fig. 9. Single phase inverter system

VC1

VC2

Acknowledgment This work was supported by the Power Generation & Electricity Delivery of the Korea Institute of Energy Technology Evaluation and Planning (KETEP) grant funded by the Korea government Ministry of Knowledge Economy (No. 20111020400260) VC1 =100V VC2 =100V [100V/div] [5msec/div] REFERENCES

[1] Conversion Structure for Grid-Connected PV Applications", IEEE Trans. Ind. Electron., vol. 56, no. 11, pp. 4416-4426, Nov. 2009. [2] N. A. Rahim, S. Mekhilef, Implementation of Three- Phase grid Connected Inverter for Photovoltaic Solar Power Generation System Proceedings IEEE. PowerCon 2002. Vol. 1, pp. 570-573., Oct 2002 [3] A. Nabae, I. Takahashi and H. Akagi, A New Neutral-Point-Clamped PWM Inverter IEEE Trans. Ind. Appl., vol. 1A-17, no. 5, pp. 518-523, Sep. 1981. [4] Y. Liang, C.O. Nwankpa, "A power-line conditioner based on flyingcapacitor multilevel voltage source converter with phase-shift SPWM" IEEE Trans. Industrial Electronics, Vol. 36, pp. 965-971, 2000. [5] E. Villanueva, P. Correa, M. Pacas, Control of a Single-Phase Cascaded H-Bridge Multilevel Inverter for Grid-Connected Photovoltaic Systems, IEEE Trans. Industrial Electronics, Vol. 56, pp. 4399-4406, 2009. [6] O. Lopez, R. Teodorescu, J. Doval-Gandoy, "Multilevel transformerless topologies for single-phase grid-connected converters" IEEE. IECON 2006, pp. 5191-5196, 2006. [7] Tae-Jin Kim, Dae-Wook Kang, Yo-Han Lee and Dong-Seok Hyun, The analysis of conduction and switching losses in multi-level inverter system, PESC. 2001 IEEE Vol. 3, pp 1363-1368, 2001. [8] D.A.B. Zambra, C. Rech, J.R. Pinheiro, "Comparison of Neutral-PointClamped, Symmetrical, and Hybrid Asymmetrical Multilevel Inverters", IEEE Trans. Ind. Electron., Vol. 57, no. 7, pp2297-2306, July 2010. [9] M. Calais, "Analysis of multicarrier PWM methods for a single-phase five level inverter", PESC. 2001 IEEE, Vol. 3, pp. 1351-1356, 2001. [10] B.P. McGrath, Multicarrier PWM strategies for multilevel inverters, IEEE Trans. Ind. Electron., Vol. 49, no. 4, pp. 858-867, 2002. [11] G. Carrara, S. Gardella, M. Marchesoni, R. Salutari, and G. Sciutto, "A new multilevel PWM method: A theoretical analysis", IEEE Trans. Power Electron., vol. 7, no. 3, pp. 497-505, July 1992.

G. Grandi, C. Rossi, D. Ostojic, D. Casadei, "A New Multilevel

Fig. 10. Voltage balancing waveforms of dc-link capacitor (C1, C2) .

vo [200V/div]

vload [100V/div] iload [20A/div]

[5msec/div]

Fig. 11. Waveforms of 5-level inverter ( Load : R = 9.3 , L = 14.9mH)

IV.

CONCLUSION

This paper proposed a new multi-level inverter topology based on a H-bridge inverter with four switches connected to the dc-link. The proposed MLI has the following advantages over the conventional inverters.

1643

Anda mungkin juga menyukai

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- PVC PLasticisersDokumen2 halamanPVC PLasticisersKrishna PrasadBelum ada peringkat

- Tunnel DamperDokumen8 halamanTunnel DamperIvanBelum ada peringkat

- Ikan Di Kepualauan Indo-AustraliaDokumen480 halamanIkan Di Kepualauan Indo-AustraliaDediBelum ada peringkat

- Wartsila CPP PaperDokumen4 halamanWartsila CPP Papergatheringforgardner9550Belum ada peringkat

- Digital Signal Processing PDFDokumen71 halamanDigital Signal Processing PDFMahesh Sambari100% (2)

- Bilstein SZ SL Sls 2010Dokumen16 halamanBilstein SZ SL Sls 2010Wimin HungBelum ada peringkat

- Curtis CatalogDokumen9 halamanCurtis CatalogtharngalBelum ada peringkat

- Create an access point for non-RouterOS laptop clientsDokumen8 halamanCreate an access point for non-RouterOS laptop clientsGorgeus WaffleBelum ada peringkat

- Electric Power Systems Research: P.K. Gayen, P. Roy Chowdhury, P.K. DharaDokumen14 halamanElectric Power Systems Research: P.K. Gayen, P. Roy Chowdhury, P.K. DharaVenkatesan SwamyBelum ada peringkat

- DC/DC Controller: Selection GuideDokumen28 halamanDC/DC Controller: Selection GuideVenkatesan SwamyBelum ada peringkat

- Important ThesisDokumen331 halamanImportant ThesisVenkatesan SwamyBelum ada peringkat

- CombinandodutyratioyfrequenceDAB DC ACDokumen11 halamanCombinandodutyratioyfrequenceDAB DC ACfiboBelum ada peringkat

- Design and Evaluation of A Novel Hybrid Sic-Gan Based Bidirectional Full-Bridge DC-DC ConverterDokumen7 halamanDesign and Evaluation of A Novel Hybrid Sic-Gan Based Bidirectional Full-Bridge DC-DC ConverterVenkatesan SwamyBelum ada peringkat

- 51 BidirectionalDokumen8 halaman51 BidirectionalDdBelum ada peringkat

- Buck Boost OrCADDokumen13 halamanBuck Boost OrCADCitharth MagendranBelum ada peringkat

- 25782-Article Text-89683-1-10-20200810Dokumen7 halaman25782-Article Text-89683-1-10-20200810Venkatesan SwamyBelum ada peringkat

- 25782-Article Text-89683-1-10-20200810Dokumen7 halaman25782-Article Text-89683-1-10-20200810Venkatesan SwamyBelum ada peringkat

- Journal Jpe 15-6 989210096Dokumen10 halamanJournal Jpe 15-6 989210096Venkatesan SwamyBelum ada peringkat

- Generalized Model of A Bidirectional DC-DC Converter: Nikolay Hinov, Dimitar Arnaudov and Dimitar PenevDokumen5 halamanGeneralized Model of A Bidirectional DC-DC Converter: Nikolay Hinov, Dimitar Arnaudov and Dimitar PenevVenkatesan SwamyBelum ada peringkat

- Reduction of Voltage Spike in The Isolated Bi-Directional Converter With Flyback SnubberDokumen10 halamanReduction of Voltage Spike in The Isolated Bi-Directional Converter With Flyback SnubberVenkatesan SwamyBelum ada peringkat

- Reduction of Voltage Spike in The Isolated Bi-Directional Converter With Flyback SnubberDokumen10 halamanReduction of Voltage Spike in The Isolated Bi-Directional Converter With Flyback SnubberVenkatesan SwamyBelum ada peringkat

- Monolithic Bidirectional Switch Based On GaN Gate Injection TransistorsDokumen6 halamanMonolithic Bidirectional Switch Based On GaN Gate Injection TransistorsVenkatesan SwamyBelum ada peringkat

- 51 BidirectionalDokumen8 halaman51 BidirectionalDdBelum ada peringkat

- Pid Ijrest 37201608 PDFDokumen4 halamanPid Ijrest 37201608 PDFErgin ÖzdikicioğluBelum ada peringkat

- Buck Boost OrCADDokumen13 halamanBuck Boost OrCADCitharth MagendranBelum ada peringkat

- Generalized Model of A Bidirectional DC-DC Converter: Nikolay Hinov, Dimitar Arnaudov and Dimitar PenevDokumen5 halamanGeneralized Model of A Bidirectional DC-DC Converter: Nikolay Hinov, Dimitar Arnaudov and Dimitar PenevVenkatesan SwamyBelum ada peringkat

- Reduction of Voltage Spike in The Isolated Bi-Directional Converter With Flyback SnubberDokumen10 halamanReduction of Voltage Spike in The Isolated Bi-Directional Converter With Flyback SnubberVenkatesan SwamyBelum ada peringkat

- Bidirectional DC To DC Converters: An Overview of Various Topologies, Switching Schemes and Control TechniquesDokumen6 halamanBidirectional DC To DC Converters: An Overview of Various Topologies, Switching Schemes and Control TechniquesVo Thanh TungBelum ada peringkat

- Energies 11 02560Dokumen15 halamanEnergies 11 02560Venkatesan SwamyBelum ada peringkat

- Energies 11 02560Dokumen15 halamanEnergies 11 02560Venkatesan SwamyBelum ada peringkat

- 25782-Article Text-89683-1-10-20200810Dokumen7 halaman25782-Article Text-89683-1-10-20200810Venkatesan SwamyBelum ada peringkat

- ZVS-ZCS Bidirectional Full-Bridge DC-DC ConverterDokumen6 halamanZVS-ZCS Bidirectional Full-Bridge DC-DC ConverterVenkatesan SwamyBelum ada peringkat

- Pid Ijrest 37201608 PDFDokumen4 halamanPid Ijrest 37201608 PDFErgin ÖzdikicioğluBelum ada peringkat

- Electronics: Design and Realization of A Bidirectional Full Bridge Converter With Improved Modulation StrategiesDokumen16 halamanElectronics: Design and Realization of A Bidirectional Full Bridge Converter With Improved Modulation StrategiesVenkatesan SwamyBelum ada peringkat

- Monolithic Bidirectional Switch Based On GaN Gate Injection TransistorsDokumen6 halamanMonolithic Bidirectional Switch Based On GaN Gate Injection TransistorsVenkatesan SwamyBelum ada peringkat

- Ee8591 Digital Signal Processing Part B & Part C Questions: Anna University Exams Regulation 2017Dokumen2 halamanEe8591 Digital Signal Processing Part B & Part C Questions: Anna University Exams Regulation 2017Venkatesan SwamyBelum ada peringkat

- MEENAKSHI RAMASWAMY ENGINEERING COLLEGE DIGITAL SIGNAL PROCESSING MODEL EXAM QUESTIONSDokumen2 halamanMEENAKSHI RAMASWAMY ENGINEERING COLLEGE DIGITAL SIGNAL PROCESSING MODEL EXAM QUESTIONSVenkatesan SwamyBelum ada peringkat

- Pneumatic Tyres: CMR Engineering CollegeDokumen17 halamanPneumatic Tyres: CMR Engineering CollegeHemanth Rama Krishna YernagulaBelum ada peringkat

- 3RP15 05-1aDokumen3 halaman3RP15 05-1atycristinaBelum ada peringkat

- 08 Candelaria Punta Del Cobre IOCG Deposits PDFDokumen27 halaman08 Candelaria Punta Del Cobre IOCG Deposits PDFDiego Morales DíazBelum ada peringkat

- dp0 PDFDokumen4 halamandp0 PDFSimonBelum ada peringkat

- GAS-INSULATED SWITCHGEAR MODELS 72kV ADVANCED ENVIRONMENTALLY FRIENDLYDokumen6 halamanGAS-INSULATED SWITCHGEAR MODELS 72kV ADVANCED ENVIRONMENTALLY FRIENDLYBudi SantonyBelum ada peringkat

- Bill of Material: The Hanover CompanyDokumen17 halamanBill of Material: The Hanover CompanyLIVIABelum ada peringkat

- Ey-H3l Yh1576Dokumen44 halamanEy-H3l Yh1576jorgeBelum ada peringkat

- Module 1 Introduction To Highway and Railroad EngineeringDokumen43 halamanModule 1 Introduction To Highway and Railroad EngineeringKenneth FajardoBelum ada peringkat

- Probability Statistics and Random Processes Third Edition T Veerarajan PDFDokumen3 halamanProbability Statistics and Random Processes Third Edition T Veerarajan PDFbhavyamBelum ada peringkat

- Crystal Chem Crystallography: - Chemistry Behind Minerals and How They Are AssembledDokumen33 halamanCrystal Chem Crystallography: - Chemistry Behind Minerals and How They Are AssembledArkodip MandalBelum ada peringkat

- F (X, Y) Sin (Xy) + X LN (Y) Find F at (0, )Dokumen9 halamanF (X, Y) Sin (Xy) + X LN (Y) Find F at (0, )muhammad abrarBelum ada peringkat

- LyonDCCT Technology ReviewDokumen4 halamanLyonDCCT Technology Reviewrajagopal gBelum ada peringkat

- Recommended Procedures For Internet-Based Connections Between Rths and Nmcs (VPN, Ipsec)Dokumen38 halamanRecommended Procedures For Internet-Based Connections Between Rths and Nmcs (VPN, Ipsec)Crismaruc Maria-madalinaBelum ada peringkat

- Practice Workbook LR Method For Addition Subtraction PDFDokumen4 halamanPractice Workbook LR Method For Addition Subtraction PDFEsa KhanBelum ada peringkat

- SUBstation Equipmens TLDokumen12 halamanSUBstation Equipmens TLJecer Casipong NuruddinBelum ada peringkat

- 01-Jul-21 03:32 PMDokumen6 halaman01-Jul-21 03:32 PMramBelum ada peringkat

- Midterm Exam Result Ce199-1l 2Q1920Dokumen3 halamanMidterm Exam Result Ce199-1l 2Q1920RA CarpioBelum ada peringkat

- Valve Actuator Data SheetDokumen1 halamanValve Actuator Data SheetRob StorrowBelum ada peringkat

- Technical Data: Pump NameDokumen6 halamanTechnical Data: Pump Nameسمير البسيونىBelum ada peringkat

- Superconductivity in RH S and PD Se: A Comparative StudyDokumen5 halamanSuperconductivity in RH S and PD Se: A Comparative StudyChithra ArulmozhiBelum ada peringkat

- Seminar SPM Additional Mathematics 3472/2: Zuhaila Binti Mohd AliDokumen52 halamanSeminar SPM Additional Mathematics 3472/2: Zuhaila Binti Mohd AliIt's nuhaBelum ada peringkat

- Serial Port InterfacingDokumen5 halamanSerial Port Interfacingyampire100% (1)

- Lecture 2 Principle of EMRDokumen33 halamanLecture 2 Principle of EMRizhar engkuBelum ada peringkat