Arquitectura de Harvard

Diunggah oleh

Manuel VillarroelHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Arquitectura de Harvard

Diunggah oleh

Manuel VillarroelHak Cipta:

Format Tersedia

La arquitectura de computadoras

La arquitectura de computadoras es el diseo conceptual y la estructura operacional fundamental de un sistema de computadora. Es decir, es un modelo y una descripcin funcional de los requerimientos y las implementaciones de diseo para varias partes de una computadora, con especial inters en la forma en que la unidad central de proceso (UCP) trabaja internamente y accede a las direcciones de memoria. Tambin suele definirse como la forma de seleccionar e interconectar componentes de hardware para crear computadoras segn los requerimientos de funcionalidad, rendimiento y costo. El ordenador recibe y enva la informacin a travs de los perifricos por medio de los canales. La UCP es la encargada de procesar la informacin que le llega al ordenador. El intercambio de informacin se tiene que hacer con los perifricos y la UCP. Todas aquellas unidades de un sistema exceptuando la UCP se denomina perifrico, por lo que el ordenador tiene dos partes bien diferenciadas, que son: la UCP (encargada de ejecutar programas y que esta compuesta por la memoria principal, la UAL y la UC) y los perifricos (que pueden ser de entrada, salida, entrada-salida y comunicaciones).

Arquitectura de Harvard.

El termino arquitectura Harvard proviene de la computadora Harvard Mark I, se encarga de almacenar instrucciones en cintas perforadas y los datos en interrupciones. Es la misma arquitectura de computadoras, posee dispositivos de almacenamiento que se encuentran separados fsicamente para los datos y las instrucciones. Las partes principales de las computadoras es la memoria y la CPU, la primera guarda los datos y la CPU los procesa. A travs de la memoria no solo se pueden manejar los datos sino tambin el lugar donde se encuentran almacenados, estos dos parmetros son de mucha importancia para la CPU. Todas las computadoras constan principalmente de dos partes, la CPU que procesa los datos, y la memoria que guarda los datos. Cuando hablamos de memoria manejamos dos parmetros, los datos en s, y el lugar donde se encuentran almacenados (o direccin). Los dos son importantes para la CPU, pues muchas instrucciones frecuentes se traducen a algo as como "coge los

datos de sta direccin y adelos a los datos de sta otra direccin", sin saber en realidad qu es lo que contienen los datos. En los ltimos aos la velocidad de las CPUs ha aumentado mucho en comparacin a la de las memorias con las que trabaja, as que se debe poner mucha atencin en reducir el nmero de veces que se accede a ella para mantener el rendimiento. Si, por ejemplo, cada instruccin ejecutada en la CPU requiere un acceso a la memoria, no se gana nada incrementando la velocidad de la CPU - este problema es conocido como 'limitacin de memoria'.

Ventajas de la arquitectura Harvard

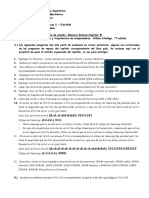

a) el tamao de las instrucciones no esta relacionado con el de los datos, y por lo tanto puede ser optimizado para que cualquier instruccin ocupe una sola posicin de memoria de programa, logrando as mayor velocidad y menor longitud de programa, b) el tiempo de acceso a las instrucciones puede superponerse con el de los datos, logrando una mayor velocidad de operacin. En contraste con una arquitectura de Von Neumann, la arquitectura Harvard es definitivamente la ganadora en velocidad, pero no en conveniencia a la hora de ejecutar grupos de instrucciones distintas. Un ejemplo de computadoras programables que usan la arquitectura Harvard, son los famosos PIC.

"Diversos modelos de PIC's"

Desventajas de la arquitectura Harvard

Una pequea desventaja de los procesadores con arquitectura Harvard, es que deben poseer instrucciones especiales para acceder a tablas de valores constantes que pueda ser necesario incluir en los programas, ya que estas tablas se encontraran fsicamente en la memoria de programa (por ejemplo en la EPROM de un microprocesador).

Arquitectura de von Neumann (princeton)

La arquitectura de von Neumann es una familia de arquitecturas de computadoras que utilizan el mismo dispositivo de almacenamiento tanto para las instrucciones como para los datos (a diferencia de la arquitectura Harvard). La mayora de computadoras modernas estn basadas en esta arquitectura, aunque pueden incluir otros dispositivos adicionales, (por ejemplo, para gestionar las interrupciones de dispositivos externos como ratn, teclado, etc).

Origen de la arquitectura de von Neumann

El nacimiento u origen de la arquitectura Von Neumann surge a raz de una colaboracin en el proyecto ENIAC del matemtico de origen hngaro, John Von Neumann. Este trabajaba en 1947 en el laboratorio atmico de Los Alamos cuando se encontr con uno de los constructores de la ENIAC. Compaero de Albert Einstein, Goedel y Turing en Princeton, Von Neumann

se interes por el problema de la necesidad de "recablear" la mquina para cada nueva tarea. Organizacin de la arquitectura de von Neumann Los ordenadores con esta arquitectura constan de cinco partes: La unidad aritmtico-lgica o ALU, la unidad de control, la memoria, un dispositivo de entrada/salida y el bus de datos que proporciona un medio de transporte de los datos entre las distintas partes. Un ordenador con esta arquitectura realiza o emula los siguientes pasos secuencialmente: 1. Enciende el ordenador y obtiene la siguiente instruccin desde la memoria en la direccin indicada por el contador de programa y la guarda en el registro de instruccin. 2. Aumenta el contador de programa en la longitud de la instruccin para apuntar a la siguiente. 3. Decodifica la instruccin mediante la unidad de control. sta se encarga de coordinar el resto de componentes del ordenador para realizar una funcin determinada. 4. Se ejecuta la instruccin. sta puede cambiar el valor del contador del programa, permitiendo as operaciones repetitivas. El contador puede cambiar tambin cuando se cumpla una cierta condicin aritmtica, haciendo que el ordenador pueda 'tomar decisiones', que pueden alcanzar cualquier grado de complejidad, mediante la aritmtica y lgica anteriores. 5. Vuelve al paso 1. Desarrollo del concepto de programa almacenado El matemtico Alan Turing, quien haba sido alertado de un problema de lgica matemtica por las lecciones de Max Newman en la Universidad de Cambridge, escribi un artculo en 1936 titulado On Computable Numbers, with an Application to the Entscheidungs problem, que fue publicado en los Proceedings of the London Mathematical Society. En l describa una mquina hipottica que llam mquina computadora universal, y que ahora es conocida como la Mquina de Turing. La mquina hipottica tenia un almacenamiento infinito (memoria en la terminologa actual) que contena tanto las instrucciones como los datos. El ingeniero alemn Konrad Zuse

escribi de forma independiente sobre este concepto en 1936. Von Neumann conoci a Turing cuando ejerca de profesor sustituto en Cambridge en 1935 y tambin durante el ao que Turing pas en la Universidad de Princeton en 1936-37. Cuando supo del artculo de 1936 de Turing no est claro.

Desventaja de la arquitectura Von Neumann

Pero no todo es amor y felicidad en la tierra de Von Neumann. La separacin que se obtiene entre el CPU y la memoria da como resultado una de las obsesiones mas grandes de la industria del hardware: el famoso cuello de botella. El problema radica, en que la CPU esta continuamente forzada a esperar a que los datos sean transportados desde o hacia la memoria RAM, ms que todo debido a la diferencia entre la taza de transferencia de datos que existen entre la CPU y la RAM.

"Imagen de ejemplo de un cuello de botella"

Cul es la diferencia entre Arquitectura Von Neumann y Arquitectura de Harvard?

La principal diferencia entre la arquitectura Harvard y la arquitectura Von Neumann se encuentra en los datos de la arquitectura Von Neumann y los programas se almacenan en la memoria de la misma y gestionado por el mismo sistema de manejo de informacin. Considerando que los datos de las tiendas de la arquitectura de Harvard y programas en los dispositivos de memoria independiente y que son manejados por diferentes subsistemas. Por supuesto, hay otras diferencias, pero lo mencionado es la diferencia ms profunda que la distingue en trminos de capacidades y usos. En un equipo que utiliza la arquitectura Von Neumann, sin cach, la unidad de procesamiento central (CPU) puede ser la lectura y la instruccin o la escritura / lectura de datos a / desde la memoria. Ambas de estas operaciones no pueden ocurrir simultneamente, como los datos e instrucciones de uso del bus del sistema mismo. En un equipo que utiliza la arquitectura de Harvard, la CPU puede leer una instruccin y los datos de acceso a la memoria al mismo tiempo, sin memoria cach. Esto significa que una computadora con arquitectura Harvard, potencialmente puede ser ms rpido para un circuito determinado por la complejidad de acceso a datos y la instruccin no se obtiene alegan para el uso de una va nica de memoria.

Diferencias entre la arquitectura Princeton y Harvard

Arquitectura Princeton La memoria de programa y la memoria de datos se hallan sobre un nico espacio de memoria. Arquitectura Harvard La memoria de programa y la memoria de datos constituyen dos espacios de memoria separados

Al espacio nico de memoria se accede mediante un nico bus de direcciones y un nico bus de datos/instrucciones. Es la arquitectura tpica de los grandes microcomputadores (Ordenadores personales).

Tambin se encuentra en algunos microcontroladores (por ejemplo, NEC).

El acceso a cada espacio de memoria puede llegar a ser mediante buses distintos, es decir, puede haber dos buses de direcciones, un bus de datos y un bus de instrucciones). Lo ms habitual es que exista un nico bus de direcciones, en cuyo caso debe existir alguna seal de control que permita diferenciar a que espacio de memoria se hace referencia (por ejemplo, seales de READ, WRITE y FETCH). Es la arquitectura propia de un buen nmero de microcontroladores (por ejemplo, PIC).

Arquitectura de entrada y salida

En arquitectura de computadoras, a la combinacin de una unidad central de procesamiento (CPU) y memoria principal (aqulla que la CPU puede escribir o leer directamente mediante instrucciones individuales) se la considera el corazn de la computadora y cualquier movimiento de informacin desde o hacia ese conjunto se lo considera entrada/salida. La CPU y su circuitera complementaria proveen mtodos de entrada/salida que se usan en programacin de bajo nivel para la implementacin de controladores de dispositivos. Los sistemas operativos y lenguajes de programacin de ms alto nivel brindan conceptos y primitivas de entrada/salida distintos y ms abstractos. Por ejemplo, un sistema operativo brinda aplicativos que manejan el concepto de archivos. El lenguaje de programacin C define funciones que les permiten a sus programas realizar E/S a travs de streams, es decir, les permiten leer datos desde y escribir datos hacia sus programas. Una alternativa para las funciones primitivas especiales es la mnada de E/S, que permite que los programas describan su E/S y que las acciones se lleven a cabo fuera del programa. Esto resulta interesante, pues las funciones de E/S introduciran un efecto colateral para cualquier lenguaje de programacin, pero ahora una programacin puramente funcional resultara prctica.

Es importante notar que la designacin de un dispositivo, sea de entrada o de salida, cambia al cambiar la perspectiva desde el que se lo ve. Los teclados y ratones toman como entrada el movimiento fsico que el usuario produce como salida y lo convierten a una seal elctrica que la computadora pueda entender. La salida de estos dispositivos son una entrada para la computadora. De manera anloga, los monitores e impresoras toman como entrada las seales que la computadora produce como salida. Luego, convierten esas seales en representaciones inteligibles que puedan ser interpretadas por el usuario. La interpretacin ser, por ejemplo, por medio de la vista, que funciona como entrada.

La arquitectura de memoria compartida

La arquitectura de memoria compartida puede suponer la separacin de la memoria en partes compartidas distribuidas entre los nodos y la memoria principal; o la distribucin de toda la memoria en los distintos nodos. Un protocolo de coherencia, escogido de acuerdo a un modo de consistencia, se encarga de mantener la coherencia de la memoria En computacin, la Distributed Shared Memory (DSM, o memoria distribuida compartida) es un tipo de implementacin hardware y software, en la que cada nodo de un cluster tiene acceso a una amplia memoria compartida que se aade a la memoria limitada privada, no compartida, propia de cada nodo. Los sistemas de software DSM pueden ser implementados bajo un sistema operativo (SO), o como una biblioteca de programacin. Los sistemas de software DSM implementados en el SO pueden concebirse como extensiones de la arquitectura de memoria virtual subyacente. Estos sistemas son transparentes al desarrollador, lo que significa que la memoria distribuida subyacente est completamente oculta para los usuarios. En contraste, los sistemas de software DSM implementados en una biblioteca no son transparentes y los desarrolladores tienen que programarlos separadamente. Sin embargo, estos ltimos sistemas ofrecen mejores caractersticas de portabilidad en la implementacin de sistemas DSM. Los sistemas de software DSM tambin tienen capacidad para organizar la regin de memoria compartida de manera flexible. Las aproximaciones basadas en pginas organizan la memoria compartida en pginas de tamao fijo. Por su parte, las aproximaciones basadas en objetos organizan la regin

como un espacio abstracto en el que se pueden almacenar objetos compartidos de tamao variable.

Tres Modelos de Computadores de Memoria Compartida

1. Uniform Memory Access (UMA) En sistemas con uniform memory access (acceso a memoria uniforme), cada procesador tiene acceso directo a una sola memoria compartida. Todas las ubicaciones de la memoria son equidistantes (en cuanto a tiempos de acceso) a cada procesador. La mayora de los sistemas UMA incorpora cach para eliminar las disputas de la memoria pero este mecanismo no se ve desde las aplicaciones. 2. Non uniform Memory Access (NUMA) Sistemas con nonuniform memory access (acceso a memoria no uniforme) tienen una memoria fsica compartida distribuida . Cada particin de esta memoria se ata directamente a un nodo pero se puede acceder a ella por procesadores en otro nodos via la red de interconexin. As, los tiempos de acceso a la memoria difieren dependiendo de si la ubicacin requerida es local al nodo o remota a este. Este nivel de complejidad agregado puede ser escondido del software de aplicacin pero hacer esto lleva a un desempeo suboptimo. Para hacer mejor uso del hardware, el programador debe tomar la arquitectura en consideracin. El cache se usa entre procesadores y memoria local asi como entre nodos. Mquinas con cach coherente a nivel del hardware se llaman ccNUMA. 3. Cache-only Memory Architecture (COMA) Sistemas con cache only memory access (acceso a memoria solo en caches) no tiene memoria compartida fsica, pero el cache solo constituye la memoria de las mquinas. Se provee un solo espacio fsico de direcciones pero los tiempos de acceso varan dependientemente si la ubicacin de la memoria requerida est en el cach local o en uno remoto. El software de aplicacin ignorara la arquitectura del sistema ya que la mquina se comporta en forma muy parecida a una mquina UMA con cach.

Anda mungkin juga menyukai

- Excel AvanzadoDokumen39 halamanExcel AvanzadoCinthia Olivera LoayzaBelum ada peringkat

- Actividad 3. Ejercicios de Windows 10Dokumen12 halamanActividad 3. Ejercicios de Windows 10Eva100% (1)

- Practica 5 ColorDokumen2 halamanPractica 5 ColorfernandarcosBelum ada peringkat

- Cuadro Comparativo RecursividadDokumen3 halamanCuadro Comparativo RecursividadAngel Ulises Ortiz RojasBelum ada peringkat

- Guia Ceneval para El Area de Redes para LSC de La UABCDokumen14 halamanGuia Ceneval para El Area de Redes para LSC de La UABCLamadridL100% (2)

- Lenguajes de Alto y Bajo NivelDokumen7 halamanLenguajes de Alto y Bajo NivelStephan FassbenderBelum ada peringkat

- Arquitectura de Los MicrocontroladoresDokumen15 halamanArquitectura de Los MicrocontroladoresJoel RinconBelum ada peringkat

- Practica ALU - CLRDokumen8 halamanPractica ALU - CLRRaúl Olmos EstradaBelum ada peringkat

- Guia Taller Capitulo VDokumen1 halamanGuia Taller Capitulo VjhondogBelum ada peringkat

- Autómatas y Lenguajes Formales - Tarea 3Dokumen6 halamanAutómatas y Lenguajes Formales - Tarea 3Juan David DuranBelum ada peringkat

- Presentación - 243008 - Control Numérico ComputarizadoDokumen6 halamanPresentación - 243008 - Control Numérico Computarizadojuan diegoBelum ada peringkat

- Aspectos Basicos de La Computacion ParalelaDokumen6 halamanAspectos Basicos de La Computacion ParalelaCésar IvánBelum ada peringkat

- Convertidores DAC ADCDokumen3 halamanConvertidores DAC ADCCristihan Criollo100% (1)

- Trabajo Colaborativo 2 Arquitectura de Computadores Consolidado FinalDokumen7 halamanTrabajo Colaborativo 2 Arquitectura de Computadores Consolidado FinalJhonatan Florez Obando0% (1)

- Simulación ensamblador MSX88Dokumen14 halamanSimulación ensamblador MSX88LeonardoBelum ada peringkat

- Tarea 2 - Angela Maria Perez Mesa - Grupo 202016896 - 116Dokumen8 halamanTarea 2 - Angela Maria Perez Mesa - Grupo 202016896 - 116Angela PerezBelum ada peringkat

- Maquinas de Estado FinitoDokumen66 halamanMaquinas de Estado FinitoDouglas Victorio Irineo Zegarrundo TorricoBelum ada peringkat

- Ejercicios de conversión de autómatas finitos a expresiones regularesDokumen8 halamanEjercicios de conversión de autómatas finitos a expresiones regularesJeimy AlbornozBelum ada peringkat

- Uso de La Herramienta Nmap y ZenmapDokumen3 halamanUso de La Herramienta Nmap y Zenmapaura martinez100% (1)

- SISTEMAS PROGRAMABLES (Sensores Opticos)Dokumen4 halamanSISTEMAS PROGRAMABLES (Sensores Opticos)alberto michelBelum ada peringkat

- Construcción de Un Analizador SemánticoDokumen2 halamanConstrucción de Un Analizador SemánticoEric RiveraBelum ada peringkat

- 1 IkDokumen8 halaman1 IkDavid A CostaBelum ada peringkat

- Mapa ConceptualDokumen4 halamanMapa ConceptualEdward NetzlaffBelum ada peringkat

- Resumen Unidad 2 GraficacionDokumen18 halamanResumen Unidad 2 GraficacionLopez OlgaBelum ada peringkat

- Matlab Aplicado A La Robotica y Mecatronica IndexDokumen12 halamanMatlab Aplicado A La Robotica y Mecatronica IndexDaeva_RaidriarBelum ada peringkat

- Trabajo Colaborativo 1 Fase 1 y Fase 2 RoboticaDokumen15 halamanTrabajo Colaborativo 1 Fase 1 y Fase 2 RoboticaMauricio RodriguezBelum ada peringkat

- Aplicacion de La Norma Iso 9126Dokumen16 halamanAplicacion de La Norma Iso 9126Diego Alejandro Uribe BlatnikBelum ada peringkat

- SO introDokumen69 halamanSO introJuan Carlos Hipolito ToscoyoaBelum ada peringkat

- Comparativo de técnicas de multiplexación: FDM, TDM, CDM y WDMDokumen2 halamanComparativo de técnicas de multiplexación: FDM, TDM, CDM y WDMDavid Montiel RamirezBelum ada peringkat

- Caracteristica y Comparaciones Con Motorola, ATM, PICDokumen6 halamanCaracteristica y Comparaciones Con Motorola, ATM, PICAndres Castro VacaBelum ada peringkat

- Programacion HibridaDokumen11 halamanProgramacion HibridaMstechnologies Jafet0% (2)

- Taller para Programación en Lenguaje de C++Dokumen3 halamanTaller para Programación en Lenguaje de C++Julian VasquezBelum ada peringkat

- Procesador IA-32 - Modo ProtegidoDokumen199 halamanProcesador IA-32 - Modo ProtegidoYer Ko100% (1)

- Lenguaje Ensamblador PDFDokumen14 halamanLenguaje Ensamblador PDFGerardo DávilaBelum ada peringkat

- Act 5Dokumen4 halamanAct 5miguel_zh92Belum ada peringkat

- 1 2 4 5 Packet Tracer Network Representation1Dokumen5 halaman1 2 4 5 Packet Tracer Network Representation1Alexander CastroBelum ada peringkat

- Procesadores SuperescalaresDokumen2 halamanProcesadores SuperescalaresWendyBelum ada peringkat

- Etapa4 - Implementación de La Interfaz Del Sistema - Jose AlexisDokumen6 halamanEtapa4 - Implementación de La Interfaz Del Sistema - Jose AlexisEdinson Medina RiveraBelum ada peringkat

- Calidad de Software Tarea 1Dokumen14 halamanCalidad de Software Tarea 1William Fernando GarciaBelum ada peringkat

- DFDDokumen21 halamanDFDNay AvilésBelum ada peringkat

- Practica 1Dokumen3 halamanPractica 1SebastianSalazarBelum ada peringkat

- Metricas en POODokumen26 halamanMetricas en POOIntiJulian666Belum ada peringkat

- Requerimientos para Instalar Labview y MatlabDokumen3 halamanRequerimientos para Instalar Labview y MatlabValery Rodriguez100% (1)

- Temario MicrocontroladoresDokumen2 halamanTemario MicrocontroladoresArchival RangelBelum ada peringkat

- Elementos y Características de La Arquitectura de Von NeumannDokumen7 halamanElementos y Características de La Arquitectura de Von NeumannSanchez BernabeBelum ada peringkat

- LabVIEW para programación de FPGA Spartan-3EDokumen4 halamanLabVIEW para programación de FPGA Spartan-3EVictoria YánezBelum ada peringkat

- Cuestionario FrameworksDokumen1 halamanCuestionario FrameworksdankenzonBelum ada peringkat

- Cuestionario Comunicaciones InalambricasDokumen8 halamanCuestionario Comunicaciones InalambricasDaniel Osko50% (2)

- Mapa Mental Lenguajes y AutómatasDokumen1 halamanMapa Mental Lenguajes y AutómatasJuan RamirezBelum ada peringkat

- Atoolo PDFDokumen4 halamanAtoolo PDFJulio CésarBelum ada peringkat

- Guia Segundo Parcial-3Dokumen45 halamanGuia Segundo Parcial-3Alejandra hernandezBelum ada peringkat

- Arquitecturas Von Neumann y Harvard: Diferencias y ventajasDokumen5 halamanArquitecturas Von Neumann y Harvard: Diferencias y ventajasandres neira100% (1)

- Examen AlgoritmosDokumen5 halamanExamen AlgoritmosVikingoVikingoBelum ada peringkat

- Control Digital DirectoDokumen1 halamanControl Digital DirectoAlejandro Garcia GonzalezBelum ada peringkat

- Computadoras SuperescalaresDokumen36 halamanComputadoras SuperescalaresLawiet ElleBelum ada peringkat

- Robot Seguidor de LineaDokumen34 halamanRobot Seguidor de LineaMateo Fernandez Ivonne OsorioBelum ada peringkat

- TP3 Relevamiento y RequerimientosDokumen6 halamanTP3 Relevamiento y RequerimientosInteligencia Artificial UnamBelum ada peringkat

- Sistema de Control - (Carrito Seguidor de Linea)Dokumen16 halamanSistema de Control - (Carrito Seguidor de Linea)Ronaldo MendietaBelum ada peringkat

- Visual Basic ModuloDokumen136 halamanVisual Basic ModuloJRangel JRangel100% (1)

- Trabajo Autonomo 4 Resolucion Ejercicios Utilizando VHDLDokumen7 halamanTrabajo Autonomo 4 Resolucion Ejercicios Utilizando VHDLHomeroOjedaBelum ada peringkat

- Evidencia #1Dokumen7 halamanEvidencia #1Berenice KztroBelum ada peringkat

- Actividad 3.1 Arquitecturas Von Neumman y HarvardDokumen5 halamanActividad 3.1 Arquitecturas Von Neumman y HarvarddiegoBelum ada peringkat

- Informatica Juridica Tarea 2Dokumen3 halamanInformatica Juridica Tarea 2Carlos Martinez GrullonBelum ada peringkat

- Práctico N°9 Parte III - Bibliografia Complementaria-Interfaz TeCo (SG2 - Client)Dokumen3 halamanPráctico N°9 Parte III - Bibliografia Complementaria-Interfaz TeCo (SG2 - Client)GeroBelum ada peringkat

- Tarea 4 - SIG Grupo 10Dokumen32 halamanTarea 4 - SIG Grupo 10liseth sernaBelum ada peringkat

- E Tarea 6 Representación de Números RealesDokumen6 halamanE Tarea 6 Representación de Números RealesgermanBelum ada peringkat

- Manual de Manejo de Driver Guide ToolkitDokumen1 halamanManual de Manejo de Driver Guide ToolkitAlan TheproxBelum ada peringkat

- Informe Previo 8Dokumen8 halamanInforme Previo 8Ronal HbBelum ada peringkat

- 3 - Guía POODokumen27 halaman3 - Guía POOluis lopBelum ada peringkat

- Bases de datos del colegio San Jorge normalizadasDokumen4 halamanBases de datos del colegio San Jorge normalizadasLibis GonzalezBelum ada peringkat

- Resumen Hardware y SoftwareDokumen3 halamanResumen Hardware y SoftwareDaniela Soto TorresBelum ada peringkat

- Sistema de CCTVDokumen6 halamanSistema de CCTVSergio Goicochea EspinozaBelum ada peringkat

- Paper MatlabDokumen2 halamanPaper MatlabBladimirHidalgôBelum ada peringkat

- CBJRRJFRNGJRMN 5488665 JDokumen24 halamanCBJRRJFRNGJRMN 5488665 JJAIME ANTONIO CORIA MONTIELBelum ada peringkat

- Codes YsDokumen9 halamanCodes Ys01-II-HU-MAITE RUDY PEREZ CHANCASANAMPABelum ada peringkat

- Cómo recuperar archivos de USB dañadaDokumen11 halamanCómo recuperar archivos de USB dañadaLuis PargaBelum ada peringkat

- Desarrollo de Un Programa en Python para Gestionar Una BibliotecaDokumen34 halamanDesarrollo de Un Programa en Python para Gestionar Una BibliotecaCamilo BernalBelum ada peringkat

- OtorDokumen2 halamanOtorDiegoAleBelum ada peringkat

- Diplomado Mecatrónica Procesos ManufacturaDokumen5 halamanDiplomado Mecatrónica Procesos ManufacturaADAN FRANCISCO GONZALEZ GOMEZBelum ada peringkat

- Certamen ADADokumen3 halamanCertamen ADATlv Roxa'n LiaBelum ada peringkat

- Proyecto de RastreoDokumen9 halamanProyecto de RastreoMidwar HenryBelum ada peringkat

- Lista de Precios Trading 03.08.2022Dokumen108 halamanLista de Precios Trading 03.08.2022Jander GomezBelum ada peringkat

- HC12tutorial TasmDokumen150 halamanHC12tutorial TasmGrim BichoSoftBelum ada peringkat

- Silabo Administración de Base de DatosDokumen7 halamanSilabo Administración de Base de DatosSeguros rsslcBelum ada peringkat

- Crear y modificar registros CMDB Remedy ForceDokumen9 halamanCrear y modificar registros CMDB Remedy Forcejean carlosBelum ada peringkat

- Informe de Mantenimiento y ReparacionDokumen9 halamanInforme de Mantenimiento y ReparacionRandixBelum ada peringkat

- Diagrama de red LAN y asignación de direccionesDokumen7 halamanDiagrama de red LAN y asignación de direccionesOsara PerezBelum ada peringkat

- Monografia BeatrizQuisbert DanielChipana FINALDokumen61 halamanMonografia BeatrizQuisbert DanielChipana FINALMike WasouskiBelum ada peringkat

- Laboratorio 01 - VMware - Instalación y Configuración de ESXi 7.0Dokumen20 halamanLaboratorio 01 - VMware - Instalación y Configuración de ESXi 7.0andreBelum ada peringkat

- Distribuciónes LTSDokumen8 halamanDistribuciónes LTSgladys.ivannia.30Belum ada peringkat