74LCX86

Diunggah oleh

Alexandre S. CorrêaDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

74LCX86

Diunggah oleh

Alexandre S. CorrêaHak Cipta:

Format Tersedia

74LCX86 Low Voltage Quad 2-Input Exclusive-OR Gate with 5V Tolerant Inputs

March 1995 Revised January 2001

74LCX86 Low Voltage Quad 2-Input Exclusive-OR Gate with 5V Tolerant Inputs

General Description

The LCX86 contains four 2-input exclusive-OR gates. The inputs tolerate voltages up to 7V allowing the interface of 5V systems to 3V systems. The 74LCX86 is fabricated with advanced CMOS technology to achieve high speed operation while maintaining CMOS low power dissipation.

Features

s 5V tolerant inputs s 2.3V3.6V VCC specifications provided s 6.5 ns tPD max (VCC = 3.3V), 10 A ICC max s Power down high impedance inputs and outputs s 24 mA output drive (VCC = 3.0V) s Implements patented noise/EMI reduction circuitry s Latch-up performance exceeds 500 mA s ESD performance: Machine model > 2000V Human model > 200V

Ordering Code:

Order Number 74LCX86M 74LCX86SJ 74LCX86MTC Package Number M14A M14D MTC14 Package Description 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter X to the ordering code.

Logic Symbol

IEEE/IEC

Connection Diagram

Pin Descriptions

Pin Names A0A3 B0B3 O0O3 Description Inputs Inputs Outputs

2001 Fairchild Semiconductor Corporation

DS012415

www.fairchildsemi.com

74LCX86

Absolute Maximum Ratings(Note 1)

Symbol VCC VI VO IIK IOK IO ICC IGND TSTG Parameter Supply Voltage DC Input Voltage DC Output Voltage DC Input Diode Current DC Output Diode Current DC Output Source/Sink Current DC Supply Current per Supply Pin DC Ground Current per Ground Pin Storage Temperature Value Conditions Units V V Output in HIGH or LOW State (Note 2) VI < GND VO < GND VO > VCC V mA mA mA mA mA

0.5 to +7.0 0.5 to +7.0 0.5 to VCC + 0.5 50 50 +50 50 100 100 65 to +150

Recommended Operating Conditions (Note 3)

Symbol VCC VI VO IOH/IOL Supply Voltage Input Voltage Output Voltage Output Current HIGH or LOW State VCC = 3.0V 3.6V VCC = 2.7V 3.0V VCC = 2.3V 2.7V TA Free-Air Operating Temperature Input Edge Rate, VIN = 0.8V2.0V, VCC = 3.0V Parameter Operating Data Retention Min 2.0 1.5 0 0 Max 3.6 3.6 5.5 VCC Units V V V mA

24 12 8 40

0 85 10

C

ns/V

t/V

Note 1: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the Absolute Maximum Ratings. The Recommended Operating Conditions table will define the conditions for actual device operation. Note 2: IO Absolute Maximum Rating must be observed. Note 3: Unused inputs must be held HIGH or LOW. They may not float.

DC Electrical Characteristics

Symbol VIH VIL VOH Parameter HIGH Level Input Voltage LOW Level Input Voltage HIGH Level Output Voltage IOH = 100A IOH = -8 mA IOH = 12 mA IOH = 18 mA IOH = 24 mA VOL LOW Level Output Voltage IOL = 100A IOL = 8mA IOL = 12 mA IOL = 16 mA IOL = 24 mA II IOFF ICC ICC Input Leakage Current Power-Off Leakage Current Quiescent Supply Current Increase in ICC per Input 0 VI 5.5V VI or VO = 5.5V VI = VCC or GND 3.6V VI 5.5V VIH = VCC 0.6V Conditions VCC (V) 2.3 2.7 2.7 3.6 2.3 2.7 2.7 3.6 2.3 3.6 2.3 2.7 3.0 3.0 2.3 3.6 2.3 2.7 3.0 3.0 2.3 3.6 0 2.3 3.6 2.3 3.6 2.3 3.6 VCC - 0.2 1.8 2.2 2.4 2.2 0.2 0.6 0.4 0.4 0.55 5.0 10 10 10 500 A A A A V V TA = 40C to +85C Min 1.7 2.0 0.7 0.8 Max V V Units

www.fairchildsemi.com

74LCX86

AC Electrical Characteristics

TA = 40C to +85C, RL = 500 Symbol Parameter VCC = 3.3V 0.3V CL = 50 pF Min tPHL tPLH tOSHL tOSLH Output to Output Skew (Note 4) Propagation Delay 1.5 1.5 Max 6.5 6.5 1.0 1.0 VCC = 2.7V CL = 50 pF Min 1.5 1.5 Max 7.0 7.0 VCC = 2.5V 0.2V CL = 30 pF Min 1.5 1.5 Max 7.8 7.8 ns ns Units

Note 4: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (tOSHL) or LOW-to-HIGH (tOSLH).

Dynamic Switching Characteristics

Symbol VOLP VOLV Parameter Quiet Output Dynamic Peak VOL Quiet Output Dynamic Valley VOL Conditions CL = 50 pF, VIH = 3.3V, VIL = 0V CL = 30 pF, VIH = 2.5V, VIL = 0V CL = 50 pF, VIH = 3.3V, VIL = 0V CL = 30 pF, VIH = 2.5V, VIL = 0V VCC (V) 3.3 2.5 3.3 2.5 TA = 25C Typical 0.8 0.6 0.8 0.6 Units V V

Capacitance

Symbol CIN COUT CPD Input Capacitance Output Capacitance Power Dissipation Capacitance Parameter Conditions VCC = Open, VI = 0V or VCC VCC = 3.3V, VI = 0V or VCC VCC = 3.3V, VI = 0V or VCC, f = 10 MHz Typical 7 8 25 Units pF pF pF

www.fairchildsemi.com

74LCX86

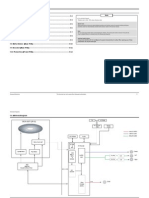

AC Loading and Waveforms Generic for LCX Family

FIGURE 1. AC Test Circuit (CL includes probe and jig capacitance) Test tPLH, tPHL tPZL, tPLZ tPZH,tPHZ Switch Open 6V at VCC = 3.3 0.3V VCC x 2 at VCC = 2.5 0.2V GND

Waveform for Inverting and Non-Inverting Functions

3-STATE Output Low Enable and Disable Times for Logic

Propagation Delay, Pulse Width and trec Waveforms

Setup Time, Hold TIme and Recovery TIme for Logic

3-STATE Output High Enable and Disable TImes for Logic FIGURE 2. Waveforms

trise and tfall

(Input Pulse Characteristics; f = 1MHz, tr = tf = 3ns) Symbol Vmi Vmo Vx Vy VCC 3.3V 0.3V 1.5V 1.5V VOL + 0.3V VOH 0.3V 2.7V 1.5V 1.5V VOL + 0.3V VOH 0.3V 2.5V 0.2V VCC/2 VCC/2 VOL + 0.15V VOH 0.15V

www.fairchildsemi.com

74LCX86

Schematic Diagram Generic for LCX Family

www.fairchildsemi.com

74LCX86

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow Package Number M14A

www.fairchildsemi.com

74LCX86

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide Package Number M14D

www.fairchildsemi.com

74LCX86 Low Voltage Quad 2-Input Exclusive-OR Gate with 5V Tolerant Inputs

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC14

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. www.fairchildsemi.com 8 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

Anda mungkin juga menyukai

- Manual 2016 Nitro g5Dokumen2 halamanManual 2016 Nitro g5Alexandre S. CorrêaBelum ada peringkat

- Vistabule 2014 Feb Brochure LRDokumen10 halamanVistabule 2014 Feb Brochure LRAlexandre S. CorrêaBelum ada peringkat

- Optical Comp Exp - Edu SilvaDokumen6 halamanOptical Comp Exp - Edu SilvaAlexandre S. CorrêaBelum ada peringkat

- Manual Transistor PDFDokumen4 halamanManual Transistor PDFAlexandre S. CorrêaBelum ada peringkat

- The UltralightDokumen20 halamanThe UltralightAlexandre S. Corrêa100% (2)

- Build "Wild Goose": A Sturdy Overnight TrailerDokumen7 halamanBuild "Wild Goose": A Sturdy Overnight TrailerAlexandre S. CorrêaBelum ada peringkat

- F e A T U R e SDokumen2 halamanF e A T U R e SAlexandre S. CorrêaBelum ada peringkat

- Modular CNC Router 2009v1 FREE PLANSDokumen10 halamanModular CNC Router 2009v1 FREE PLANSModularCNC57% (7)

- CCE TV HPS-2071B Diagrama EsquematicoDokumen1 halamanCCE TV HPS-2071B Diagrama EsquematicoDaniel AvecillaBelum ada peringkat

- Schematic Diagrams: Special NoteDokumen12 halamanSchematic Diagrams: Special NoteAlexandre S. Corrêa100% (1)

- 4HD D0049.0611 - 06FDokumen104 halaman4HD D0049.0611 - 06FCarlosLimaBelum ada peringkat

- 1947 Trailer For TwoDokumen7 halaman1947 Trailer For TwoAlexandre S. CorrêaBelum ada peringkat

- Schematic Diagram DVD-P370Dokumen8 halamanSchematic Diagram DVD-P370Alexandre S. Corrêa0% (1)

- Sansung CL21A551MLDokumen9 halamanSansung CL21A551MLleno2Belum ada peringkat

- 74574Dokumen6 halaman74574Alexandre S. CorrêaBelum ada peringkat

- 74688Dokumen4 halaman74688Alexandre S. CorrêaBelum ada peringkat

- Cold Cold HOT HOT: QFP80 QFP80Dokumen1 halamanCold Cold HOT HOT: QFP80 QFP80Jone Ferreira Dos SantosBelum ada peringkat

- Yamaha Receiver Rxv-595 SchematicDokumen7 halamanYamaha Receiver Rxv-595 SchematicMauricio Bumba100% (1)

- XR-A550 XR-A330: Stereo CD Cassette Deck ReceiverDokumen82 halamanXR-A550 XR-A330: Stereo CD Cassette Deck ReceiverAlexandre S. CorrêaBelum ada peringkat

- 74573Dokumen4 halaman74573jamesrychurdBelum ada peringkat

- Build Your Own VAWT by David MussellDokumen17 halamanBuild Your Own VAWT by David MussellMr Void100% (9)

- Datasheet 7400Dokumen9 halamanDatasheet 7400gab50Belum ada peringkat

- Tip41-2 20wDokumen3 halamanTip41-2 20wAlexandre S. CorrêaBelum ada peringkat

- TDA2002 10wDokumen21 halamanTDA2002 10wAlexandre S. CorrêaBelum ada peringkat

- DC Da90Dokumen24 halamanDC Da90Alexandre S. CorrêaBelum ada peringkat

- TL 074Dokumen10 halamanTL 074Alexandre S. CorrêaBelum ada peringkat

- ICL7106 and ICL7107 VoltmeterDokumen16 halamanICL7106 and ICL7107 VoltmeterAntonino ScordatoBelum ada peringkat

- Ta 8403 KDokumen5 halamanTa 8403 KFlorenz RemasteredBelum ada peringkat

- 802Dokumen4 halaman802BooksBelum ada peringkat

- 74VHCU04Dokumen6 halaman74VHCU04Alexandre S. CorrêaBelum ada peringkat

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- CMOS Analog Design PDFDokumen1 halamanCMOS Analog Design PDFRanjith DevulapalliBelum ada peringkat

- Basic Characteristics of Digital IcsDokumen17 halamanBasic Characteristics of Digital IcsfgkloBelum ada peringkat

- M.E. Applied ElectronicsDokumen40 halamanM.E. Applied ElectronicsRaja RamachandranBelum ada peringkat

- JESD204B Survival GuideDokumen101 halamanJESD204B Survival Guidenguyentienduy1512Belum ada peringkat

- Latch UpDokumen4 halamanLatch UpCherry AbhiBelum ada peringkat

- Slva700 PDFDokumen8 halamanSlva700 PDFPadmo PadmundonoBelum ada peringkat

- Description of TTL, ECL and CMOS Glue Logic FamiliesDokumen2 halamanDescription of TTL, ECL and CMOS Glue Logic Familiesapi-26100966Belum ada peringkat

- Data Sheet: 74LVC2G07Dokumen13 halamanData Sheet: 74LVC2G07Le DungBelum ada peringkat

- Cmos Analog Ic Design FundamentalsDokumen395 halamanCmos Analog Ic Design FundamentalsLeandro PollanoBelum ada peringkat

- 1 Mbit (128K X 8) Parallel EEPROM With Software Data ProtectionDokumen22 halaman1 Mbit (128K X 8) Parallel EEPROM With Software Data ProtectionvanmarteBelum ada peringkat

- Infra-Red CAR-KEY Transmitter: OM1058 in Case SO-8Dokumen4 halamanInfra-Red CAR-KEY Transmitter: OM1058 in Case SO-8lepicane7Belum ada peringkat

- 428L2 PDFDokumen13 halaman428L2 PDFesquisof100% (1)

- A6841 DABiC-5 8-Bit Serial Input Latched Sink DriversDokumen10 halamanA6841 DABiC-5 8-Bit Serial Input Latched Sink DriversJennifer NealBelum ada peringkat

- Memory OrganisationDokumen57 halamanMemory OrganisationArunava SarkarBelum ada peringkat

- Comic X Penthouse n4 PDF by Doberman WWW Cantabriatorrent NetDokumen2 halamanComic X Penthouse n4 PDF by Doberman WWW Cantabriatorrent NetCory0% (1)

- CMOS-LOCOS - 01 Manual PDFDokumen53 halamanCMOS-LOCOS - 01 Manual PDFFernando Sánchez HernándezBelum ada peringkat

- CMOS Translinear CellsDokumen4 halamanCMOS Translinear CellsSumitChoudharyBelum ada peringkat

- Concept MapDokumen18 halamanConcept MapSriramBelum ada peringkat

- On-Chip ESD Protection Design For IcsDokumen14 halamanOn-Chip ESD Protection Design For IcsMK BricksBelum ada peringkat

- I - Hierarchy of Limits of Power PDFDokumen12 halamanI - Hierarchy of Limits of Power PDFmonishabe23100% (2)

- 100 HzsquarewavenonsmdsourceDokumen3 halaman100 HzsquarewavenonsmdsourceDavidDiriloBelum ada peringkat

- Cad of Electronics Lab: MbreaknDokumen4 halamanCad of Electronics Lab: MbreaknAnonymous eWMnRr70qBelum ada peringkat

- Not Gate Using Transistor - Google SearchDokumen2 halamanNot Gate Using Transistor - Google SearchHimanshu KumarBelum ada peringkat

- NL 49Dokumen23 halamanNL 49teomondoBelum ada peringkat

- Field Effect TransistorDokumen43 halamanField Effect TransistorArif IstiaqBelum ada peringkat

- Datasheet IC ULN Series-AllegroDokumen50 halamanDatasheet IC ULN Series-AllegroLokesh KumarBelum ada peringkat

- DEE6113 - Practical Work3 PDFDokumen8 halamanDEE6113 - Practical Work3 PDFFonzBahari67% (3)

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Dokumen2 halamanPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirBelum ada peringkat

- VLSI Design (Online Lectures) Assignment-1Dokumen3 halamanVLSI Design (Online Lectures) Assignment-1TarushiBelum ada peringkat

- Dynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)Dokumen15 halamanDynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)himanshu chandrakarBelum ada peringkat