RF and Wireless Asics: Applications

Diunggah oleh

SriramJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

RF and Wireless Asics: Applications

Diunggah oleh

SriramHak Cipta:

Format Tersedia

RF ICs ASICs / ECE6108

RF and Wireless ASICs

For wireless customers with high volume and/or who are developing products for new emerging markets, Maxim's ASICs offer a persuasive means of boosting integration and reducing cost. If you are designing in well-known high-volume markets, our ASICs enable you to "lock up" your circuit-design intellectual property (IP) from the competition. Emerging market customers not only enjoy the security of their IP, but also the significant cost savings over employing existing catalog parts. Applications:

Cellular/PCS, Including Both Handheld Terminals and Infrastructure Direct Broadcast Services via Satellite Global Position System Receivers Wireless/Broadband Radios Cable TV

Typical Blocks Suitable for Integration:

Sriram Sundar S / ECE

RF ICs ASICs / ECE6108

Circuit Design Examples: GPS Receiver with Integrated Synthesizer: The Symmetricom GPS RF front end with integrated synthesizer IC is a key element in a high performance GPS receiver. The front end, implemented on a GST-2 Quick Chip 9-60D, downconverts the RF signal (L1:1575MHz) to a final IF (15.42MHz) with differential output to enable three level adaptive digitization for high receiver selectivity. A low-phase-noise, on-chip, VCO-based frequency synthesizer generates all required on-chip local oscillators. Utilizing a double-conversion superheterodyne with external SAW filters, high levels of image rejection and blocking immunity are possible.

A Single Chip Silicon Bipolar Receiver for GPS/GLONASS Applications: The topic describes a silicon bipolar ASIC design for high-end GPS receivers that delivers a reference frequency and IF outputs to allow for tracking of GLONASS satellites. The 3.2mm receiver operates at a minimum supply voltage of 2.7V, over -40C to +85C temperature range. It has a 4dB noise figure (including RF filters), a total on-chip gain of 130dB, and an IIP3 of -31dBm. An RF/IF silicon bipolar ASIC, ROCIII (receiver-on-a-chip) has been designed to deliver a receiver solution for a range of GPS/GLONASS products aimed at the professional marketplace. These applications include synchronization of cellular base stations (high blocking immunity) and survey grade receivers with sub-cm accuracy (low amplitude and phase noise). The ROCIII delivered successful performance after a single design pass and has now gone into production. The ASIC is packaged in chip-on-board (COB) modules that also contain the extra passive components and control loops. Each COB module is targeted at a specific set of

Sriram Sundar S / ECE

RF ICs ASICs / ECE6108

applications and has the advantage of being a rugged component that can be directly placed on a digital motherboard using standard, surface mount, manufacturing techniques.

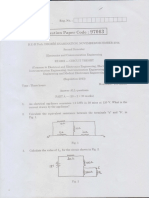

Figure 1 : Simplified schematic of ROCIII embedded in a GPS/GLONASS COB module A simplified schematic of the ROCIII, embedded in a GPS/GLONASS COB module is contained in Figure 1. The 1.91mm x 1.71mm ASIC was designed on the Maxim GST-2 silicon bipolar process with a headline Ft of 27GHz. It operates from a supply voltage of 2.7V to 3.3V and draws a DC current of 53mA. The operating temperature range is -40 to +85C. Gain, noise figure and input referred IP3 (IIP3) information for each stage and the complete receiver is contained in Table 1. The receiver employs a dual down-conversion scheme that offers good frequency selectivity and high attenuation of image responses that could compromise out-ofband jamming performance. Another advantage is the extra stability margin that is afforded via gain distribution between RF, 1st IF and 2nd IF frequencies, especially given that the total on-chip operating gain for nominal AGC conditions is 130dB. 1st LO radiation is also low which is important for multiple receiver systems.

Sriram Sundar S / ECE

RF ICs ASICs / ECE6108

Table 1. Gain, noise figure and IP3 for ROCIII circuits and complete receiver. Circuit Preselect filter LNA NF dB Gain dB 1 2.2 -1 18 -2.5 25 -16 36 -1 11 40 4.0 109.5 Two pole ceramic No external match required 1575 MHz RF SAW Voltage Lossy match on input conversion gain Comments

Image reject filter 2.5 RF downconverter 10.8 1st IF filter 16

135 MHz SAW Effective IP3 cut-off point NF includes 100 differential input termination off-chip discrete LC filter Operating at 7dB below maximum gain

IF downconverter 10.1 2 IF filter Variable gain amp Fixed gain amp Total Receiver

nd

A key feature of the receiver is that it combines good linearity with a high level of RF gain that allows for a high selectivity, but high insertion loss, SAW device as the 1st IF filter. This filter delivers a high degree of close to carrier jamming margin as well as acting as an effective 3rd order intermod. product cut-off point. Figure 2 contains a plot of jamming powers close to carrier for a ROCIII COB module compared to a GPS receiver that has been designed specifically for C/A-code military applications. The improvement of up to 40dB is very significant. Both receivers give similar blocking performance at the main cellular transmit bands of 940 and 1840MHz. Note that the in-band jamming power is limited by the carrier tracking loop bandwidth in the DSP. The frequency response of the GPS strip of the receiver is contained in Figure 3 and was obtained by sweeping the RF input frequency from 1570.42MHz to 1580.42MHz and recording the GPS 2nd IF output.

Figure 2. Comparison of close-to carrier jamming powers for ROCIII module and commercial receiver.

Sriram Sundar S / ECE

RF ICs ASICs / ECE6108

Figure 3. Swept frequency response of receiver's GPS strip, relative scale on Y-axis. The frequency plan captured in the ROCIII operates from a low cost reference of 20MHz and has RF=1575.42MHz, 1st IF=135.42MHz, 2nd IF=15.42MHz. A separate output at 90MHz is provided from the ROCIII synthesiser that acts as a reference for an external, low cost GLONASS IF module. This module is based around two commercial ICs, a VHF downconverter and a dual modulus prescaler. Extra division within this module (f/160) provides a PLL comparison frequency of 0.5625MHz that exactly equals the GLONASS channel spacing and hence allows the unit to select the various GLONASS satellites. The VHF downconverter is driven via an IF filter by the ROCIII RF mixer outputs.

Figure 4. Noise figure over frequency for ROCIII LNA at three Vcc values. The LNA uses a 2 stage shunt/series feedback topology and does not require external matching. The DC supply is delivered via a l/4 stripline connected to the output port and the circuit is self-biasing. A plot of noise figure over the band of interest and at three Vcc levels is

Sriram Sundar S / ECE

RF ICs ASICs / ECE6108

contained in Figure 4. The measured performance detailed in Table 1 compares well with the simulation results obtained from Maxim's SPICE based Analog Design System (ADS) which are Gain=18.5dB, NF=2.4dB and IIP3=-13.9dBm. The RF downconverter is based on a double balanced Gilbert cell with LO drive provided from a low impedance differential pair. Both the Gilbert cell and LO drive are PTAT biased via a classical arrangement. Bias current for both stages is optimised to minimise noise figure, maximise IP3 and maximise gain. The RF input is matched externally via a lossy match technique. The typical source for this circuit is a single-ended, 50 RF SAW used as an image reject filter. The IF output is delivered via low output impedance emitter followers and is suitable for driving directly the 135MHz IF SAW. The deliberate mismatch keeps the group delay distortion of the SAW within an acceptable level by attenuation of the triple-transit response. One aspect of circuit performance not covered in Table 1 is LO power at mixer RF input = 49dBm (equivalent to 40dB LO to RF isolation). The IF down-converter has a preamplifier plus Gilbert cell type topology with PTAT biasing. The circuit has been optimised to deliver a high level of conversion gain with good noise figure. A differential input termination resistor (off-chip) of 100 is used to minimise SAW group delay distortion. The moderate IIP3 value of -28dBm for this circuit is more than adequate given the relatively narrow bandwidth of the preceding 1st IF SAW (2.8MHz). The variable gain amplifier compensates for total receiver gain variation to ensure that the noise signal delivered to the 3-level digitiser is always at the correct level for optimum coding. In conjunction with the DSP, the VGA also implements an adaptive digitisation threshold scheme that helps to mitigate against in-band jamming signals. The circuit has a useful gain control range of greater than 60dB, with a maximum gain level of 18dB. Both the absolute gain level, gain range and gain slope have been compensated for temperature and supply variations. The gain control input is processed by a control signal compensation amplifier before being applied to the VGA current steering core. This compensation amplifier is based around a multi-tanh doublet input stage that provides a very linear gain slope. The fixed gain amplifier circuit provides 40dB of differential, DC coupled gain and can deliver close to 1V of single ended swing before entering compression. It is designed to drive either a separate digitiser or a companion digital ASIC (under design). In order to ensure that the total swing is available over the complete temperature range, the final output stage is biased from a source that delivers constant current with temperature rather than PTAT. The core of the L-band VCO is based on a common collector Clapp topology with square root PTAT biasing and signal extraction from the base node. This circuit has been optimised for low noise, high signal swing without asymmetrical clipping and maximum resonator loaded Q. The signal is fed to two limiting amplifier structures that are designed to deliver constant signal swing over temperature. The circuit operates with an external wire wound inductor and varactor diode. Figure 5 contains a plot of the reciprocal of the reflection coefficient at the VCO's resonator port over temperature and supply voltage. The phase noise at 100kHz offset is 103dBc/Hz, this figure can be improved by 5dB using coaxial ceramic resonator.

Sriram Sundar S / ECE

Anda mungkin juga menyukai

- EC8661 VLSI Design LaboratoryDokumen53 halamanEC8661 VLSI Design LaboratorySriram100% (4)

- 2014 - Apr May PDFDokumen4 halaman2014 - Apr May PDFSriramBelum ada peringkat

- MeasurementsDokumen12 halamanMeasurementsSriramBelum ada peringkat

- Data Path Circuits - EC6601Dokumen10 halamanData Path Circuits - EC6601SriramBelum ada peringkat

- EC6612 - VLSI Design Laboratory ManualDokumen39 halamanEC6612 - VLSI Design Laboratory ManualSriramBelum ada peringkat

- Circuit Theory 2014 - Apr MayDokumen6 halamanCircuit Theory 2014 - Apr MaySriramBelum ada peringkat

- VLSI Design Lab EC-6612-nDokumen58 halamanVLSI Design Lab EC-6612-nSriramBelum ada peringkat

- Principles of Management: Lesson PlanDokumen23 halamanPrinciples of Management: Lesson PlanSriram100% (1)

- Ec6512 Communication Systems Laboratory ManuslDokumen86 halamanEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- EC6702Dokumen2 halamanEC6702SriramBelum ada peringkat

- Design Entry and Simulation of Sequential CircuitsDokumen7 halamanDesign Entry and Simulation of Sequential CircuitsSriramBelum ada peringkat

- Wireless Communication - EC 2401 - I - Answer KeyDokumen9 halamanWireless Communication - EC 2401 - I - Answer KeySriramBelum ada peringkat

- Sensors: SL - N o Application Sensor Example PriceDokumen6 halamanSensors: SL - N o Application Sensor Example PriceSriramBelum ada peringkat

- What Determines The Color of An LED?: SemiconductingDokumen1 halamanWhat Determines The Color of An LED?: SemiconductingSriramBelum ada peringkat

- Ec 6501Dokumen1 halamanEc 6501SriramBelum ada peringkat

- EC2354 - VLSI DesignDokumen2 halamanEC2354 - VLSI DesignSriramBelum ada peringkat

- DSP WorkshopDokumen2 halamanDSP WorkshopSriramBelum ada peringkat

- Ec6512 Communication Systems Laboratory ManuslDokumen86 halamanEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- VerilogDokumen12 halamanVerilogSriramBelum ada peringkat

- ECE Department Course DetailsDokumen151 halamanECE Department Course DetailsSriramBelum ada peringkat

- Concept MapDokumen18 halamanConcept MapSriramBelum ada peringkat

- Kalasalingam University ECE302 Analog Communication Question BankDokumen6 halamanKalasalingam University ECE302 Analog Communication Question BankSriramBelum ada peringkat

- Ece 2013Dokumen14 halamanEce 2013SriramBelum ada peringkat

- Verilog Course ManualDokumen60 halamanVerilog Course ManualSriramBelum ada peringkat

- Ec2357 - Vlsi Design LaboratoryDokumen45 halamanEc2357 - Vlsi Design LaboratorySriramBelum ada peringkat

- SEMESTER Requirements Lab EquipmentDokumen29 halamanSEMESTER Requirements Lab EquipmentSriramBelum ada peringkat

- Ece 2008Dokumen27 halamanEce 2008SriramBelum ada peringkat

- Verilog Lab ProgramsDokumen25 halamanVerilog Lab ProgramsSriramBelum ada peringkat

- Analog DesignDokumen4 halamanAnalog DesignSriramBelum ada peringkat

- VerilogDokumen12 halamanVerilogSriramBelum ada peringkat

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- MSM6000 Chipset SolutionDokumen4 halamanMSM6000 Chipset SolutionRafael Hernández100% (1)

- Design of An Interactive Smart Refrigerator Based On Embeddes SystemsDokumen4 halamanDesign of An Interactive Smart Refrigerator Based On Embeddes SystemsVyshnaviBelum ada peringkat

- Re: Engineering Mechanics: Dynamics 6th Edition, Meriam, Kraige Solutions ManualDokumen10 halamanRe: Engineering Mechanics: Dynamics 6th Edition, Meriam, Kraige Solutions ManualtosafBelum ada peringkat

- Sbi QuesDokumen92 halamanSbi QuesNavdeep SinghBelum ada peringkat

- AMIE Recommended BooksDokumen2 halamanAMIE Recommended BooksSujeet SharmaBelum ada peringkat

- Built in Logic Block Observer (BILBO)Dokumen14 halamanBuilt in Logic Block Observer (BILBO)Mr Predator100% (5)

- Information and Communication Technology For SHS Part 1Dokumen22 halamanInformation and Communication Technology For SHS Part 1Samuel Teyemensah Kubi100% (1)

- Digital Logic Handbook 1975-76Dokumen711 halamanDigital Logic Handbook 1975-76Kevin G. RhoadsBelum ada peringkat

- Adeola Project New FRM Chapter 1 To 4Dokumen26 halamanAdeola Project New FRM Chapter 1 To 4Ajewole Eben Tope100% (1)

- TF2202 Sistem Logika DigitalDokumen130 halamanTF2202 Sistem Logika DigitalfisikamedikokeBelum ada peringkat

- Introduction To Comsol OptionalDokumen220 halamanIntroduction To Comsol OptionalJasleen KaurBelum ada peringkat

- Cost EstimatingDokumen3 halamanCost EstimatingMesha Atkinson0% (2)

- Resume - Sachin RavindranDokumen1 halamanResume - Sachin RavindranJosh pokeBelum ada peringkat

- DSP Architecture PDFDokumen353 halamanDSP Architecture PDFNhật TrungBelum ada peringkat

- Jss1 Wk6aDokumen4 halamanJss1 Wk6aKelvin NTAHBelum ada peringkat

- Course Schedule3Dokumen3 halamanCourse Schedule3Matin Sadat BeheshtiBelum ada peringkat

- Slya021 PDFDokumen31 halamanSlya021 PDFShahul Hameed KBelum ada peringkat

- Prize Box ManualDokumen21 halamanPrize Box ManualMaom OsorioBelum ada peringkat

- 4.2022 11 04 (I Iii) eDokumen29 halaman4.2022 11 04 (I Iii) esiyamsankerBelum ada peringkat

- Lecture 4 - Wafer CleanDokumen24 halamanLecture 4 - Wafer Cleanimage05Belum ada peringkat

- Mmic 1Dokumen15 halamanMmic 1Prithish Chand S PBelum ada peringkat

- ECE218 Lab Manual Digital Circuits GuideDokumen60 halamanECE218 Lab Manual Digital Circuits GuideYen Binh Nguyen100% (2)

- Introduction to VLSI TechnologyDokumen5 halamanIntroduction to VLSI TechnologyanupvasuBelum ada peringkat

- Vlsi Unit-IDokumen45 halamanVlsi Unit-Isuneelanubolu7Belum ada peringkat

- Fabrication Layout Design Rules 2005Dokumen28 halamanFabrication Layout Design Rules 2005lai_infoBelum ada peringkat

- BEng (EEE) Third Year Electives and Internships GuideDokumen21 halamanBEng (EEE) Third Year Electives and Internships GuideYan YantonoBelum ada peringkat

- ES106-CFP-Module 1 - Computer OrganizationDokumen74 halamanES106-CFP-Module 1 - Computer OrganizationKija Yeon100% (1)

- L34 ProcessVariationDokumen49 halamanL34 ProcessVariationsanju012Belum ada peringkat

- TextbookDokumen138 halamanTextbookNgô Việtt AnnhBelum ada peringkat

- Manual Service 50UHD 9M32BDokumen44 halamanManual Service 50UHD 9M32BOfelia GiménezBelum ada peringkat