Ijaiem 2013 07 24 086

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Ijaiem 2013 07 24 086

Hak Cipta:

Format Tersedia

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 7, July 2013 ISSN 2319 - 4847

ANALYTICAL SOLUTION OF 3D POISSION EQUATION USING SEPERATION OF VARIABLE METHOD

Prashant Mani1, ManojKumarPandey2

1 Research Scholar, 2Director Department of Electronics and Communication Engineering , SRM University NCR Campus Ghaziabad

ABSTRACT

This paper focuses a solution of three dimensional poission equation using separation of variable method for Fully Depleted Silicon on Insulator(FDSOI) MOSFET .The 3D Approach to solve poissions equation using suitable boundary conditions , results high accuracy to calculate the potential of the channel as compare to 1D ,2D approach .Simple and accurate analytical expression for surface potential in channel are derived .The modeling of MOSFET with 3D help to reduce SCE ,DIBL ,Subthreshold swing etc .Seperation of variable method is used in solution of poission equation , the equation can separated in on side having single variable .

I.

Keywords : SOI MOSFET, Poission Equation, 3D Solution INTRODUCTION CMOS CIRCUITS fabricated on silicon-on-insulator (SOI) wafers are gaining prominence in present-day very large-scale integration (VLSI) technology. SOI technology shows better performance over its bulk counterpart because of the following. As the individual devices are perfectly isolated,latchup can be totally eliminated in SOI CMOS circuits. The higher radiation tolerance of SOI MOSFETs. long channel SOI MOSFETs using the solution of one-dimensional (1-D) Poissons equation.As the device dimensions continue to scale down to deep submicrometer regime to obtain better performance, analytical modeling of these devices becomes more challenging . The assumption of constant surface potential used in the charge sharing models is invalid for submicrometer channel lengths. Although these models are simple, they are not as accurate as the models, which solve 2-D Poissons equation. The solution of 2-D Poissons equation has been obtained using various approaches. The solution of 2-D Poissons equation by power series approach has also been obtained [11].However, the solution of 2-D Poissons equation by power series approach is obtained by neglecting the higher order terms and, hence, it is not as accurate as the other approaches.Analytical solution of 2-D Poissons equation by means of Greens function technique [12] is another method to solve 2-D Poissons equation. Another well-known approach to solve 2-D Poissons equation is to separate the 2-D Poissons equation into a 1-D Poissons equation and a 2-D Laplace equation [13]. The ongoing device geometry scaling has pushed MOSFETs to the regime of both short-channel (for higher speed, lower supply voltage) and narrow-width (for higher density and lower power consumption) MOSFETs. Such MOSFETs, called smallgeometry MOSFETs, are very complex as three-dimensional (3-D) electrostatic effects affect the performance of the transistor. The analytical models for short-channel SOI MOSFETs discussed above take into account the scaling of the channel length and SOI film thickness but fail to take into account the narrow width effects, which become predominant as the width of the transistor is reduced. Narrow-width effects of ultrathin SOI devices are more complicated because of mesa isolation.An analytical model for of mesa-isolated fully depleted (FD) ultrathin SOI MOSFET that takes into account the narrow width effect has been reported [14].This modelsolves 3-D Poissons equation using the separation of variables method. However, the boundary conditions used for the solution of Poissons equation are applicable only for bulk MOSFETs.In fact, to the best of our knowledge, there is no 3-D analytical model for SOI MOSFETs available in the literature that takes into account both short channel and narrow width effects. The 3-D Poissons equation is solved analytically using the separation of variables technique in the next section.

II.

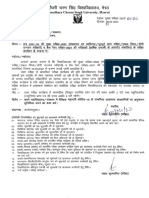

SOLUTION OF 3D POISSONS EQUATION The cross-sectional viewof an n-channel SOIMOSFET along the channel length is shownin Fig. 1(a). The sourceSOI film and drainSOI film junctions are located aty=0 and y= Leff,where Leff is the effective channel length .The front and

Volume 2, Issue 7, July 2013

Page 571

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 7, July 2013 ISSN 2319 - 4847

back interfaces are located at Si-SiO2 at x=0 and x= ts, where ts is SOI film thickness. Toxf and toxb are the thickness of frontgate an backgate oxidethicknessVgf and Vgb are the applied potential . In order to analyze the structure shown in Fig. 1, we need to solve both Poissons equation and current continuity equation.However, in the subthreshold regime, the currents are small and Poissons equation alone is sufficient. In this paper, we consider a fully depleted (FD) SOI film. The Poissons equation inthe FD SOI film region is given by

where NA is the doping concentration and is the potential at a particular point (x,y,z) in the SOI film. The boundary conditions required to solve the 3-D Poissons equation are

The boundary conditions given by (2) and (3) indicate that the potential applied at the front (back) gate is the sum of the potential at the front (back) SiSiO interface and the drop across the front (back) gate oxide. In (2) and (3), and are the flatband voltages and and are the interface trapped charges associated with the front and back gates respectively, and and are the permittivities for silicon and silicon dioxide, respectively.Equations (4) and (5) represent the boundary conditions at the source and drain ends of the channel, being the built-in potential of the n -p junctions and is the drain-to-source applied voltage. Equations (6) and (7) indicate that the potential applied at the front gate is the sum of the surface potential at the edge of the transistor and the drop across the sidewall oxide. In order to solve (1), it is separated into 1-D Poissons equation, and 2- and 3-D Laplace equation as

III.

Solution of l(x)

Volume 2, Issue 7, July 2013

Page 572

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 7, July 2013 ISSN 2319 - 4847

In equation 11, l is the solution of 1 D POISSION equation ,using the boundary condition given below.

Now after solving the above boundary condition we find the solution in the form of

(14)

IV.

Solution of s (x,y) In equation 11 ,s is the solution of 2 D laplace equation ,the boundary condtions required to solve the laplace equation are given below.

Fig. 1. (a) Cross sectional view of an n-channel SOI MOSFET

ALONG THE CHANNEL LENGTH AND (B)ALONG THE CHANNEL WIDTH.

(15) (16) (17) (18)

The solution comes in the form of summation of sin and sinhyperbolic terms

(19) Here the terms can be explained as below mentions

Volume 2, Issue 7, July 2013

Page 573

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 7, July 2013 ISSN 2319 - 4847

V.

Solution of v (x,y,z) In equation v is the solution of 3D laplace equation ,the boundary conditions equation are given below.

required to solve the laplace

After solving the laplace equation with above given equation we find the solution in the form of

Such that

Volume 2, Issue 7, July 2013

Page 574

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 7, July 2013 ISSN 2319 - 4847

Where the terms can be expressed as

here the term equation A.10 and A.11 are internal expression of 3D solution of laplace equation.

VI.

CONCLUSION A 3-D model for SOI MOSFET based on an analytical solution of 3-D Poissons equation is presented . The model takes into account the narrow-width effects in addition to the SCE.The The 3-D Poissons equation is solved analytically using the separation of variables technique in the next section. The solution will then extend to obtain the expression of threshold voltage of the small geometry SOI MOSFET.

Journal Papers: [1] S. T. Liu, W. C. Jenkins, and H. L. Hughes, Total dose radiation hard 0.35 _m SOI CMOS technology, IEEE Trans. Nucl. Sci., vol. 45, pp. 24422449, Dec. 1998. [2] P. Francis, A. Terao, B. Gentinne, D. Flendre, and J. P. Colinge, SOI technology for high-temperature applications, in IEDM Tech. Dig.,1992, pp. 353356. [3] L. Geppert, Solid state, IEEE Spectrum, vol. 36, pp. 5256, Jan. 1999.

Volume 2, Issue 7, July 2013

Page 575

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org, editorijaiem@gmail.com Volume 2, Issue 7, July 2013 ISSN 2319 - 4847

[4] H.-K. Lim and J. G. Fossum, Threshold voltage of thin-film Silicon-On-Insulator (SOI) MOSFETs, IEEE Trans. Electron Devices,vol. ED-30, pp. 12441251, Oct. 1983. [5] S. Veeraraghavan and J. G. Fossum, SCEs in SOI MOSFETs, IEEETrans. Electron Devices, vol. 36, pp. 522528, May 1989. [6] T. C. Hsiao and J. C. S. Woo, Subthreshold characteristics of fully depleted submicrometer SOI MOSFETs, IEEE Trans. Electron Devices, vol. 42, pp. 11201125, Nov. 1995. [7] K. K. Young, SCEs in fully depleted SOI MOSFETs, IEEE Trans. Electron Devices, vol. 36, pp. 399402, Apr. 1989. [8] H.-O. Joachim, Y. Yamaguchi, K. Ishikawa, I. Yasuo, and T. Nishimura,Simulation and two dimensional analytical modeling of subthreshold slope in ultrathin-film SOI MOSFETs down to 0.1_m gate length,IEEE Trans. Electron Devices, vol. 40, pp. 18121817, Nov. 1993. [9] S. R. Banna, P. C. H. Chan, P. K. Ko, C. T. Nguyen, and M. Chan,Threshold voltage model for deep-submicrometer fully depleted SOI MOSFETs, IEEE Trans. Electron Devices, vol. 42, pp. 19491955,1995. [10] A. O. Adan, K. Higashi, and Y. Fukushima, Analytical threshold voltage model for ultrathin SOI MOSFETs including short-channel and floating-body effects, IEEE Trans. Electron Devices, vol. 46, pp. 729737, June 1999. [11] P. C. Yeh and J. G. Fossum, Physical subthreshold MOSFET modelingapplied to viable design of deepsubmicrometer fully depleted SOI lowvoltage CMOS technology, IEEE Trans. Electron Devices, vol. 42, pp. 1605 1613, Nov. 1995. [12] J.-Y. Guo and C.-Y. Wu, A new 2-D analytic threshold voltage model for fully depleted short channel SOI MOSFETs, IEEE Trans. Electron Devices, vol. 40, pp. 16531661, Nov. 1993. [13] J. C. S.Woo, K.W. Terrill, and P. K.Vasudev, Two dimensional analytic modeling of very thin SOI MOSFETs, IEEE Trans. Electron Devices, vol. 37, pp. 19992006, 1990. [14] K.-W. Su and J. B. Kuo, Analytical threshold voltage formula including narrow channel effects for VLSI mesa-isolated fully depleted ultrathin silicon-on-insulator n-channel metaloxidesilicon devices,Jpn. J. Appl. Phys., vol. 34, pp. 40104019, 1995. [ 15] K. O. Jeppson, Influence of the channel width on the threshold voltage modulation of MOSFETs, Electron. Lett., vol. 11, pp. 297299, 1975. [16] L. D. Yau, A simple theory to predict the threshold voltage of short channel IGFETs, Solid State Electron., vol. 17, pp. 10591063, 1974. [17] B. Agrawal, V. K. De, and J. D. Meindl, Three dimensional analytical subthreshold models for bulk MOSFETs, IEEE Trans. Electron Devices, vol. 42, pp. 21702180, Dec. 1995. [18] M. Matloubian, R. Sundaresan, and H. Lu, Measurement and modeling of the sidewall threshold voltage of mesaisolated SOI MOSFETs,IEEE Trans. Electron Devices, vol. 36, pp. 938942, Oct. 1989.

Volume 2, Issue 7, July 2013

Page 576

Anda mungkin juga menyukai

- Detection of Malicious Web Contents Using Machine and Deep Learning ApproachesDokumen6 halamanDetection of Malicious Web Contents Using Machine and Deep Learning ApproachesInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Detection of Malicious Web Contents Using Machine and Deep Learning ApproachesDokumen6 halamanDetection of Malicious Web Contents Using Machine and Deep Learning ApproachesInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- THE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSDokumen7 halamanTHE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Experimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterDokumen7 halamanExperimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- An Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewDokumen9 halamanAn Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Experimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterDokumen7 halamanExperimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Analysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyDokumen6 halamanAnalysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- THE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSDokumen7 halamanTHE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Customer Satisfaction A Pillar of Total Quality ManagementDokumen9 halamanCustomer Satisfaction A Pillar of Total Quality ManagementInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Analysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyDokumen6 halamanAnalysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Study of Customer Experience and Uses of Uber Cab Services in MumbaiDokumen12 halamanStudy of Customer Experience and Uses of Uber Cab Services in MumbaiInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Customer Satisfaction A Pillar of Total Quality ManagementDokumen9 halamanCustomer Satisfaction A Pillar of Total Quality ManagementInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Staycation As A Marketing Tool For Survival Post Covid-19 in Five Star Hotels in Pune CityDokumen10 halamanStaycation As A Marketing Tool For Survival Post Covid-19 in Five Star Hotels in Pune CityInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Soil Stabilization of Road by Using Spent WashDokumen7 halamanSoil Stabilization of Road by Using Spent WashInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Mexican Innovation System: A System's Dynamics PerspectiveDokumen12 halamanThe Mexican Innovation System: A System's Dynamics PerspectiveInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Impact of Effective Communication To Enhance Management SkillsDokumen6 halamanThe Impact of Effective Communication To Enhance Management SkillsInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Study of Customer Experience and Uses of Uber Cab Services in MumbaiDokumen12 halamanStudy of Customer Experience and Uses of Uber Cab Services in MumbaiInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- A Digital Record For Privacy and Security in Internet of ThingsDokumen10 halamanA Digital Record For Privacy and Security in Internet of ThingsInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- An Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewDokumen9 halamanAn Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Design and Detection of Fruits and Vegetable Spoiled Detetction SystemDokumen8 halamanDesign and Detection of Fruits and Vegetable Spoiled Detetction SystemInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- A Comparative Analysis of Two Biggest Upi Paymentapps: Bhim and Google Pay (Tez)Dokumen10 halamanA Comparative Analysis of Two Biggest Upi Paymentapps: Bhim and Google Pay (Tez)International Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Performance of Short Transmission Line Using Mathematical MethodDokumen8 halamanPerformance of Short Transmission Line Using Mathematical MethodInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Synthetic Datasets For Myocardial Infarction Based On Actual DatasetsDokumen9 halamanSynthetic Datasets For Myocardial Infarction Based On Actual DatasetsInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Advanced Load Flow Study and Stability Analysis of A Real Time SystemDokumen8 halamanAdvanced Load Flow Study and Stability Analysis of A Real Time SystemInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Challenges Faced by Speciality Restaurants in Pune City To Retain Employees During and Post COVID-19Dokumen10 halamanChallenges Faced by Speciality Restaurants in Pune City To Retain Employees During and Post COVID-19International Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Secured Contactless Atm Transaction During Pandemics With Feasible Time Constraint and Pattern For OtpDokumen12 halamanSecured Contactless Atm Transaction During Pandemics With Feasible Time Constraint and Pattern For OtpInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Impact of Covid-19 On Employment Opportunities For Fresh Graduates in Hospitality &tourism IndustryDokumen8 halamanImpact of Covid-19 On Employment Opportunities For Fresh Graduates in Hospitality &tourism IndustryInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- A Deep Learning Based Assistant For The Visually ImpairedDokumen11 halamanA Deep Learning Based Assistant For The Visually ImpairedInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Anchoring of Inflation Expectations and Monetary Policy Transparency in IndiaDokumen9 halamanAnchoring of Inflation Expectations and Monetary Policy Transparency in IndiaInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Predicting The Effect of Fineparticulate Matter (PM2.5) On Anecosystemincludingclimate, Plants and Human Health Using MachinelearningmethodsDokumen10 halamanPredicting The Effect of Fineparticulate Matter (PM2.5) On Anecosystemincludingclimate, Plants and Human Health Using MachinelearningmethodsInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5782)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (72)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Syllabus of 14.130X Taught in MITDokumen6 halamanSyllabus of 14.130X Taught in MITBhargav DindukurthiBelum ada peringkat

- Cs8251 Lesson PlanDokumen2 halamanCs8251 Lesson Planshajitha120450% (2)

- Sampat Kumar, MSC (It02)Dokumen4 halamanSampat Kumar, MSC (It02)sampat1021Belum ada peringkat

- EDUC 450 Final Reports PDFDokumen511 halamanEDUC 450 Final Reports PDFRuelyn DagumBelum ada peringkat

- Woz On Integer BASICDokumen3 halamanWoz On Integer BASICMoe B. Us100% (2)

- Maths IaDokumen4 halamanMaths IapavanBelum ada peringkat

- ANFIS: Adaptive Neuro-Fuzzy Inference System ModelingDokumen21 halamanANFIS: Adaptive Neuro-Fuzzy Inference System ModelingarellanoruizBelum ada peringkat

- Mathalino: E N W S G S V V V V V W W W D Γ Γ Γ Γ Γ Γ Γ Γ Ll Pl Li Pi GiDokumen8 halamanMathalino: E N W S G S V V V V V W W W D Γ Γ Γ Γ Γ Γ Γ Γ Ll Pl Li Pi GiLovely Joy ArdanielBelum ada peringkat

- Chaudhary Charan Singh University Annual Exam Schedule 2022Dokumen25 halamanChaudhary Charan Singh University Annual Exam Schedule 2022Shubham DBelum ada peringkat

- Projection: Figure 1:the Six Principal ViewsDokumen12 halamanProjection: Figure 1:the Six Principal ViewsetilaBelum ada peringkat

- Scan Converting Ellipse Algorithm: by Amjad Khan Khalil Amjad@aup - Edu.pkDokumen24 halamanScan Converting Ellipse Algorithm: by Amjad Khan Khalil Amjad@aup - Edu.pkSultan Masood NawabzadaBelum ada peringkat

- Thermodynamic Properties of Fluids: 6.1 Property Relations For Homogeneous PhasesDokumen7 halamanThermodynamic Properties of Fluids: 6.1 Property Relations For Homogeneous PhasesdhruvBelum ada peringkat

- 6 BT Ei PDFDokumen99 halaman6 BT Ei PDFramesh babuBelum ada peringkat

- Lect 1 - 2Dokumen15 halamanLect 1 - 2Shubham AjmeraBelum ada peringkat

- Chapter-3 Load and Stress AnalysisDokumen96 halamanChapter-3 Load and Stress AnalysisDhinesh3693100% (1)

- NASA-Requirements Peer Review ChecklistDokumen4 halamanNASA-Requirements Peer Review Checklistorawan_jBelum ada peringkat

- Raisunsoft DFX PresentationDokumen10 halamanRaisunsoft DFX PresentationshubhakthBelum ada peringkat

- Toxic Language Identification Via Audio Using A Self-Attentive Convolutional Neural Networks (CNN)Dokumen7 halamanToxic Language Identification Via Audio Using A Self-Attentive Convolutional Neural Networks (CNN)International Journal of Innovative Science and Research TechnologyBelum ada peringkat

- IIM Ahmedabad researchers introduce open-source QuantLib for derivatives pricingDokumen25 halamanIIM Ahmedabad researchers introduce open-source QuantLib for derivatives pricingvicky.sajnaniBelum ada peringkat

- Grade 9 Mathematics Max - Marks:80+20: Patel Public SchoolDokumen3 halamanGrade 9 Mathematics Max - Marks:80+20: Patel Public SchoolApoorvaBelum ada peringkat

- Chapter 12 - Thermodynamics - FormulaeDokumen5 halamanChapter 12 - Thermodynamics - FormulaeRoop KumarBelum ada peringkat

- SCCS 420 CH 22-1 (Delivery Forwarding Routing)Dokumen18 halamanSCCS 420 CH 22-1 (Delivery Forwarding Routing)api-3738694100% (1)

- Vehicle Detection and Tracking at Night in Video SurveillanceDokumen5 halamanVehicle Detection and Tracking at Night in Video SurveillanceDivine Grace BurmalBelum ada peringkat

- The Dyslexic Reader 2010 - Issue 55Dokumen32 halamanThe Dyslexic Reader 2010 - Issue 55Davis Dyslexia Association InternationalBelum ada peringkat

- Steps in SHA-256 AlgorithmDokumen5 halamanSteps in SHA-256 AlgorithmOsama YaqoobBelum ada peringkat

- PID Tuning Tips: Check Control Loop Basics With A Time LineDokumen2 halamanPID Tuning Tips: Check Control Loop Basics With A Time Linetomaz_filhoBelum ada peringkat

- CS210 Lecture 5 Proof of Correctness Solving Local Minima in GridDokumen24 halamanCS210 Lecture 5 Proof of Correctness Solving Local Minima in GridSahil BansalBelum ada peringkat

- Grade 4Dokumen17 halamanGrade 4Cht Geby100% (1)

- Unit - I (Partial Differential Equations)Dokumen13 halamanUnit - I (Partial Differential Equations)sathesh waranBelum ada peringkat