Mos Ic Technology

Diunggah oleh

Mansi JhambHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Mos Ic Technology

Diunggah oleh

Mansi JhambHak Cipta:

Format Tersedia

Paper Code: ICTEC-605 L T C Paper: MOS IC Technology 4 4 INSTRUCTIONS TO PAPER SETTERS: Maximum Marks : 60 1. Question No.

1 should be compulsory and cover the entire syllabus. This question should have objective or short answer type questions. It should be of 20 marks. 2. Apart from Question No. 1, rest of the paper shall consist of four units as per the syllabus. Every unit should have two questions. However, student may be asked to attempt only 1 question from each unit. Each question should be 10 marks Objective: Study of: Derive basic analytical MOS circuit equations. Locate information not presented in class, in the library. Analyze circuits using both analytical and CAD tools. Use a design flow to design a CMOS integrated circuit in a team environment. Interpret a design specification. Design test benches which can prove that a design meet a specification. Identify regions where circuit models are valid. Unit 1 Introduction [T1]: Basic principle of MOS transistor, Introduction to large signal MOS models (long channel) for digital design. (3 lectures) MOS Circuit Layout & Simulation [T1]: MOS SPICE model, device characterization, Circuit characterization, interconnects simulation. MOS device layout: Transistor layout, Inverter layout, CMOS digital circuit layout & simulation. (4 lectures) Unit 2 The MOS Inverter [T1]: Inverter principle, Depletion and enhancement load inverters, the basic CMOS inverter, transfer characteristics, logic threshold, Noise margins, and Dynamic behavior, Propagation Delay, Power Consumption. (8 lectures) Unit 3 Combinational MOS Logic Design [T1] Static MOS design [T1]: Complementary MOS, Ratioed logic, Pass Transistor logic, complex logic circuits. (4 lectures) Sequential MOS Logic Design [T1] Static latches, Flip flops & Registers, Dynamic Latches & Registers, CMOS Schmitt trigger, Monostable sequential Circuits, Astable Circuits. Memory Design: ROM & RAM cells design (6 lectures) Unit 4 Dynamic MOS design [T1]: Dynamic logic families and performances. (4 lectures) Interconnect & Clock Distribution [T1] [T2] Interconnect delays, Cross Talks, Clock Distribution. Introduction to low power design, Input and Output Interface circuits. (3 lectures) BiCMOS Logic Circuits [T1] Introduction, BJT Structure & operation, Basic BiCMOS Circuit behavior, Switching Delay in BiCMOS Logic circuits, BiCMOS Application. (4 lectures) Text Books 1[T1] Kang & Leblebigi CMOS Digital IC Circuit Analysis & Design- McGraw Hill, 2003. 2[T2] Rabey, Digital Integrated Circuits Design, Pearson Education, Second Edition, 2003. 3 4Reference Books 1[R1] Weste and Eshraghian, Principles of CMOS VLSI design Addison-Wesley, 2002.

Anda mungkin juga menyukai

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- B.tech. M.tech. DD Mca Se PracDokumen3 halamanB.tech. M.tech. DD Mca Se PracMansi JhambBelum ada peringkat

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5795)

- Syl LB Tech Ece 040811Dokumen117 halamanSyl LB Tech Ece 040811Mansi JhambBelum ada peringkat

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- DSD Using VerilogDokumen1 halamanDSD Using VerilogMansi JhambBelum ada peringkat

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- List of Enrollment Working Centre NorthDokumen4 halamanList of Enrollment Working Centre NorthMansi JhambBelum ada peringkat

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- FC10 Operating InstructionsDokumen32 halamanFC10 Operating InstructionsThanhTungHoangBelum ada peringkat

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- FORM VESSEL Order SP-MSP 8Dokumen2 halamanFORM VESSEL Order SP-MSP 8MARCOBelum ada peringkat

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Cat G3516A: Natural Gas Generator SetsDokumen5 halamanCat G3516A: Natural Gas Generator SetsRecovery MailBelum ada peringkat

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- Toshiba Fc-22 SMDokumen252 halamanToshiba Fc-22 SMmehdi_palangiBelum ada peringkat

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Toyota SP100 Series Sewing Machine Instruction ManualDokumen51 halamanToyota SP100 Series Sewing Machine Instruction ManualiliiexpugnansBelum ada peringkat

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- List of Instruments & EquipmentsDokumen1 halamanList of Instruments & EquipmentsRAHUL SINGHBelum ada peringkat

- Unit-IV-Induction MotorsDokumen57 halamanUnit-IV-Induction MotorssujithBelum ada peringkat

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (345)

- Discussion Lab 9Dokumen1 halamanDiscussion Lab 9thevand11Belum ada peringkat

- Lab 1 Config GPIODokumen26 halamanLab 1 Config GPIONguyễn Việt HưngBelum ada peringkat

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Hyundai Led4 InstruccionesDokumen5 halamanHyundai Led4 InstruccionesEncep ZaenalBelum ada peringkat

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Pre Test 8Dokumen5 halamanPre Test 8Gerome TongolBelum ada peringkat

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- DUCT Type. INVERTER SPLIT TYPE AIR CONDITIONER (50Hz) ARHA24LATN AOHA24LACL. Models Indoor Unit Outdoor UnitDokumen44 halamanDUCT Type. INVERTER SPLIT TYPE AIR CONDITIONER (50Hz) ARHA24LATN AOHA24LACL. Models Indoor Unit Outdoor UnitEnekoBelum ada peringkat

- Method Statement For Fan Coil UnitsDokumen6 halamanMethod Statement For Fan Coil UnitsTawrez KhatibBelum ada peringkat

- Belden CatalogDokumen6 halamanBelden Catalogeddyson_24Belum ada peringkat

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- Western Electric No. 2 Sewing Machine Instruction ManualDokumen44 halamanWestern Electric No. 2 Sewing Machine Instruction ManualiliiexpugnansBelum ada peringkat

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- 1974 MECL Integrated Circuits Series A Vol4 PDFDokumen624 halaman1974 MECL Integrated Circuits Series A Vol4 PDFjalmeida88Belum ada peringkat

- Gree Cassette Brochure 4pp 2016 Web PDFDokumen4 halamanGree Cassette Brochure 4pp 2016 Web PDFFiroz AlamBelum ada peringkat

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- CTVT Trafindo 2010Dokumen19 halamanCTVT Trafindo 2010Ahmad Ikhsan KurniantoBelum ada peringkat

- 667 Electrical Installation Material Ki Hella enDokumen179 halaman667 Electrical Installation Material Ki Hella enMire Si VasiBelum ada peringkat

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- M&E CoordinationDokumen11 halamanM&E Coordinationدهلن سامتBelum ada peringkat

- Data Sheet - UPS SystemDokumen7 halamanData Sheet - UPS SystemPrakash SinhaBelum ada peringkat

- Appendix: - Optional FunctionDokumen11 halamanAppendix: - Optional FunctionArvin ArmojallasBelum ada peringkat

- Autolube System (HYD) OverviewDokumen21 halamanAutolube System (HYD) OverviewDaniel Alfonso Diaz FloresBelum ada peringkat

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- Installation and Operation Manual For Esareka Aluminum Stop LogDokumen1 halamanInstallation and Operation Manual For Esareka Aluminum Stop LogWarren YongBelum ada peringkat

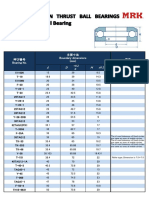

- King Pin Thrust Ball BearingsDokumen3 halamanKing Pin Thrust Ball BearingsFernando Bautista100% (2)

- Speedaire Positive Displacement Industrial Blowers and Vacuum PumpsDokumen101 halamanSpeedaire Positive Displacement Industrial Blowers and Vacuum PumpsalexanderBelum ada peringkat

- B 815 DFC EeDokumen17 halamanB 815 DFC EeBasman GeorgeBelum ada peringkat

- Operation Guide MSBDokumen8 halamanOperation Guide MSBMao RathanithBelum ada peringkat

- Standard Drawing For Piping ArrangementDokumen23 halamanStandard Drawing For Piping ArrangementEndra BudimansyahBelum ada peringkat

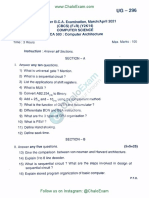

- V Semester B.C.A. Examination, March/April 2021 (CBCS) (F+R) (Y2K14) Computer ScienceDokumen2 halamanV Semester B.C.A. Examination, March/April 2021 (CBCS) (F+R) (Y2K14) Computer ScienceNâñè DévrûBelum ada peringkat

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)