M.E Vlsi FT 2011

Diunggah oleh

செல்வம் முத்துராமன்Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

M.E Vlsi FT 2011

Diunggah oleh

செல்வம் முத்துராமன்Hak Cipta:

Format Tersedia

Department of Electronics and Communication Engineering

Faculty of Engineering

KARPAGAM UNIVERSITY

Karpagam Academy of Higher Education

(Established under Section 3 of UGC Act 1956)

Eachanari, Coimbatore-641 021. INDIA

KARPAGAM UNIVERSITY Karpagam Academy of Higher Education (Established under Section 3 of UGC Act 1956) Eachanari, Coimbatore-641 021.

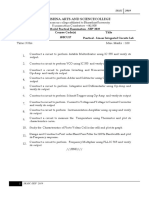

FACULTY OF ENGINEERING DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING M.E. (VLSI DESIGN FULL TIME) CURRICULUM - 2011

SUB. CODE TITLE OF THE COURSE SEMESTER I THEORY: 11MECC101 Applied Mathematics 11MEVL101 Advanced Digital System Design 11MEVL102 VLSI Design Techniques 11MEVL103 Solid State Device Modeling and Simulation 11MEVL104 Testing of VLSI Circuits PRACTICAL 11MEVL111 VLSI Design Lab I TOTAL

L 3 3 3 3 3 0

T 0 0 0 0 0 0 18

P 0 0 0 0 0 3

C 3 3 3 3 3 1 16

CIA ESE TOTAL 40 40 40 40 40 40 60 60 60 60 60 60 100 100 100 100 100 100 600

SUB. CODE TITLE OF THE COURSE SEMESTER II THEORY: 11MEVL201 Analysis and Design of Analog Integrated Circuits 11MEVL202 VLSI Signal Processing 11MEVLE** Elective I 11MEVLE** Elective II 11MEVLE** Elective III PRACTICAL 11MEVL211 VLSI Design Lab II TOTAL

CIA ESE TOTAL 40 40 40 40 40 40 60 60 60 60 60 60 100 100 100 100 100 100 600

3 3 3 3 3 0

0 0 0 0 0 0 18

0 0 0 0 0 3

3 3 3 3 3 1 16

SUB. CODE TITLE OF THE COURSE SEMESTER III THEORY: Digital Signal Processing 11MEVL301 Integrated Circuits Computer Aided Design of 11MEVL302 VLSI Circuits Research Methodology 11MECC301 Pedagogy & Communication Skills 11MEVLE** Elective IV 11MEVLE** Elective V PRACTICAL 11MEVL311 Project Work (Phase I) TOTAL

CIA ESE TOTAL 40 40 40 60 60 60 60 60 60 100 100 100 100 100 100 600

3 3 3 3 3 0

0 0 0 0 0 0 27

0 0 0 0 0 12

3 3 3 3 3 4 19

40 40 40

SUB. CODE TITLE OF THE COURSE SEMESTER IV THEORY: 11MEVL411 Project Work (Phase II) Project (Phase I & Phase II)

L 0 0

T 0 0

P 36 48

C 12 16

CIA ESE TOTAL 120 160 180 240 300 400

LIST OF ELECTIVES

SUB. CODE 11MEVLE01 11MEVLE02 11MEVLE03 11MEVLE04 11MEVLE05 11MEVLE06 11MEVLE07 11MEVLE08 11MEVLE09 11MEVLE10 11MEVLE11 11MEVLE12 11MEVLE13 11MEVLE14

TITLE OF THE COURSE Advanced Microprocessors and Microcontrollers ASIC Design VHDL Genetic Algorithms and their Applications Low Power VLSI Design Analog VLSI Design CMOS VLSI Design Design of Semiconductor Memories Physical Design of VLSI Circuits Neural Networks and Applications Reliability Engineering Electromagnetic interference and compatibility in system design Digital Speech Signal Processing DSP Processor Architecture and Programming

L 3 3 3 3 3 3 3 3 3 3 3 3 3 3

T 0 0 0 0 0 0 0 0 0 0 0 0 0 0

P 0 0 0 0 0 0 0 0 0 0 0 0 0 0

C 3 3 3 3 3 3 3 3 3 3 3 3 3 3

CIA ESE TOTAL 40 40 40 40 40 40 40 40 40 40 40 40 40 40 60 60 60 60 60 60 60 60 60 60 60 60 60 60 100 100 100 100 100 100 100 100 100 100 100 100 100 100

L Lecture Hour; T Tutorial Hour; P Practical hour; C - Credit; CIA Continuous Internal Assessment; ESE End Semester Examination

SEMESTER - I 11MECC101 APPLIED MATHEMATICS 30 0 3

UNIT I ADVANCED MATRIX THEORY Matrix norms Jordan canonical form Generalized eigenvectors Singular value decomposition Pseudo inverse Least square approximations QR algorithm. UNIT II CALCULUS OF VARIATIONS Variation and its properties Eulers equation Functionals dependent on first and higher order derivatives Functionals dependent on functions of several independent variables Some applications Direct methods: Ritz and Kantorovich methods. UNIT - III LINEAR PROGRAMMING Basic concepts Graphical and Simplex methods Transportation problem Assignment problem. UNIT IV Z TRANSFORMS Transform of standard functions Convolution Initial and Final value problems Shifting Theorem Inverse transform (Using Partial Fraction Residues) Solution of difference Equations using Z Transform. UNIT V RANDOM PROCESSES Classification Stationary random processes Auto Correlation Cross Correlations Power spectral density Linear system with random input Gaussian Process. REFERENCES Venkataraman.M.K, 2000, Higher Mathematics for Engineering & Science, National Publishing Company, Florida Bronson.R, 1989, Matrix Operations , Schaums outline Series, McGraw Hill, New York. Elsgoltis, 1970, Differential Equations and Calculus of Variations ", MIR Publishers, Moscow. Gupta.A.S, 1999, Calculus of Variations with Applications , Prentice Hall of India, New Delhi. Veerarajan.T, 2000, Probability, Statistics & Random Processes, Tata McGraw Hill, New Delhi. Gupta.P.K and Hira.D.S, 1999, Operations Research ", S.Chand & Co, New Delhi. Veerarajan.T, 2000, Mathematics III, Tata McGraw Hill. Taha.H.A, 1997, operation research-An introduction, 6th Edition, PHI, New Delhi. Grewal.B.S, 2005, Higher Engineering Mathematics, Khanna publication.

11MEVL101 ADVANCED DIGITAL SYSTEM DESIGN UNIT I SEQUENTIAL CIRCUIT DESIGN Analysis of Clocked Synchronous Sequential Networks (CSSN) Modeling of CSSN State Stable Assignment and Reduction Design of CSSN Design of Iterative Circuits ASM Chart ASM Realization.

3 0 0 3

UNIT II ASYNCHRONOUS SEQUENTIAL CIRCUIT DESIGN Analysis of Asynchronous Sequential Circuit (ASC) Flow Table Reduction Races in ASC State Assignment Problem and the Transition Table Design of ASC Static and Dynamic Hazards Essential Hazards Data Synchronizers Designing Vending Machine Controller Mixed Operating Mode Asynchronous Circuits. UNIT III FAULT DIAGNOSIS AND TESTABILITY ALGORITHMS Fault Table Method Path Sensitization Method Boolean Difference Method Kohavi Algorithm Tolerance Techniques The Compact Algorithm Practical PLAs Fault in PLA Test Generation Masking Cycle DFT Schemes Built-in Self Test . UNIT IV SYNCHRONOUS DESIGN USING PROGRAMMABLE DEVICES EPROM to Realize a Sequential Circuit Programmable Logic Devices Designing a Synchronous Sequential Circuit using a GAL EPROM Realization State machine using PLD FPGA Xilinx FPGA Xilinx 2000 - Xilinx 3000 UNIT V SYSTEM DESIGN USING VHDL VHDL Description of Combinational Circuits Arrays VHDL Operators Compilation and Simulation of VHDL Code Modelling using VHDL Flip Flops Registers Counters Sequential Machine Combinational Logic Circuits - VHDL Code for Serial Adder, Binary Multiplier Binary Divider complete Sequential Systems Design of a Simple Microprocessor. REFERENCES Donald G. Givone, 2002, Digital principles and Design, 4th Edition, Tata McGraw Hill, New Delhi. John M Yarbrough, 2001, Digital Logic applications and Design ,5 th Edition, Thomson Learning, United Kingdom. Nripendra N Biswas, 2001 , Logic Design Theory ,4th Edition, Prentice Hall of India, New Delhi. Charles H. Jr.Roth,1998, Digital System Design using VHDL , 3 rd Edition, Thomson Learning, United Kingdom. Charles H. Jr.Roth, 2004, Fundamentals of Logic design ,5 th Edition, Thomson Learning, United Kingdom. Stephen Brown and Zvonk Vranesic, 2002, Fundamentals of Digital Logic with VHDL Design, 6th Edition,Tata McGraw Hill, New Delhi. Navabi.Z. 1998, VHDL Analysis and Modeling of Digital Systems, 2nd Edition, McGraw International, New York.

11MEVL102 VLSI DESIGN TECHNIQUES UNIT - I

3 0 0 3

VLSI DESIGN PROCESS & MOS TRANSISTOR THEORY AND PROCESS TECHNOLOGY VLSI Design Process Architectural Design Logical Design Physical Design Layout Styles Full custom, Semicustom approaches. NMOS and PMOS transistors, Threshold voltage- Body effect- Design equations- Second order effects. MOS models and small signal AC characteristics. Basic CMOS technology UNIT - II INVERTERS AND LOGIC GATES NMOS and CMOS Inverters, Stick diagram, Inverter ratio, DC and transient characteristics , switching times, Super buffers, Driving large capacitance loads, CMOS logic structures , Transmission gates, Static CMOS design, dynamic CMOS design. UNIT - III CIRCUIT CHARACTERISATION & PERFORMANCE ESTIMATION Resistance estimation, Capacitance estimation, Inductance, switching characteristics, transistor sizing, power dissipation and design margining. Charge sharing .Scaling. UNIT - IV VLSI SYSTEM COMPONENTS CIRCUITS Multiplexers, Decoders, comparators, priority encoders, Shift registers. Arithmetic circuits Ripple carry adders, Carry look ahead adders, High-speed adders, Multipliers UNIT - V VERILOG HARDWARE DESCRIPTION LANGUAGE Overview of digital design with Verilog HDL, hierarchical 7odeling concepts, modules and port definitions, gate level 7odeling, data flow 7odeling, behavioral 7odeling, task & functions, Test Bench. REFERENCES Jan M Rabaey, 2002, Digital Integrated Circuits, 4th Edition, Prentice Hall of India, New Delhi. Sung-Mo Kang and Yusuf Leblebici, 2003, CMOS Digital Integrated Circuits- Analysis and Design,5th Edition,Tata McGraw Hill, New Delhi. Neil H.E. Weste and Kamran Eshraghian, 2000, Principles of CMOS VLSI Design , 2nd Edition, Pearson Education, ASIA. John P.Uyemura2002, Introduction to VLSI Circuits and Systems, 5th Edition, John Wiley & Sons, Inc. Samir Palnitkar, 2004, Verilog HDL , 2nd Edition, Pearson Education, New Delhi. Eugene D.Fabricius, 1990, Introduction to VLSI Design,2nd Edition, McGraw Hill International Editions, New York Bhasker.J, Publications.B.S, 2001, A Verilog HDL Primer, 2nd Edition. Pucknell, 1995, Basic VLSI Design, 2nd Edition, Prentice Hall of India Publication, New Delhi. Wayne Wolf, 2002, Modern VLSI Design System on chip, 5 th Edition, Pearson Education, New Delhi

11MEVL103

SOLID STATE DEVICE MODELING AND SIMULATION

3 0 0 3

UNIT I BASIC SEMICONDUCTOR PHYSICS Quantum Mechanical Concepts, Carrier Concentration, Transport Equation, Band gap, Mobility and Resistivity, Carrier Generation and Recombination, Avalanche Process, Noise Sources. Diodes: Forward and Reverse biased junctions Reverse bias breakdown Transient and AC conditions - Static and Dynamic behavior- Small and Large signal models SPICE model for a Diode Temperature and Area effects on Diode Model Parameters. UNIT II BIPOLAR DEVICE MODELING Transistor Models: BJT Transistor Action Minority carrier distribution and Terminal currents Switching- Eber - Molls and Gummel Poon Model, SPICE modeling - temperature and area effects. UNIT III MOSFET MODELING MOS Transistor NMOS, PMOS MOS Device equations - Threshold Voltage Second order effects - Temperature Short Channel and Narrow Width Effect, Models for Enhancement, Depletion Type MOSFET, CMOS Models in SPICE. UNIT IV PARAMETER MEASUREMENT Bipolar Junction Transistor Parameter Static Parameter Measurement Techniques Large signal parameter Measurement Techniques, Gummel Plots, MOSFET: Long and Short Channel Parameters, Measurement of Capacitance. UNIT V OPTOELECTRONIC DEVICE MODELING Static and Dynamic Models, Rate Equations, Numerical Technique, Equivalent Circuits, Modeling of LEDs, Laser Diode and Photo detectors. REFERENCES Ben.G.Streetman, 1997, Solid State Devices, 3rd Edition,Prentice Hall. Giuseppe Massobrio and Paolo Antogentti, 1993, Semiconductor Device Modeling with SPICE, 2nd Edition, McGraw-Hill Inc, New York. Tyagi.M.S, 1981, Introduction to Semiconductor Devices,2nd Edition, Mc Graw Hill, New York. Sze.S.M, 1985,Semiconductor Devices - Physics and Technology,2nd Edition,John Wiley and sons. Mohammed Ismail & Terri Fiez, 2001, Analog VLSI-Signal & Information Processing, 1 st Edition,Tata McGraw Hill Publishing company Ltd, New Delhi. 11MEVL104 TESTING OF VLSI CIRCUITS 30 0 3

UNIT - I INTRODUCTION Introduction to Testing - Faults in digital circuits - Modeling of faults - Logical Fault Models Fault detection - Fault location - Fault dominance - Logic Simulation - Types of simulation - Delay models - Gate level Event-driven simulation.

UNIT - II

TEST GENERATION FOR COMBINATIONAL AND SEQUENTIAL CIRCUITS Test generation for combinational logic circuits - Testable combinational logic circuit design - Test generation for sequential circuits - design of testable sequential circuits. UNIT III DESIGN FOR TESTABILITY Design for Testability - Ad-hoc design - Generic scan based design - Classical scan based design System level DFT approaches. UNIT IV BUILT-IN SELF TEST Built-In Self Test - Test pattern generation for BIST - Circular BIST - BIST Architectures Testable Memory Design - Test algorithms - Test generation for Embedded RAMs UNIT - V SELF-CHECKING AND SYSTEM LEVEL DIAGNOSIS Logic Level Diagnosis Diagnosis by UUT reduction Fault Diagnosis for Combinational Circuits Self-checking design System Level Diagnosis. REFERENCE BOOKS Abramovici.M, Breuer.M.A and Friedman.A.D, 2002, Digital Systems and Testable design ,4 th Edition, Jaico Publishing House. Lala.P.K, 2002, Digital Circuit Testing and Testability, 5th Edition,Academic Press. Bushnell.M.L and Agrawal.V.D, 2002, Essentials of Electronic Testing for Digital Memory and Mixed-Signal VLSI Circuits, 4th Edition, Kluwar Academic Publishers. PRACTICALS 11MEVL111 VLSI DESIGN LABORATORY I 00 3 2

LIST OF EXPERIMENTS 1 Modeling of Sequential Digital system using VHDL. 2 Modeling of Sequential Digital system using Verilog. 3 Writing Test Benches Using Verilog / VHDL 4 Design and Implementation of ALU using FPGA. 5 Simulation of NMOS and CMOS circuits using SPICE. 6 Design of Static and Dynamic Logic Circuits 7 Modeling of MOSFET using C. 8 Implementation of FFT, Digital Filters. 9 Implementation of DSP algorithms using software package. 10 Implementation of MAC Unit using FPGA. SEMESTER II 11MEVL201 ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITS

3 0 0 3 UNIT I MODELS FOR INTEGRATED CIRCUIT ACTIVE DEVICES Depletion region of a pn junction large signal behavior of bipolar transistors- small signal model of bipolar transistor- large signal behavior of MOSFET- small signal model of the MOS transistorsshort channel effects in MOS transistors weak inversion in MOS transistors- substrate current flow in MOS transistor. UNIT - II CIRCUIT CONFIGURATION FOR LINEARIC Current sources, Analysis of difference amplifiers with active load using BJT and FET, supply and temperature independent biasing techniques, voltage references. Output stages: Emitter follower, source follower and Push pull output stages. UNIT III OPERATIONAL AMPLIFIERS Analysis of operational amplifiers circuit, slew rate model and high frequency analysis, Frequency response of integrated circuits: Single stage and multistage amplifiers, Operational amplifier noise UNIT - IV ANALOG MULTIPLIER AND PLL Analysis of four quadrant and variable trans conductance multiplier, voltage controlled oscillator, closed loop analysis of PLL, Monolithic PLL design in integrated circuits: Sources of noise- Noise models of Integrated-circuit Components Circuit Noise Calculations Equivalent Input Noise Generators Noise Bandwidth Noise Figure and Noise Temperature UNIT - V ANALOG DESIGN WITH MOS TECHNOLOGY MOS Current Mirrors Simple, Cascode, Wilson and Widlar current source CMOS Class AB output stages Two stage MOS Operational Amplifiers, with Cascode, MOS Telescopic-Cascode Operational Amplifier MOS Folded Cascode and MOS Active Cascode Operational Amplifiers REFERENCES Gray, Meyer, Lewis, Hurst, 2002, Analysis and design of Analog ICs, 4th Edition, Wiley International, Behzad Razavi, 2000, Design of Analog CMOS Integrated Circuits, 4 th Edition, S.Chand and company ltd. Nandita Dasgupata, Amitava Dasgupta, 2004, Semiconductor Devices, Modelling and Technology, 6th Edition,Prentice Hall of Indiapvt.ltd. Grebene, 2003, Bipolar and MOS Analog Integrated circuit design, 5 th Edition, John Wiley & sons, Inc. Phillip E.Allen Douglas R. Holberg, 2003, CMOS Analog Circuit Design, 2nd Edition, Oxford University Press. 11MEVL202 VLSI SIGNAL PROCESSING 30 0 3

UNIT I INTRODUCTION TO DSP SYSTEMS Introduction To DSP Systems -Typical DSP algorithms; Iteration Bound data flow graph representations, loop bound and iteration bound, Longest path Matrix algorithm; Pipelining and parallel processing Pipelining of FIR digital filters, parallel processing, pipelining and parallel processing for low power.

10

UNIT II RETIMING, FOLDING AND UNFOLDING Retiming - definitions and properties Retiming techniques; Unfolding an algorithm for Unfolding, properties of unfolding, sample period reduction and parallel processing application; Folding Folding transformation Register minimizing techniques Register minimization in folded architectures UNIT III FAST CONVOLUTION Fast convolution Cook-Toom algorithm, modified Cook-Took algorithm Winograd Algorithm, Iterated Convolution Cyclic Convolution; Pipelined and parallel recursive and adaptive filters inefficient/efficient single channel interleaving, Look- Ahead pipelining in first- order IIR filters, Look-Ahead pipelining with power-of-two decompositionparallel processing of IIR filters, combined pipelining and parallel processing of IIR filters, pipelined adaptive digital filters, relaxed look-ahead, pipelined LMS adaptive filter . UNIT IV BIT-LEVEL ARITHMETIC ARCHITECTURES Bit-Level Arithmetic Architectures- parallel multipliers with sign extension, parallel carry-ripple array multipliers, parallel carry-save multiplier, 4x 4 bit Baugh- Wooley carry-save multiplication tabular form and implementation, design of Lyons bit-serial multipliers using Horners rule, bitserial FIR filter, CSD representation, CSD multiplication using Horners rule for precision improvement. UNIT V PROGRAMMING DIGITAL SIGNAL PROCESSORS Synchronous, Wave and asynchronous pipelining- synchronous pipelining and clocking styles, clock skew in edge-triggered single-phase clocking, two-phase clocking, wave pipelining, asynchronous pipelining bundled data versus dual rail protocol; Programming Digital Signal Processors general architecture with important features; Low power Design needs for low power VLSI chips, charging and discharging capacitance, short-circuit current of an inverter, CMOS leakage current, basic principles of low power design. REFERENCE BOOKS Keshab K.Parhi, 1999, VLSI Digital Signal Processing systems, Design and Implementation, 2nd Edition ,Wiley, Inter Science. Gary Yeap, 1998, Practical Low Power Digital VLSI Design, 2nd Edition, Kluwer Academic Publishers. Mohammed Isamail and Terri Fiez, 1994, Analog VLSI Signal and Information Processing, 2 nd Edition, Mc Graw-Hill, New York Kung.S.Y, White House. H.J, Kailath.T, 1985, VLSI and Modern Signal Processing, Prentice Hall. PRACTICALS 11MEVL211 VLSI DESIGN LAB II 00 3 2

11

LIST OF EXPERIMENTS 1. Implementation of 8 Bit ALU in FPGA / CPLD. 2. Implementation of 4 Bit Sliced processor in FPGA / CPLD. 3. Implementation of Elevator controller using embedded microcontroller. 4. Implementation of Alarm clock controller using embedded microcontroller. 5. Implementation of model train controller using embedded microcontroller. 6. System design using PLL.

SEMESTER III 11MEVL301- DIGITAL SIGNAL PROCESSING INTEGRATED CIRCUITS 30 0 3

UNIT I DSP INTEGRATED CIRCUITS AND VLSI CIRCUIT TECHNOLOGIES Standard digital signal processors, Application specific ICs for DSP, DSP systems, DSP system design, Integrated circuit design. MOS transistors, MOS logic, VLSI process technologies, Trends in CMOS technologies UNIT II DIGITAL SIGNAL PROCESSING Digital signal processing, Sampling of analog signals, Selection of sample frequency, Signalprocessing systems, Frequency response, Transfer functions, Signal flow graphs, Filter structures, Adaptive DSP algorithms, DFT-The Discrete Fourier Transform, FFT-The Fast Fourier Transform Algorithm, Image coding, Discrete cosine transforms. UNIT III DIGITAL FILTERS AND FINITE WORD LENGTH EFFECTS FIR filters, FIR filter structures, FIR chips, IIR filters, Specifications of IIR filters, Mapping of analog transfer functions, Mapping of analog filter structures, Multirate systems, Interpolation with an integer factor L, Sampling rate change with a ratio L/M, Multirate filters. Finite word length effects -Parasitic oscillations, Scaling of signal levels, Round-off noise, Measuring round-off noise, Coefficient sensitivity, Sensitivity and noise. UNIT IV DSP ARCHITECTURES AND SYNTHESIS OF DSP ARCHITECTURES DSP system architectures, Standard DSP architecture, Ideal DSP architectures, Multiprocessors and multicomputers, Systolic and Wave front arrays, Shared memory architectures. Mapping of DSP algorithms onto hardware, Implementation based on complex PEs, Shared memory architecture with Bit serial PEs. UNIT V ARITHMETIC UNITS AND INTEGRATED CIRCUIT DESIGN Conventional number system, Redundant Number system, Residue Number System, Bit-parallel and Bit-Serial arithmetic, Basic shift accumulator, Reducing the memory size, Complex multipliers, Improved shift-accumulator. Layout of VLSI circuits, FFT processor, DCT processor and Interpolator as case studies. REFERENCES Lars Wanhammer, 1999, DSP Integrated Circuits, 3rd Edition, Academic press, New York.

12

Oppenheim.A.V, 2000, Discrete-time Signal Processing, 4th Edition, Pearson education, New Delhi. Emmanuel.C, Ifeachor,W. Barrie ,Jervis,2001, Digital signal processing A practical approach , 2nd Edition, Pearson education, Asia. Keshab K.Parhi, 1999, VLSI digital Signal Processing Systems design and Implementation, 2 nd Edition, John Wiley & Sons. Bayoumi & Magdy.A, 2005, VLSI Design Methodologies for Digital Signal Processing Architectures, 6th Edition, BS Publications. 11MEVL302 COMPUTER AIDED DESIGN OF VLSI CIRCUITS 30 0 3 UNIT - I Introduction to VLSI Design methodologies - Review of Data structures and algorithms Review of VLSI Design automation tools - Algorithmic Graph Theory and Computational Complexity - Tractable and Intractable problems - general purpose methods for combinatorial optimization. UNIT - II Layout Compaction - Design rules - problem formulation - algorithms for constraint graph compaction - placement and partitioning - Circuit representation - Placement algorithms partitioning UNIT - III Floor planning concepts - shape functions and floorplan sizing - Types of local routing problems Area routing - channel routing - global routing - algorithms for global routing. UNIT - IV Simulation - Gate-level modeling and simulation - Switch-level modeling and simulation Combinational Logic Synthesis - Binary Decision Diagrams - Two Level Logic Synthesis. UNIT - V High level Synthesis - Hardware models - Internal representation - Allocation - assignment and scheduling - Simple scheduling algorithm - Assignment problem High level transformations. REFERENCES Gerez.S.H, 2002, Algorithms for VLSI Design Automation, 4th Edition,John Wiley & Sons. Sherwani.N.A, 2002, Algorithms for VLSI Physical Design Automation,4 th Edition, Kluwar Academic Publishers. Drechsler.R, 1998, Evolutionary Algorithms for VLSI CAD, 2 nd Edition,Kluwer Academic Publishers, Boston. Hill.D, Shugard.D, Fishburn.J and Keutzer.K, 1989, Algorithms and Techniques for VLSI Layout Synthesis, 3rd Edition, Kluwer Academic Publishers, Boston. 11MECC301 RESEARCH METHODOLOGY PEDAGOGY & COMMUNICATION SKILLS 30 0 3

13

UNIT I HIGHER EDUCATION AN INTRODUCTION Historical perspectives, the objectives of higher education, role of higher education-social focus, curricular focus, administrative focus, drivers of change in higher education-globalization, changing demographics, structuring of employment, technological change, demand of accountability, consumerism,. Expectations by employers, rate of knowledge growth, campus demographics, concern for community. Restructuring and new patterns of decision making. UNIT II RESEARCH PROCESSES AND METHODOLOGY Introduction to Research Research strategies Ethics Code of conduct for Research Health and Safety IPR Research Events Networks Outreach Activities Best Research practices Quality assurance for Research Career Management for Researchers Research seminars Journal critiques -. UNIT III EFFECTIVE RESEARCH SKILLS Data collection Modeling Simulation Analysis Prototyping Presentation Skills Data Presentation Skills Research Writing skills (For Articles, Reports, Journals and Thesis) Creative Skills Effective Interview Skills Team Building Skills Communication and Interpersonal Skills knowledge Transfer skills Vivo voce Teaching and Information Skills Effective use of Library Survey Skills Planning and Control Methods Statistical Tools Patents and Copyrights Advanced Research Techniques and Tools. UNIT IV TECHNIQUES OF TEACHING AND EVALUATION Large group techniques lecture, seminar, symposium, panel discussion-project approaches and workshop. Small Group techniques-group discussion simulation, role playing-Buzz techniques, brain storming, case discussion and assignmentsystem approach in education. Individualized techniques-CAI Keller plan PSI and programmed learning-methods of evaluation-self evaluation and student evaluation in higher education, question banking, diagnostic testing and remedial teaching. UNIT V ESSENTIALS FOR EFFECTIVE COMMUNICATION IN ENGLISH Improving Vocabulary stock-general and technical vocabulary-British and American vocabularyhomophones & homonyms, idioms and phrases-Different grammatical functions of the same wordGrammar-Tenses, Voice, reported speech, Modals, spoken English structures, formal and informalletters, project reports, descriptions, circulars, synopsis and summary writing. Listening skills for competitive exams-Reading skills-skimming and scanning Reading journals, magazines and newspapers for comprehension. Practical use of English conversation, seminars, individual speeches and group discussions. Reference skills-Using dictionary, thesaurus and encyclopedia effectively. Error shooting for better use of English. TEXT BOOKS Alley, Michael, 1996, The Craft of Scientific Writing, 3rd Edition, Springer. Alley, Michael, 2003, The Craft of Scientific Presentations, Springer. REFERENCES

14

Hubbuch, Susan.M, 2005, Writing Research Papers Across the Curriculum, 5 th Edition, Thompson, Florida. Vedanayagam.E.G, 1989, Teaching technology for college teachers, Sterling publishers (Pvt) Ltd, New Delhi. Kumar.K.H, 2005, Educational technology, New age international (Pvt) Ltd, New Delhi. Tony Bates.A.N, 1997, Technology, e-learning and distance education, Rout ledge, New York. Aggarwal.J.C, 1995, Essential of educational technology, Teaching Learning innovations in education , Vikas publishing house (p) Ltd, New Delhi, Crow & Crow, 2005, Educational Psychology, Erusia Publishing House, New Delhi. Ashraf Rizvi.M, Effective technical communication, TataMcGraw Hill Co.Ltd, New Delhi. WEB SITE www.english4engineer.com www.learn4good.com/language/engineer LIST OF ELECTIVES SEMESTER II 11MEVL2E01 ADVANCED MICROPROCESSORS AND MICROCONTROLLERS 3 0 0 3 UNIT I MICROPROCESSOR ARCHITECTURE Instruction set Data formats Instruction formats Addressing modes Memory hierarchy register file Cache Virtual memory and paging Segmentation Pipelining The instruction pipeline pipeline hazards Instruction level parallelism reduced instruction set Computer principles RISC versus CISC RISC properties RISC evaluation On-chip register files versus cache evaluation UNIT II HIGH PERFORMANCE CISC ARCHITECTURE PENTIUM The software model functional description CPU pin descriptions RISC concepts bus operations Super scalar architecture pipe lining Branch prediction The instruction and caches Floating point unit protected mode operation Segmentation paging Protection multitasking Exception and interrupts Input /Output Virtual 8086 model Interrupt processing -Instruction types Addressing modes Processor flags Instruction set -programming the Pentium processor. UNIT III HIGH PERFORMANCE RISC ARCHITECTURE :ARM The ARM architecture ARM assembly language program ARM organization and implementation The ARM instruction set - The thumb instruction set ARM CPU cores. UNIT IV MOTOROLA 68HC11 MICROCONTROLLERS Instructions and addressing modes operating modes Hardware reset Interrupt system Parallel I/O ports Flags Real time clock Programmable timer pulse accumulator serial

15

communication interface A/D converter hardware expansion Assembly language Programming UNIT V PIC MICRO CONTROLLER CPU architecture Instruction set Interrupts Timers I/O port expansion I2C bus for peripheral chip access A/D converter UART REFERENCES Daniel Tabak, 1995, Advanced Microprocessors ,2nd Edition, McGraw Hill.Inc, New York. James L. Antonakos, 1997, The Pentium Microprocessor, 2nd Edition, Pearson Education, New Delhi. Steve Furber, 2000, ARM System On Chip architecture,3rd Edition, Addison Wesley, Boston. Gene .H.Miller, 2003, Micro Computer Engineering,3rd Edition, Pearson Education, New Delhi. John .B. Peatman, 1997, Design with PIC Microcontroller,2nd Edition, Prentice hall. James L.Antonakos, 1999,An Introduction to the Intel family of Microprocessors, 2nd Edition, Pearson Education, New Delhi. 11MEVL2E02 ASIC DESIGN 30 0 3

UNIT I INTRODUCTION Types of ASICs Design Flow CMOS transistors, CMOS design rules Combinational Logic Cell Sequential logic cell Data path logic cell Transistors as Resistors Transistor Parasitic Capacitance Logical effort Library cell design Library architecture. UNIT II PROGRAMMABLE ASICS Anti fuse static RAM EPROM and EEPROM technology PREP bench marks Actel ACT Xilinx LCA Altera FLEX Altera MAX DC & AC inputs and outputs Clock and power inputs Xilinx I/O blocks. UNIT III PROGRAMMABLE ASIC DESIGN SOFTWARE Actel ACT Xilinx LCA Xilinx EPLD Altera MAX 5000 and 7000 Altera MAX 9000 Altera FLEX Design systems Logic Synthesis Half Gate ASIC Schematic entry Low level design language PLA tools EDIF CFI design representation. UNIT IV LOGIC SYNTHESIS, SIMULATION AND TESTING Verilog and logic synthesis VHDL and logic synthesis - Types of simulation Boundary scan test Fault simulation Automatic test pattern generation. UNIT V ASIC CONSTRUCTION AND ROUTING System partition FPGA partitioning partitioning methods floor planning placement physical design flow global routing detailed routing special routing circuit extraction DRC. REFERENCES

16

SMITH.M.J.S, 1997, Application Specific Integrated Circuits, Addison Wesley Longman Inc, Boston. Andrew Brown, 1991 , VLSI Circuits and Systems in Silicon, McGraw Hill, New York. Brown.S.D, Francis.R.J, Rox.J, Uranesic.Z.G, 1992, Field Programmable Gate Arrays, Kluever Academic Publishers. Mohammed Ismail and Terri Fiez, 1994 ,Analog VLSI Signal and Information Processing, McGraw Hill, New York. Kung.S.Y, Whilo House.H.J, Kailath.T, 1985, VLSI and Modern Signal Processing, Prentice Hall. Jose E.France, Yannis Tsividis, 1994, Design of Analog Digital VLSI Circuits for Telecommunication and Signal Processing, Prentice Hall. 11MEVL2E03 VHDL 30 0 3

UNIT I VHDL FUNDAMENTALS Fundamental Concepts Modeling Digital Systems Domains and Levels of Modeling Modeling Languages VHDL Modeling concepts Scalar Data Types and Operations Constants and variables Scalar Types Type Classification Attributes and Scalar types Expressions and operators Sequential Statements If statements Case statements Null Statements Loop statements Assertion and Report statements. UNIT II COMPOSITE DATA TYPES & BASIC MODELING CONSTRUCTS Arrays Unconstrained Array types Array Operations and Referencing Records Basic Modeling Constructs Entity Declarations Architecture Bodies Behavioral Descriptions Structural Descriptions Design Processing. Case Study: A pipelined Multiplier Accumulator.

UNIT III SUBPROGRAMS AND PACKAGES Procedures Procedure Parameters Concurrent Procedure Call Statements functions Overloading Visibility of Declarations Packages and Use Clauses Package declarations Package bodies Use Clauses The predefined Aliases - Aliases for data objects Aliases for Non-Data Items. Case Study: A Bit-Vector Arithmetic Package. UNIT IV SIGNALS, COMPONENTS, CONFIGURATIONS Basic Resolved signals IEEE Std_Logic_1164 Resolved subtypes Resolved signal parameters Generic Constants Parameterizing behavior Parameterizing structure Components and Configurations Components Configuring component Instances Configuration Specification Generate Statements generating iterative structure Conditionally generating structures Configuration of generate Statements. Case Study: The DLX Computer System. UNIT V ADTs AND FILES Access Types Linked Data structures Abstract Data Types using Packages Files and Input/Output Files The Package Textio Verilog. Case Study: Queuing Networks. REFERENCES

17

Peter J.Ashenden, May 2001,The Designers Guide to VHDL, 2 nd Edition, Morgan Kaufmann Publishers, San Francisco. Zainalabedin Navabi, 1998,VHDL Analysis and Modeling of Digital Systems, 2 nd Edition, McGraw Hill International Editions, New York. James M.Lee, Verilog Quick start, 2nd Edition, Kluwer Academic Publishers.

11MEVL2E04 - GENETIC ALGORITHM AND ITS APPLICATION

30 0 3

UNIT I INTRODUCTION Fundamentals of genetic algorithm: A brief history of evolutionary computation biological terminology-search space -encoding, reproduction-elements of genetic algorithm-genetic modelingcomparison of GA and traditional search methods. UNIT II GENETIC ALGORITHMS Genetic technology: steady state algorithm - fitness scaling - inversion. Genetic programming Genetic Algorithm in problem solving UNIT III GENETIC ENGINEERING Genetic Algorithm in engineering and optimization-natural evolution Simulated annealing and Tabu search .Genetic Algorithm in scientific models and theoretical foundations. UNIT - IV IMPLEMENTATION Implementing a Genetic Algorithm computer implementation - low level operator and knowledge based techniques in Genetic Algorithm. UNIT V OPTIMIZATION Applications of Genetic based machine learning-Genetic Algorithm and parallel processors, composite laminates, constraint optimization, multilevel optimization, real life problem. REFERENCES Melanie Mitchell, 2004, An introduction to Genetic Algorithm, Prentice-Hall of India, New Delhi. David.E.Golberg, 1999, Genetic algorithms in search, optimization and machine learning, Addision-Wesley, Boston. Rajasekaran.S and Vijayalakshmi Pai.G.A, 2003, Neural Networks, Fuzzy logic and Genetic Algorithms, Synthesis and Applications, Prentice Hall of India, New Delhi. Nils.J.Nilsson, 1998, Artificial Intelligence- A new synthesis, Morgan Kauffmann Publishers Inc, San Francisco,California. 11MEVL2E05 LOW POWER VLSI DESIGN 30 0 3

18

UNIT I POWER DISSIPATION IN CMOS Hierarchy of limits of power Sources of power consumption Physics of power dissipation in CMOS FET devices- Basic principle of low power design. UNIT II POWER OPTIMIZATION Logical level power optimization Circuit level low power design Circuit techniques for reducing power consumption in adders and multipliers. UNIT III DESIGN OF LOW POWER CMOS CIRCUITS Computer Arithmetic techniques for low power systems Reducing power consumption in memories Low power clock, Interconnect and layout design Advanced techniques Special techniques UNIT IV POWER ESTIMATION Power estimation techniques Logic level power estimation Simulation power analysis Probabilistic power analysis . UNIT V SYNTHESIS AND SOFTWARE DESIGN FOR LOW POWER Synthesis for low power Behavioral level transforms- Software design for low power REFERENCES Roy.K and Prasad.S.C, 2000, LOW POWER CMOS VLSI circuit design, Wiley, New Jersey. Dimitrios Soudris, Chirstian Pignet, Costas Goutis, 2002, Designing CMOS Circuits For Low Power, Kluwer. Kuo.J.B and Lou.J.H, 1999, Low voltage CMOS VLSI Circuits, Wiley, New Jersey. Chandrakasan.A.P and Broadersen.R.W, 1995, Low power digital CMOS design, Kluwer. Gary Yeap, 1998, Practical low power digital VLSI design, Kluwer. Abdellatif Bellaouar,Mohamed.I. Elmasry, 1995, Low power digital VLSI design ,Kluwer. James B. Kuo, Shin chia Lin, 2001, Low voltage SOI CMOS VLSI Devices and Circuits, John Wiley and sons, inc, New Jersey. 11MEVL2E06 UNIT - I ANALOG VLSI DESIGN 30 0 3

BASIC CMOS CIRCUIT TECHNIQUES, CONTINUOUS TIME AND LOW-VOLTAGESIGNAL PROCESSING Mixed-Signal VLSI Chips-Basic CMOS Circuits-Basic Gain Stage-Gain Boosting TechniquesSuper MOSTransistor- Primitive Analog Cells-Linear Voltage-Current Converters-MOS Multipliers and Resistors-CMOS,Bipolar and Low-Voltage BiCMOS Op-Amp DesignInstrumentation Amplifier Design-Low Voltage Filters. UNIT II BASIC BICMOS CIRCUIT TECHNIQUES, CURRENT -MODE SIGNAL PROCESSING & NEURAL INFORMATION PROCESSING Continuous-Time Signal Processing-Sampled-Data Signal Processing-Switched- Current Data Converters-Practical Considerations in SI Circuits Biologically-Inspired Neural Networks -

19

Floating - Gate, Low-Power Neural Networks-CMOS Technology and Models-Design Methodology-Networks-Contrast Sensitive Silicon Retina. UNIT III SAMPLED-DATA ANALOG FILTERS, OVER SAMPLED A/D CONVERTERS AND ANALOG INTEGRATED SENSORS First-order and Second SC Circuits-Bilinear Transformation - Cascade Design-Switched-Capacitor Ladder Filter-Synthesis of Switched-Current Filter- Nyquist rate A/D Converters-Modulators for Over sampled A/D Conversion-First and Second Order and Multibit Sigma-Delta ModulatorsInterpolative Modulators Cascaded Architecture-Decimation Filters-mechanical, Thermal, Humidity and Magnetic Sensors-Sensor Interfaces. UNIT IV DESIGN FOR TESTABILITY & ANALOG VLSI INTERCONNECTS Fault modelling and Simulation - Testability-Analysis Technique-Ad Hoc Methods and General Guidelines-Scan Techniques-Boundary Scan-Built-in Self Test-Analog Test Buses-Design for Electron -Beam Testablity-Physicsof Interconnects in VLSIScaling of Interconnects-A Model for Estimating Wiring Density-A Configurable Architecture for Prototyping Analog Circuits. UNIT V STATISTICAL MODELING & SIMULATION, ANALOG-DIGITAL LAYOUT Review of Statistical Concepts Statistical Device Modeling- Statistical Circuit SimulationAutomation Analog Circuit Design-automatic Analog Layout-CMOS Transistor Layout-Resistor Layout-Capacitor Layout-Analog Cell Layout-Mixed Analog Digital Layout. REFERENCES Mohammed Ismail, Terri Fiez, 1994, Analog VLSI signal and Information Processing, McGrawHill International Editons, New York. Malcom R.Haskard, Lan C.May, 1998," Analog VLSI Design - NMOS and CMOS ", Prentice Hall, New Jersey. Randall L Geiger, Phillip E. Allen, 1990," Noel K.Strader, VLSI Design Techniques for Analog and Digital Circuits ", Mc Graw Hill International Company, New York. Jose E.France, Yannis Tsividis, 1994," Design of Analog-Digital VLSI Circuits for Telecommunication and signal Processing ", Prentice Hall, New Jersey. 11MEVL2E07 CMOS VLSI DESIGN 30 0 3

UNIT I MOS TRANSISTOR THEORY Introduction to I.C Technology. Basic MOS transistors. Threshold Voltage. Body effect. Basic D.C. Equations. Second order effects. MOS models. Small signal A.C characteristics. The complementary CMOS inverter. DC characteristics. Static Load MOS inverters. The differential inverters. Transmission gate. UNIT II CMOS PROCESSING TECHNOLOGY Silicon semiconductor technology. Wafer processing, Oxidation, epitaxy, deposition, Ion implantation. CMOS technology. nwell, pwell process. Silicon on insulator. CMOS process enhancement. Interconnect and circuit elements. Layout design rules. Latchup. UNIT III CIRCUIT CHARACTERISTICS & PERFORMANCE ESTIMATION

20

Resistance estimation. Capacitance estimation. MOS capacitor characteristics. Device capacitances. Diffusion capacitance. SPICE modeling of MOS capacitance. Routing capacitance. Distributed RC effects. Inductance. Switching characteristics. Rise time. Fall time. Delay time. Empirical delay models. Gate delays. CMOS gate transistor sizing. Power dissipation. Scaling of MOS transistor dimensions. UNIT IV CMOS CIRCUIT AND LOGIC DESIGN Cmos Logic gate design. Fan in and fan out. Typical CMOS NAND and NOR delays. Transistor sizing. CMOS logic structures. Complementary logic. BICMOS logic. Pseudo nMOS logic. Dynamic CMOS logic. Clocked CMOS logic. Pass transistor logic. CMOS domino logic. NP domino logic. Cascade voltage switch logic. Source follower pull up Logic (SFPL). Clocking strategies I/O structures. UNIT V CMOS SUBSYSTEM DESIGN Data path operations. Addition/subtraction. Parity generators. Comparators. Zero/one detectors. Binary Counters. ALUs. Multiplication. Array, Radix-n, Wallace Tree and Serial Multiplication. Shifters. Memory elements. RWM, Rom, Content Addressable Memory. Control: FSM, PLA Control Implementation. REFERENCES Neil.H.E.Weste and Eshragian.K, 2000, Principles of CMOS VLSI Design, 2nd Edition, Addison,Wesley, New Jersey Douglas A. Pucknell & K.Eshragian, 2000, Basic VLSI Design, 3rd Edition, PHI, New Delhi. Jacob Baker.R, Harry.W. LI, & David K. Boyce, 2000, CMOS Circuit Design, 3rd Indian reprint, PHI, New Delhi. 11MEVL2E08 DESIGN OF SEMICONDUCTOR MEMORIES 30 0 3

UNIT I RANDOM ACCESS MEMORY TECHNOLOGIES Static Random Access Memories (srams): SRAM Cell Structures-MOS SRAM Architecture-MOS SRAM Cell and Peripheral Circuit Operation-BipolarSRAM Technologies- Silicon On Insulator (SOl) Technology-Advanced SRAM Architectures and Technologies- Application Specific SRAMs. Dynamic Random Access Memories (DRAMs): DRAM Technology DevelopmentCMOS DRAMs-DRAMs Cell Theory and Advanced Cell Strucutures-iCMOS,DRAMs-Soft Error Failures in DRAMs-Advanced DRAM Designs and Architecture-Application Specific DRAMs. UNIT II NONVOLATILE MEMORIES Masked Read-Only Memories (ROMs)-High Density ROMs-Programmable Read-Only Memories (PROMs)-BipolarPROMs-CMOS PROMs-Erasable (UV) - Programmable Road- Only Memories (EPROMs)-Floating-GateEPROM Cell-One-Time Programmable (OTP) Eproms-Electrically Erasable PROMs (EEPROMs)-EEPROM Technology And Arcitecture- Nonvolatile SRAM-Flash Memories (EPROMs or EEPROM)-AdvancedFlash Memory Architecture UNIT III MEMORY FAULT MODELING, TESTING, AND MEMORY DESIGN FOR TESTABILITY AND FAULT TOLERANCE

21

RAM Fault Modeling, Electrical Testing, Peusdo Random Testing-Megabit DRAM TestingNonvolatile Memory Modeling and Testing-IDDQ Fault Modeling and Testing-Application Specific Memory Testing

UNIT IV

SEMICONDUCTOR MEMORY RELIABILITY AND RADIATION EFFECTS General Reliability Issues-RAM Failure Modes and Mechanism-Nonvolatile Memory ReliabilityReliability Modeling and Failure Rate Prediction-Design for Reliability-Reliability Test StructuresReliability Screening andQualification. RAM Fault Modeling, Electrical Testing, Peusdo Random Testing-Megabit DRAM Testing-Nonvolatile Memory Modeling and Testing-IDDQ Fault Modeling and Testing-Application Specific Memory Testing. UNIT V PACKAGING TECHNOLOGIES Radiation Effects-Single Event Phenomenon (SEP)-Radiation Hardening Techniques- Radiation Hardening Process and Design Issues-Radiation Hardened Memory Characteristics-Radiation Hardness Assurance and Testing Radiation Dosimetry-Water Level Radiation Testing and Test Structures. Ferroelectric Random Access Memories (FRAMs)-Gallium Arsenide (GaAs) FRAMsAnalog Memories-Magnetoresistive Random Access Memories (MRAMs)-Experimental Memory Devices. Memory Hybrids and MCMs (2D)-Memory Stacks and MCMs (3D)-Memory MCM Testing and Reliability Issues-Memory Cards-High Density Memory Packaging Future Directions. REFERENCES Ashok K. Sharma, 2002 ,Semiconductor Memories, Technology, Testing, and Reliability, WileyIEEE Press. Ashok K. Sharma, 2003, Semiconductor Memories, Two-Volume Set, Wiley-IEEE Press, Ashok K. Sharma, 1997, Semiconductor Memories-Technology, Testing, and Reliability, Prentice Hall of India Brent Keeth, Jacob Baker.R, 2000,DRAM Circuit Design- A Tutorial, Wiley-IEEE Press. Betty Prince , 1999, High Performance Memories- New Architecture DRAMs and SRAMs Evolution and Function, Wiley, New york. SEMESTER III 11MEVL3E09 PHYSICAL DESIGN OF VLSI CIRCUITS 30 0 3

UNIT I INTRODUCTION TO VLSI TECHNOLOGY Layout Rules-Circuit abstraction Cell generation using programmable logic array transistor chaining, Wein Berger arrays and gate matrices-layout of standard cells gate arrays and sea of gates, field programmable gate array(FPGA)-layout methodologies-Packaging-Computational Complexity-Algorithmic Paradigms UNIT II PLACEMENT USING TOP-DOWN APPROACH

22

Partitioning: Approximation of Hyper Graphs with Graphs, Kernighan-Lin Heuristic- Ratio cutpartition with capacity and i/o constraints. Floor planning: Rectangular dual floor planninghierarchical approach- simulated annealing- Floor plan sizing- Placement: Cost function- force directed method- placement by simulated annealing partitioning placement- module placement on a resistive network regular placement- linear placement.

UNIT III ROUTING USING TOP DOWN APPROACH Fundamentals: Maze Running- line searching- Steiner trees Global Routing: Sequential Approaches- hierarchical approaches- multi commodity flow based techniques- Randomized Routing- One Step approach- Integer Linear Programming Detailed Routing: Channel RoutingSwitch box routing. Routing in FPGA: Array based FPGA- Row based FPGAs UNIT IV PERFORMANCE ISSUES IN CIRCUIT LAYOUT Delay Models: Gate Delay Models- Models for interconnected Delay- Delay in RC trees. Timing Driven Placement: Zero Stack Algorithm- Weight based placement- Linear Programming Approach Timing Driving Routing: Delay Minimization- Click Skew Problem- Buffered Clock Trees. Minimization: constrained via Minimization unconstrained via Minimization- Other issues in minimization UNIT V SINGLE LAYER ROUTING, CELL GENERATION AND COMPACTION Planar subset problem(PSP)- Single layer global routing- Single Layer Global Routing- Single Layer detailed Routing- Wire length and bend minimization technique Over The Cell (OTC) Routing- Multiple chip modules(MCM)- Programmable Logic Arrays- Transistor chaining- Wein Burger Arrays- Gate matrix layout- 1D compaction- 2D compaction. REFERENCES Sarafzadeh, Wong.C.K, 1995 ,An Introduction to VLSI Physical Design, Mc Graw Hill International Edition, New York. Preas M. Lorenzatti, 1998, Physical Design and Automation of VLSI systems, The Benjamin Cummins Publishers. Ban Wong, Anurag Mittal, Yu Cao, Greg Starr, 2004, Nano CMOS Circuit and Physical Design Wiley, John & Sons, Hoboken NJ. Naveed A. Sherwani, 1998, Algorithm for VLSI Physical Design Automation, 3rd Edition , Springer. 11MEVL3E10 NEURAL NETWORKS AND APPLICATIONS 30 0 3

UNIT I BASIC LEARNING ALGORITHMS Biological Neuron Artificial Neural Model - Types of activation functions Architecture: Feedforward and Feedback Learning Process: Error Correction Learning Memory Based Learning Hebbian Learning Competitive Learning - Boltzman Learning Supervised and Unsupervised Learning Learning Tasks: Pattern Space Weight Space Pattern Association Pattern Recognition Function Approximation Control Filtering - Beamforming Memory

23

Adaptation - Statistical Learning Theory Single Layer Perceptron Perceptron Learning Algorithm Perceptron Convergence Theorem Least Mean Square Learning Algorithm Multilayer Perceptron Back Propagation Algorithm XOR problem Limitations of Back Propagation Algorithm.

UNIT II

RADIAL-BASIS FUNCTION NETWORKS AND SUPPORT VECTOR MACHINES Radial Basis Function Networks:Exact Interpolator Regularization Theory Generalized Radial Basis Function Networks - Learning in Radial Basis Function Networks - Applications: XOR Problem Image Classification. Support Vector Machines: Optimal Hyperplane for Linearly Separable Patterns and Nonseparable Patterns Support Vector Machine for Pattern Recognition XOR Problem - insensitive Loss Function Support Vector Machines for Nonlinear Regression UNIT III ATTRACTOR NEURAL NETWORKS Associative Learning Attractor Neural Network Associative Memory Linear Associative Memory Hopfield Network Content Addressable Memory Strange Attractors and Chaos Error Performance of Hopfield Networks - Applications of Hopfield Networks Simulated Annealing Boltzmann Machine Bidirectional Associative Memory BAM Stability Analysis Error Correction in BAMs - Memory Annihilation of Structured Maps in BAMS Continuous BAMs Adaptive BAMs Applications UNIT IV ADAPTIVE RESONANCE THEORY Noise-Saturation Dilemma - Solving Noise-Saturation Dilemma Recurrent On-center Offsurround - Networks Building Blocks of Adaptive Resonance Substrate of Resonance Structural Details of Resonance Model Adaptive Resonance Theory Applications UNIT V SELF ORGANISING MAPS Self-organizing Map Maximal Eigenvector Filtering Sangers Rule Generalized Learning Law Competitive Learning - Vector Quantization Mexican Hat Networks Selforganizing, Feature Maps Applications. REFERENCES Satish Kumar, 2004, Neural Networks- A Classroom Approach, Tata McGraw-Hill Publishing Company Limited, New Delhi. Simon Haykin, 2001, Neural Networks: A Comprehensive Foundation, 2nd edition, Addison Wesley Longman (Singapore) Private Limited, New Delhi. Martin T.Hagan, Howard B. Demuth, and Mark Beale, 2003, Neural Network Design, Thomson Learning, New Delhi. James A. Freeman and David M. Skapura, 2003, Neural Networks Algorithms, Applications, and Programming Techniques, Pearson Education (Singapore) Private Limited, New Delhi. Rajasekaran.S, Vijayalakshmi Pai.G.A, 2003, Neural Networks, Fuzzy Logic and Genetic Algorithms, Synthesis and Applications, PHI, New Delhi.

24

11MEVL3E11

RELIABILITY ENGINEERING

30 0 3

UNIT I PROBABILITY PLOTTING AND LOAD-STRENGTH INTERFERENCE Statistical distribution , statistical confidence and hypothesis testing ,probability plotting techniques Weibull, extreme value ,hazard, binomial data; Analysis of load strength interference , Safety margin and loading roughness on reliability. UNIT II RELIABILITY PREDICTION, MODELLING AND DESIGN Statistical design of experiments and analysis of variance Taguchi method, Reliability prediction, Reliability modeling, Block diagram and Fault tree Analysis ,petric Nets, State space Analysis, Monte carlo simulation, Design analysis methods quality function deployment, load strength analysis, failure modes, effects and criticality analysis. UNIT III ELECTRONICS AND SOFTWARE SYSTEMS RELIABILITY Reliability of electronic components, component types and failure mechanisms, Electronic system reliability prediction, Reliability in electronic system design; software errors, software structure and modularity, fault tolerance, software reliability, prediction and measurement, hardware/software interfaces. UNIT IV RELIABILITY TESTING AND ANALYSIS Test environments, testing for reliability and durability, failure reporting, Pareto analysis, Accelerated test data analysis, CUSUM charts, Exploratory data analysis and proportional hazards modeling, reliability demonstration, reliability growth monitoring. UNIT V MANUFACTURE AND RELIABILITY MAQNAGEMENT Control of production variability, Acceptance sampling, Quality control and stress screening, Production failure reporting; preventive maintenance strategy, Maintenance schedules, Design for maintainability, Integrated reliability programmes , reliability and costs, standard for reliability, quality and safety, specifying reliability, organization for reliability. REFERENCES Patrick D.T. OConnor, David Newton and Richard Bromley, 2002, Practical Reliability Engineering, 4th edition, John Wiley & Sons, New Jersey. David J. Klinger, Yoshinao Nakada and Maria A. Menendez, Von Nostrand Reinhold, 1998, "AT & T Reliability Manual", 5th Edition, New York. Gregg K. Hobbs, 2000, "Accelerated Reliability Engineering - HALT and HASS", John Wiley & Sons, New York. Lewis, 1996, "Introduction to Reliability Engineering", 2nd Edition, Wiley International, New York. 11MEVL3E12 ELECTROMAGNETIC INTERFERENCE AND COMPATIBILITY IN SYSTEM DESIGN 3 0 0 3

25

UNIT I EMI/EMC CONCEPTS EMI-EMC definitions and Units of parameters; Sources and victim of EMI; Conducted and Radiated EMI Emission and Susceptibility; Transient EMI, ESD; Radiation Hazards. UNIT II EMI COUPLING PRINCIPLES Conducted, radiated and transient coupling; Common ground impedance coupling ; Common mode and ground loop coupling ; Differential mode coupling ; Near field cable to cable coupling, cross talk ; Field to cable coupling ; Power mains and Power supply coupling. UNIT III EMI CONTROL TECHNIQUES Shielding, Filtering, Grounding, Bonding, Isolation transformer, Transient suppressors, Cable routing, Signal control. UNIT IV EMC DESIGN OF PCBS Component selection and mounting; PCB trace impedance; Routing; Cross talk control; Power distribution decoupling; Zoning; Grounding; VIAs connection; Terminations. UNIT V EMI MEASUREMENTS AND STANDARDS Open area test site; TEM cell; EMI test shielded chamber and shielded ferrite lined anechoic chamber; Tx /Rx Antennas, Sensors, Injectors / Couplers, and coupling factors; EMI Rx and spectrum analyzer; Civilian standards-CISPR, FCC, IEC, EN; Military standards-MIL461E/462. REFERENCES Kodali,V.P, 1996, Engineering EMC Principles, Measurements and Technologies, IEEE Press, Newyork. Henry W.Ott, 1997,Noise Reduction Techniques in Electronic Systems, 2nd edition,A Wiley Inter Science Publications, John Wiley and Sons, Newyork. Bemhard Keiser, 1987, Principles of Electromagnetic Compatibility,3 rd Edition, Artech house, Norwood. Paul.C.R, 1992,Introduction to Electromagnetic Compatibility , John Wiley and Sons, Inc,New york. Don R.J.White Consultant Incorporate, 1988, Handbook of EMI/EMC , Vol I-V. 11MEVL3E13 DIGITAL SPEECH SIGNAL PROCESSING 30 0 3

UNIT I MECHANICS OF SPEECH Speech production mechanism Nature of Speech signal Discrete time modelling of Speech production Representation of Speech signals Classification of Speech sounds Phones Phonemes Phonetic and Phonemic alphabets Articulatory features. Music production Auditory perception Anatomical pathways from the ear to the perception of sound Peripheral auditory system Psycho acoustics UNIT II TIME DOMAIN METHODS FOR SPEECH PROCESSING Time domain parameters of Speech signal Methods for extracting the parameters Energy, Average Magnitude Zero crossing Rate Silence Discrimination using ZCR and

26

energy Short Time Auto Correlation Function Pitch period estimation using Auto Correlation Function UNIT III FREQUENCY DOMAIN METHOD FOR SPEECH PROCESSING Short Time Fourier analysis Filter bank analysis Formant extraction Pitch Extraction Analysis by Synthesis- Analysis synthesis systems- Phase vocoderChannel Vocoder. HOMOMORPHIC SPEECH ANALYSIS Cepstral analysis of Speech Formant and Pitch Estimation Homomorphic Vocoders. UNIT IV LINEAR PREDICTIVE ANALYSIS OF SPEECH Formulation of Linear Prediction problem in Time Domain Basic Principle Auto correlation method Covariance method Solution of LPC equations Cholesky method Durbins Recursive algorithm lattice formation and solutions Comparison of different methods Application of LPC parameters Pitch detection using LPC parameters Formant analysis VELP CELP. UNIT V APPLICATION OF SPEECH SIGNAL PROCESSING Algorithms: Spectral Estimation, dynamic time warping, hidden Markov model Music analysis Pitch Detection Feature analysis for recognition Automatic Speech Recognition Feature Extraction for ASR Deterministic sequence recognition Statistical Sequence recognition ASR systems Speaker identification and verification Voice response system Speech Synthesis: Text to speech, voice over IP. REFERENCES Ben Gold and Nelson Morgan, 2004,Speech and Audio Signal Processing, John Wiley and Sons Inc. Singapore, Rabiner.L.R and Schaffer.R.W, 1978, Digital Processing of Speech signals , Prentice Hall, New Jersey. Quatieri , 2001, Discrete-time Speech Signal Processing, Prentice Hall,New Jersey. Flanagan.J.L,1972 ,Speech analysis- Synthesis and Perception, 2nd edition, Berlin. Witten.I.H, 1982, Principles of Computer Speech, Academic Press, New york.

11MEVL3E14 DSP PROCESSOR ARCHITECTURE AND PROGRAMMING

300 3

UNIT I FUNDAMENTALS OF PROGRAMMABLE DSPs Multiplier and Multiplier accumulator Modified Bus Structures and Memory access in P- DSPs Multiple access memory Multi-port memory VLIW architecture- Pipelining Special Addressing modes in P-DSPs On chip Peripherals. UNIT II TMS320C5X PROCESSOR Architecture Assembly language syntax - Addressing modes Assembly language Instructions Pipeline structure, Operation Block Diagram of DSP starter kit Application Programs for processing real time signals.

27

UNIT III TMS320C3X PROCESSOR Architecture Data formats - Addressing modes Groups of addressing modes- Instruction sets Operation Block Diagram of DSP starter kit Application Programs for processing real time signals Generating and finding the sum of series, Convolution of two sequences, Filter design UNIT IV ADSP PROCESSORS Architecture of ADSP-21XX and ADSP-210XX series of DSP processors- Addressing modes and assembly language instructions Application programs Filter design, FFT calculation. UNIT V ADVANCED PROCESSORS Architecture of TMS320C54X: Pipe line operation, Code Composer studio Architecture of TMS320C6X Architecture of Motorola DSP563XX Comparison of the features of DSP family processors. REFERENCES Venkataramani.B and Bhaskar.M, 2003,Digital Signal Processors Architecture, Programming and Applications, Tata McGraw Hill Publishing Company Limited, New Delhi. User guides Texas Instrumentation, Analog Devices, Motorola.

28

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Analog Communications: Lab ManualDokumen99 halamanAnalog Communications: Lab Manualuday kiranBelum ada peringkat

- All India Anna Oravida Munnetra KAZHAGI:..r"! R.Egulations: (Inc Amendments Passed by THF On 5.2-2.007)Dokumen38 halamanAll India Anna Oravida Munnetra KAZHAGI:..r"! R.Egulations: (Inc Amendments Passed by THF On 5.2-2.007)செல்வம் முத்துராமன்Belum ada peringkat

- BamaDokumen1 halamanBamaசெல்வம் முத்துராமன்Belum ada peringkat

- Cs PDFDokumen224 halamanCs PDFசெல்வம் முத்துராமன்Belum ada peringkat

- TV, ECS - CoursesDokumen1 halamanTV, ECS - Coursesசெல்வம் முத்துராமன்Belum ada peringkat

- IndexDokumen1 halamanIndexசெல்வம் முத்துராமன்Belum ada peringkat

- Draft NEP 2019 en RevisedDokumen484 halamanDraft NEP 2019 en RevisedArjun PrabhakaranBelum ada peringkat

- Experiment.3.SingleTunedAmp 22112016Dokumen12 halamanExperiment.3.SingleTunedAmp 22112016Saurav kumarBelum ada peringkat

- How To ApplyDokumen6 halamanHow To ApplyKpsmurugesan KpsmBelum ada peringkat

- 18ecu01 BenDokumen7 halaman18ecu01 Benசெல்வம் முத்துராமன்Belum ada peringkat

- ICI SchemeDokumen8 halamanICI Schemeசெல்வம் முத்துராமன்Belum ada peringkat

- EC6504 Microprocessor and Microcontroller PDFDokumen165 halamanEC6504 Microprocessor and Microcontroller PDFசெல்வம் முத்துராமன்Belum ada peringkat

- Expt4 Chopper AmplifierDokumen2 halamanExpt4 Chopper AmplifierESAUBelum ada peringkat

- BENDokumen7 halamanBENசெல்வம் முத்துராமன்Belum ada peringkat

- Goms 65 24042019Dokumen12 halamanGoms 65 24042019செல்வம் முத்துராமன்Belum ada peringkat

- 18ECU17-Linear Integrated Circuits LabDokumen1 halaman18ECU17-Linear Integrated Circuits Labசெல்வம் முத்துராமன்Belum ada peringkat

- 18ECU04-Integrated Circuits and InstrumentationDokumen3 halaman18ECU04-Integrated Circuits and Instrumentationசெல்வம் முத்துராமன்Belum ada peringkat

- 4901Dokumen4 halaman4901செல்வம் முத்துராமன்Belum ada peringkat

- Executive DevelopmentDokumen2 halamanExecutive Developmentசெல்வம் முத்துராமன்Belum ada peringkat

- Executive Development PDFDokumen2 halamanExecutive Development PDFசெல்வம் முத்துராமன்Belum ada peringkat

- Design of Low Power Multiplier Using CNTFET: 2017 IEEE 7th International Advance Computing Conference (IACC)Dokumen4 halamanDesign of Low Power Multiplier Using CNTFET: 2017 IEEE 7th International Advance Computing Conference (IACC)செல்வம் முத்துராமன்Belum ada peringkat

- Financial Analysis of Shanthi Gears Limited, Coimbatore"Dokumen19 halamanFinancial Analysis of Shanthi Gears Limited, Coimbatore"செல்வம் முத்துராமன்Belum ada peringkat

- Cover PagesDokumen13 halamanCover Pagesசெல்வம் முத்துராமன்Belum ada peringkat

- How To ApplyDokumen6 halamanHow To ApplyKpsmurugesan KpsmBelum ada peringkat

- Final Course July-Dec 2019Dokumen20 halamanFinal Course July-Dec 2019செல்வம் முத்துராமன்Belum ada peringkat

- AC 02 (01) AC 02 (01) : Department: Electronics and Communication Systems Semester: EvenDokumen6 halamanAC 02 (01) AC 02 (01) : Department: Electronics and Communication Systems Semester: Evenசெல்வம் முத்துராமன்Belum ada peringkat

- New Microsoft Word DocumentDokumen2 halamanNew Microsoft Word Documentசெல்வம் முத்துராமன்Belum ada peringkat

- Robotics and Machine Vision SystemDokumen55 halamanRobotics and Machine Vision Systemசெல்வம் முத்துராமன்Belum ada peringkat

- 2 Days: DAY 1 SessionDokumen2 halaman2 Days: DAY 1 Sessionசெல்வம் முத்துராமன்Belum ada peringkat

- 2 Days: DAY 1 SessionDokumen2 halaman2 Days: DAY 1 Sessionசெல்வம் முத்துராமன்Belum ada peringkat

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (120)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Electronics Designer's Cookbook PDFDokumen186 halamanElectronics Designer's Cookbook PDFmathurashwaniBelum ada peringkat

- ECE202 LAB02 JFET Frequency ResponseDokumen7 halamanECE202 LAB02 JFET Frequency ResponseEloisa VictorioBelum ada peringkat

- 00536822Dokumen7 halaman00536822Rogerio PaludoBelum ada peringkat

- Boylestad Electronics Multiple Choice Q&a ChapterDokumen6 halamanBoylestad Electronics Multiple Choice Q&a ChapterDenaiya Watton LeehBelum ada peringkat

- Introduction To PLCsDokumen42 halamanIntroduction To PLCsArun Kumar YadavBelum ada peringkat

- Electronics and Circuit Analysis Using MATLABDokumen17 halamanElectronics and Circuit Analysis Using MATLABjames3h3parkBelum ada peringkat

- ISA2 Old e PDFDokumen15 halamanISA2 Old e PDFMNM AdminBelum ada peringkat

- D1RF Series / V2RF Series: Fiber-SensorsDokumen6 halamanD1RF Series / V2RF Series: Fiber-SensorsDaniel RidaoBelum ada peringkat

- MCQ in Industrial Electronics - Pinoybix - All PDFDokumen23 halamanMCQ in Industrial Electronics - Pinoybix - All PDFHazel GraceBelum ada peringkat

- Air University: Department of Electrical and Computer Engineering Lab TitleDokumen5 halamanAir University: Department of Electrical and Computer Engineering Lab TitleAMMAD MAHMOODBelum ada peringkat

- Siemens 3RG7404 0CH00 DatasheetDokumen54 halamanSiemens 3RG7404 0CH00 DatasheetManea George-CristianBelum ada peringkat

- PLC64 Hardware ManualDokumen21 halamanPLC64 Hardware Manualsfist tesdaBelum ada peringkat

- Kps 2222aDokumen3 halamanKps 2222apruebapreuba2015Belum ada peringkat

- 2SB892 / 2SD1207: Data SheetDokumen5 halaman2SB892 / 2SD1207: Data SheetSamuel RodrigoBelum ada peringkat

- CCH - 8 - Differential and Multistage AmplifierDokumen124 halamanCCH - 8 - Differential and Multistage Amplifier鄭又嘉Belum ada peringkat

- Bipolar Transistor EvaluationDokumen15 halamanBipolar Transistor Evaluationmark777markBelum ada peringkat

- EDCDokumen1 halamanEDClakshmipoBelum ada peringkat

- Working With Displays - Book 2 of The Arduino Short Reads SeriesDokumen87 halamanWorking With Displays - Book 2 of The Arduino Short Reads SeriesJorge Jockyman JuniorBelum ada peringkat

- MJ 15004Dokumen5 halamanMJ 15004Adal VeraBelum ada peringkat

- AM GenerationDokumen132 halamanAM GenerationShashank Kna Hna Hs100% (2)

- On TapDokumen7 halamanOn TapLê Minh ThắngBelum ada peringkat

- BD135 BD139: NPN Silicon TransistorsDokumen4 halamanBD135 BD139: NPN Silicon TransistorsLaurentiu IacobBelum ada peringkat

- Keil Agsi 7 Seg LedsDokumen7 halamanKeil Agsi 7 Seg LedsSourav MondalBelum ada peringkat

- Ece 334 ManualDokumen37 halamanEce 334 ManualZelalem GirmaBelum ada peringkat

- Noise Modeling PDFDokumen112 halamanNoise Modeling PDFSHAIK MUSTHAFABelum ada peringkat

- Tri Boost Kit Instructions: Click Here For Older Triboost Version Instructions (No 3-Way LED)Dokumen17 halamanTri Boost Kit Instructions: Click Here For Older Triboost Version Instructions (No 3-Way LED)rick_marcominiBelum ada peringkat

- ACDC Pages 17-32 (Low Res)Dokumen16 halamanACDC Pages 17-32 (Low Res)Naufal MaulanaBelum ada peringkat

- FY BSC Aeronautics (Avo)Dokumen25 halamanFY BSC Aeronautics (Avo)Pritam BombleBelum ada peringkat

- BJTDokumen46 halamanBJTshubhiyadavBelum ada peringkat

- Electronic Invent 14 G WadDokumen300 halamanElectronic Invent 14 G WadXemanon Ero100% (1)