Dma

Diunggah oleh

mrmiguel_32530Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Dma

Diunggah oleh

mrmiguel_32530Hak Cipta:

Format Tersedia

SEP

SNEST

DGEST

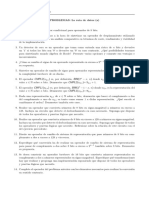

INSTITUTO TECNOLGICO DE TOLUCA

INGENIERIA EN SISTEMAS COMPUTACIONALES

RESUMEN DMA

ASIGNATURA

Arquitectura de Computadoras

PROFESOR(A)

Francisco Ramrez

POR:

Miranda lvarez Evilenia Miguel ngel Ramrez Bautista Miguel ngel Villa Bastida

METEPEC, ESTADO DE MXICO A 10 DE MARZO DE 201110 DE MARZO DE 2011

DMA La tcnica DMA para E/S permite el acceso directo a la memoria mientras el procesador este deshabilitado en forma temporal. Esto permite transferir datos entre la memoria y el dispositivo E/S a una velocidad que solo est limitada por la velocidad de los componentes de la memoria del sistema o controlador de DMA. Su velocidad en transfrencia de 10 a 12 Mbytes. Las transferencias DMA se emplean para refrescar la DRAM, memoria de video para refrescar la pantalla y lecturas y escrituras en el sistema de memoria de disco. En su operacin se utilizan dos seales de control para solicitar y reconoce una transferencia de acceso directo a memoria. HOLD(entrada) se utiliza para solicitar una accin de DMA y HLDA es la que reconoce la accin. HOLD es igual a 1.El microprocesador responde, en unos cuantos pulsos de reloj, suspendiendo la ejecucin del programa y colocando los canales de direccin, datos y de control en su estado de alta impedancia. HOLD tiene mayor prioridad que las entradas de interrupcin INTR o NMI. Interrupciones son al final de la instruccin y HOLD a la mitad de instruccin. RESET es la nica terminal que tiene ms prioridad que HOLD. La seal HLDA se activa para indicar que el microprocesador ha llevado sus canales al estado de lata impedancia. Una lectura de DMA transfiere los datos de la memoria hacia E/S. Una escritura de DMA transfiere los datos a un dispositivo de E/S hacia la memoria. En ambas operaciones, la memoria y el espacio E/S se controlan simultneamente y eso es porque el sistema contiene Seales separadas para control de memoria y E/S. La velocidad de transferencia de datos se determina por la velocidad del dispositivo de memoria o de un controlador que, a menudo, controla las transferencias de DMA. Si la velocidad de memoria es de 100 ns, las transferencias de DMA ocurrirn a una frecuencia de hasta 1/100ns o sea 10 Mbytes por segundo. Si el controlador de DMA en un sistema funciona a una frecuencia mxima de 5 MHz y todava se va a utilizar la memoria de 100 ns, la frecuencia mxima de transferencia es de 5 MMz porque el controlador de DMA es ms lento qtos a alta velocidadue la memoria. En muchos casos, el controlador de DMA reduce la velocidad del sistema cuando ocurren las transferencias de DMA. CONTROLADOR 8237 DE AMD Suministra a la memoria y al E/S seales de control de informacin y direccionamiento a la memoria durante la transferencia de DMA. El es un microprocesador que transfiere da tos a alta velocidad entre la memoria y el espacio E/S. El 8237 tiene cuatro canales y es compatible con los microprocesadores 8086 y 8088. Y puede expandirse para incluir cualquier nmero de entradas de canal DMA, aunque 4 canales son adecuados para muchos sistemas pequeos.

Definicin de terminales CLK: conecta con reloj, siempre y cuando sea de 5MHz o menos CS: selecciona el integrado RESET: inicializa, borra los registros de comandos, estado, solicitud y temporales. READY: el 8237 inserta estados de espera para los componentes de memoria HLDA: reconoce cesin DREQ: son entradas que se emplean para solicitar transferencias de DMA DB: canales de datos IOR: es una terminal bidireccional lee E/S IOW: escribe en E/S EOP: seal bidireccional que se emplea como entrada para terminar un proceso de DMA o como salida para sealar el final de una transferencia de DMA. DACK3-DACK0: reconocimiento de canal DMA AEN: Habilitacin de direccin ADSTB: seal estroboscpica de habilitacin de direccin MEMR: lectura de memoria MEMW: escritura de memoria

REGISTROS INTERNOS Registro de direccin actual (CAR): contiene la direccin en memoria de 16 bits utilizada para la transferencia de DMA. Cada canal tiene su propio registro CAR para ello. Cuando se transfiere un dato durante una operacin de DMA, se incrementa o decrementa el CAR, segn se programo. Registro de contador (CWCR): programa a un canal para el numero de bits(hasta 64) transferidos durante una accin DMA. El no. Cargado en este registro es uno menos que el numero de bits transferidos. Direccin base (BA): y contador de palabras base (BWC): se emplean para seleccionar la auto inicializacin automtica de un canal. En el modo de auto inicializacin, estos registros se emplean para volver a cargar los registros CAR y CWCR despus que ha concluido la accin DMA. Registro de comandos (CR): programa la operacin del controlador 8237. Registro de modo (MR): programa de modo de operacin de un canal. Cada canal tiene su propio registro de modo, seleccionado por las posiciones de bit 1 y 0. Los bits restantes del registro de modo se seleccionan operacin, auto inicializacin, incremento/decremento y modo para el canal. Los modos de funcionamiento, incluyen: modo demanda, nico, modo bloque y modo cascada. Modo demanda transfiere datos hasta que entra la seal EOP externa o hasta que la entrada DREQ se vuelve iniciativa. Modo nico libera la seal de HOLD despus de transferir cada byte de datos. El modo bloque transfiere de forma automtica el numero de bytes indicado por el registro contador del canal. El modo cascada se emplea cuando hay ms de un 8237 que trabaje en un sistema. Registro de solicitud (RR): se emplea para solicitar una transferencia de DMA por programa. Activar o desactivar registro de enmascaramiento (MRSR): Activa o desactiva dicho registro. La seal RESET activa los enmascaramientos deshabilitando todos los canales. Registro de enmascaramiento (SR): habilita o deshabilita todos los enmascaramientos con un comando, en lugar del enmascaramiento individual de cada canal como con MRSR. Registro de Estado (SR): muestra el estado de cada canal de DMA los bits TC indican si el canal ha llegado a su cuenta terminal (transferencia de todos sus bytes). Las funciones de los comandos de programacin son: 1.-Borra el primero/ultimo flip-flop: Esto dentro del 8237, Ese flip-flop selecciona cual byte (alto o bajo) se lee o se escribe en los registros de direccin y de conteo actuales. 2.-Inicio Maestro: Acta en la misma forma exacta que la seal RESET para 8237. Este comando, igual que la seal RESET deshabilita todos los canales. 3.-Desactivar registro de enmascaramiento: habilita a los cuatro canales de DMA.

FUNCIONAMIENTO DEL CANAL DE (BUS) COMPARTIDO Multiprocesamiento es cuando algunos sistemas emplean ms de un microprocesador para efectuar su trabajo, tambin llamado sistema distribuido. Y a un sistema que lleva a cabo ms de una tarea se le llama multitarea. En sistemas que tienen ms de un microprocesador se debe crear y emplear algn mtodo de control. En un ambiente distribuido, multiprocesamiento, multitarea, c

Anda mungkin juga menyukai

- Programacion Del 8088Dokumen11 halamanProgramacion Del 8088mrmiguel_32530Belum ada peringkat

- 2009 12 15 Bpmnenadonisflyer Elmlgudor 100107032533 Phpapp01Dokumen2 halaman2009 12 15 Bpmnenadonisflyer Elmlgudor 100107032533 Phpapp01mrmiguel_32530Belum ada peringkat

- Emulador EMU8086Dokumen15 halamanEmulador EMU8086Ariel OrtzBelum ada peringkat

- Emulador EMU8086Dokumen15 halamanEmulador EMU8086Ariel OrtzBelum ada peringkat

- Tarea Iso2 UmlDokumen17 halamanTarea Iso2 UmlEdwin CruzBelum ada peringkat

- Laeducacinbsicaenmxico1962 2013 130808121117 Phpapp01 PDFDokumen16 halamanLaeducacinbsicaenmxico1962 2013 130808121117 Phpapp01 PDFmrmiguel_32530Belum ada peringkat

- Curso Completo de HTML Jorge Ferrer Victor Garcia Rodrigo Garcia HTML Programacion ManualDokumen447 halamanCurso Completo de HTML Jorge Ferrer Victor Garcia Rodrigo Garcia HTML Programacion ManualT-Punisher100% (2)

- Compuertas lógicas TTLDokumen4 halamanCompuertas lógicas TTLAlberto PanameñoBelum ada peringkat

- Ups CT002157Dokumen204 halamanUps CT002157jasminunikaBelum ada peringkat

- SoDokumen37 halamanSomrmiguel_32530Belum ada peringkat

- Como y Porque Seleccionar Camaras de Seguridad de Megapixeles IP y Analogicas PDFDokumen10 halamanComo y Porque Seleccionar Camaras de Seguridad de Megapixeles IP y Analogicas PDFmrmiguel_32530Belum ada peringkat

- Desarrollo de Proyectos de Software: División de Ingeniería en Sistemas ComputacionalesDokumen100 halamanDesarrollo de Proyectos de Software: División de Ingeniería en Sistemas ComputacionalesIvan Guadalupe Hernandez DominguezBelum ada peringkat

- Tesis Desnutricion Del Rendimiento Educativo PDFDokumen50 halamanTesis Desnutricion Del Rendimiento Educativo PDFmrmiguel_32530Belum ada peringkat

- Tutorial AssemblerDokumen99 halamanTutorial AssemblerJedion Melbin Paucar Cardenas100% (4)

- La Función de La Seguridad en Cloud ComputingDokumen12 halamanLa Función de La Seguridad en Cloud Computingrobertomarques106130Belum ada peringkat

- Desarrollo de Proyectos de Software: División de Ingeniería en Sistemas ComputacionalesDokumen100 halamanDesarrollo de Proyectos de Software: División de Ingeniería en Sistemas ComputacionalesIvan Guadalupe Hernandez DominguezBelum ada peringkat

- Planificacion y ModeladoDokumen86 halamanPlanificacion y ModeladoEber SanchezBelum ada peringkat

- Sistema de Seguridad Por Reconocimiento de Voz (Tesis de Ingenieria ESIME) PDFDokumen81 halamanSistema de Seguridad Por Reconocimiento de Voz (Tesis de Ingenieria ESIME) PDFEstelaZetinaBelum ada peringkat

- Curso Básico de EnsambladorDokumen67 halamanCurso Básico de Ensambladorinfobits100% (10)

- Micro Control AdoresDokumen54 halamanMicro Control Adoresmrmiguel_32530Belum ada peringkat

- Desarrollo de Proyectos de Software - ISCDokumen9 halamanDesarrollo de Proyectos de Software - ISCRafa MendezBelum ada peringkat

- Aprendizaje SupervisadoDokumen24 halamanAprendizaje Supervisadomrmiguel_32530Belum ada peringkat

- Checar Entrada y SalidaDokumen1 halamanChecar Entrada y Salidamrmiguel_32530Belum ada peringkat

- TAREA4Dokumen17 halamanTAREA4Uriel SbBelum ada peringkat

- Conceptos Electronica IndustrialDokumen5 halamanConceptos Electronica Industrialjulio durandBelum ada peringkat

- Como Solucionar Su PC No Está Conectado A InternetDokumen3 halamanComo Solucionar Su PC No Está Conectado A InternetBG JluisBelum ada peringkat

- Copia de Mapa Conceptual MantenimientoDokumen1 halamanCopia de Mapa Conceptual Mantenimientomarcela ladino0% (1)

- Ccna Semestre 1 Examen 10 (100%)Dokumen8 halamanCcna Semestre 1 Examen 10 (100%)rukismenBelum ada peringkat

- Topologías de Redes PDHDokumen9 halamanTopologías de Redes PDHLozano Sanchez Miguel AngelBelum ada peringkat

- Repaso de conceptos y ejemplos de programación PLC DL06Dokumen72 halamanRepaso de conceptos y ejemplos de programación PLC DL06Rodolfo Loza100% (1)

- Ejemplos de Problemas Con ArreglosDokumen27 halamanEjemplos de Problemas Con ArreglosJEFERBelum ada peringkat

- Enunciado PEC1 81515 2020 SOLDokumen12 halamanEnunciado PEC1 81515 2020 SOLmanuelBelum ada peringkat

- Formatear Usb Protegida Contra EscrituraDokumen4 halamanFormatear Usb Protegida Contra Escrituraodennys JarquinBelum ada peringkat

- Apple-Segmentacion Del MercadoDokumen10 halamanApple-Segmentacion Del MercadoMateo GanchalBelum ada peringkat

- SP85 RevF UserGde 59064 es-ESDokumen122 halamanSP85 RevF UserGde 59064 es-ESRodrigo caballeroBelum ada peringkat

- Cakephp Manual Español 1.1Dokumen92 halamanCakephp Manual Español 1.1hrivera@exusmultimedia.com100% (22)

- 236114Dokumen45 halaman236114Fernando Reyes CalvoBelum ada peringkat

- Fanuc KukaDokumen250 halamanFanuc KukaClecio de PaulaBelum ada peringkat

- Tipos de Cable Utp, STP y Cable CoaxialDokumen9 halamanTipos de Cable Utp, STP y Cable CoaxialANGEL MAURICIO SARMIENTO ZARZOSABelum ada peringkat

- BOLETIN 126 - Detector de Movimiento Inalámbrico Doble Tecnología Climax IRMP-23Dokumen10 halamanBOLETIN 126 - Detector de Movimiento Inalámbrico Doble Tecnología Climax IRMP-23Ivan FonsecaBelum ada peringkat

- Circuito 555 temporizador versátilDokumen21 halamanCircuito 555 temporizador versátillunajoseBelum ada peringkat

- Reporte Practica2 TimerDokumen2 halamanReporte Practica2 TimerLary Guzman100% (1)

- Brochure Care OrchestratorDokumen5 halamanBrochure Care OrchestratorPablo Simón Narbona MenaBelum ada peringkat

- Requerimientos de Betgol Virtuales Actual 2022Dokumen3 halamanRequerimientos de Betgol Virtuales Actual 2022Karem CornejoBelum ada peringkat

- Correo ElectrónicoDokumen6 halamanCorreo ElectrónicoTatis GomezBelum ada peringkat

- Microprocesadores y MicrocontroladoresDokumen8 halamanMicroprocesadores y MicrocontroladoresA Gardenia100% (1)

- Practica1Shell MohaDokumen16 halamanPractica1Shell MohaGinés SaézBelum ada peringkat

- Laboratorio No 5 (Switch y Vlan)Dokumen7 halamanLaboratorio No 5 (Switch y Vlan)Franklin Vargas MoriBelum ada peringkat

- Clase #1 - BienvenidaDokumen17 halamanClase #1 - BienvenidaCarlos Mario Perez CastillaBelum ada peringkat

- Tarea - Perifericos de La ComputadoraDokumen3 halamanTarea - Perifericos de La ComputadoraAaron Chicaiza100% (1)

- Avolites Titan 1 GuiaDokumen37 halamanAvolites Titan 1 GuiaNåndo Scorsela100% (1)

- Lista de Precios Trascentek SAS 07 09 2020 PDFDokumen19 halamanLista de Precios Trascentek SAS 07 09 2020 PDFMAKRO SERVERBelum ada peringkat

- La Ruta de Datos ADokumen2 halamanLa Ruta de Datos AHotYoelBelum ada peringkat

- Criterios de Selección de HardwareDokumen3 halamanCriterios de Selección de HardwareHeiner FonsecaBelum ada peringkat