Apuntes Sobre Amplificador Diferencial Basado en Transistores JFET PDF

Diunggah oleh

Edison OrtegaJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Apuntes Sobre Amplificador Diferencial Basado en Transistores JFET PDF

Diunggah oleh

Edison OrtegaHak Cipta:

Format Tersedia

Tema 2.

0 Amplificador diferencial basado en transistores JFET Es bien sabido que los amplificadores basados en transistores FET (ya sea MOSFET incremental (enhancement mode mosfet), MOSFET decremental (depletion mode mosfet) o JFET), ofrecen dos cualidades muy superiores a las ofrecidas por amplificadores basados en transistores BJT. Estas son: Muy alta impedancia de entrada (del orden de 109 ohms, o superior). La impedancia de entrada es inversamente proporcional al nivel de corriente que el amplificador consume o bien, extrae de etapas previas de un circuito. Por lo tanto, es deseable que la etapa de amplificacin posea alta impedancia de entrada, ya que comnmente, las etapas previas solo pueden proporcionar seales con niveles muy pequeos de corriente y voltaje. Mayor frecuencia de operacin. Debido a la propia naturaleza del transistor FET, este dispositivo ofrece mayor velocidad de respuesta a una seal o estmulo de entrada. Esto permite que amplifique adecuadamente, seales de altas frecuencias (que pueden ir desde varios MHz hasta los GHz); en general, superiores a las soportadas por transistores BJT.

Sin embargo, los amplificadores basados en FET, tambin presentan una desventaja en relacin a los BJT; ya que ofrecen menor ganancia.

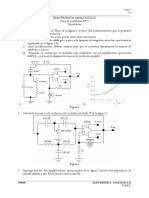

Definicin de conceptos bsicos Antes de determinar los niveles de corriente y voltaje en CD del amplificador diferencial, es bien importante recordar algunos conceptos bsicos acerca del transistor JFET. Al igual que el BJT, el JFET es un dispositivo de tres terminales, en la figura 1 se muestra un JFET de canal n. En esta figura, se indica el nombre de cada terminal (izquierda), las polaridades y las direcciones en las que fluyen las corrientes (derecha).

Figura 1. Transistor JFET canal n A diferencia del transistor BJT, el JFET es un dispositivo controlado por voltaje. Esto implica que la corriente de salida (ID), es controlada por el voltaje de entrada (VGS); en otras palabras, la corriente de drenaje vara dependiendo de la diferencia de potencial que exista entre compuerta y fuente.

Elabor: Fernando Vera Zarza

Febrero de 2010

Pgina 1 de 12

La corriente de salida y el voltaje de entrada, son parmetros que se relacionan a travs de la famosa Ecuacin de Shockley; la cual establece que: En donde: IDSS (Drain Source Saturation), es la corriente de drenaje a fuente en saturacin. IDSS, representa el nivel mximo que puede alcanzar la corriente de salida (ID). Se llega a este mximo nivel, cuando el voltaje de entrada (VGS) es igual a cero; es decir: 0 .

, lo cual se comprueba al revisar la expresin (2.1). IDSS, es un valor proporcionado por el fabricante del transistor, por lo que viene especificado en la hoja de datos (datasheet) correspondiente. Vp (Pinch off voltage), es el voltaje de estrechamiento. Este parmetro, representa el voltaje de entrada (VGS); para el cual la corriente de salida (ID) se vuelve cero, es decir: 0 .

, lo cual tambin se comprueba al revisar la expresin (2.1). Es importante aclarar, que para VALORES DE VGS MENORES A Vp, LA CORRIENTE ID TRATAR DE MANTENERSE EN CERO. Aunque, PARA ESTOS VALORES, LA RELACIN ENTRE VGS e ID, YA NO ESTA DETERMINADA POR (2.1). Vp, tambin es un valor proporcionado por el fabricante del transistor, por lo que viene especificado en la hoja de datos correspondiente.

Entonces, si de las hojas de especificaciones se conoce IDSS y Vp, mediante (2.1) se puede encontrar el valor de ID para un determinado valor de VGS. La figura 2, muestra una grfica conocida como caracterstica de transferencia del JFET (esta grfica corresponde al transistor 2N3819). Los valores aproximados de esta grfica, se obtienen al proponer valores para VGS y calculando ID, mediante (2.1). Por ejemplo, el punto (VGS, ID) mostrado en la grfica es (-1.2V, 4.3mA). Asumiendo que, segn la hoja de especificaciones del 2N3819, IDSS = 10mA y Vp = -3V. Entonces, para VGS = -1.2V, se obtiene que ID = 3.6mA. Finalmente, los valores (-1.2V, 3.6mA), son un resultado bastante aproximado a los que se muestran en la curva de la figura 2.

Elabor: Fernando Vera Zarza

Febrero de 2010

Pgina 2 de 12

Figura 2. La caracterstica de transferencia, es una representacin grfica de la relacin que existe entre el voltaje de entrada (VGS) y la corriente de salida (ID) en un JFET, en este caso el 2N3819. Para que un JFET amplifique adecuadamente, sin distorsin de la seal de salida, es necesario que el dispositivo opere en la regin de saturacin (no confundir con las regiones del transistor BJT; la regin til para amplificar seales con un JFET, es llamada regin de saturacin, ver figura 3). La regin en la que opera un determinado transistor se puede conocer ubicando el punto de operacin (Q) en las curvas caractersticas (tambin llamada caracterstica de salida) del transistor. Para ubicar correctamente el punto de operacin, basta con conocer los tres parmetros que lo definen: , , .

Por el momento se asume que VDS es mayor a cero y que adems es lo suficientemente grande, ms adelante se determinar su valor exacto. Como se ha mencionado, el valor de VGS se puede proponer y el valor de ID se calcula a partir de (2.1). Ahora bien, Cuales son valores que pueden ser propuestos para VGS? Considerando que VDS mantiene un valor constante (para la grafica mostrada en la figura 3, supngase que de 5V). Si VGS se vuelve mayor a cero (VGS > 0), el JFET canal n operar en la regin hmica. Por otra parte, manteniendo VDS constante, si VGS se vuelve menor (o bien, ms negativo) que Vp (VGS < Vp), el JFET canal n operar en la regin de corte. Por lo tanto, manteniendo VDS constante, para que el JFET canal n opere en la regin de saturacin, es necesario que VGS sea mayor o igual a Vp y menor o igual a cero (Vp VGS 0).

Febrero de 2010 Pgina 3 de 12

Elabor: Fernando Vera Zarza

Figura 3. Caracterstica de salida del JFET canal n (2N3819) Anteriormente se asumi que VDS > 0; el valor exacto de este voltaje, depende de los elementos (componentes elctricos) conectados a las terminales del transistor; los cuales deben ser elegidos para satisfacer la siguiente condicin: .

Yendo de izquierda a derecha en la figura 3, cuando VDS < (VGS Vp), el JFET canal n opera en la regin hmica (regin en marrn, a la izquierda de la lnea en rojo, figura 3). De igual manera, cuando VDS = (VGS Vp), el JFET canal n opera justo en el lmite entre la regin hmica y la regin de saturacin (lnea en rojo, figura 3). Por lo tanto, para que el JFET canal n opere en la regin de saturacin (regin en azul, a la derecha de la lnea en rojo, figura 3), se tiene que lograr que VDS > (VGS Vp).

Hasta el momento se ha dicho que la ecuacin (2.1), es la que determina el comportamiento del JFET, ya que establece la relacin entre el voltaje de entrada y la corriente de salida del transistor. Sin embargo, an falta revisar como se utiliza esta ecuacin al momento de que el transistor forma parte de un circuito elctrico; en este caso, del amplificador diferencial (ver figura 4). Al tomar en cuenta que el transistor forma parte de un circuito; es necesario determinar cmo los elementos conectados a sus terminales, interactan con este dispositivo. En otras palabras, es necesario encontrar la relacin entre la ecuacin (2.1) y las ecuaciones derivadas de los elementos conectados al transistor, sin pasar por alto la condicin (2.5). As pues, se da paso al anlisis en CD del amplificador diferencial basado en transistores JFET.

Elabor: Fernando Vera Zarza Febrero de 2010 Pgina 4 de 12

Figura 4. Amplificador diferencial basado en transistores JFET

Anlisis en CD del amplificador diferencial Para simplificar el anlisis inicial, se asumir que: .

Tambin se asumir que los voltajes de entrada vi1 y vi2 son iguales, por lo que el voltaje diferencial de entrada, es cero: 0 .

Debido a (2.6), (2.7) y asumiendo que tanto Q1, como Q2 tienen caractersticas internas muy similares, se puede considerar que al amplificador diferencial se encuentra en equilibrio; es decir, las corrientes y las diferencias de potencial en la rama 1, son iguales a las de la rama 2.

Elabor: Fernando Vera Zarza

Febrero de 2010

Pgina 5 de 12

Entonces, la condicin de equilibrio implica que: .

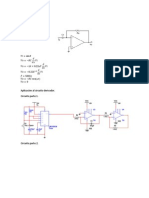

Inicialmente, se asumir que VGS1, y por lo tanto VGS2, son valores conocidos. Partiendo de esto y de la condicin de equilibrio, se determinar el resto de los parmetros. Considerando la rama 1, empleando el 2N3819 y suponiendo que VGS1 ya es un valor conocido, entonces es posible determinar ID1 mediante (2.1). Ahora bien, aplicando ley de Kirchhoff de voltaje en la malla I (ver figura 5), se obtiene que: 0 .

Figura 5. Ley de Kirchhoff de Voltaje (Malla I) y Ley de Kirchhoff de Corriente (Nodo I) Derivado de conceptos elementales acerca del transistor JFET (y en general para cualquier FET), se puede considerar que:

Elabor: Fernando Vera Zarza

.

Febrero de 2010 Pgina 6 de 12

Por lo tanto, al conocer ID1 tambin se conoce IS1; ya que: Sustituyendo (2.11) en (2.9), se obtiene: 0 0 . . .

Al aplicar ley de Kirchhoff de corriente en el nodo I (ver figura 5), se obtiene que:

Las igualdades (2.8), resultado de la condicin de equilibrio, indican que IS1 = IS2 sustituyendo esta igualdad en (2.13) y simplificando, se obtiene: O lo que es lo mismo, de acuerdo con (2.11): . .

Mediante (2.15) se puede conocer el valor de ISS. Adems, sustituyendo (2.15) en (2.12), se obtiene que: 0 .

VGS1 ya es un valor conocido, al igual que ID1. A VSS se le asigna el valor de la fuente de alimentacin disponible, si se propone un valor para RS1, entonces se podra calcular el valor de RSS. RS1 debe ser propuesto de un valor muy pequeo en relacin al valor de RSS, de lo contrario la ganancia disminuira respecto a la calculada. En un principio se puede considerar que RSS = 100RS1, sustituyendo esta igualdad en (2.19): 0 Reordenando y despejando: . .

Determinando as, el valor de RS1, y en consecuencia el valor de RSS. Para determinar el valor de RD1, se reordena el circuito como se muestra en la figura 6, y se aplica ley de Kirchhoff de voltaje en la malla II, obteniendo: 0 .

El valor de vo1 (o lo que es lo mismo, de VD1), tambin puede ser propuesto en base al nivel mximo que se desea obtener a la salida.

Elabor: Fernando Vera Zarza

Febrero de 2010

Pgina 7 de 12

Figura 6. Al re ordenar el circuito el anlisis se simplifica. En este caso la fuente VDD, sigue conectada al mismo punto, solamente se gira hacia adentro de la pgina para que se aprecie mejor como forma parte de la malla II. Al utilizar (2.1) para encontrar el valor de ID1 y despus utilizar este resultado para calcular IS1 e ISS, es claro que se ha logrado que (2.1) se relacione con las expresiones (derivadas de las leyes de Kirchhoff) obtenidas de las redes formadas por los componentes conectados a las terminales del JFET. Por lo tanto, faltara involucrar en el anlisis, la condicin establecida en (2.5); lo cual se consigue al proponer el valor de VD1. Para esto, se toma la igualdad que indica el lmite entre la regin hmica y de saturacin; es decir: .

La expresin anterior, representa el valor mnimo que VDS1 puede tener antes de que el JFET pase a la regin hmica. Adems, se sabe que: Igualando (2.22) y (2.23) se obtiene: Por lo tanto, tambin es cierto que: 0 . . . .

El valor de VS1 se calcula aplicando ley de Kirchhoff de voltaje en la malla III (ver figura 7), obteniendo:

Elabor: Fernando Vera Zarza

Febrero de 2010

Pgina 8 de 12

Figura 7. Ley de Kirchhoff de Voltaje (Malla III) para determinar VS1. Sustituyendo (2.26) en (2.25): .

Este es el valor mnimo que puede ser propuesto para VD1, de lo contrario VDS1 no cumplira con (2.5) y por lo tanto, el JFET estara operando en la regin hmica, lo cual no es deseable para tareas de amplificacin. Por otra parte, es evidente que al conocer VD1, se sustituye este valor en (2.21) y se calcula RD1. Adems, conociendo VD1 y VS1 tambin se puede calcular el voltaje diferencial VDS1. Ahora bien, si (2.27) representa el nivel mnimo que puede ser propuesto para VD1, Por qu entonces no se propone un valor mayor y en base a este se calcula RD1? Para analizar esta situacin, se supondr que la condicin de equilibrio es alterada; es decir: 0

.

/

Considerando lo anterior, el voltaje diferencial de salida vod, se determina por la siguiente expresin: 2 .

Todos los parmetros del lado derecho de la expresin (2.29), se asumen constantes, excepto RD1 (se sabe que RD = RD1 = RD2). Si RD1 se incrementa, tambin se incrementa vod. Por lo tanto, si RD1 se reduce, tambin se reduce vod. Esto significa que para un valor constante vid, se obtiene un mayor vod,

Elabor: Fernando Vera Zarza Febrero de 2010 Pgina 9 de 12

si RD1 se incrementa. En otras palabras, dado que la ganancia (en este caso la ganancia diferencial Ad) est definida como: .

Si RD1 se incrementa, tambin se incrementa la ganancia diferencial del amplificador Ad. Por otra parte, despejando (2.21): .

Segn esta expresin, si se incrementa el valor de RD1 automticamente VD1 disminuira su valor, provocando que (2.5) no se cumpla. Y como consecuencia, provocando que el JFET salga de la regin de saturacin. Se desea entonces, que RD1 sea de un valor muy grande para proporcionar alta ganancia. Sin embargo, si RD1 es demasiado grande, VD1 sera demasiado pequeo, lo que provocara que el JFET pasar a la regin hmica. Como conclusin, se demuestra entonces que (2.27) es un valor ptimo de VD1 porque permite que los transistores operen en la regin de saturacin y adems, permite alcanzar la mayor ganancia posible, sin distorsin de la seal de salida, en el amplificador diferencial. Pasando a otras cosas, una vez que la condicin de equilibrio es alterada (2.28), ocurre algo similar a lo que pasa en el amplificador basado en BJT. Si vi1 cambia, automticamente cambia VGS1, modificando as el resto de las corrientes y diferencias de potencial en la rama 1 y en su contraparte del lado derecho. Sin embargo, al igual que para el amplificador BJT, el nico parmetro que siempre permanece constante, es la corriente de fuente comn ISS. Sin importar la forma en que varen los voltajes de entrada y en consecuencia el resto de los parmetros, ISS nunca se modificar. Debido a este comportamiento y tambin debido a (2.13), si ocurre un incremento de corriente en una de las ramas, su contraparte lo compensa disminuyendo en forma proporcional. Entonces, es evidente que las variaciones de las corrientes que fluyen por cada rama, son consecuencia de las variaciones de los voltajes vi1 y vi2 o bien, del vid. Por lo tanto, una vez que el voltaje de entrada diferencial se vuelve distinto de cero, las corrientes en cada rama se pueden calcular a partir de las siguientes expresiones: 2 2 2

2 2 2

Al calcular las corrientes de drenaje, se pueden calcular el resto de las corrientes y diferencias de potencial correspondientes a cada rama.

Elabor: Fernando Vera Zarza

Febrero de 2010

Pgina 10 de 12

Hasta el momento, solo se han considerado niveles de CD aplicados en la entrada (vi1 y vi2) del amplificador. Es importante resaltar que las corrientes de CD de cada rama, no se modifican por seales de CA aplicadas a la entrada (ver figura 8).

Figura 8. El circuito de la izquierda muestra los niveles de corriente en CD, cuando se aplican 0V a la entrada de amplificador diferencial, el amplificador esta en equilibrio. En el circuito de la derecha, se muestra claramente como estos niveles de corriente se mantienen sin cambio, an cuando se aplica una seal de CA de 200mV de amplitud y un offset de 0V. Los nicos voltajes de entrada que modifican los niveles de CD en el amplificador, tambin son voltajes de CD; tales como, una fuente de voltaje de corriente directa o incluso los niveles de offset en seales de CA, como se muestra en la figura 9. Al realizar un anlisis en CD del amplificador, el voltaje de las seales de CA aplicadas en vi1 y vi2 se consideran 0V, a menos que dichas seales, contengan componentes de CD o bien, niveles de offset diferentes de cero. En cuyo caso, una manera sencilla de realizar este anlisis, es sustituyendo la posible fuente de CA, por una fuente de CD con valor igual al offset de la seal original. Por ejemplo, suponiendo que se desea realizar el anlisis en CD del circuito de la izquierda mostrado en la figura 9. Lo que se podra hacer para simplificar el anlisis, es sustituir la fuente de CA (V25) por una fuente de CD, cuyo valor es igual al offset de la seal de CA. Tal como se muestra en el circuito de la derecha en la figura 9. Para conocer con precisin las corrientes de CA, generadas en cada rama al aplicar seales de CA en vi1 y/o vi2, se requiere conocer muy bien algn modelo del transistor, tal como el modelo , el modelo hbrido o el modelo de transconductancia. Debido a esto, el anlisis en CA se cubrir en apuntes complementarios, prximamente elaborados. De momento, bastar con entender que al aplicar seales de CA en vi1 y/o vi2 las seales obtenidas en vo1 y/o vo2, tambin sern seales de CA pero

Elabor: Fernando Vera Zarza Febrero de 2010 Pgina 11 de 12

amplificadas. La ganancia en voltaje de las seales de CA y/o CD obtenidas a la salida de este amplificador diferencial, ES LA MISMA, y est DETERMINADA por (2.29) y (2.30).

Figura 9. En estos dos circuitos, se comprueba que el efecto de una fuente de CD conectada a la entrada del amplificador diferencial, tiene el mismo efecto que el componente en CD o el offset de una seal de CA.

Elabor: Fernando Vera Zarza

Febrero de 2010

Pgina 12 de 12

Anda mungkin juga menyukai

- Armónicas en Sistemas Eléctricos IndustrialesDari EverandArmónicas en Sistemas Eléctricos IndustrialesPenilaian: 4.5 dari 5 bintang4.5/5 (12)

- Probabilidad y EstadisticaDokumen18 halamanProbabilidad y EstadisticaEdison Ortega50% (4)

- Trabajo de Investigación 3 ELA2Dokumen7 halamanTrabajo de Investigación 3 ELA2Juan David Rodriguez BeltranBelum ada peringkat

- Uni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Quinto LaboratorioDokumen3 halamanUni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Quinto LaboratorioAlfred PILLACA GOMEZBelum ada peringkat

- Campanas de FranklinDokumen7 halamanCampanas de FranklinEdison Ortega100% (1)

- Probabilidad de Error y Tasa de Errores de BitsDokumen4 halamanProbabilidad de Error y Tasa de Errores de BitsRoger Gómez GómezBelum ada peringkat

- Polarizacion de Los MosfetDokumen12 halamanPolarizacion de Los MosfetVictor Manuel CanahuiriBelum ada peringkat

- Informe UJTDokumen2 halamanInforme UJTIan AsBelum ada peringkat

- L-005-Realimentacion-Burga RiosDokumen10 halamanL-005-Realimentacion-Burga RiosFlavio AndreéBelum ada peringkat

- Practica 4. Circuitos Msi Parte 2 Informe Laboratorio Circuitos DigitalesDokumen26 halamanPractica 4. Circuitos Msi Parte 2 Informe Laboratorio Circuitos DigitalesDanielaBelum ada peringkat

- CL Diodos SemiconductoresDokumen9 halamanCL Diodos SemiconductoresAlma PartidaBelum ada peringkat

- Mediciones Practica 1Dokumen6 halamanMediciones Practica 1Tavo NajeraBelum ada peringkat

- Deber #2 Amplificadores DiferencialesDokumen30 halamanDeber #2 Amplificadores DiferencialesluisciferelectronicaBelum ada peringkat

- Preinforme UJTDokumen4 halamanPreinforme UJTGabriel CanoBelum ada peringkat

- Laboratorio 6 Transitores Efecto de CampoDokumen5 halamanLaboratorio 6 Transitores Efecto de CampoDiego VargasBelum ada peringkat

- Problemas Propuestos 2018-2Dokumen4 halamanProblemas Propuestos 2018-2Jhoelito KennedyBelum ada peringkat

- Clase de Transistores (Amplificadores BJT)Dokumen38 halamanClase de Transistores (Amplificadores BJT)Anonymous dbT2wROrxrBelum ada peringkat

- Ujt SCRDokumen26 halamanUjt SCRLuis Antonio Mairena AcostaBelum ada peringkat

- CMOSDokumen21 halamanCMOSJonathanDavidBelum ada peringkat

- ElectroDokumen11 halamanElectroGinoEnzoRiosBelum ada peringkat

- Informe Montaje de Fuente de Poder Dual VariableDokumen15 halamanInforme Montaje de Fuente de Poder Dual VariableJorge Rivera100% (1)

- Caracteristica Exponencial BJTDokumen3 halamanCaracteristica Exponencial BJTJhazzel Cruz MendozaBelum ada peringkat

- Tutorial de LTSpice 2Dokumen8 halamanTutorial de LTSpice 2Mario Sanchez DuarteBelum ada peringkat

- P1 DispositivosDokumen15 halamanP1 DispositivosSagrario Rojas TorresBelum ada peringkat

- MosfetDokumen12 halamanMosfetLuis Allauca100% (1)

- Parametros de Rendimiento de Los Rectificadores - ModificadaDokumen11 halamanParametros de Rendimiento de Los Rectificadores - ModificadaferminBelum ada peringkat

- Práctica 2 Amplificador Clase BDokumen8 halamanPráctica 2 Amplificador Clase BEmmanuel HerreraBelum ada peringkat

- Oscilador Puente de WienDokumen3 halamanOscilador Puente de WienAlex MartinezBelum ada peringkat

- Amplificador InversorDokumen2 halamanAmplificador Inversorjose100% (2)

- Informe Final N°5 Sistemas DigitalesDokumen11 halamanInforme Final N°5 Sistemas DigitalesHans PuenteBelum ada peringkat

- Balun PDFDokumen2 halamanBalun PDFauthorBelum ada peringkat

- Tarea Digitales 1Dokumen8 halamanTarea Digitales 1Jorge Gustavo Santiago SotoBelum ada peringkat

- 1 El Osciloscopio y Generador de FuncionesDokumen6 halaman1 El Osciloscopio y Generador de FuncionesRonaldo LCBelum ada peringkat

- Procedimiento y Cuestionario 1,2,3 y 4Dokumen12 halamanProcedimiento y Cuestionario 1,2,3 y 4Sandra Mirella Toribio RodriguezBelum ada peringkat

- Lab MultietapaDokumen15 halamanLab MultietapaalbertwillyBelum ada peringkat

- Informe Previo 1 Circuitos Digitales 1 (Compuertas Lógicas BaskcasDokumen9 halamanInforme Previo 1 Circuitos Digitales 1 (Compuertas Lógicas BaskcasJorge Gustavo Santiago SotoBelum ada peringkat

- Laboratorio PCM 2Dokumen4 halamanLaboratorio PCM 2Checho LopezBelum ada peringkat

- Informe TermistorDokumen14 halamanInforme TermistorErick CordovaBelum ada peringkat

- Práctica 7 PLL Como Sintetizador de FrecuenciasDokumen7 halamanPráctica 7 PLL Como Sintetizador de FrecuenciasDavid GomezBelum ada peringkat

- Informe Final Laboratorio 1 Sistemas DigitalesDokumen15 halamanInforme Final Laboratorio 1 Sistemas DigitalesO'BESSO DE LA SOTA GLEN RENATO100% (1)

- BalunDokumen2 halamanBalunLuz Maria PenagosBelum ada peringkat

- Experiencias LaboratorioDokumen41 halamanExperiencias LaboratorioIsrael ArenasBelum ada peringkat

- LAB2 Amp Simetria ComplementariaDokumen4 halamanLAB2 Amp Simetria ComplementariaJEAN LEONARDO ESTRADA ROQUEBelum ada peringkat

- Sistemas Digitales I 2 LaboratorioDokumen15 halamanSistemas Digitales I 2 LaboratorioMiguel Obispo ChaguaBelum ada peringkat

- Respuesta en FrecuenciaDokumen5 halamanRespuesta en FrecuenciaŠtiveņ Ōrjûëla100% (1)

- Ejercicios Resueltos Amplificadores MultietapaDokumen14 halamanEjercicios Resueltos Amplificadores MultietapaPaDRBelum ada peringkat

- 2021-3 MOSFET PolarizaciónDokumen19 halaman2021-3 MOSFET PolarizaciónNicolas CarvajalBelum ada peringkat

- Informe - Par DarlingtonDokumen5 halamanInforme - Par DarlingtonEliasib BernalBelum ada peringkat

- Informe Del Filtro Paso BandaDokumen6 halamanInforme Del Filtro Paso BandaHopper JavierBelum ada peringkat

- Amplificador Realimentado en CascadaDokumen5 halamanAmplificador Realimentado en CascadaGin DlcBelum ada peringkat

- Trabajo Preparatorio 4 Laboratorio de Circuitos Electrónicos EPNDokumen4 halamanTrabajo Preparatorio 4 Laboratorio de Circuitos Electrónicos EPNxavier2ramos-1Belum ada peringkat

- Configuracion CascadaDokumen7 halamanConfiguracion CascadaKely Estefani Alcántara PinedoBelum ada peringkat

- Configuracion en CascadaDokumen7 halamanConfiguracion en CascadaGersonPaulinhoSulcaBelum ada peringkat

- Amplificador Diferencial Informe 3 UNMSMDokumen4 halamanAmplificador Diferencial Informe 3 UNMSMJhilmar Arroyo UribeBelum ada peringkat

- Clase2 IDokumen14 halamanClase2 Irvh164Belum ada peringkat

- CIRCUITOS OSCILADORES (Editado)Dokumen11 halamanCIRCUITOS OSCILADORES (Editado)Henry RamirezBelum ada peringkat

- Guia 9Dokumen6 halamanGuia 9Hugo CarhuallanquiBelum ada peringkat

- INFORME FINAL Nº4 - Sistemas DigitalesDokumen21 halamanINFORME FINAL Nº4 - Sistemas DigitalesMARIO ALBERTO CCOYORI MENDOZABelum ada peringkat

- Transistores JfetDokumen14 halamanTransistores JfetNeiraCariasDanielBelum ada peringkat

- Trabajo JFETDokumen12 halamanTrabajo JFETAlfonso Villahermosa SanchezBelum ada peringkat

- Mosfet D Amplificador 2N7000Dokumen8 halamanMosfet D Amplificador 2N7000Julian Andres VictoriaBelum ada peringkat

- Transistor JfetDokumen9 halamanTransistor JfetwolfstarprojectsBelum ada peringkat

- Módulo 3 Estrategias y Herramientas de Eduaccion AmbientalDokumen122 halamanMódulo 3 Estrategias y Herramientas de Eduaccion AmbientalEdison OrtegaBelum ada peringkat

- DifusividadDokumen1 halamanDifusividadEdison OrtegaBelum ada peringkat

- Circuito de Una Fuente EstabilizadaDokumen7 halamanCircuito de Una Fuente EstabilizadaEdison OrtegaBelum ada peringkat

- DifusividadDokumen1 halamanDifusividadEdison OrtegaBelum ada peringkat

- Universidad Politecnica SalesianaDokumen5 halamanUniversidad Politecnica SalesianaEdison OrtegaBelum ada peringkat

- Explique El Concepto de Microclima Través de La FiguraDokumen1 halamanExplique El Concepto de Microclima Través de La FiguraEdison OrtegaBelum ada peringkat

- Proyecto Tilapias (Recuperado Automáticamente)Dokumen7 halamanProyecto Tilapias (Recuperado Automáticamente)Edison OrtegaBelum ada peringkat

- Taller Aquenos y AlquinosDokumen4 halamanTaller Aquenos y AlquinosEdison Ortega100% (1)

- Final PRGDokumen4 halamanFinal PRGEdison OrtegaBelum ada peringkat

- Manual ArcGis P1 2 3Dokumen60 halamanManual ArcGis P1 2 3Edison OrtegaBelum ada peringkat

- Ciclo Del AzufreDokumen7 halamanCiclo Del AzufreEdison OrtegaBelum ada peringkat

- Juan Segarra Mapas ArgDokumen2 halamanJuan Segarra Mapas ArgEdison OrtegaBelum ada peringkat

- Ac VS DCDokumen3 halamanAc VS DCEdison OrtegaBelum ada peringkat

- Modularización, Funciones y Parámetros JavaDokumen27 halamanModularización, Funciones y Parámetros JavaJhonny PalaguachiBelum ada peringkat

- Ac VS DCDokumen2 halamanAc VS DCEdison OrtegaBelum ada peringkat

- Practi 07Dokumen14 halamanPracti 07Isela Zecua AlejoBelum ada peringkat

- CÓDIGOMATLABINTERPOLACIÓNDELAGRANGEDokumen1 halamanCÓDIGOMATLABINTERPOLACIÓNDELAGRANGEGeorge BlankassBelum ada peringkat

- Leccion14 GrafosDokumen71 halamanLeccion14 GrafosRicardo VázquezBelum ada peringkat

- Matlab GraficosDokumen111 halamanMatlab GraficosCristhian CarrascoBelum ada peringkat

- GasesDokumen5 halamanGasesEdison OrtegaBelum ada peringkat

- Modularización, Funciones y Parámetros JavaDokumen27 halamanModularización, Funciones y Parámetros JavaJhonny PalaguachiBelum ada peringkat

- Capitulo1 ProgramacionDokumen26 halamanCapitulo1 ProgramacionAndrés Sebastián VallejoBelum ada peringkat

- Digital 5Dokumen7 halamanDigital 5Edison OrtegaBelum ada peringkat

- LOGICADokumen88 halamanLOGICAJuan Carlos Neyra GutierrezBelum ada peringkat

- Microcontroladores PIC 3rd Edition (Carlos A. Reyes)Dokumen221 halamanMicrocontroladores PIC 3rd Edition (Carlos A. Reyes)Andres CahvezBelum ada peringkat

- Informe 2Dokumen8 halamanInforme 2Edison OrtegaBelum ada peringkat

- Solucionpro1 Logica PDFDokumen7 halamanSolucionpro1 Logica PDFMiguel Angel Gomez AguadoBelum ada peringkat

- Circuito DerivadorDokumen2 halamanCircuito DerivadorEdison OrtegaBelum ada peringkat

- Distancias DielectricasDokumen5 halamanDistancias Dielectricasangel jimenez100% (1)

- Top PWMDokumen12 halamanTop PWMcarlos noelBelum ada peringkat

- Tipos de Memoria SemiconductorasDokumen3 halamanTipos de Memoria SemiconductorasAntonio ChavezBelum ada peringkat

- Cuestionarios y Problemarios Etapa IiDokumen51 halamanCuestionarios y Problemarios Etapa Iicasandra contrerasBelum ada peringkat

- TAREA Nº3 ElectronicaDokumen2 halamanTAREA Nº3 ElectronicaDilan CordovaBelum ada peringkat

- 9871104251Dokumen10 halaman9871104251Leando MaureiraBelum ada peringkat

- Calculo de PanelesDokumen16 halamanCalculo de PanelesJose Samuel Melgares ValdiviaBelum ada peringkat

- Practica Variador de FrecuenciaDokumen4 halamanPractica Variador de FrecuenciaCristian RamirezBelum ada peringkat

- World Line S.A.C.: Importe 2 Últimos Meses Facturados Mar-23 S/ 671.69 Abr-23 S/ 808.82Dokumen1 halamanWorld Line S.A.C.: Importe 2 Últimos Meses Facturados Mar-23 S/ 671.69 Abr-23 S/ 808.82QuilmesBelum ada peringkat

- Energia Renovable HidraulicaDokumen22 halamanEnergia Renovable HidraulicaNax BerrumBelum ada peringkat

- Pse1 EjercicioDokumen9 halamanPse1 EjercicioADRIANA CASTAÑEDA ALVAREZBelum ada peringkat

- Tarea 1 (Unidad 1)Dokumen18 halamanTarea 1 (Unidad 1)Abraham MirandaBelum ada peringkat

- NPA-409376-EL-ET-018 - R0 Especificación Técnica Construcción y Montaje EléctricoDokumen76 halamanNPA-409376-EL-ET-018 - R0 Especificación Técnica Construcción y Montaje EléctricoCAMILABelum ada peringkat

- Pa2.hazop en Binax.u2.8-CDokumen5 halamanPa2.hazop en Binax.u2.8-CJesus Alejandro Santiago GuillenBelum ada peringkat

- Guiade Ejercicios VIIDokumen4 halamanGuiade Ejercicios VIIFranco Olguin RolonBelum ada peringkat

- Articulo Conductividad EléctricaDokumen19 halamanArticulo Conductividad EléctricaANDREA YELITZA LOPEZ PAEZBelum ada peringkat

- Fórmulas Del Amperímetro y VoltímetroDokumen17 halamanFórmulas Del Amperímetro y VoltímetroJenifer RamosBelum ada peringkat

- El Análisis de Un Circuito Trifásico de Tensiones y Corrientes Perfectas o SimétricasDokumen5 halamanEl Análisis de Un Circuito Trifásico de Tensiones y Corrientes Perfectas o Simétricascristian garcesBelum ada peringkat

- Instalaciones2 TSUDokumen17 halamanInstalaciones2 TSULuis Ernesto LealBelum ada peringkat

- Actividad Fase 2Dokumen8 halamanActividad Fase 2kevin narvaez henriquezBelum ada peringkat

- I-Lp2602 InterruptoresDokumen16 halamanI-Lp2602 InterruptoresCHAHRHLHOHSBelum ada peringkat

- Laboratorio Nro. 4-Polarizcion de Un TransistorDokumen5 halamanLaboratorio Nro. 4-Polarizcion de Un TransistorjefersonBelum ada peringkat

- Manual de Operacion Csh5lmark2Dokumen91 halamanManual de Operacion Csh5lmark2PEDRO PABLO PRIETO MONZONBelum ada peringkat

- Antecedentes 2020Dokumen16 halamanAntecedentes 2020DxrWin XndrxngoBelum ada peringkat

- Electronica de Comunicaciones Osciladores: Msc. Ing. Max Fredi Quispe AguilarDokumen19 halamanElectronica de Comunicaciones Osciladores: Msc. Ing. Max Fredi Quispe AguilarCésar GuerreroBelum ada peringkat

- El Transistor Es Un Componente Electrónico Capaz de Actuar Como Un Interruptor y Además Como Un Amplificador Todo Mediante Una Pequeña Señal Eléctrica y Sin Partes MóvilesDokumen4 halamanEl Transistor Es Un Componente Electrónico Capaz de Actuar Como Un Interruptor y Además Como Un Amplificador Todo Mediante Una Pequeña Señal Eléctrica y Sin Partes Móvilesjose0% (1)

- Interpretacion Esquemas Electricos PDFDokumen117 halamanInterpretacion Esquemas Electricos PDFherminiodBelum ada peringkat

- Cad y CdaDokumen9 halamanCad y CdaFernanda Zepeda AlcarazBelum ada peringkat

- ConductimetríaDokumen14 halamanConductimetríaRaul Chuquirimay RojasBelum ada peringkat

- Control Logico ProgramableDokumen124 halamanControl Logico ProgramableAngel Xavier GarciaBelum ada peringkat