Dynamic Ram Interfacing Notes

Diunggah oleh

rneevanDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Dynamic Ram Interfacing Notes

Diunggah oleh

rneevanHak Cipta:

Format Tersedia

Dynamic RAM interfacing Whenever a large capacity memory is required in a microcomputer system, the memory subsystem is generally designed

using dynamic RAM because there are various advantages of dynamic RAM. E.g. higher packing density, lower cost and less power consumption. A typical static RAM cell may require 6 transistors while the dynamic RAM cell requires only a transistors along with a capacitor. Hence it is possible to obtain higher packaging density and hence low cost units are available. The basic dynamic RAM cell uses a capacitor to store the charge as a representation of data. This capacitor is manufactured as a diode that is reverse-biased so that the storage capacitance comes into the picture. This storage capacitance is utilized for storing the charge representation of data but the reverse-biased diode has leakage current that tends to discharge the capacitor giving rise to the possibility of data loss. To avoid this possible data loss, the data stored in a dynamic RAM cell must be refreshed after a fixed time interval regularly. The process of refreshing the data in RAM is called as Refresh cycle. The refresh activity is similar to reading the data from each and every cell of memory, independent of the requirement of microprocessor. During this refresh period all other operations related to the memory subsystem are suspended. Hence the refresh activity causes loss of time, resulting in reduce system performance. However keeping in view the advantages of dynamic RAM, like low power consumption, high packaging density and low cost, most of the advanced computing system are designed using dynamic RAM, at the cost of operating speed. The Refresh cycle is different from the memory read cycle in the following aspects. 1. The memory address is not provided by the CPU address bus, rather it is generated by a refresh mechanism counter called as refresh counter. 2. Unlike memory read cycle, more than one memory chip may be enabled at a time so as to reduce the number of total memory refresh cycles. 3. The data enable control of the selected memory chip is deactivated, and data is not allowed to appear on the system data bus during refresh, as more than one memory units are refreshed simultaneously. This is to avoid the data from the different chips to appear on the bus simultaneously. 4. Memory read is either a processor initiated or an external bus master initiated and carried out by the refresh mechanism. Dynamic RAM is available in units of several kilobits to megabits of memory. This memory is arranged internally in a two dimensional matrix array so that it will have n rows and m columns. The row address n and column address m are important for the refreshing operation. For example, a typical 4K bit dynamic RAM chip has an internally arranged bit array of dimension 64 * 64 , i.e. 64 rows and 64 columns. The row address and column address will require 6 bits each. These 6 bits for each row address and column address will be generated by the refresh counter, during the refresh cycles. A complete row of 64 cells is refreshed at a time to minimizes the refreshing time. Thus the refresh counter needs to generate only row addresses. The row address are multiplexed, over lower order address lines. The refresh signals act to control the multiplexer, i.e. when refresh cycle is in process the refresh counter puts the row address over the address bus for refreshing.

Otherwise, the address bus of the processor is connected to the address bus of DRAM, during normal processor initiated activities. A timer, called refresh timer, derives a pulse for refreshing action after each refresh interval. Refresh interval can be qualitatively defined as the time for which a dynamic RAM cell can hold data charge level practically constant, i.e. no data loss takes place. Suppose the typical dynamic RAM chip has 64 rows, then each row should be refreshed after each refresh interval or in other words, all the 64 rows are to refreshed in a single refresh interval. This refresh interval depends upon the manufacturing technology of the dynamic RAM cell. It may range anywhere from 1ms to 3ms. Let us consider 2ms as a typical refresh time interval. Hence, the frequency of the refresh pulses will be calculated as follows: Refresh Time ( per row ) tr= (2 * 10 -3) / 64. Refresh Frequency fr= 64 / ( 2 * 10 -3) = 32 * 103 Hz.

Each chip is of 16K * 1-bit dynamic RAM cell array. The system contains two 16K byte dynamic RAM units. All the address and data lines are assumed to be available from an 8086 microprocessor system. The OE pin controls output data buffer of the memory chips. The CE pins are active high chip selects of memory chips. The refresh cycle starts, if the refresh output of the refresh timer goes high, OE and CE also tend to go high. The high CE enables the memory chip for refreshing, while high OE prevents the data from appearing on the data bus, as discussed in memory refresh cycle. The 16K * 1-bit dynamic RAM has an internal array of 128*128 cells, requiring 7 bits for row address. The lower order 7 lines A0-A6 are multiplexed with the refresh counter output A10-A16.

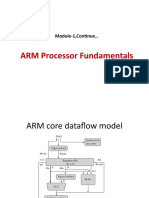

Dual Core Processor Architecture

Dual-core CPU refers to has two complete execution cores in a single integrated circuit. It includes 2 processors and their caches and cache controllers onto a single integrated circuit. Both core work side by side to help each other in processing and executing. Each "core" independently implements optimizations such as superscalar execution, pipelining, and multithreading. A system with n cores is effective when it is presented with n or more threads.

Anda mungkin juga menyukai

- Chapter 7 Interrupts of 8085Dokumen20 halamanChapter 7 Interrupts of 8085shubhankar pal100% (1)

- Memory Segmentation of Intel 8086.ppsDokumen17 halamanMemory Segmentation of Intel 8086.ppsmnshrao0% (1)

- 18CS44 MODULE1 Chapter2Dokumen38 halaman18CS44 MODULE1 Chapter2Jim MoriartyBelum ada peringkat

- Address Decoding TechniqueDokumen8 halamanAddress Decoding TechniqueYash SarohaBelum ada peringkat

- Interrupt Sequence in An 8086 SystemDokumen3 halamanInterrupt Sequence in An 8086 Systemyr48Belum ada peringkat

- Instruction Format 8051Dokumen26 halamanInstruction Format 8051alex24arulBelum ada peringkat

- Subsystem Design: Architectural IssuesDokumen26 halamanSubsystem Design: Architectural IssuesSanjana M PBelum ada peringkat

- Memory Interfacing With 8086Dokumen10 halamanMemory Interfacing With 8086satyanarayana12Belum ada peringkat

- Unit 4: Multiplexing and Multi-User AccessDokumen44 halamanUnit 4: Multiplexing and Multi-User AccessdfbbvcxBelum ada peringkat

- 8086 and Memory Interfacing - FinalDokumen28 halaman8086 and Memory Interfacing - FinalAnushkaSinha100% (2)

- 8086 Microprocessor - InterruptsDokumen35 halaman8086 Microprocessor - InterruptsRocky SamratBelum ada peringkat

- ARM Exception HandlingDokumen30 halamanARM Exception HandlingkarthikborkarBelum ada peringkat

- Assignment 1Dokumen10 halamanAssignment 1vijaya saraswathi jayakumarBelum ada peringkat

- EE8711-Power System Simulation Lab ManualDokumen162 halamanEE8711-Power System Simulation Lab ManualAbdul YaseenBelum ada peringkat

- Memory InterfacingDokumen14 halamanMemory InterfacingSusmita Sau100% (3)

- Ec8762 Dip Lab ManualDokumen55 halamanEc8762 Dip Lab ManualSridharan D100% (1)

- Two Stage AmplifierDokumen17 halamanTwo Stage AmplifierRobert Tac-an Nericua100% (1)

- Running Machines: Arm Multiple ChoiceDokumen4 halamanRunning Machines: Arm Multiple ChoicePoojaBelum ada peringkat

- Microprocessor Question BankDokumen4 halamanMicroprocessor Question BankDarshan SharmaBelum ada peringkat

- Unit 7 Interfacing Memory and Parallel IO PeripheralsDokumen23 halamanUnit 7 Interfacing Memory and Parallel IO PeripheralsPreetham Saigal0% (1)

- Unit-I Introduction To Cellular Mobile Communications Limitations of Conventional Mobile Telephone SystemsDokumen33 halamanUnit-I Introduction To Cellular Mobile Communications Limitations of Conventional Mobile Telephone SystemsJeevan Sai Maddi100% (1)

- Embedded Systems Lab Manual Exp. 1-4Dokumen18 halamanEmbedded Systems Lab Manual Exp. 1-4Akshit Jain100% (1)

- EMIDokumen25 halamanEMIBala SubramanyamBelum ada peringkat

- 2 MarksDokumen11 halaman2 MarksSid VibhorBelum ada peringkat

- eInfoChips Interview QuestionsDokumen2 halamaneInfoChips Interview Questionsshafi hasmaniBelum ada peringkat

- 8051 Instruction SetDokumen79 halaman8051 Instruction SetpremsonyBelum ada peringkat

- 8086 - Interfacing Analog To Digital Converters (ADC)Dokumen22 halaman8086 - Interfacing Analog To Digital Converters (ADC)PARIJAAT B MITRABelum ada peringkat

- IoT Module-5 NotesDokumen6 halamanIoT Module-5 Notessachin mBelum ada peringkat

- Microcontroller 8051Dokumen72 halamanMicrocontroller 8051vaibhav sharmaBelum ada peringkat

- 8051 MicrocontrollerDokumen32 halaman8051 MicrocontrollerRachit Sharma91% (11)

- CNTLDokumen31 halamanCNTLAkanksha DixitBelum ada peringkat

- SAN Problems: Application IOPS and RAID ConfigurationsDokumen6 halamanSAN Problems: Application IOPS and RAID ConfigurationsArsalan OzilBelum ada peringkat

- UNIT-V-TMS320C54x-DSP ProcessorDokumen47 halamanUNIT-V-TMS320C54x-DSP ProcessorVasant DivekarBelum ada peringkat

- 8086 Lab manual-DTU PDFDokumen46 halaman8086 Lab manual-DTU PDFsivakumarBelum ada peringkat

- ARM - PPT 8Dokumen74 halamanARM - PPT 8roysalways4u100% (1)

- 2 Marks Question Power System 1Dokumen10 halaman2 Marks Question Power System 1Arun KumarBelum ada peringkat

- 8051 Oscillator CKT Diagram and DescriptionDokumen3 halaman8051 Oscillator CKT Diagram and DescriptionVipul Badge100% (1)

- Introduction To Asics: Application-Specific Integrated CircuitsDokumen21 halamanIntroduction To Asics: Application-Specific Integrated CircuitsRameshkumar JayaramanBelum ada peringkat

- Modes in Cylindrical Optical FiberDokumen16 halamanModes in Cylindrical Optical FiberbeaulajenishBelum ada peringkat

- EE8691-Embedded SystemsDokumen10 halamanEE8691-Embedded SystemspranavBelum ada peringkat

- CPDS Viva QuestionsDokumen20 halamanCPDS Viva QuestionsUday Desiraj67% (6)

- VLSI Array SubsystemsDokumen17 halamanVLSI Array SubsystemsSireesha Tekuru80% (5)

- UNIT 4 - Switched CapacitanceDokumen75 halamanUNIT 4 - Switched Capacitancerajasekarkpr100% (1)

- 8096 Microcontrollers NotesDokumen9 halaman8096 Microcontrollers NotesNarasimha Murthy YayavaramBelum ada peringkat

- Basic Concepts of Memory Interfacing - ComputerSCDokumen7 halamanBasic Concepts of Memory Interfacing - ComputerSCParamartha BanerjeeBelum ada peringkat

- The 8085 Microprocessor ArchitectureDokumen30 halamanThe 8085 Microprocessor Architectureabhisheksharma12392% (13)

- Types of PipelineDokumen2 halamanTypes of Pipelinenazia100% (1)

- Keyboard Interfacing PicDokumen4 halamanKeyboard Interfacing PicJacob Chako100% (1)

- Question Paper 8051 Microcontroller and ApplicationsDokumen1 halamanQuestion Paper 8051 Microcontroller and Applicationsveeramaniks408Belum ada peringkat

- DSD Lab ManualDokumen64 halamanDSD Lab ManualAkkonduru KumarBelum ada peringkat

- Barrel ShifterDokumen79 halamanBarrel ShifterVinay Reddy100% (2)

- Unit-4 Memory NotesDokumen25 halamanUnit-4 Memory NotestarunprovidesBelum ada peringkat

- Computer OrganizationDokumen32 halamanComputer Organizationy22cd125Belum ada peringkat

- Chapter 4 Memory ElementDokumen87 halamanChapter 4 Memory ElementWann FarieraBelum ada peringkat

- E2805 B 43Dokumen4 halamanE2805 B 43Verma JagdeepBelum ada peringkat

- How RAM WorksDokumen9 halamanHow RAM WorksPablo Miguel FelsteadBelum ada peringkat

- How RAM WorksDokumen3 halamanHow RAM WorksMohamed Hussain100% (2)

- Architecture Part 2Dokumen3 halamanArchitecture Part 2araik.gevorgyan.20021907Belum ada peringkat

- Dlco Unit 5 PDFDokumen24 halamanDlco Unit 5 PDFKarunya MannavaBelum ada peringkat

- MemoryDokumen27 halamanMemorySRUTHI. SBelum ada peringkat

- EFSDokumen4 halamanEFSRobson RogérioBelum ada peringkat

- DxDiag 2Dokumen20 halamanDxDiag 2iwanssloBelum ada peringkat

- Dcuci50 SG Vol1Dokumen448 halamanDcuci50 SG Vol1kayudo80Belum ada peringkat

- Want To Obtain Optimum Picture Quality With Your SAMSUNG Ultra HD Blu-Ray Player?Dokumen2 halamanWant To Obtain Optimum Picture Quality With Your SAMSUNG Ultra HD Blu-Ray Player?fuilkjBelum ada peringkat

- DWSIM Installation GuidelinesDokumen4 halamanDWSIM Installation GuidelinesVignesh KBelum ada peringkat

- Dell Technologies SC420 DatasheetDokumen3 halamanDell Technologies SC420 DatasheetNathalia MoralesBelum ada peringkat

- Cap10 DX75620 Trickytec ENDokumen10 halamanCap10 DX75620 Trickytec ENEdinson Ariel Chavarro QuinteroBelum ada peringkat

- Library Management SystemDokumen6 halamanLibrary Management Systemmani gridlabsBelum ada peringkat

- Colibri Carrier Board Design GuideDokumen47 halamanColibri Carrier Board Design GuideshahbazBelum ada peringkat

- Toshiba Stor.e Alu 2S 2.5 PDFDokumen0 halamanToshiba Stor.e Alu 2S 2.5 PDFGina van GeelBelum ada peringkat

- Intel Core 2 Duo E4600 SpecificationsDokumen5 halamanIntel Core 2 Duo E4600 Specificationsclaus47Belum ada peringkat

- PR-780 3G Series Embedded 4-Channel DVR PR-790 Series Embedded 4-Channel DVRDokumen1 halamanPR-780 3G Series Embedded 4-Channel DVR PR-790 Series Embedded 4-Channel DVRCollege SansFilBelum ada peringkat

- Exploring The PICK Operating System 2nd Edition by Jonathan E Sisk and Steve VanArsdaleDokumen366 halamanExploring The PICK Operating System 2nd Edition by Jonathan E Sisk and Steve VanArsdaleMartin MoralesBelum ada peringkat

- Instruction For Calibrator-GBDokumen21 halamanInstruction For Calibrator-GBFauziah100% (1)

- Arm Instruction ProgramDokumen121 halamanArm Instruction ProgramErmin KatardzicBelum ada peringkat

- Centrala Za Dojavu Pozara-Cad-150-2Dokumen2 halamanCentrala Za Dojavu Pozara-Cad-150-2Milorad PantelinacBelum ada peringkat

- BK3431 BekenDokumen18 halamanBK3431 BekenrmBelum ada peringkat

- Oracle Database Appliance Help Desk Support Consultant Online AssessmentDokumen29 halamanOracle Database Appliance Help Desk Support Consultant Online AssessmentCarlos OrellanaBelum ada peringkat

- Diagrama Cabos PLCDokumen17 halamanDiagrama Cabos PLCnferreiBelum ada peringkat

- GPU ArchitectureDokumen28 halamanGPU Architecturesalution technologyBelum ada peringkat

- 5.3 IBM General Parallel File System: 5.3.1 Common GPFS FeaturesDokumen12 halaman5.3 IBM General Parallel File System: 5.3.1 Common GPFS FeaturesRajBelum ada peringkat

- Ib 0600516 EngfDokumen148 halamanIb 0600516 EngfRafael GagoBelum ada peringkat

- SF600 Specification V2.6Dokumen24 halamanSF600 Specification V2.6L Vinoth LoganathanBelum ada peringkat

- Power On Self Test Beep CodesDokumen5 halamanPower On Self Test Beep CodesTilak AmarghdeBelum ada peringkat

- x3650 m4 7915 Isg en PDFDokumen1.218 halamanx3650 m4 7915 Isg en PDFUdin PABelum ada peringkat

- Mockingboard 4c+ Installation ManualDokumen10 halamanMockingboard 4c+ Installation Manual9tg5gv8jtqBelum ada peringkat

- Assignment 1 Comp314Dokumen6 halamanAssignment 1 Comp314Lam DerekBelum ada peringkat

- SXS Memory Card / Hardware Compatibility ChartDokumen1 halamanSXS Memory Card / Hardware Compatibility ChartSonyProUSABelum ada peringkat

- Streamline NX v3Dokumen8 halamanStreamline NX v3Datthanhtv NguyenBelum ada peringkat

- FV-121NT-T51: en Vir On M en TDokumen3 halamanFV-121NT-T51: en Vir On M en Tthe jejunBelum ada peringkat

- CISSP All-in-One Exam Guide, Ninth EditionDari EverandCISSP All-in-One Exam Guide, Ninth EditionPenilaian: 5 dari 5 bintang5/5 (1)

- Chip War: The Fight for the World's Most Critical TechnologyDari EverandChip War: The Fight for the World's Most Critical TechnologyPenilaian: 4.5 dari 5 bintang4.5/5 (82)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyDari EverandChip War: The Quest to Dominate the World's Most Critical TechnologyPenilaian: 4.5 dari 5 bintang4.5/5 (228)

- Cyber-Physical Systems: Foundations, Principles and ApplicationsDari EverandCyber-Physical Systems: Foundations, Principles and ApplicationsHoubing H. SongBelum ada peringkat

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Dari EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Penilaian: 5 dari 5 bintang5/5 (1)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsDari EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsPenilaian: 5 dari 5 bintang5/5 (3)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Dari EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Penilaian: 5 dari 5 bintang5/5 (3)

- Computer Science: A Concise IntroductionDari EverandComputer Science: A Concise IntroductionPenilaian: 4.5 dari 5 bintang4.5/5 (14)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Dari EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Penilaian: 5 dari 5 bintang5/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Dari EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Penilaian: 5 dari 5 bintang5/5 (2)

- SysML in Action with Cameo Systems ModelerDari EverandSysML in Action with Cameo Systems ModelerPenilaian: 5 dari 5 bintang5/5 (2)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFDari EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFBelum ada peringkat

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxDari EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxBelum ada peringkat

- The comprehensive guide to build Raspberry Pi 5 RoboticsDari EverandThe comprehensive guide to build Raspberry Pi 5 RoboticsBelum ada peringkat

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XDari EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XPenilaian: 3 dari 5 bintang3/5 (2)

- Raspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideDari EverandRaspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideBelum ada peringkat

- Amazon Web Services (AWS) Interview Questions and AnswersDari EverandAmazon Web Services (AWS) Interview Questions and AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (3)

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XDari EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XPenilaian: 5 dari 5 bintang5/5 (1)

- Cancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionDari EverandCancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionPenilaian: 5 dari 5 bintang5/5 (2)

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesDari EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesBelum ada peringkat

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1715193157?v=1)