Encoder S

Diunggah oleh

josemarazJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Encoder S

Diunggah oleh

josemarazHak Cipta:

Format Tersedia

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Captulo 4.

DISEO DEL ENCODER

4.1 ARQUITECTURA

4.2 RBOL DE WALLACE

4.3 SUMADORES

4.4 FUNCIONAMIENTO

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

4.1 ARQUITECTURA

Un encoder no es ms que un elemento que traduce un cdigo termomtrico a

cdigo binario de N bits. A la hora de disear un encoder tenemos varias opciones y

arquitecturas. En nuestro diseo el encoder deber tener en cuenta los siguientes

aspectos:

1. La reasignacin de comparadores, es decir, cualquier comparador puede

ser reasignado a cualquier otro cdigo.

2. Solamente sern vlidas un grupo de salidas de comparadores (las de los

comparadores seleccionados en la etapa de calibracin). Las salidas de

los comparadores no seleccionados deben ser ignoradas.

3. Las salidas de los comparadores pueden no formar un cdigo

termomtrico debido a los errores de burbuja.

4. El nmero de comparadores ser mayor de 63 debido a los valores extra

de referencias de tensin aadidas en los extremos del rango de tensiones

a la entrada para asegurar una densidad uniforme de referencias de

tensin. Estas referencias de tensin se aadirn colocando ms

resistencias en la escalera, tanto por arriba como por abajo, con lo cual el

nmero de comparadores de la escalera aumentar.

En la figura 4.1 podemos ver algunas soluciones arquitecturales para un encoder. En la

figura 4.1(a) no hay reasignacin de comparadores con lo que podemos usar una

estructura tradicional para nuestro encoder. En la figura 4.1(b) las referencias de tensin

de los comparadores 4 y 5 estn intercambiadas debido a que hay una burbuja en la

salida de uno de los comparadores. Para corregir esto los comparadores 4 y 5 deben ser

reasignados. Una posible solucin para esto consiste en reasignar explcitamente las

salidas de los comparadores 4 y 5 para formar un cdigo termomtrico (ver figura

4.1(b)). Despus de esto podemos usar un esquema de encoder tradicional para

completar el proceso de conversin. El problema de esta solucin es que requiere una

gran matriz de conexiones que consumir mucha rea y potencia. Esta matriz ser

lgicamente mayor, cuanto mayor sea el nmero de bits (N) de nuestro cdigo binario.

Un esquema de encoders muy usado para conversiones A/D de alta velocidad consiste

en contar el nmero de 1 sumando. El hecho de contar los 1 sumando, hace que el

encoder sea inmune a los errores de burbuja. Como podemos ver en la figura 4.1(c),

obtenemos una salida digital totalmente correcta con el simple hecho de sumar los 1.

A la hora de usar esta arquitectura debemos tener en cuenta la redundancia de

comparadores de manera que slo se puedan contar como mximo un total de NC unos,

siendo NC el nmero de comparadores sin hacer redundancia, es decir, las salidas de los

comparadores no seleccionados deben ser ignoradas. Esto no es difcil de implementar

en nuestro diseo ya que los comparadores no seleccionados tienen por defecto su salida

a 0 y no contribuyen por tanto al resultado de la suma. Un encoder diseado mediante

suma, se encarga implcitamente tambin de la reasignacin de comparadores. Es por

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

esta facilidad y sencillez de operacin por lo que hemos escogido un encoder basado en

suma para nuestro esquema.

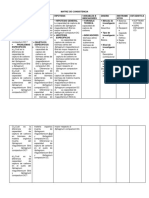

Figura 4.1. Soluciones para el encoder

A la hora de comenzar a disear nuestro encoder, es necesario tener en cuenta dos

aspectos esenciales comentados anteriormente.

1. Referencias de tensin extra: Las referencias de tensin que vamos a aadir a

cada extremo de nuestro tango de tensiones, implicar que se tengan que aadir

resistencias a cada extremo de nuestra escalera. Debido a qque el nmero de

referencias de tensin est ligado al nmero de comparadores mediante la

expresin.

1 = NR NC

Donde NC=nmero de comparadores y NR=nmero de resistencias de la

escalera de resistencias.

En principio el nmero de comparadores de nuestro Flash es de 63 ya que:

1 2 =

N

NC

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Siendo N=nmero de bits. En nuestro caso N=6 tendremos, NC=63 y por tanto

NR=64.

Como ya comentamos en el captulo anterior, debemos aadir 10 referencias de

tensin extra por arriba y por debajo de nuestra escalera aproximadamente. Para

simplificar nuestro diseo del encoder, tomaremos un nmero de referencias

extra a aadir que sea mltiplo de 2

N

. Como 10 no es mltiplo de 2

N

, cogeremos

el nmero inmediatamente inferior que sea mltiplo de 2

N

, es decir, tomaremos 8

referencias extras de tensin por cada lado. Lo que implica un total de:

80 8 64 8 = + + = NR

79 = NC

Tendremos entonces un total de 80 resistencias y 79 comparadores en nuestro

Flash sin hacer redundancia.

2. Redundancia: como ya vimos en el captulo anterior, la redundancia de

comparadores es un aspecto bsico en nuestro diseo. Como ya dijimos tambin

en ese captulo, el nmero idneo para hacer redundancia era 4, debido a que

con esta cantidad de redundancia obtenemos buenos valores de SNDR,

pudindonos permitir en los comparadores un offset bastante alto (de unos

5LSB). Por tanto nuestro esquema Flash bsico formado por escalera de

resistencias y comparadores deber ser repetido hasta cuatro veces en nuestro

circuito. Obviamente, y ya que la escalera de resistencias es la misma para los

cuatro bloques, no implementaremos cuatro escaleras para nuestro esquema ya

que esto incrementara el consumo mucho. Lo que haremos ser utilizar la

misma escalera de resistencias para los cuatro bloques de comparadores.

En la figura 4.2 podemos observar el esquema resultante una vez tenidos en cuenta estos

dos aspectos fundamentales para el diseo del encoder. Como podemos observar en la

grfica, el nmero total de entradas que irn al encoder ser de 315 entradas. As

mismo, podemos ver como en el cuarto bloque de comparadores no tenemos 8

resistencias extras por debajo sino que slo tenemos 7. Esto est relacionado con el

nmero de entradas que van al encoder, ya que como veremos ms adelante

detalladamente, con 315 entradas el circuito del encoder se simplifica mucho ms que si

tenemos 316 entradas.

Una vez que hemos elegido el mtodo de suma como mtodo idneo para el encoder,

debemos disear la estructura de dicho encoder. Para ello nos basaremos en un artculo

de R. Kanan

1

. A pesar de que en este artculo no encontramos un encoder que se ajuste

a nuestras necesidades, si que nos da una idea de cmo disearlo. Tras descartar otras

posibilidades, el esquema final con el que nos quedamos para nuestro diseo es el

mostrado en la figura 4.3.

1

A 640mW high accuracy 8-bit lGHz flash ADC encoder

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Figura 4.2. Esquema con referencias de tensin extras y redundancia

Figura 4.3. Esquema interno del encoder

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Como vemos en el esquema anterior, el objetivo es realizar varias cuentas de forma

paralela y despus sumarlas todas en paralelo tambin, con una estructura en pipeline.

Cada etapa est separada de la etapa posterior y anterior mediante un bloque de

biestables con lo que conseguimos una perfecta estructura en pipeline. El inconveniente

de esta estructura en pipeline es que tardaremos ms en obtener la primera salida del

encoder, concretamente, tardaremos 5 ciclos de reloj en obtener dicha salida ya que

tenemos 5 etapas de pipeline. La gran ventaja es que despus de estos 5 ciclos

obtendremos las salidas en cada ciclo de reloj sin tener que esperar a que las seales

atraviesen todo el retraso combinacional de las puertas que hay desde la entrada hasta la

salida.

Como podemos ver en el esquema, nuestro encoder estar compuesto por:

rboles de Wallace de 5 bits: que sern los circuitos encargados de contar los 1.

Sumadores de 5 y 6 bits: que sern los encargados de sumar las diferentes cuentas

que se realizan de manera independiente.

Biestables tipo D: sern los encargados de dividir nuestro circuito en varias etapas

con el objetivo de hacer una estructura en pipeline.

El diseo de estos elementos se detalla apliamente a continuacin.

4.2 RBOL DE WALLACE

Como ya hemos comentado anteriormente y hemos mostrado en el esquema del

encoder, usaremos la estructura de rbol de Wallace para contar los 1 debido a que es

la estructura ms rpida para la cuenta de unos. En el artculo de R. Kanan mencionado

anteriormente podemos encontrar el esquema de un rbol de Wallace de 4 bits. No

obstante nosotros necesitamos uno de 5 bits con lo que ser necesario hacer un diseo

propio nuevamente.

El rbol de Wallace se basa nicamente en celdas elementales de suma. En la primera

etapa lgica del rbol se cuenta el nmero de 1 a la entrada y expresa el resultado a la

salida con un cdigo binario de 2 bits. La segunda etapa consiste en sumar las salidas de

2 bits de las celdas adyacentes dos a dos, dando una salida binaria de 3 bits, y as

sucesivamente hasta obtener el cdigo binario final a la salida para el rbol. El nmero

de celdas bsicas de un rbol de Wallace de N bits viene dado por la expresin:

1 2 = N n

N

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Con lo que un rbol de Wallace de 5 bits como los que necesitamos tendr un total de

26 celdas elementales. Siguiendo el esquema del rbol de Wallace de 4 bits expuesto en

el artculo mencionado anteriormente, podemos llegar a un rbol de 5 bits como el

mostrado a continuacin. Como podemos ver en la grfica, el rbol de Wallace de 5 bits

ha sido obtenido a partir del rbol de Wallace de 4 bits, duplicando la estructura, con

esto conseguimos un bit ms de resolucin. Esta tcnica de duplicar la estructura para

conseguir un bit ms de resolucin es muy empleada a la hora de disear circuitos

digitales ya que en un rbol de Wallace de N bits de resolucin tenemos:

2

N

posibles valores de entrada

Si duplicamos la estructura, en el nuevo rbol que obtenemos tendremos ahora:

2 x 2

N

=2

N+1

posibles valores de entrada

Es decir, la resolucin de este nuevo rbol construido duplicando la estructura ser N+1

bits, con lo que vemos que duplicando la estructura, la resolucin ha aumentado en 1

bit. Siguiendo este razonamiento pasamos del rbol de Wallace de 4 bits explicado en el

artculo anterior al rbol de Wallace de 5 bits mostrado a continuacin:

Figura 4.4. rbol de Wallace de 5 bits

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Como ya comentamos en el apartado anterior, la estructura de nuestro encoger se

simplifica mucho si el nmero de entradas es 315 en lugar de 316, es por eso por lo que

hemos eliminado una referencia de tensin en el bloque de comparadores ms bajo. Este

hecho, est relacionado con lo que acabamos de explicar referente al duplicado de

estructuras. Como vemos en la figura 4.3, la entrada de nuestro encoger est formada

por rboles de Wallace de 5 bits. Cada rbol de Wallace tiene 2

N

-1 entradas, es decir

que cada rbol de Wallace de 5 bits tiene 31 entradas. Adems debemos saber que por

cada dos rboles de Wallace podemos incluir otra entrada extra, que ir directamente

conectada a la segunda etapa de celdas unidad del rbol. Este fenmeno puede

observarse en la figura 4.4. Como vemos al duplicar dos rboles de Wallace de 4 bits no

hemos obtenido 30 entradas sino 31. Esa entrada extra ha sido conectada directamente a

la segunda etapa lgica de celdas del rbol de 5 bits como podemos ver en la figura.

Exactamente lo mismo ocurre cuando duplicamos rboles de 5 bits, por cada dos

rboles conseguimos una entrada extra. Entonces si llamamos NW al nmero de rboles

de Wallace de 5 bits usados en la primera etapa de nuestro encoder y NE al nmero de

entrdas disponibles en nuestro encoder, podemos calcular el nmero de entradas

disponibles para nuestro encoder mediante la siguiente expresin:

2

31

NW

NW NE + =

En nuestro caso tenemos:

315 = NE

Es por esto por lo que el nmero de entradas ha sido reducido de 316 a 315, as nos

evitamos tener que volver a duplicar la estructura con lo que se aadiran unos cuantos

rboles de Wallace ms que sera desaprovechados ya que slo usaramos una de sus

entradas. Con 315 entradas conseguimos una estructura ptima.

Como vemos en el esquema anterior del rbol de 5 bits, el rbol est formado

nicamente por celdas elementales de tres entradas y dos salidas. Las salidas de estas

celdas dependern del nmero de unos que tengamos a la entrada de ellas. La relacin

entre las entradas y las salidas en cada celda es la siguiente:

Figura 4.5. Relacin entre las entradas y las salidas de una celda unidad

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Con esta relacin entre entradas y salidas, y usando un mapa de Karnaugh, podemos

sacar con facilidad la expresin de la celda unidad mediante puertas lgicas. Si

llamamos A, B y C a las entradas y S1 y S2 a las salidas obtenemos:

S1: (A and B) or [ (A or B) and C ] =AB +AC +BC

S2: [ (A xor B) and not C ] or [ (A xnor B) and C ] =(A

B)notC +not(A

B)C =A

C

Figura 4.5. Celda unidad obtenida mediante mapas de Karnaugh

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

4.3 SUMADORES

Como ya hemos mencionado anteriormente y mostrado en la figura 4.3, sern

necesarios distintos tipos de sumadores para nuestro encoder. En concreto sern

necesarios sumadores de 5 y 6 bits. Como podemos ver en la figura 4.3, estos

sumadores se encargan de ir sumando en paralelo .los 1 contados por los rboles de

Wallace. La suma de los 1 contados no se hace toda de una sola vez sino que se

divide en etapas separadas una de otra mediante biestables formando una estructura en

pipeline, como ya explicamos anteriormente.

Normalmente los sumadores suelen ser circuitos bastante lentos ya que aunque realizan

con bastante rapidez el clculo de una suma, tiene que esperar a que les llegue el acarreo

de la etapa anterior con lo cual el retraso combinacional se va incrementando hasta

hacerse significativo. Debido a que en nuestro circuito necesitamos sumadores de la

mayor velocidad posible, optaremos por sumadores que minimicen este retraso de los

acarreos. Estos sumadores son los sumadores con seleccin de acarreo.

Figura 4.6. Sumador con seleccin de acarreo

Como podemos ver en la figura, en cada etapa se calcula la suma para los dos posibles

acarreos, tanto para acarreo 0 como para acarreo 1. Despus el valor correcto se

elige dependiendo del acarreo de la etapa anterior mediante una lgica de seleccin que

no es ms que un multiplexor.

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

4.4 FUNCIONAMIENTO

Una vez que ya tenemos diseada la arquitectura de nuestro encoder, pasaremos

a montarlo y simularlo con CADENCE. En primer lugar vemos que en las libreras

dadas por el fabricante, no disponemos de puertas AND ni OR, pero si NAND, con lo

cual lo primero ser expresar el circuito de la figura 4.5 con las puertas adecuadas a

nuestra tecnologa.

Figura 4.7. Celda unidad en CADENCE

Una vez que tenemos esto pasamos a montar los rboles de Wallace de 4 y 5 bits

y a continuacin pasamos a montar los sumadores y los bloques de biestables. Una vez

que tenemos todos los bloques montados, pasamos a construir el esquema de la figura

4.3, obteniendo lo siguiente:

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Figura 4.8. Esquema del encoder en CADENCE

Es importante sealar que las 5 entradas extras que sacamos fruto de la duplicacin de

los rboles de Wallace de 5 bits, debern ser retrasadas mediante biestables antes de ser

conectadas a los sumadores de 5 bits. Estos biestables sern necesarios ya que estas 5

seales no han pasado por el primer bloque grande de biestables con lo que irn

adelantadas respecto a las 310 seales restantes.

Para probar el funcionamiento del encoder haremos u anlisis variando las entradas.

Conectaremos dos fuentes de tensin que den pulsos cuadrados con distinto periodo.

Una de las fuentes la conectamos a las 6 entradas ms bajas y la otra a las 9 entradas

ms altas, de manera que cuando las dos fuentes estn a 1 la salida deber ser 15,

cuando slo una de ellas est a 1, la salida deber ser 6 o 9, dependiendo de la que

est a 1 y cuando las dos estn a 0 la salida deber ser 0. El funcionamiento se

detalla en el siguiente diagrama.

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Figura 4.9. Cambio de las entradas y resultado que se debe obtener

Con estas entradas el resultado obtenido trabajando a una frecuencia de 300Mhz es el

siguiente:

Figura 4.10. Resultado de simulacin del encoder en CADENCE

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

______________________________________________________________________

DISEO DE UN ADC CON ESQUEMA DE AUTOCALIBRACIN

Como vemos en la grfica, en primer lugar tenemos el reloj, que en este caso es de

300Mhz. Esta ha sido la frecuencia ms alta para la que hemos podido conseguir un

correcto funcionamiento en simulacin, por lo que esta ser la frecuencia que limite la

frecuencia de funcionamiento de nuestro convertidor por el momento. Como vemos las

salidas correctas empiezan a producirse una vez pasados 5 ciclos de reloj como ya

anunciamos anteriormente debido a la estructura en pipeline. A continuacin tenemos

los valores que van tomando las dos fuentes y por ltimo tenemos las salidas de los 6

bits desde el MSB hasta el LSB en orden descendente. Como podemos observar si nos

fijamos en los cuatro bits menos significativos, las salidas son las que ya esperbamos,

es decir: 15, 9, 6 y 0.

Por tanto podemos concluir diciendo que a pesar de la buena arquitectura seleccionada

(la ms rpida posible), la frecuencia de nuestro encoder y por tanto de nuestro

convertidor esta por ahora limitada a 300Mhz.

______________________________________________________________________________________________

Rafael Ibez Hueso Julio2006

Anda mungkin juga menyukai

- Mae Ecomomia AplicadaDokumen2 halamanMae Ecomomia AplicadajosemarazBelum ada peringkat

- Apunte para La Guía 3 PDFDokumen4 halamanApunte para La Guía 3 PDFjosemarazBelum ada peringkat

- Plan de Estudio LICENCIATURA EN MATEMATICA APLICADADokumen5 halamanPlan de Estudio LICENCIATURA EN MATEMATICA APLICADAjosemarazBelum ada peringkat

- Apunte para La Guía1Dokumen8 halamanApunte para La Guía1josemarazBelum ada peringkat

- Practicas Completas 1S 2020 PDFDokumen23 halamanPracticas Completas 1S 2020 PDFjosemarazBelum ada peringkat

- Teórica 2 EC LimitesDokumen9 halamanTeórica 2 EC LimitesjosemarazBelum ada peringkat

- Ingeniería ElectromecánicaDokumen4 halamanIngeniería ElectromecánicaGustavo DoevioBelum ada peringkat

- Ceo Capital Hum A NoDokumen68 halamanCeo Capital Hum A NoLucHo GuardiolaBelum ada peringkat

- Elpuertoparalelocon LabviewDokumen17 halamanElpuertoparalelocon LabviewViviano AlmonteBelum ada peringkat

- Rotacion EjesDokumen26 halamanRotacion Ejesca_alzuBelum ada peringkat

- Manual Sinamics V20 2016 PDFDokumen35 halamanManual Sinamics V20 2016 PDFhmariño_7Belum ada peringkat

- Control PidDokumen6 halamanControl PidR Rdez DaveBelum ada peringkat

- Bobinas de RogowskiDokumen38 halamanBobinas de RogowskiJhoan David Bermúdez CardonaBelum ada peringkat

- IrracionalesDokumen17 halamanIrracionalesjosemarazBelum ada peringkat

- Prof. MatematicaDokumen3 halamanProf. MatematicajosemarazBelum ada peringkat

- CB Matematica Mecanica PDFDokumen97 halamanCB Matematica Mecanica PDFtornero78100% (1)

- SPL Parametros SoldaduraDokumen3 halamanSPL Parametros SoldadurajosemarazBelum ada peringkat

- Potencia ElectricaDokumen23 halamanPotencia ElectricaeldubiBelum ada peringkat

- 7 Automatismoelectronico153-216 PDFDokumen64 halaman7 Automatismoelectronico153-216 PDFDaniel Acevedo ChaconBelum ada peringkat

- Euler AbbDokumen8 halamanEuler AbbjosemarazBelum ada peringkat

- Enseñar geometría proyectiva en la formación de profesoresDokumen10 halamanEnseñar geometría proyectiva en la formación de profesoresjosemarazBelum ada peringkat

- MENDEZ 2 HermanosDokumen4 halamanMENDEZ 2 Hermanosjosemaraz100% (1)

- Manual RapidDokumen1.322 halamanManual RapidjosemarazBelum ada peringkat

- Unidad3 TRIGONOMETRIA 1ºparteDokumen17 halamanUnidad3 TRIGONOMETRIA 1ºparteJuli AmayaBelum ada peringkat

- TrifasicaDokumen38 halamanTrifasicaOscar Manuel Manuel PatiñoBelum ada peringkat

- Tema 5. El Tiristor: ÁnodoDokumen8 halamanTema 5. El Tiristor: ÁnodoFernando Cruz AlvizoBelum ada peringkat

- Tema 5. El Tiristor: ÁnodoDokumen8 halamanTema 5. El Tiristor: ÁnodoFernando Cruz AlvizoBelum ada peringkat

- Control soldadura resistencia SERRATRON 10iSTDokumen98 halamanControl soldadura resistencia SERRATRON 10iSTjosemarazBelum ada peringkat

- Tema 5. El Tiristor: ÁnodoDokumen8 halamanTema 5. El Tiristor: ÁnodoFernando Cruz AlvizoBelum ada peringkat

- ARO Compact Welder 9A09 T387EDokumen91 halamanARO Compact Welder 9A09 T387EjosemarazBelum ada peringkat

- Diagrama de ParetoDokumen4 halamanDiagrama de ParetoDevis WillBelum ada peringkat

- Equipo de red necesario para acceso inalámbrico de meseros y clientesDokumen4 halamanEquipo de red necesario para acceso inalámbrico de meseros y clientesRafaelBelum ada peringkat

- Plan Estratégico Del Programa de Estudios de Computación e Informática - Iestp Padre Abad 2018Dokumen5 halamanPlan Estratégico Del Programa de Estudios de Computación e Informática - Iestp Padre Abad 2018OswaldoAlexHilarioFernandezBelum ada peringkat

- Aditivos QuimicosDokumen4 halamanAditivos QuimicosJJ ESBelum ada peringkat

- COA y validación técnicas análisisDokumen4 halamanCOA y validación técnicas análisisMaria PaulaBelum ada peringkat

- 12 Formas de Vender Tus Clases Presenciales Como Cursos OnlineDokumen5 halaman12 Formas de Vender Tus Clases Presenciales Como Cursos OnlinePLKBelum ada peringkat

- Uso de Flashback OracleDokumen9 halamanUso de Flashback OracleKaterin GutierrezBelum ada peringkat

- 24 - Python, GraficandoDokumen25 halaman24 - Python, GraficandoFreddy QuinnBelum ada peringkat

- Planeación de ProcesosDokumen7 halamanPlaneación de ProcesosjosemanuelmachaBelum ada peringkat

- Capitulo6 PDFDokumen3 halamanCapitulo6 PDFLina LuciaBelum ada peringkat

- Todo para Celulares Chinos! (Codigos, Configuraciones y Mas..Dokumen6 halamanTodo para Celulares Chinos! (Codigos, Configuraciones y Mas..yohan rosalesBelum ada peringkat

- Lección 7Dokumen5 halamanLección 7لويس أنتوني نونيزBelum ada peringkat

- Ejemplo Didactico DataMartDokumen44 halamanEjemplo Didactico DataMartAlberto lopez avendañoBelum ada peringkat

- Seguidor de línea velocista: normas y competencia de robots autónomosDokumen5 halamanSeguidor de línea velocista: normas y competencia de robots autónomosDiego Armando Torrez TiconaBelum ada peringkat

- Contador de Programa Del Microprocesador Z80Dokumen10 halamanContador de Programa Del Microprocesador Z80FernandoQuisaguano0% (1)

- Produccion Final de LogicaDokumen21 halamanProduccion Final de LogicaRicky AlmonteBelum ada peringkat

- Reporte EstadiaDokumen17 halamanReporte EstadiaEnrique Gonzalez HerreraBelum ada peringkat

- Arquitectura Del ComputadorDokumen9 halamanArquitectura Del ComputadorSilvio ArzenoBelum ada peringkat

- GHJ Razonamiento Matematico U2A2Dokumen4 halamanGHJ Razonamiento Matematico U2A2Gustavo HernándezBelum ada peringkat

- EspiralDokumen12 halamanEspiralChivas De CorazonBelum ada peringkat

- Informe de práctica académica sobre estudio de viabilidad técnico-económica del cambio de tecnología de producción de agua desmineralizadaDokumen1 halamanInforme de práctica académica sobre estudio de viabilidad técnico-económica del cambio de tecnología de producción de agua desmineralizadaIvan MarsigliaBelum ada peringkat

- Trabajo Práctico 3Dokumen5 halamanTrabajo Práctico 3Ariel LedesmaBelum ada peringkat

- Estudio de Caso #4Dokumen5 halamanEstudio de Caso #4joseK.0% (1)

- Tarea Estrategias Avanz. Control PDFDokumen24 halamanTarea Estrategias Avanz. Control PDFjoshuac4Belum ada peringkat

- Procesador de TextosDokumen3 halamanProcesador de TextosArlette SamBelum ada peringkat

- Capacidad captura carbono SphagnumDokumen2 halamanCapacidad captura carbono Sphagnumjesus curichahuaBelum ada peringkat

- Definición DeseminarioDokumen2 halamanDefinición DeseminarioFal Ska TorresBelum ada peringkat

- Curriculum VitaeDokumen5 halamanCurriculum VitaeDiego Hernando Figueroa VargasBelum ada peringkat

- Calleja, Relatos PDFDokumen256 halamanCalleja, Relatos PDFabel_decimononico100% (1)

- LMDDokumen2 halamanLMDitzeljaneth100% (1)