Estructura Seg y Paralela

Diunggah oleh

Carmen LaraHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Estructura Seg y Paralela

Diunggah oleh

Carmen LaraHak Cipta:

Format Tersedia

INSTITUTO TECNOLOGICO DE MEXICALI

MATERIA:

Arquitectura de la Computacin

TEMA: Estructura Segmentada y Paralela

ALUMNA

Ledesma Ma. Del Carmen Lara

PROFESOR:

NO CONTROL

08490570

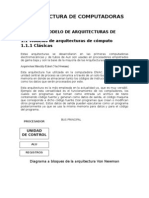

La arquitectura de computadoras es el diseo conceptual y la estructura operacional fundamental de un sistema de computadora. Es decir, es un modelo y una descripcin funcional de los requerimientos y las implementaciones de diseo para varias partes de una computadora, con especial inters en la forma en que la unidad central de proceso (CPU) trabaja internamente y accede a las direcciones de memoria. Tambin suele definirse como la forma de seleccionar e interconectar componentes de hardware para crear computadoras segn los requerimientos de funcionalidad, rendimiento y costo. Estructura segmentada Consiste en la segmentacin del procesador (pipe-line), descomponindolo en etapas para poder procesar una instruccin diferente en cada una de ellas y trabajar con varias a la vez. La arquitectura en pipeline (basada en filtros) consiste en ir transformando un flujo de datos en un proceso comprendido por varias fases secuenciales, siendo la entrada de cada una la salida. Caractersticas del proceso necesarias para poder aplicar segmentacin: Se debe poder descomponer en etapas. Es necesario que las entradas de una etapa estn determinadas nicamente por las salidas de la anterior. Cada etapa debe poder ser realizada por un circuito especfico de forma ms rpida que el conjunto del proceso. Los tiempos de ejecucin de cada etapa deben parecidos.

Aplicacin de la segmentacin:

A operadores aritmticos: Ejecutan una o varias operaciones de la ALU. Pueden ser lineales (sumas) o no lineales (divisin). En este caso suelen ser cclicos (bucles). Los procesadores actuales incluyen varias ALUS segmentadas, y cada una se puede ocupar de varias operaciones. A ejecucin de instrucciones: Suelen ser cauces lineales. Alguna de sus fases puede a su vez sub-segmentarse (uso de una ALU segmentada para la fase de ejecucin). Arquitectura Paralela. La arquitectura paralela o de lneas paralelas (pipe-line), es una tcnica en la que se descomponen un proceso secuencial en suboperaciones, y cada subproceso se ejecuta en un segmento dedicado especial que opera en forma concurrente con los otros segmentos. Una lnea puede considerarse como un conjunto de segmentos de procesamiento por el que fluye informacin binaria.

Cada segmento ejecuta un procesamiento parcial, dictado por la manera en que se divide la tarea. El resultado obtenido del clculo en cada segmento se transfiere al siguiente segmento en la lnea. El resultado final se obtiene despus de que los datos han recorrido todos los segmentos. El nombre "lnea" implica un flujo reinformacin similar a una lnea de ensamblado industrial. Es caracterstico de las lneas que varios clculos puedan estar en proceso en distintos segmentos, al mismo tiempo. La simultaneidad de los clculos es posible al asociar un registro con cada segmento en la lnea. Los registros proporcionan aislamiento entre cada segmento para que cada uno pueda operar sobre datos distintos en forma simultnea. Tal vez la manera ms simple de apreciar la arquitectura de lneas paralelas es imaginar que cada segmento consta de un registro de entrada seguido de un circuito combinatorio.

El registro contiene los datos y el circuito combinatorio ejecuta las sub operacin en el segmento particular. La salida del circuito combinacional es un segmento dado se aplica al registro de entrada del siguiente segmento. Se aplica un reloj a todos los registros despus de que se ha transcurrido un tiempo suficiente para ejecutar toda la actividad del segmento. De esta manera la informacin fluye por la lnea un paso a la vez.

Anda mungkin juga menyukai

- UF0852 - Instalación y actualización de sistemas operativosDari EverandUF0852 - Instalación y actualización de sistemas operativosPenilaian: 5 dari 5 bintang5/5 (1)

- Computadores para bases de datos. IFCT0310Dari EverandComputadores para bases de datos. IFCT0310Belum ada peringkat

- Extraer PDF de Pagina ProtegidaDokumen2 halamanExtraer PDF de Pagina ProtegidaAnthony0% (2)

- Modelos de Arquitecturas de ComputadorasDokumen7 halamanModelos de Arquitecturas de ComputadorasAmsydarkJadeBelum ada peringkat

- Arquitectura ParalelaDokumen17 halamanArquitectura ParalelamamamboBelum ada peringkat

- Arquitectura Paralela.Dokumen11 halamanArquitectura Paralela.jcliraBelum ada peringkat

- Enciso Luna Cristian Gerardo Isc 19400563Dokumen5 halamanEnciso Luna Cristian Gerardo Isc 19400563Cristian Gerardo Enciso LunaBelum ada peringkat

- Arquitectura de ComputadorasDokumen47 halamanArquitectura de ComputadorasRigoberto He HeBelum ada peringkat

- Modelos de Arquitecturas de ComputadorasDokumen4 halamanModelos de Arquitecturas de ComputadorasJose MoralesBelum ada peringkat

- Modelos de Arquitecturas de CómputoDokumen16 halamanModelos de Arquitecturas de CómputoFERNANDA JAQUELINE GONZALEZ LOPEZBelum ada peringkat

- Organización Del ProcesadorDokumen4 halamanOrganización Del ProcesadorJosé YañezBelum ada peringkat

- Arquitecturas de ComputoDokumen34 halamanArquitecturas de ComputoStephanie Martinez100% (1)

- 1 Tipos de ArquitecturasDokumen9 halaman1 Tipos de ArquitecturasKenia CruzBelum ada peringkat

- Tarea 5Dokumen11 halamanTarea 5juan mezaBelum ada peringkat

- Unidad 1 Modelo de Arquitecturas de CómputoDokumen37 halamanUnidad 1 Modelo de Arquitecturas de CómputoRosario Ramírez Rios100% (1)

- Arquitecturas Sincronas.Dokumen9 halamanArquitecturas Sincronas.XIOMARA JIMÉNEZBelum ada peringkat

- Arquitectura en ParaleloDokumen4 halamanArquitectura en ParaleloJamersBelum ada peringkat

- Organización Del ProcesadorDokumen19 halamanOrganización Del ProcesadorJepsi Avila0% (1)

- Arquitectura de ComputadorasDokumen53 halamanArquitectura de Computadorastilsma100% (3)

- Principales Estilos ArquitectónicosDokumen14 halamanPrincipales Estilos ArquitectónicosMathias RSBelum ada peringkat

- Procesamiento ParaleloDokumen7 halamanProcesamiento ParaleloJuan ThompsonBelum ada peringkat

- Analisis de Componentes CpuDokumen16 halamanAnalisis de Componentes CpuJesús Melchor Hau NohBelum ada peringkat

- Arquitectura de ComputadorasDokumen3 halamanArquitectura de ComputadorasGenesis BriceñoBelum ada peringkat

- Procesamiento en Pipeline (Segmentación)Dokumen9 halamanProcesamiento en Pipeline (Segmentación)Joskani MendozaBelum ada peringkat

- Tipos de ParalelismoDokumen8 halamanTipos de Paralelismo'Julio Mirabal'Belum ada peringkat

- Computadores SupersegmentadosDokumen13 halamanComputadores SupersegmentadoschubijonesBelum ada peringkat

- Plantilla Aqr ComputadorasDokumen4 halamanPlantilla Aqr Computadorasniki mejiaBelum ada peringkat

- Estructura de Un ProcesadorDokumen2 halamanEstructura de Un ProcesadorLUIS ZAMUDIOBelum ada peringkat

- 04) Fraga, M. (1997)Dokumen14 halaman04) Fraga, M. (1997)Julio César Sosa Yeladaqui100% (1)

- Computadoras SuperescalaresDokumen36 halamanComputadoras SuperescalaresLawiet ElleBelum ada peringkat

- Segmentacion ElectronicaDokumen1 halamanSegmentacion ElectronicaAdriana DasilvaBelum ada peringkat

- Antologia de Arquitectura de ComputadorasDokumen95 halamanAntologia de Arquitectura de ComputadorasCésar Vicente Morales MoralesBelum ada peringkat

- Tipos de ModelosDokumen19 halamanTipos de ModelosWicho FloresBelum ada peringkat

- Arquitecturas de Computo SegmentadasDokumen2 halamanArquitecturas de Computo Segmentadassergio_ramirez_76Belum ada peringkat

- Diferencia Entre Hilos y ProcesosDokumen10 halamanDiferencia Entre Hilos y ProcesosEly RamirezBelum ada peringkat

- PipelineDokumen14 halamanPipelinePaolaCarhuasIsidroBelum ada peringkat

- Sincro ComunicacionDokumen25 halamanSincro ComunicacionAnahi GODOY PONCEBelum ada peringkat

- Sincro ComunicacionDokumen25 halamanSincro ComunicacionAnahi GODOY PONCEBelum ada peringkat

- Ar QCompuDokumen49 halamanAr QCompuEduardo GantzBelum ada peringkat

- Antologia de Arquitectura de ComputadorasDokumen95 halamanAntologia de Arquitectura de ComputadorasCésar Vicente Morales Morales100% (1)

- Multiprocesamiento, Procesamiento Vectorial y Paralelotura ComputadorDokumen12 halamanMultiprocesamiento, Procesamiento Vectorial y Paralelotura ComputadorKevin EnriquezBelum ada peringkat

- Arquitectura de ComputadorasDokumen19 halamanArquitectura de ComputadorasCarrillo Zúñiga Quirino IsaíasBelum ada peringkat

- Ensayo Sobre Modelos de Arquitectura de ComputadorasDokumen5 halamanEnsayo Sobre Modelos de Arquitectura de ComputadorasAldair Cruz BautistaBelum ada peringkat

- Sincro ComunicacionDokumen29 halamanSincro ComunicacionEduardo Sanchez PiñaBelum ada peringkat

- TEMA 03 PES 2023 - Componentes, Estructura y Funcionamiento de La Unidad Central de ProcesoDokumen14 halamanTEMA 03 PES 2023 - Componentes, Estructura y Funcionamiento de La Unidad Central de Procesoleandro.lopezBelum ada peringkat

- Trabajo ParalelismoDokumen19 halamanTrabajo ParalelismoBelkys GonzalezBelum ada peringkat

- Arquitectura de ComputadorasDokumen4 halamanArquitectura de ComputadorasCampeonBelum ada peringkat

- Arquitecturas ClásicasDokumen11 halamanArquitecturas ClásicasGiovani ArellanoBelum ada peringkat

- Modelos de Arquitectura de Computo Equipo 3Dokumen11 halamanModelos de Arquitectura de Computo Equipo 3Jorge Alberto Jimenez Rosales100% (1)

- Prác.1y2 SoporteDokumen27 halamanPrác.1y2 SoporteJerykozBelum ada peringkat

- Capitulo 7 - Sistemas Multiprocesadores y ParalelosDokumen174 halamanCapitulo 7 - Sistemas Multiprocesadores y ParalelosLuis Angel ChoquehuancaBelum ada peringkat

- Jaime Francisco Ruiz Lopez Modelos de Arquitectura de ComputoDokumen3 halamanJaime Francisco Ruiz Lopez Modelos de Arquitectura de Computojaime francisco ruiz lopezBelum ada peringkat

- Analisis HilosDokumen6 halamanAnalisis HilosLUIGI davian patiño cardonaBelum ada peringkat

- Procesamiento SegmentadoDokumen2 halamanProcesamiento SegmentadoClaudia CornejoBelum ada peringkat

- Guia 1 AC 2023Dokumen10 halamanGuia 1 AC 2023Lenin RamosBelum ada peringkat

- Tarea 4 ODC - Yael MonteroDokumen4 halamanTarea 4 ODC - Yael MonteroYael MonteroBelum ada peringkat

- Guia Taller Capitulo IIIDokumen11 halamanGuia Taller Capitulo IIIFrancini BecerraBelum ada peringkat

- 4.5 Casos de EstudioDokumen5 halaman4.5 Casos de EstudioSilvio Dresser0% (1)

- Prácticas de redes de datos e industrialesDari EverandPrácticas de redes de datos e industrialesPenilaian: 4 dari 5 bintang4/5 (5)

- Reparación de instalaciones automatizadas. ELEE0109Dari EverandReparación de instalaciones automatizadas. ELEE0109Belum ada peringkat

- Generación de malla: Avances y aplicaciones en la generación de mallas de visión por computadoraDari EverandGeneración de malla: Avances y aplicaciones en la generación de mallas de visión por computadoraBelum ada peringkat

- Manual PVSOL EspDokumen173 halamanManual PVSOL EspRobin Gomez100% (1)

- WPI Log 2023.06.28 18.52.25Dokumen4 halamanWPI Log 2023.06.28 18.52.25mmejiapenduloBelum ada peringkat

- Programacion BashDokumen41 halamanProgramacion BashTobias ValderreyBelum ada peringkat

- Metodología MESSAGEDokumen17 halamanMetodología MESSAGEIvan AdvinculaBelum ada peringkat

- Test DelitosDokumen13 halamanTest DelitosnormluzBelum ada peringkat

- Actividad Integradora Obligatoria #2Dokumen4 halamanActividad Integradora Obligatoria #2Gaston Di BellaBelum ada peringkat

- Problemas Resueltos de Mecanica de Suelo PDFDokumen128 halamanProblemas Resueltos de Mecanica de Suelo PDFJairo Gonzalez0% (1)

- Evidencia 5Dokumen5 halamanEvidencia 5Alexis Espitia BernalBelum ada peringkat

- Plataforma Jitsi MeetDokumen10 halamanPlataforma Jitsi MeetRuminaBelum ada peringkat

- Decision Trees ExerciseDokumen44 halamanDecision Trees ExerciseHeriberto CruzBelum ada peringkat

- HP ML350e Gen8 Spec PDFDokumen2 halamanHP ML350e Gen8 Spec PDFEdwin UlloaBelum ada peringkat

- Diseño de Publicaciones Con Microsoft Publisher - Ficha 1Dokumen12 halamanDiseño de Publicaciones Con Microsoft Publisher - Ficha 1Antonio Barrera FierroBelum ada peringkat

- Ficha BinarioDokumen6 halamanFicha BinarioEduardo Aguado MagañaBelum ada peringkat

- Realizar Procesos de Rastreo y Sus RegistrosDokumen34 halamanRealizar Procesos de Rastreo y Sus Registrosdaniel pinzonBelum ada peringkat

- Montaje de Partes ElectrónicasDokumen1 halamanMontaje de Partes ElectrónicasClaudia LázaroBelum ada peringkat

- Ejercicio Acosta ListasDokumen2 halamanEjercicio Acosta ListasSymphony CSBelum ada peringkat

- FT-SST-092 Formato Analisis de Tareas CriticasDokumen2 halamanFT-SST-092 Formato Analisis de Tareas CriticasNubia RosalesBelum ada peringkat

- La Declaración If-Then en VBADokumen3 halamanLa Declaración If-Then en VBAAlvaro Herbas DuranBelum ada peringkat

- EPLISAC-2230109 - 400KVA 10-22.9-460 - EPLI - 19sept19Dokumen1 halamanEPLISAC-2230109 - 400KVA 10-22.9-460 - EPLI - 19sept19Boris Marcial Sanchez VasquezBelum ada peringkat

- ALLFusion BPWin 4Dokumen4 halamanALLFusion BPWin 4Daniel Gómez RBelum ada peringkat

- Examen 7 - CostoDokumen9 halamanExamen 7 - CostoYuri RodriguezBelum ada peringkat

- Formulas Word Informatica AplicadaDokumen5 halamanFormulas Word Informatica Aplicadaangel peñaBelum ada peringkat

- Evolucion Del Internet DanyDokumen9 halamanEvolucion Del Internet DanyJhony Javier Inuma TamaniBelum ada peringkat

- Creación de Equipos en SAP PMdocxDokumen14 halamanCreación de Equipos en SAP PMdocxCésarRenatoCopacondoriCuayla100% (1)

- Uso de Canarios para La Protecci N de Redes 1Dokumen6 halamanUso de Canarios para La Protecci N de Redes 1Julio BarreraBelum ada peringkat

- Plan y Programa de AuditoriaDokumen36 halamanPlan y Programa de Auditoriaoepcmatrix2011100% (2)

- Pic Ejercicio 1 05Dokumen6 halamanPic Ejercicio 1 05luis albertoBelum ada peringkat

- Artículo ConisoftDokumen15 halamanArtículo Conisoftadel_itaBelum ada peringkat

- Informatica Aplicada - Trabajo FinalDokumen8 halamanInformatica Aplicada - Trabajo FinalgreBelum ada peringkat