El Flip Flop

Diunggah oleh

Enrique RodriguezHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

El Flip Flop

Diunggah oleh

Enrique RodriguezHak Cipta:

Format Tersedia

El flip-flop J-K.

Contadores

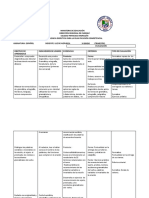

En este captulo estudiaremos uno de los elementos ms importantes, si no el ms importante, en el arsenal de los bloques fundamentales de los circuitos lgicos conocidos como secuenciales. Este elemento es el flip-flop J-K y se representa de la manera siguiente:

Como puede verse en el smbolo del flip-flop J- , este posee dos salidas complementarias Q y Q al igual que el flip-flop !-". #as caractersticas del flip-flop J- son las siguientes: $%& Cuando J'% y K'%, al ir la entrada de la terminal de relo( C $clock& de % a ) nada ocurre y el flip-flop J- retiene el estado que posea anteriormente. $*& Cuando J'% y K'), al ir la entrada C de % a ) el flip-flop J- tomar el estado Q'% independientemente del estado en el que se encontraba anteriormente. $+& Cuando J') y K'%, al ir la entrada C de % a ) el flip-flop J- tomar el estado Q') independientemente del estado en el que se encontraba anteriormente. $,& Cuando J') y K'), al ir la entrada C de % a ) el flip-flop J- tomar un estado opuesto a aqu-l en el cual se encontraba anteriormente. Esto quiere decir que si antes de la transicin en la terminal C de % a ) el flip-flop J- se encontraba en el estado Q'%, entonces tomar el estado Q') despu-s de la transicin. .simismo, si se encontraba en el estado Q') antes de la transicin, entonces tomar el estado Q'% despu-s de la transicin. /bs-rvese que la transicin de ) a % en la terminal C no produce efecto alguno en la salida 0. 1nicamente la transicin de % a ) es la que puede producir efecto alguno. 2uesto que es una cada de % a ) o una transicin negativa la que produce esta accin, este flip-flop J- es reconocido como uno accionado por una seal de reloj negativa en la terminal de 3relo(4 $cloc5&. E6isten tambi-n en el mercado flip-flops J- en los cuales la transicin que produce la accin en la terminal de salida Q es una transicin positiva de ) a % y no la transicin negativa de % a ) $precaucin: aqu no 7ay volta(es negativos involucrados&. Estos flip-flops J- son conocidos en el mercado como flipflops accionados por una seal de reloj positiva. /bs-rvese cuidadosamente que es 8nicamente una transicin en la terminal C la que puede producir accin alguna a la salida del flip-flop J- . "i la entrada en la terminal C permanece constante, cualesquier variacin en las terminales J yK no podr producir efecto alguno en la salida Q del flip-flop J- . En forma similar al flip-flop !-", el flip-flop J- tambi-n posee dos salidas complementarias, Q y Q, con la diferencia de que el flip-flop J-K no posee estados no-definidos. !epasemos con la ayuda de grficos animados usando foquitos encendidos y apagados algunas de las

caractersticas del flip-flop J- dadas arriba, empe9ando por la primera que nos dice que cuando J'% y K'% entonces al ir la entrada de la terminal de relo( C $clock& de % a ) nada ocurre y el flip-flop Jretiene el estado que posea anteriormente $en este e(emplo, el flip-flop J- se encuentra en el estado Q'%: y si se encontrara en el estado Q') tambi-n permanecera en dic7o estado sin importar el n8mero de pulsos recibidos en la entrada C&:

;eamos a7ora lo que ocurre de acuerdo a la segunda caracterstica que nos dice que cuando J'% y K'), al ir la entrada C de % a ) el flip-flop J- tomar el estado Q'% independientemente del estado en el que se encontraba anteriormente $en este caso se supondr que el flip-flop J- est inicialmente en el estado Q')&:

!epasemos a7ora lo que ocurre de acuerdo a la tercera caracterstica que nos dice que cuando J') y K'%, al ir la entrada C de % a ) el flip-flop J- tomar el estado Q') independientemente del estado en el que se encontraba anteriormente $en este caso se supondr que el flip-flop J- est inicialmente en el estado Q'%, y para mayor simplicidad visual se indicar 8nicamente el 3final4 de la secuencia de estados, entendi-ndose tras esto que la misma secuencia se volver a repetir&:

.8n ms interesante es la cuarta caracterstica que nos dice que cuando J') y K') entonces al ir la entrada C de % a ) el flip-flop J- tomar un estado opuesto a aqu-l en el cual se encontraba anteriormente:

El flip-flop J- , al igual que todos los bloques fundamentales dentro de los circuitos lgicos, se construye utili9ando funciones lgicas bsicas.

Consideramos a continuacin una configuracin 7ec7a e6clusivamente a base de flip-flops J- :

2ara anali9ar cualesquier circuito lgico que contenga flip-flops J- , la regla es e6tremadamente sencilla: Suponemos que todos los flip-flops J-K de la configuracin estn en el estado Q=0 !plicamos varias transiciones negativas en la terminal de entrada "o terminal #reloj#$ C % &acemos una lista de los estados que adquieren los flip-flops J-K de la configuracin despu's de &a(er ocurrido cada transicin )ontinuamos el procedimiento &asta que todos los flip-flops J-K de la configuracin original &a%an regresado al estado original Q=0. <eniendo lo anterior en cuenta, empe9amos suponiendo que la salida del primer flip-flop J- es Q1') y que la salida del segundo flip-flop J- es tambi-n Q2'). En otras palabras, el estado original de la configuracin es Q1Q2')). ;emos entonces en el diagrama de la configuracin cules son las entradas a cada flip-flop J- :

.l llevarse a cabo la primera transicin negativa en la terminal de entrada, el primer flip-flop J- tomar el estado Q1'%, ya que antes de la transicin estaba condicionado por las entradas J'% y K'). "imultneamente, el segundo flip-flop J- tomar el estado opuesto al que tena anteriormente, esto es, tomar el estado Q2'%, ya que antes de la transicin estaba condicionado por las entradas J') y K'). 2or lo tanto, despu-s de la primera transicin la configuracin 7abr tomado el estado Q1Q2'%%. #a situacin de la configuracin es a7ora la siguiente:

.l llevarse a cabo la segunda transicin en la terminal de entrada, el primer flip-flop J- tomar el estado Q1'), ya que antes de la segunda transicin estaba condicionado por las entradas J') y K'%. "imultneamente, el segundo flip-flip J- tomar el estado Q2'), ya que antes de la segunda transicin estaba condicionado por las entradas J') y K'%. 2or lo tanto, despu-s de la segunda transicin la configuracin toma el estado Q1Q2')). El circuito 7a regresado a su estado original. 2odemos resumir la secuencia de estados en una 3tabla4 que a primera vista podra aseme(ar una 3<abla de ;erdad4, pero que sin embargo no es tal, ya que es conceptualmente diferente. "e trata de una tabla conocida como tabla de estados y tambi-n como tabla de secuencias, la cual no nos dice cul es la salida del circuito para una cierta combinacin de entradas, sino que nos muestra cul es la secuencia de un estado del circuito al siguiente estado, en forma ordenada, de arriba 7acia aba(o:

Con el fin de evitar confusiones, se 7an dibu(ado las tablas de secuencias que sern mostradas en este libro de un modo algo diferente a como se 7an dibu(ado las <ablas de ;erdad. En una tabla de secuencias, cada 3bit4 de informacin, ya sea un 304 un 314, est encerrado en su propia 3ca(ita4, la cual podemos visuali9ar como representando un flip-flop J- o cualquier otro tipo de flip-flop. =e este modo, cada rengln en una tabla de secuencias representa en un momento dado el estado de todos los flip-flops de los que est 7ec7o el circuito, representa lo que llamamos com8nmente el estado de la mquina, simboli9ado simplemente como Q. Cualquier circuito lgico con elementos de memoria en un momento dado est completamente determinado por el estado en el que estn cada uno de sus elementos de memoria, lo cual incluye sus flip-flops !-", sus flip-flops J- , los valores que 7ay en cada una de las 3celdas4 de su memoria !.>, en fin, todos los registros y elementos de memoria de los que est 7ec7a la mquina. ? como el n8mero de estos elementos es siempre una cantidad finita, estas mquinas son conocidas com8nmente como mquinas de estado finito $finite state mac&ines&. . diferencia de la <abla de ;erdad en la cual el orden en el que estn puestos los renglones es un asunto sin trascendencia, en la tabla de secuencias el orden de los renglones tiene que ser mantenido intacto para poder leer de la misma cul ser el siguiente estado Qn+1 al cual avan9ar un contador en una transicin de estados cuando se encuentra dentro de cierto estado Qn. El avance del tiempo en una tabla de secuencias siempre debe ser ledo de arriba 7acia aba(o, y el paso de un rengln al siguiente debe ser ledo como la transicin de un estado a otro tras cada 3pulso4 en la se@al de entrada para la terminal de 3relo(4. "i continuamos aplicando transiciones negativas a la terminal de entrada reloj C, la secuencia arriba mostrada se repetir indefinidamente. Circuitos 7ec7os a base de flip-flops J- como el que acabamos de estudiar son conocidos comunmente como contadores. 2uesto que el contador estudiado requiere dos transiciones para regresar a la condicin inicial, decimos que es un contador mdulo-*. En general, si un contador requiere n transiciones para regresar a la condicin inicial, decimos que es un contador mdulo-n. El t-rmino t-cnico se 7a tomado 3prestado4 directamente del campo de las matemticas, en donde tenemos aritm-ticas finitas mdulo-n en las cuales al ir contando 7acia arriba la suma no se va acumulando indefinidamente sino que, al llegar al n8mero n, el conteo comien9a nuevamente otra ve9 de cero. $Es una lstima que aquellos estudiantes que tienen problemas para entender las aritm-ticas modulares no tengan acceso a simuladores lgicos en los cuales con circuitos como los flip-flops J- se pueden apreciar aritm-ticas modulares en accin. En otras palabras, el asunto de las aritm-ticas modulares no es un asunto meramente terico que inventaron unos matemticos ociosos que no tenan me(or cosa que 7acer. Es algo que tiene aplicacin directa en la prctica, y aqu lo estamos viendo en accin.& /bs-rvese cmo en el contador estudiado todos los flip-flops J- son activados simultneamente. <odo contador en el cual sus flip-flops J- son accionados a un mismo tiempo con una se@al de 3relo(4 com8n a sus terminales de entrada de relo( C es conocido como un contador s ncrono. E6isten tambi-n contadores en los cuales cada flip-flop J- a trav-s de su terminal de salida Q acciona la terminal C del flip-flop J- que le sigue. Este tipo de contadores recibe el nombre de contador as ncrono. Esta definicin se e6tiende 7acia cualquier otro tipo de contadores y circuitos secuenciales de todo g-nero basado no slo en el flip-flop J- sino en otros flip-flops derivados del flip-flop J- . 2or e(emplo, el siguiente circuito secuencial construdo con flip-flops del tipo + $derivable del flip-flop Jseg8n se ver en la seccin de problemas resueltos& es un contador asncrono:

mientras que el siguiente contador es un contador sncrono $obs-rvese cmo la terminal de relo( resaltada de color a9ul alimenta todas las entradas C de los flip-flops del contador&:

En la parte que corresponde a la serie de problemas resueltos para este captulo, veremos que es posible construr de una manera muy sencilla un contador (inario de conteo ascendente con el simple 7ec7o de conectar varios flip-flops J- en cascada. "i denotamos el estado de cada flip-flop J- como Q, y conectamos cuatro flip-flops J- en cascada, entonces representando el estado del contador como Q1Q2Q1Q2 y empe9ando el conteo binario desde cero, usando foquitos para representar con cada foquito encendido el estado de 314 y representando el estado de 304 con el foquito apagado la secuencia de estados que revelan al contador como un contador binario ascendente es, dinmicamente 7ablando, la siguiente:

<an fcil es construr con flip-flops J- un contador binario de conteo ascendiente como un contador binario de conteo descendiente Auevamente, para el caso de un contador binario de conteo descendiente de cuatro bits utili9ando cuatro flip-flops J- y utili9ando foquitos para visuali9ar el estado de cada flipflop, dinmicamente tendramos algo como lo siguiente:

.qu se podra ob(etar que mientras que un contador binario ascendente de cuatro bits sera el contador ideal para contar en un sistema &e,adecimal, con %B smbolos diferentes, puesto que un 7umano cuenta de die9 en die9 en el sistema decimal entonces tendra dificultades para poder 3comunicarse4 con un contador binario puro que use cuatro flip-flops J- y el cual recorra %B estados diferentes antes de regresar al estado 3cero4. #o ideal sera un contador binario cuya secuencia de estados abarque 8nicamente die9 estados diferentes en lugar de %B, o sea, un contador binario que nos d- el equivalente de un decimal codificado en cdigo binario $conocido en literatura t-cnica inglesa como contador binario

!C", del acrnimo -inar% )oded +ecimal&. #a secuencia de estados que recorrera un contador tal sera la siguiente:

Esto se puede lograr for9ando al contador binario a que cuando trate de llegar al estado 0101 dic7o contador binario sea for9ado o condicionado de alguna manera para entrar en el estado 0000. #os detalles sobre las maneras en las cuales podemos lograr esto se vern en mayor detalle en la seccin de problemas resueltos. /tro concepto clave es el de los contadores con peso. E6iste cierto tipo de contadores en los cuales si asignamos un cierto 3peso4 num-rico a cada flip-flop J- que los compone , el contador parece llevar a cabo un conteo ascendente en el sistema decimal. Consideremos un contador cuya ta(la de secuencias mostrando su secuencia natural de estados es la siguiente:

"upongamos a7ora que asignamos una unidad de peso al primer flip-flop J- con salida Q1, una unidad de peso al segundo flip-flop J- de salida Q2, dos unidades de peso al tercer flip-flop J- de salida Q# y cuatro unidades de peso al cuarto flip-flop J- de salida Q$. .l empe9ar el conteo, el estado de la configuracin es Q1Q2Q#Q$%0000, cuyo equivalente decimal es 0. =espu-s de la primera transicin, el contador toma el estado Q1Q2Q#Q$%1000. 2uesto que la salida del primer flip-flop J- es Q1%1 y a su ve9 contribuye con un peso de una unidad, el equivalente decimal del estado del contador ser 1. =espu-s de la segunda transicin, el contador toma el estado Q1Q2Q#Q$%1100. 2uesto que la salida de los dos primeros flip-flops es 1 y cada uno contribuye con un peso de una unidad, el equivalente decimal del estado del contador ser 1+1%2. =espu-s de la tercera transicin, el contador toma el estado Q1Q2Q#Q$%1010. 2uesto el primer flip-flop contribuye con un peso de una unidad y el tercer flip-flop contribuye con un peso de dos unidades, el equivalente decimal del estado del contador ser 1+2%#. Continuando el anlisis, vemos que el contador produce una cuenta decimal ascendente ordenada que llega 7asta el estado con un equivalente del n8mero decimal &. 2uesto que el peso del contador es una unidad - una unidad - dos unidades - cuatro unidades, representamos dic7o peso como 1-1'-2-$. /bs-rvese el uso de la comillla puesta en el peso correspondiente al segundo flip-flop que repite el mismo peso del primero. .7ora bien, para dise@ar un contador 7ec7o a base de flip-flops J- e6isten varias alternativas, algunas de las cuales se discuten en los problemas resueltos correspondientes a este captulo. El dise@ista deber estar alerta para determinar cul de todos producir el dise@o ptimo para lograr la secuencia deseada. =ebemos mencionar tambi-n que todo contador que produ9ca una salida sim-trica de pulsos en su 8ltimo flip-flop J- es conocido como un contador sim(trico. =e no ser as, el contador es conocido como un

contador asim(trico. $=efinimos un tren sim-trico de pulsos como aqu-l en el cual los 3unos4 y los 3ceros4 siempre ocurren de manera alternada, y cada 314 tiene la misma duracin de tiempo que un 304.& .unque el flip-flop J- es un elemento central para la construccin de contadores electrnicos, su uso no est limitado a este tipo de circuitos. #as aplicaciones de un bloque tan verstil como lo es el flip-flop Json tan amplias que estn limitadas 8nicamente por la imaginacin del dise@ista. =el flip-flop J- se pueden obtener otros componentes ms sencillos y ms especiali9ados como el flip-flop " y el flip-flop ). .qu es en donde tenemos el punto de partida para la construccin de componentes funcionales ms especiali9ados tales como el re*istro de transferencia $s&ift register&, conocido tambi-n como re*istro de despla+amiento y como re*istro de corrimiento. En este componente podemos ir metiendo varios bits de uno en uno 7asta llenarlo a su m6ima capacidad, tras lo cual podemos enviarlos (untos 7acia afuera en forma paralela o inclusive en forma serial a la ve9 que vamos reintroduciendo la informacin de nuevo al registro de despla9amiento para otro uso posterior. Esta accin la podemos esquemati9ar de la siguiente manera en un circuito lgico que podemos suponer que se 7a construdo con cuatro flip-flops J:

En este e(emplo, tras el primer 3pulso de relo(4, el 8ltimo bit correspondiente a la palabra binaria 1011 7a entrado ya en el primer flip-flip del registro de transferencia. .l siguiente 3pulso de relo(4, le toca su turno al pen8ltimo bit de la palabra binaria entrar al primer flip-flop del registro de transferencia, a la ve9 que el bit que estaba en el primer flip-flop es despla9ado 7acia el segundo flip-flop 7acia su derec7a. =e este modo, la palabra binaria va entrando al registro de despla9amiento 7asta que est completamente dentro del registro, y eventualmente empie9a a salir del registro ba(o la accin de los siguientes pulsos de relo(. 2uesto que este es un registro de transferencia en el cual la informacin binaria entra en forma serial $por la i9quierda& y sale en forma serial $por la derec7a&, este tipo de registro es conocido como de entrada-serial salida-serial o siso $serial-input serial-output&. "uponiendo que 7ayamos construdo un registro de transferencia de cuatro bits y en el cual se 7aya metido la palabra binaria %)%%, entonces si imaginamos que 7emos conectado foquitos a las salidas Q de cada flip-flop J- para representar el estado de 3encendido4 $3%4& y 3apagado4 $3)4&, entonces podemos representar con un grfico dinmico de la siguiente manera la salida serial de la palabra binaria 1011 empe9ando el bit que est ms 7acia la derec7a, lo cual de(ar al registro de transferencia en el estado 0101 $suponiendo que no le entra nada por la i9quierda& tras el primer 3pulso de relo(4, pasando al estado 0010 tras el segundo 3pulso de relo(, y as sucesivamente 7asta que los cuatro bits 7ayan salido por la derec7a y el registro de transferencia 7aya quedado completamente vaco con puros ceros $foquitos apagados& al finali9ar la secuencia de operaciones de transferencia de bit por bit:

"e pueden concebir otros tres tipos de registros de transferencia, empe9ando por el que es conocido como de entrada-serial salida-paralela o sipo $serial-input parallel-output&:

y el que es conocido como de entrada-paralela salida-serial o piso $parallel-input serial-output&:

y el que es conocido como de entrada-paralela salida-paralela o pipo $parallel-input parallel-output&:

=ise@ar un registro de transferencia con flip-flops J- o cualquier otro tipo de flip-flop es un asunto relativamente fcil. El problema general en el dise@o de circuitos secuenciales consiste en, dada una ta(la de secuencias, dise@ar un circuito lgico que pueda producir en forma ordenada dic7a tabla de secuencias, todo ba(o el control de un 3pulso de relo(4 maestro. En otros tiempos, dados los costos altsimos de un componente tan bsico como el inversor lgico A/< construdo a base de lentos relevadores electromecnicos o de componentes ms rpidos pero a8n ms costosos como los tubos electrnicos al vaco, dise@ar un circuito secuencial con la menor cantidad terica posible de componentes era un asunto de la ms alta prioridad, y para ello se invertan muc7as 7oras de estudio refinando al m6imo t-cnicas como el mapa de arnaug7 para poder obtener los dise@os ms econmicos posibles. 2ero el dramtico abaratamiento de los circuitos integrados en donde se implementan las funciones lgicas bsicas 7a 7ec7o posibles otros recursos ms prcticos de dise@o que no enfati9an tanto aquellas 7erramientas tericas de tan laborioso acceso que inclusive estaban fuera del alcance de la mayora de los t-cnicos por ser impartidas en cursos a nivel universitario en las carreras de ingeniera el-ctrica, ingeniera electrnica y ciencias computacionales. "upngase que se desea construr una mquina secuencial que sea capa9 de generar una secuencia de oc7o palabras de , bits cada palabra. "i tenemos la ta(la de secuencias a la mano, entonces todo lo que

tenemos que 7acer es proporcionar un contador binario de conteo ascendente que empe9ando con el estado Q1Q2Q#%000 suba al estado Q1Q2Q#%001 en el siguiente 3pulso de relo(4, tras esto al estado Q1Q2Q#%010 en el siguiente 3pulso de relo(4, y as sucesivamente, llevando a cabo un conteo binario ascendente. 2odemos construr fcilmente un contador de este tipo con flip-flops J- . / me(or a8n, lo podemos comprar ya 7ec7o dentro de un circuito integrado como el C"$,20 $el cual incluye dos contadores binarios ascendentes por el precio de uno&:

<odo lo que tenemos que 7acer a7ora es agregarle una memoria !/>, conectando directamente las salidas Q del contador binario a las entradas - de domicilios de la memoria !/>. El !/> tiene que tener grabada en su memoria la tabla de secuencias en forma ordenada, con la primera secuencia puesta como el dato locali9able en el primer domicilio, la segunda secuencia puesta como el dato locali9able en el segundo domicilio, y as sucesivamente. El circuito presenta as el siguiente aspecto:

<odo lo que tenemos que 7acer a7ora es aplicarle 3pulsos4 de la se@al de relo( de la duracin deseada en la terminal de entrada 3!elo(4 para ver traba(ar a nuestro secuenciador. E6iste otra alternativa de dise@o, e6plorada en la seccin de problemas resueltos de este captulo, la cual consiste en utili9ar una memoria !/> en la cual se recurre al 3truco4 de retroalimentar las entradas del !/> con sus salidas, de modo tal que cada domicilio apunte 7acia una localidad que es otro domicilio del mismo !/> % a la ve. la secuencia que sigue. =e esta manera, el abaratamiento de la microelectrnica no solo 7a 7ec7o posible que un t-cnico pueda lograr lo mismo que lo que antes requera a un ingeniero para lograr, 7a 7ec7o obsoletos muc7os de los conocimientos tan arduamente adquiridos por este ingeniero que 7oy en da nos sirven 8nicamente como e(ercicio intelectual, un e(ercicio intelectual muy interesante pero de dudosa utilidad en la prctica.

Anda mungkin juga menyukai

- Material 2018B ADM106 02 86884Dokumen43 halamanMaterial 2018B ADM106 02 86884Enrique RodriguezBelum ada peringkat

- Metodo de Montante UAGRMDokumen8 halamanMetodo de Montante UAGRMEnrique RodriguezBelum ada peringkat

- Semáforo ElectrónicoDokumen10 halamanSemáforo ElectrónicoEnrique RodriguezBelum ada peringkat

- SelanaDokumen7 halamanSelanaEnrique RodriguezBelum ada peringkat

- Borda, Guillermo A. - Tratado de Derecho Civil - Sucesiones - Tomo I PDFDokumen495 halamanBorda, Guillermo A. - Tratado de Derecho Civil - Sucesiones - Tomo I PDFJavi Clop96% (24)

- Resumen Platero y YoDokumen16 halamanResumen Platero y YoKaren A100% (1)

- ExamenDokumen3 halamanExamenJhampierEscalanteMezaBelum ada peringkat

- Resumen Hacia Una Escuela para Todos y Con TodosDokumen5 halamanResumen Hacia Una Escuela para Todos y Con TodosAnyifer AleyBelum ada peringkat

- Amparo HansenDokumen19 halamanAmparo HansenManuel CaballeroBelum ada peringkat

- RSD - Social Intelligence - Vibing by TylerDokumen6 halamanRSD - Social Intelligence - Vibing by TyleralanvergaraBelum ada peringkat

- Ensayo-Nacionalidad MexicanaDokumen5 halamanEnsayo-Nacionalidad MexicanaSofia C Sandoval Alvarez100% (2)

- AporofobiaDokumen5 halamanAporofobiaalfmotattoBelum ada peringkat

- Hivec 2 Textbook - Spanish PDFDokumen31 halamanHivec 2 Textbook - Spanish PDFluischaconserinBelum ada peringkat

- Antologia de HuerteroDokumen881 halamanAntologia de HuerteroAlvaro MOlina LOzanoBelum ada peringkat

- Revista Pórtico 2-2012Dokumen147 halamanRevista Pórtico 2-2012Sara TrejosBelum ada peringkat

- Cómo Ganarás Tu BatallaDokumen11 halamanCómo Ganarás Tu BatallaRitchieMPBelum ada peringkat

- Maria Oyente de DiosDokumen8 halamanMaria Oyente de DiosJuanjo Olmos100% (4)

- Maynade Josefina - La Vida Serena de PitagorasDokumen148 halamanMaynade Josefina - La Vida Serena de PitagorasCarlos Felipe CavalittoBelum ada peringkat

- Crecimiento EspiritualDokumen244 halamanCrecimiento Espirituallorena salas100% (1)

- Taller Silencio Administrativo FinalDokumen4 halamanTaller Silencio Administrativo Finaljuan garciaBelum ada peringkat

- U3 - Control - Sumativo - S11 - Control Evaluación ACP y AFE - Revisión Del IntentoDokumen2 halamanU3 - Control - Sumativo - S11 - Control Evaluación ACP y AFE - Revisión Del IntentoRIOLA MACARENA DE LOURDES Y��EZ BARR�ABelum ada peringkat

- Ley 582 06 Ley General Educacion NICARAGUADokumen43 halamanLey 582 06 Ley General Educacion NICARAGUAeparajon75% (4)

- Análisis de Precios-Tipos de Precios - Analisis de ComeracializacionDokumen3 halamanAnálisis de Precios-Tipos de Precios - Analisis de ComeracializacionBrian JaramilloBelum ada peringkat

- II Capac Obstetricia NST CST PDFDokumen42 halamanII Capac Obstetricia NST CST PDFJC GBBelum ada peringkat

- # 4 Dipl Inter ATDokumen26 halaman# 4 Dipl Inter ATmiguel_198819Belum ada peringkat

- Inventario de Personalidad de EysenckDokumen14 halamanInventario de Personalidad de EysenckDiana Auccasi Garibay0% (1)

- Ministerio de Educación Secuencias X Grados 2022Dokumen7 halamanMinisterio de Educación Secuencias X Grados 2022Luz ArauzBelum ada peringkat

- Seminario RecristalizaciónDokumen43 halamanSeminario RecristalizaciónAndresDuranBelum ada peringkat

- DiagnósticoDokumen4 halamanDiagnósticoAna Carmenza Romero PenaBelum ada peringkat

- Presentacion OralDokumen13 halamanPresentacion OralBoneth BerriosBelum ada peringkat

- Tema 4 La Ambivalencia y El Balance DecisionalDokumen11 halamanTema 4 La Ambivalencia y El Balance DecisionalAngélica Gutierrez100% (1)

- La Condición Humana y SocialDokumen3 halamanLa Condición Humana y SocialAdan Arellanes VelascoBelum ada peringkat

- Mapa Conceptual de La Ciencia SocialDokumen2 halamanMapa Conceptual de La Ciencia SocialJhonatan ChoperenaBelum ada peringkat

- Ejemplo de TFMDokumen54 halamanEjemplo de TFMThonny E Mendoza50% (2)