New WWWW FFF

Diunggah oleh

priyasrinivasan24Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

New WWWW FFF

Diunggah oleh

priyasrinivasan24Hak Cipta:

Format Tersedia

EC2307

COMMUNICATION SYSTEMS LABORATORY

SYLLABUS

EC2307 COMMUNICATION SYSTEMS LABORATORY LTPC0032

S.NO

1.

NAME OF THE EXPERIMENT

AMPLITUDE MODULATION AND DEMODULATION

2.

FREQUENCY MODULATION AND DEMODULATION PULSE MODULATION PAM / PWM / PPM

3.

4.

PULSE CODE MODULATION

5.

DELTA MODULATION, ADAPTIVE DELTA MODULATION

6.

DIGITAL MODULATION & DEMODULATION ASK, PSK, QPSK, FSK MATLAB)

(HARDWARE &

7.

DESIGNING, ASSEMBLING AND TESTING OF PRE-EMPHASIS / DE-EMPHASIS CIRCUITS

8.

PLL AND FREQUENCY SYNTHESIZER

9.

LINE CODING

10.

ERROR CONTROL CODING USING MATLAB

11.

SAMPLING & TIME DIVISION MULTIPLEXING

12.

FREQUENCY DIVISION MULTIPLEXING

TOTAL= 45 PERIOD

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY JAYAM COLLEGE OF ENGINEERING & TECHNOLOGY DEPT OF ELECTRONICS AND COMMUNICATION ENGINEERING

B. E. - ELECTRONICS AND COMMUNICATION ENGINEERING (R 2008) EC2307 - COMMUNICATION SYSTEMS LABORATORY REQUIREMENT FOR A BATCH OF 30 STUDENTS

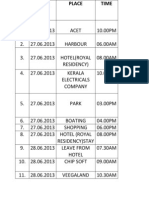

S.No. 1 2 3 4 5 6 7 8 9 10 11 12 CRO - 20 MHz

Description of Equipment

Quantity required 15 15 15 10 2 2 2 2 2 2 2 5 user license

Quantity available 12 15 15 10 1 1 2 2 1 2 1 5

Deficiency % 33% 50% 50% -

Function Generator (1 MHz ) Power Supply ( 0 - 30 Volts Variable ) ( IC Power supply) Bread Board AM Transceiver Kit FM Transceiver Kit PAM,PPM,PWM Trainer Kits PCM /DM/ ADM Trainer Kit Line Coding & Decoding Kit ASK,PSK,FSK,QPSK Trainer Kits Sampling & TDM trainer kit Mat lab (Communication tool box)

Consumables 13 14 15 16 17 18 19 IC 565,566,567,741 BC 107 BFW10 OA79 Resistors ( Various ranges ) Capacitors ( Various ranges ) Decade Inductance box Minimum of 50 No. each 50 50 50 50 50 50 50 -

HOD/ECE

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY EC2307 - COMMUNICATION SYSTEMS LABORATORY

LIST OF EXPERIMENTS:

S.NO

1. 2. 3. 4. 5. 6.

NAME OF THE EXPERIMENT

AMPLITUDE MODULATION AND DEMODULATION FREQUENCY MODULATION AND DEMODULATION PULSE MODULATION PAM / PWM / PPM PULSE CODE MODULATION DELTA MODULATION, ADAPTIVE DELTA MODULATION DIGITAL MODULATION & DEMODULATION ASK, PSK, QPSK, FSK MATLAB) (HARDWARE &

7. 8. 9. 10. 11. 12.

DESIGNING, ASSEMBLING AND TESTING OF PRE-EMPHASIS / DE-EMPHASIS CIRCUITS PLL AND FREQUENCY SYNTHESIZER LINE CODING ERROR CONTROL CODING USING MATLAB SAMPLING & TIME DIVISION MULTIPLEXING FREQUENCY DIVISION MULTIPLEXING ADDITIONAL EXPERIMENTS

1.

2. DESIGN EXPERIMENTS 1. 2.

OPEN ENDED EXPERIMENTS 1. 2. 3.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 1 DATE: AIM:

AMPLITUDE MODULATION AND DEMODULATION

To generate amplitude modulated wave and to demodulate the modulated wave using envelope detector. APPARATUS REQUIRED: S.No 1. 2. 3. 4. 5. 6. Name of the apparatus Amplitude modulation transmitter kit (ACL-01) Amplitude modulation receiver kit (ACL-02) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 1 As Required Dual mode

THEORY: Amplitude modulation: Modulation is defined as the process by which some characteristics of a carrier signal is varied in accordance with a modulating signal. The base band signal is referred to as the modulating signal and the output of the modulation process is called as the modulation signal. Let us consider modulating signal, Vm and carrier signal, Vc then the modulation index can be calculated as: a) when Vm< Vc ,modulation index , ma is said to be Under modulation b) when Vm=Vc, modulation index , ma is said to be Critical modulation c) when Vm>Vc, modulation index ,ma is said to be Over modulation Amplitude demodulation: The process of detection provides a means of recovering the modulating signal from carrier signal. Demodulation is the reverse process of modulation.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram: Amplitude modulation & demodulation :

Kit diagram:

Procedure: 1. Refer to block diagram and Carry out the following connections. 2. Keep all the switch faults in OFF position. 3. Connect SINE OUT post of function generator section (ACL-01) to the I/p of Balance Modulator1 (ACL-01) SIGNAL IN Post. 4. To connect o/p of VCO (ACL-01) RF OUT post to the input of Balance modulator 1 CARRIER IN post (ACL-01). 5. Connect the power supply with proper polarity to the kit ACL-01 & ACL-02, while connecting

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307 ensure that the power supply is OFF. 6. Keep switch SW1 towards 1-10 KHz position.

COMMUNICATION SYSTEMS LABORATORY

7. Keep Out post LEVEL about 0.5Vpp; FREQ. About 1 KHz. 8. Keep switch SW2 towards 500 KHz position. 9. Keep RF out LEVEL about 1 Vpp; FREQ. about 450 KHz, Switch on 500 KHz. 10. Plot the graph as per output and input wave form.

Tabular Column:

INPUT SIGNAL: CARRIER SIGNAL: M= VMAX-VMIN VMax+VMIN

S.No

Given signal

Type of the signal

Amplitude in (volt)

FMAX FMIN

=

Time period in (ms)

UNDER MODULATION

Vm<Vc, m<1

MODULATED SIGNAL CRITICAL MODULATION

=

FMAX FMIN FMAX

Vm=Vc m=1

OVER MODULATION

Vm>Vc m>1

2 DEMODULATED SIGNAL

FMIN FMAX FMIN

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Waveform:

Result: Thus the AM modulator and Demodulator circuit is constructed and tested. From the plotted waveform of modulated signal on graph paper , modulation index values for specific readings are: 1. when Vm<Vc,modulation index ,ma=.. 2. when Vm=Vc,modulation index ,ma=.. 3. when Vm>Vc,modulation index ,ma=..

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 2 DATE: AIM:

FREQUENCY MODULATION AND DEMODULATION

To generate Frequency modulated wave using varactor diode and to plot the demodulation characteristics of the fm demodulator using Foster-Seeley Demodulator. APPARATUS REQUIRED: S.No 1. 2. 3. 4. 5. 6. Name of the apparatus Frequency modulation transmitter kit (ACL-03) Frequency modulation receiver kit (ACL-04) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 1 As Required Dual mode

THEORY: Frequency modulation Generation: In practice, there are two main methods used to generate the FM: Direct method: The most common device with variable reactance is the Varactor or Varicap, which is a particular diode whose capacity varies as a function of the reverse bias voltage. The frequency of the carrier is established with AFC circuits (Automatic Frequency Control) or PLL (Phase Locked Loop). Indirect method: In this case, FM is done by Phase Modulation, after the modulating signal has been integrated. In the phase modulator the carrier can be generated by a quartz oscillator and so its frequency stabilization is easier. Frequency demodulation: Demodulation is the reverse process of modulation. For the detection of the frequency modulated signals, different circuit solutions have been used : 1. Travis discrimination 2. Foster-seeley discriminator 3. Ratio discriminator 4. Quadrature detector 5. PLL detector 6. Detuned resonance detector 7. Amplitude limiter:

R.M.SURYA ,AP/ECE JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram: Frequency modulation & demodulation :

FUNCTION GENERATOR

LOCAL OSCILLATOR

LIMITER

FOSTER SEELEY DETECTOR

MIXER

Kit diagram:

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307 Procedure:

COMMUNICATION SYSTEMS LABORATORY

1. Refer to block diagram and Carry out the following connections. 2. Keep all the switch faults in OFF position. 3. Connect the o/p of function generator OUT post to the modulation IN post frequency modulator. 4. Connect the oscilloscope to the output of the modulator FM/RF OUT. 5. To observe the FM at lower frequencies apply Sine wave of 1KHz and 1Vpp from external function generator to MOD IN post of onboard Function Generator and keep JP4 at 10-100KHz position and adjust the frequency at about 20-25KHz and output level of Function generator at 2Vpp. 6. Connect the oscilloscope across post FS OUT. If the central frequency of the discriminator and the carrier frequency of the FM signal and local oscillator frequency coincide, you obtain demodulated signal of FOSTERSEELEY DETECTOR . 7. Connect the FS OUT to the IN post of LOW PASS FILTER. Note that the demodulated signal has null continuous component. Tabular Column:

INPUT SIGNAL: MODULATING FREQUENCY:

of

S.no

Given signal

Frequency deviation (DF) (Fmax Fmin)/2

FMAX

Modulation index mf = DF/f

Amplitude in (volt)

Time period in (ms)

MODULATED SIGNAL FMIN FMAX DEMODULATED SIGNAL

FMIN

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Waveform:

Result: Thus the FM modulator and Demodulator circuit is constructed and tested. From the plotted waveform of modulated signal on graph paper, modulation index values and Frequency deviation for specific readings are calculated.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 3a DATE: AIM:

PULSE MODULATION PULSE AMPLITUDE MODULATION

To generate pulse amplitude modulated wave and demodulated wave. APPARATUS REQUIRED: S.No 1. 3. 4. 5. 6. Name of the apparatus Pulse modulation transreceiver kit (DCL-08) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 As Required Single mode

THEORY: Pulse amplitude modulation: In Pulse Amplitude Modulation, the signal is sampled at regular intervals and the amplitude of each sample is made proportional to the amplitude of the signal at that instant of sampling. This amplitude of each sample is hold for the sample duration to make pulses flat top. The Pulse Amplitude Demodulator consists of Active Low Pass Butterworth filter. It filters out the sampling frequency and their harmonics from the modulated signal and recovers the base band by integrated action. In pulse amplitude modulation (PAM), the amplitude of a carrier consisting of a periodic train of rectangular pulses is varied in proportion with the sample values of a message signal. In this type of modulation, the pulse duration is held constant. By making the amplitude of each rectangular pulse the same as that of the message signal at the leading edge of the pulse. If the top of the samples vary as per the message signal variations, it is due to natural sampling. Instead, if the top of the samples remain constant, then it is called as flat top sampling. Flat-top sampling introduces amplitude distortion and delay. This distortion is called aperture effect. This effect is reduced by employing equalizer. The equalizer has the effect of decreasing the in-band loss of the reconstruction filter, as the frequency increases in such a manner as to compensate for the aperture effect.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

SAMPLING FREQUENCY FUNCTION GENERATOR PAM MODULATOR 4TH ORDER FILTER

Kit diagram:

Procedure: 1. Refer to Block Diagram & Carry out the following connections and Switch settings. 2. Connect the power supply with the proper polarity to the Kit DCL-08 and switch ON. 3. Keep all the switch faults in OFF position. 4. Select 16 KHz sampling frequency by jumper JP1. 5. Connect PAM OUT post to AMP IN post. 6. Connect AMP OUT post to FIL IN post. 7. Keep the amplifier gain control potentiometer P5 to maximum completely clockwise. 8. Observe the Amplified signal at AMP OUT Post. 9. Observe the Pulse Amplitude Demodulated signal at FIL OUT, which is same as the input signal. 10. Repeat the experiment for different input signal and sampling frequencies.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

Waveform:

Result: Thus pulse amplitude modulation and demodulation circuits were constructed and its output waveforms were observed.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 3b DATE: AIM:

PULSE MODULATION PULSE WIDTH MODULATION

To generate pulse width modulated wave and demodulated wave. APPARATUS REQUIRED: S.No 1. 3. 4. 5. 6. Name of the apparatus Pulse modulation transreceiver kit (DCL-08) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 As Required Single mode

THEORY: Pulse Width modulation: This technique of modulation controls the variation of duty cycle of the square wave the amplitude variation of the modulation signal is reflected in the ON period variation of square wave. Hence, it is a technique of V to T conversion. Pulse width demodulation: The input signal is Pulse Width Modulated, so the ON time of the signal is changing according to the modulating signal. In this demodulation technique during the ON time of PWM signal one counter is enabled. At the end of ON time, counter gives a particular count, which directly corresponds to the amplitude of input signal. Then this count is fed to a DAC. The output of DAC corresponds to the amplitude of input signal. Thus train of varying pulse widths gives varying count values and accordingly DAC give outputs, which is directly proportional to amplitude of input signal. This is then filtered to get original signal. Thus at the output we get the original modulating signal extracted from PWM wave.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

CLOCK 4TH ORDER FILTER

FUNCTION GENERATOR

PWM MODULATOR

Kit diagram:

Procedure: 1. Refer to Block Diagram & Carry out the following connections and Switch settings. 2. Connect the power supply with the proper polarity to the Kit DCL-08 and switch ON. 3. Keep all the switch faults in OFF position. 4. Put jumper JP3 to 2nd position 5. Connect the 1 KHz sine wave signal generated onboard 1 KHz post to PAM IN Post. 6. Observe the Pulse Width Demodulated signal at FIL OUT, which is same as the input signal. 7. Repeat the experiment for different input signal and sampling frequencies.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

Waveform:

Result: Thus pulse width modulation and demodulation circuits were constructed and its output waveforms were observed.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 3c DATE: AIM:

PULSE MODULATION PULSE POSITION MODULATION

To generate pulse position modulated wave and demodulated wave. APPARATUS REQUIRED: S.No 1. 3. 4. 5. 6. Name of the apparatus Pulse modulation transreceiver kit (DCL-08) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 As Required Single mode

THEORY: Pulse position modulation: The position of the TTL pulse is changed on time scale according to the variation of input modulating signal amplitude, Width of the pulses and Amplitude of the pulses remain same. Pulse position demodulation: This pulse position modulated signal is converted into PWM pulse form using Monostable multivibrator. This signal is then demodulated using the same technique of PWM demodulation. In this demodulation technique during the ON time of PWM signal one counter is enabled. At the end of ON time, counter gives a particular count, which directly corresponds to the amplitude of input signal. Then this count is fed to a DAC. The output of DAC corresponds to the amplitude of input signal. Thus train of varying pulse widths gives varying count values and accordingly DAC gives outputs, which is directly proportional to amplitude of input signal. This is then filtered to get original signal. Thus at the output we get the original modulating signal extracted from PWM wave.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

CLOCK

FUNCTION GENERATOR

PPM MODULATOR

4TH ORDER FILTER

Kit diagram:

Procedure: 1. Refer to Block Diagram & Carry out the following connections and Switch settings. 2. Connect the power supply with the proper polarity to the Kit DCL-08 and switch ON. 3. Keep all the switch faults in OFF position. 4. Put jumper JP3 to 2nd position 5. Connect the 1 KHz sine wave signal generated onboard 1 KHz post to PAM IN Post. 6. Observe the Pulse Width Demodulated signal at FIL OUT, which is same as the input signal. 7. Repeat the experiment for different input signal and sampling frequencies.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

Waveform:

Result: Thus pulse position modulation and demodulation circuits were constructed and its output waveforms were observed.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 4 DATE: AIM:

PULSE CODE MODULATION

To generate pulse code modulated wave and demodulated wave. APPARATUS REQUIRED: S.No 1. 2. 3. 4. 5. 6. Name of the apparatus Pulse code modulation transmitter kit (DCL-03) Pulse code modulation receiver kit (DCL-04) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 1 As Required Single mode

THEORY: Pulse code modulation and demodulation: The sine waves (analog signal) of frequency 500Hz and 1 KHz and DC Signal DC1 and DC2 whose amplitude can be varied accordingly are generated onboard on DCL-03. These signals are fed to the input of the Sampling logic CH0 & CH1 and their samples are multiplexed by interleaving them properly in their assigned time slots. The Crystal oscillator generates a clock of 6.4MHz from which all the transmitter data and timing signals are derived. For fast mode operation the transmitter clock is 240KHz, and Sampling clock is 16KHz.For slow mode operation depending on jumper position the transmitter clock is 1.23Hz or 0.6Hz and sampling clock is 0.088Hz or 0.044Hz i.e. the sampling rate per channel is 11 or 22 seconds and serial data transmission rate is 813 milliseconds or 1.6 seconds. The multiplexed data is Pulse Code Modulated before transmission. At the receiver after the Pulse Code Demodulation, the recovered data multiplexed data is sent to Demultiplexing logic. The two demultiplexed samples are fed to Reconstruction unit which

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

consists of 4th order Low Pass Butterworth Filter, where frequency components are filtered out to recover the original base band signal at the receiver output CH0 and CH1.

Block Diagram: Pulse code modulation:

Pulse code demodulation:

Kit diagram:

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Procedure: 1. Refer the Block Diagram & Carry out the following connections. 2. Connect power supply in polarity to the kits DCL-03 and DCL-04 and switch ON. 3. Connect sine wave frequency 500Hz and 1 KHz to the input CH0 and CH1 of the sample and hold logic. 4. Connect OUT 0 to CH0 IN & OUT 1 to CH1 IN. 5. Set the speed selection switch SW1 to FAST mode. 6. Select parity selection switch to NONE mode on both the kit DCL-03 and DCL-04 as shown in switch setting diagram. 7. Connect TXDATA, TXCLK and TXSYNC of the transmitter section DCL-03 to the corresponding RXDATA, RXCLK, and RXSYNC of the receiver section DCL-04. 8. Connect posts DAC OUT to IN post of demultiplexed section on DCL-04. 9. Repeat the above experiment with DC Signal at the inputs of the Channel CH0 and CH1. 10. Connect ground points of both the kits with the help of connecting chord provided during all the experiments. Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Waveform:

Result: Thus pulse code modulation and demodulation circuits were constructed and its output waveforms were observed.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 5a DATE: AIM:

DELTA MODULATION

To generate Delta modulated wave and demodulated wave. APPARATUS REQUIRED: S.No 1. 3. 4. 5. 6. Name of the apparatus Delta modulation transreceiver kit (DCL-07) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 As Required Single mode

THEORY: Delta modulation: Delta modulation is the differential pulse code modulation scheme in which the difference signal is encoded into just a single bit. In digital modulation system, the analog signal is sampled and digitally coded. This code represents the sampled amplitude of the analog signal. The digital signal is sent to the receiver through any channel in serial form. At the receiver the digital signal is decoded and filtered to get reconstructed analog signal. Sufficient number of samples are required to allow the analog signal to be reconstructed accurately. Delta modulation is a process of converting analog signal into one bit code, means only one bit is sent per sample. This bit indicates whether the signal is larger or smaller than the previous samples. Delta demodulator: The Delta Demodulator consists of a D-flip/flop, followed by an integrator and a 2nd and 4th order low pass Butterworth filter. The Delta Demodulator receives the data stream from D-flip/flop of Delta Modulator. It latches this data at every rising edge of receiver clock. This data stream is then fed to integrator; its output tries to follow the analog signal in ramp fashion and hence is a good approximation of the signal itself.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

DIGITAL SAMPLER FUNCTION GENERATOR INTEGRATOR 1AND 3 FF 4TH ORDER FILTER

Kit diagram:

Procedure: 1. 2. 3. 4. 5. Refer to Block Diagram & Carry out the following connections and Switch settings. Connect the power supply with the proper polarity to the Kit DCL-07 and switch ON. Keep all the switch faults in OFF position. Connect output of buffer post OUT to Digital Sampler input post IN1 . Then select clock rate of 8 KHz by pressing switch S1 selected clock is indicated by LED glow. 6. Keep Switch S2 in Delta position. 7. Connect output of Digital Sampler post OUT to input post IN of Integrator 1. 8. Observe the Delta modulated output at output of Digital Sampler post OUT and compare it with the clock rate selected. It is half the frequency of clock rate selected 9. Connect output of Demodulator post OUT to the input of Integrator 3 post IN 10. Keep Switch S4 in high position. 11. Connect output of Integrator 3 post OUT to the input of output buffer post IN .

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

Waveform:

Result: Thus Delta modulation and demodulation were constructed and its output waveforms were observed.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 5b DATE: AIM:

ADAPTIVE DELTA MODULATION

To generate Adaptive delta modulated wave and demodulated wave. APPARATUS REQUIRED: S.No 1. 3. 4. 5. 6. Name of the apparatus Delta modulation transreceiver kit (DCL-07) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 As Required Single mode

THEORY: Adaptive delta modulation:

Delta Modulation system is unable to chase the rapidly changing information of the analog signal, which gives rise to distortion and poor quality reception. The problem can be overcome by increasing the integrator gain. Adaptive Delta Modulation is a variation of Delta Modulation, which offers relief from disadvantage of DM by adopting the step size to accommodate changing signal conditions. If the input signal is large, step is cause to increase, thereby reducing slope overload effects. A Delta Modulator consists of a comparator in the forward path and an integrator in the feedback path of a simple control loop. The usual implementation involves a continuously variable slope Delta (CVSD). There are varieties of IC's for CVSD encoding and decoding in today's semiconductor market. CVSD produces equal quality at 32Kbit/sec. In CVSD Decoder CVSD mod output is fed to the input of comparator. Adaptive Delta Modulation do not change step size on a pulse-to pulse basis, but changes are made much more slowly, such slow control is referred to as syllabic.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

DIGITAL SAMPLER FUNCTION GENERATOR INTEGRATOR 1AND 3 FF 4TH ORDER FILTER

Kit diagram:

1. 2. 3. 4. 5. 6.

Procedure: Refer to Block Diagram & Carry out the following connections and Switch settings. Connect the power supply with the proper polarity to the Kit DCL-07 and switch ON. Keep all the switch faults in OFF position. Connect output of buffer post OUT to Digital Sampler input post IN1 . Then select clock rate of 8 KHz by pressing switch S1 selected clock is indicated by LED glow. 7. Keep Switch S3 in Low position. 8. Connect output of Digital Sampler post OUT to input post IN of Integrator 2. 9. Connect output of Demodulator post OUT to the input of Integrator 3 post IN. 10. Keep Switch S4 in LOW position. 11. Connect output of Integrator 3 post OUT to the input of output buffer post IN. 12. Connect output of output buffer post OUT to the input of 2nd order filter post IN. 13. Connect output of 2nd order filter post OUT to the input of 4th order filter post IN 14. Observe output at digital sampler output post

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

Waveform:

Result: Thus Adaptive delta modulations were constructed and its output waveforms were observed.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 6a DATE: AIM:

DIGITAL MODULATION & DEMODULATION ASK(HARDWARE)

To generate Carrier Modulation Techniques by Amplitude Shift Keying. APPARATUS REQUIRED: S.No 1. 2. 3. 4. 5. 6. Name of the apparatus Data conditioning and carrier modulation kit(DCL-05) Data conditioning and carrier demodulation kit (DCL-06) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 1 As Required Dual mode

THEORY: Amplitude shift keying: Carrier modulation is a technique by which digital data is made to modulate a continuous wave (sine wave) carrier. For all types of carrier modulation, the carrier frequency should be at least 2 times that of modulating frequency. In Amplitude shift keying, the carrier is transmitted when the modulating data is `one' and the carrier is rejected from transmission when the data is `zero'. In DCL-05 the ASK Modulators employs an Analog Multiplexer as a modulating switch, which can switch between carrier and ground, for every `one' to `zero' transitions. The carrier frequency chosen for ASK modulation is 1 MHz. ASK DEMODULATOR block on DCL-06 employs an envelope detector to recover the data from the modulated carrier. The ASK modulated input is fed to the half wave rectifier. The rectified input is fed to the filter, where the original data is recovered. The threshold detector is used to recover the original amplitude levels of the data. So whenever the sine wave is transmitted, the detector identifies it as a `one' and whenever the carrier is absent, the detector identifies it as a `zero'.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

Kit diagram:

Procedure: 1. Refer the block diagram and carryout the following connections and switch settings. 2. Connect power supply in proper polarity to the kits DCL-05 and DCL-06 and switch it ON. 3. Connect clock and data generated ON DCL-05 to coding clock in and DATA INPUT respectively by means of connecting chords provided. 4. Connect NRZ-L data input to control input of carrier modulated logic. 5. ASK=>connect carrier component SIN2 to INPUT1 and GROUND TO INPUT2 of the carrier modulator logic. 6. Connect ASK modulated signal modulator output on DCL-05 to ASK of the ASK demodulator on DCL-05.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

Waveform:

Result: Thus the techniques of ASK modulation and demodulation is performed and the graph is plotted.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 6b DATE: AIM:

DIGITAL MODULATION & DEMODULATION FSK

To generate Carrier Modulation Techniques by Frequency Shift Keying. APPARATUS REQUIRED: S.No 1. 2. 3. 4. 5. 6. Name of the apparatus Data conditioning and carrier modulation kit(DCL-05) Data conditioning and carrier demodulation kit (DCL-06) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 1 As Required Dual mode

THEORY: Frequency shift keying: Carrier modulation is a technique by which digital data is made to modulate a continuous wave (sine wave) carrier. For all types of carrier modulation, the carrier frequency should be at least 2 times that of modulating frequency. In Frequency Shift keying

modulation techniques, the modulated output shifts between two frequencies for all `one' (mark) to `zero' (space) transitions. The carrier frequency chosen for FSK modulation are 500 KHz and 1MHz. Note that the above frequencies are greater than twice the modulating frequency. Note that the FSK may be thought of as an FM system in which the carrier frequency is midway between the mark and space frequencies, and modulation is by a square wave. CARRIER GENERATOR block on DCL-05 generates the carrier waves 500 KHz and 1 MHz, which are available at SIN1 and SIN2 post. The FSK modulator is also built around the 2 to 1 Analog Multiplexer, which switches between the 500KHz and 1MHz signals for all 'one' to `zero' transitions.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

Kit diagram:

Procedure: 1. Refer the block diagram and carryout the following connections and switch settings. 2. Connect power supply in proper polarity to the kits DCL-05 and DCL-06 and switch it ON. 3. Connect clock and data generated ON DCL-05 to coding clock in and DATA INPUT respectively by means of connecting chords provided. 4. Connect NRZ-L data input to control input of carrier modulated logic. 5. ASK=>connect carrier component SIN2 to INPUT1 and GROUND TO INPUT2 of the carrier modulator logic. 6. Connect FSK modulated signal modulator output on DCL-05 to FSK of the FSK demodulator on DCL-05.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

Waveform:

Result: Thus the techniques of FSK modulation and demodulation is performed and the graph is plotted.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 6c DATE: AIM:

DIGITAL MODULATION & DEMODULATION PSK

To generate Carrier Modulation Techniques by Phase Shift Keying. APPARATUS REQUIRED: S.No 1. 2. 3. 4. 5. 6. Name of the apparatus Data conditioning and carrier modulation kit(DCL-05) Data conditioning and carrier demodulation kit (DCL-06) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply Quantity 1 1 1 1 As Required Dual mode

THEORY: Phase shift keying:

Phase-shift keying (PSK) is a digital modulation scheme that conveys data by changing, or modulating, the phase of a reference signal (the carrier wave). Any digital modulation scheme uses a finite number of distinct signals to represent digital data. PSK uses a finite number of phases, each assigned a unique pattern of binary bits. Usually, each phase encodes an equal number of bits. Each pattern of bits forms the symbol that is represented by the particular phase. The demodulator, which is designed specifically for the symbol-set used by the modulator, determines the phase of the received signal and maps it back to the symbol it represents, thus recovering the original data. This requires the receiver to be able to compare the phase of the received signal to a reference signal such a system is termed coherent (and referred to as CPSK).

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

Kit diagram:

Procedure: 1. Refer the block diagram and carryout the following connections and switch settings. 2. Connect power supply in proper polarity to the kits DCL-05 and DCL-06 and switch it ON. 3. Connect clock and data generated ON DCL-05 to coding clock in and DATA INPUT respectively by means of connecting chords provided. 4. Connect NRZ-L data input to control input of carrier modulated logic. 5. PSK=>connect carrier component SIN2 to INPUT1 and GROUND TO INPUT2 of the carrier modulator logic. 6. Connect PSK modulated signal modulator output on DCL-05 to PSK of the PSK demodulator on DCL-05.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

Waveform:

Result: Thus the technique of PSK modulation and demodulation is performed and the graph is plotted.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 6d DATE: AIM:

DIGITAL MODULATION & DEMODULATION QPSK

To generate Carrier Modulation Techniques by Quadrature phase Shift Keying. APPARATUS REQUIRED: S.No 1. Name of the apparatus Quantity

Data conditioning and carrier modulation kit(ADCL- 1 02) Data conditioning and carrier demodulation kit (ADCL-03) Cathode Ray Oscilloscope Connecting probes Patch chords Power Supply 1 1 1 As Required Dual mode

2. 3. 4. 5. 6.

THEORY: Quadrature Phase shift keying: QPSK is another form of angle-modulated, constant-amplitude digital modulation. It is an M-ary encoding technique where M=4. with QPSK four output phases are possible for a single carrier frequency. Two bits (a dibit) are clocked into the bit splitter. After both bits have been serially inputted, they are simultaneously parallel outputted. One bit is directed to the I channel and the other to the Q channel. The I bit modulates a carrier that is in phase with the reference oscillator and the Q bit modulates a carrier that is 900 out of phase with the reference carrier. QPSK modulator is two BPSK modulators combined in parallel.The input QPSK signal is given to the I and Q product detectors and the carrier recovery circuit. The carrier recovery circuit produces the original transmit carrier oscillator signal. The recovered carrier must be frequency and phase coherent with the transmit reference carrier. The QPSK signal is demodulated in the I and Q product detectors, which generate the original I and Q data bits. The output of the product detectors are fed to the bit combining circuit, where they are converted from parallel I and Q data channels to a single binary output data stream.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

Kit diagram:

Procedure: 1. Refer to the block diagram & carry out the following connections and switch settings 2. Connect power supply in proper polarity to the kit. 3. Select data pattern of simulated data using switch SW1 4. Connect SDATA generated in DATA IN to NRZ-L CODER. 5. Connect the coded data NRZ-L DATA to the DATA IN of the DIBIT ONVERSION 6. Connect SCLOCK to CLK IN of DIBIT CONVERSION

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

7. Connect the dibit data I bit to control input C1 of CARRIER MODULATION 8. Connect the dibit data Q bit to control input C2 of CARRIER MODULATION 9. Connect the carrier component to input of CARRIER MODULATOR as follows a. SIN1 to IN1 b. SIN2 to IN2 c. SIN3 to IN3 d. SIN4 to IN4 10. Connect the QPSK MOD OUT to MOD IN of the QPSK DEMODULATOR 11. Observe the output of the first squarer at the SQUARER1 12. Observe the output of the second squarer at SQUARER2 13. Observe the four sampling clocks at the output of the SAMPLING CLOCK GENERATOR 14. Observe the output of ADDER1 15. Observe the output of ADDER2 16. Observe the recovered data bit I at the output of the ENVELOPE DETECTOR 1 17. Observe the recovered data bit Q at the output of the ENVELOPE DETECTOR 2 18. Connect I BIT, Q BIT & CLK OUT of QPSK demodulator to I BIT IN & Q BIT IN & CLK IN posts of data decoder respectively. 19. Observe the recovered NRZ-L data from I and Q bits at the output of the DATA DECODER 20. Use RESET switch if delay occurs at data out post and use PHASE SYNC switch if there is mismatch in the patterns of data at output with respect to the transmitter data.

Tabular column:

S.NO 1 2 3 4

Given Signal Message Signal Carrier Signal Modulated Signal Demodulated Signal

Amplitude(volts)

Time period (ms)

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Waveform:

Result: Thus the techniques of QPSK modulation and demodulation are performed and the graph is plotted.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 7a DATE: AIM:

DESIGNING, ASSEMBLING AND TESTING OF PREEMPHASIS CIRCUIT

To construct and verify pre-emphasis network using active & passive components and plot the waveform. APPARATUS REQUIRED: S.No 1. 2. Name of the Component Transistor Resistors Range BC107 75K 22K,15K,1K,1.2K 3. Capacitor 470pF 0.1F 4. 5. 6. Function generator CRO Bread board (0-1)MHz (0-20)MHz Quantity 1 2 Each 1 1 1 1 1 1

THEORY: Pre-emphasis: Frequencies contain in human speech mostly occupy the region from 100 to 10,000 Hz, but most of the power is contained in the region of 500 Hz for men and 800 Hz for women. Common voice characteristics emit low frequencies higher in amplitude than higher frequencies. The problem is that in FM system the noise output of the receiver increases linearly with the frequency, which means that the signal to noise ratio becomes poorer as the modulating frequency increases. Also, noise can make radio reception less readable and unpleasant. This noise is greatest in frequencies above 3KHz.The high frequency noise causes interference to the already weak high frequency voice. To reduce the effect of this noise and ensure an even power spread of audio frequencies, Pre emphasis is used at the Transmitter side.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

A pre-emphasis network in the transmitter accentuates the audio frequencies above 3 KHz, so providing the higher average deviation across the voice spectrum, thus Improving the signal to noise ratio. Circuit diagram: Using active component:

Using passive components:

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Procedure: 1. Connections are made as per the circuit diagram. 2. Set input signal amplitude using function generator. 3. Vary the input signal frequency from 0Hz to 100kHz in regular steps. 4. Note down the corresponding output voltage. 5. Plot the graph: Gain(dB) vs Frequency(Hz). Tabular column: Vi = S.NO Given Signal Frequency(Hz) Output Voltage(vo) Gain (dB)=20 log (V0/Vi)

1 2

Message Signal Carrier Signal

Model Graph:

Result: Thus pre-emphasis circuit using active and passive components is constructed and verified.

R.M.SURYA ,AP/ECE JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 7b DATE: AIM:

DESIGNING, ASSEMBLING AND TESTING OF DE-EMPHASIS CIRCUIT

To construct and verify De-emphasis network using active & passive components and plot the waveform. APPARATUS REQUIRED: S.No 1. 2. 3. 4. 5. 6. Name of the Component IC Resistors Capacitor Function generator CRO DPS Range IC741 100K,2.2K,15K,820 0.1F,1F,0.001F (0-1)MHz (0-20)MHz (15-0-15)V Quantity 1 Each 1 Each 1 1 1 1

THEORY: De-emphasis: The problem in FM broadcasting is that noise and hiss tend to be more noticeable, especially when receiving the weaker stations. To reduce this effect, the treble response of the audio signal is artificially boosted prior to transmission. This is known as pre-emphasis. At the receiver side a corresponding filter or de-emphasis circuit is required to reduce the treble response to correct level. Since most noise and hiss tend to be at the higher frequencies, the de-emphasis removes a lot of this. Pre-emphasis and de-emphasis thus allow an improved signal to noise ratio to be achieved while maintaining the frequency response of the original audio signal. The de-emphasis stage is used after the detector stage.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Circuit diagram: Using active components:

Using passive components:

Procedure: 1. Connections are made as per the circuit diagram. 2. Set input signal amplitude using function generator. 3. Vary the input signal frequency from 0Hz to 100kHz in regular steps. 4. Note down the corresponding output voltage. 5. Plot the graph: Gain(dB) vs Frequency(Hz).

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Tabular column :

Vi=

S.NO

Given Signal

Frequency(Hz)

Output Voltage(vo)

Gain (dB)=20 log (V0/Vi)

1 2

Message Signal Carrier Signal

Model Graph:

Result: Thus De-emphasis circuit using active and passive components is constructed and verified.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

EX NO: 8a DATE: AIM:

PHASE LOCKED LOOP

To study IC 565 PLL and find the following parameters: 1. Lock Range 2. Capture Range APPARATUS REQUIRED: S.No 1. 2. Capacitors 0.01F 3. 4. 5. 6. Resistor Function generator CRO DPS 12K (0-1)MHz (0-20)MHz (15-0-15)V Each 2 Each 1 Each 1 Each 1 Each 1 Name of the apparatus IC Range NE565 10F, 0.001F Quantity Each 1 Each 1

THEORY: Phase Locked Loop: A phase-locked loop is a feedback system combining a voltage controlled oscillator and a phase comparator so connected that the oscillator frequency (or phase) accurately tracks that of an applied frequency- or phase-modulated signal. Phase-locked loops can be used, for example, to generate stable output frequency signals from a fixed low-frequency signal. However, they only found broad acceptance in the marketplace when integrated PLLs became available as relatively low-cost components in the mid-1960s. The phase locked loop can be analyzed in general as a negative feedback system with a forward gain term and a feedback term. The loop filter is a low-pass type, typically with one pole and one zero. The transient response of the loop depends on: 1. The magnitude of the pole/zero, 2. The charge pump magnitude, 3. The VCO sensitivity, 4. The feedback factor, N.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

Block Diagram:

Circuit diagram:

Procedure: 1. Connect the circuit as per the circuit diagram. 2. Measure the free running frequency of IC565 at pin 4 using CRO with the input signal (say 0V) from the signal generator or shorting pin 2 to ground. 3. Set the input signal say 1V, 1 kHz to pin 2 using signal generator and observe the waveform on the CRO.

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

4. The frequency is varied till the output signal is 1800 out of phase with input. This is the upper end of lock range(f2). 5. The frequency is reduced till the output is 900 out of phase with the input. This is the upper end of capture range(f3). 6. The frequency is varied till a 900 phase shift is obtained in the output with reference to the input once again. This is the lower end of lock range(f4). 7. As the frequency is reduced further, output goes to 1800 out of phase with the input once again. This is the lower end of the capture range(f1). 8. The lock range, fL=(f2-f4) 9. The capture range, fc=(f3-f1) 10. Compare these values with its theoretical value.

Tabular column: S.no 1 2 3 Parameter Lock Range(fL) Capture Range(fC) Free running frequency(fOUT) Theoretical value Practical value

Calculation:

fOU T= 1.2/(4R1C1) Hz fL= + 8fOUT/V Hz

V=(+V)-(-V) volts

fC= +[fL/(2*3.6*103*C2)]1/2 Hz

S.NO

Input frequency (Hz) fN

Output Frequency(Hz) (Theoretical) fOUT = 5fN

Output Frequency(Hz) (practical)

Amplitude

(volts)

Time

(ms)

Frequency

(Hz)

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

1 2 3 4 5 6

Waveform:

Result: Thus the PLL is studied and the Lock range, capture range and free running frequency have been calculated.

R.M.SURYA ,AP/ECE JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

EC2307

COMMUNICATION SYSTEMS LABORATORY

R.M.SURYA ,AP/ECE

JAYAM COLLEGE OF ENGINEERING AND TECHNOLOGY

Anda mungkin juga menyukai

- CAO Ddinternal Marks III-Ece BDokumen4 halamanCAO Ddinternal Marks III-Ece Bpriyasrinivasan24Belum ada peringkat

- FM HHDokumen7 halamanFM HHpriyasrinivasan24Belum ada peringkat

- Long Arrrrrrrrbsences FormatDokumen13 halamanLong Arrrrrrrrbsences Formatpriyasrinivasan24Belum ada peringkat

- Designing, Assembling and Testing of De-Emphasis CircuitDokumen5 halamanDesigning, Assembling and Testing of De-Emphasis Circuitpriyasrinivasan24Belum ada peringkat

- Short Term Course List KKKDokumen2 halamanShort Term Course List KKKpriyasrinivasan24Belum ada peringkat

- Guest List NNNDokumen2 halamanGuest List NNNpriyasrinivasan24Belum ada peringkat

- S.No. Conference/Workshop/ Organizer DateDokumen2 halamanS.No. Conference/Workshop/ Organizer Datepriyasrinivasan24Belum ada peringkat

- SyllabusavDokumen2 halamanSyllabusavpriyasrinivasan24Belum ada peringkat

- Ss SsDokumen1 halamanSs Sspriyasrinivasan24Belum ada peringkat

- SyllabusavDokumen2 halamanSyllabusavpriyasrinivasan24Belum ada peringkat

- Po2 Ec2ttDokumen2 halamanPo2 Ec2ttpriyasrinivasan24Belum ada peringkat

- S.No Date Place Time: 1. 26.06.2013 Acet 10.00PMDokumen3 halamanS.No Date Place Time: 1. 26.06.2013 Acet 10.00PMpriyasrinivasan24Belum ada peringkat

- BATHRI1 T 4 DDokumen2 halamanBATHRI1 T 4 Dpriyasrinivasan24Belum ada peringkat

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (120)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Gobi 3000 Product SheetDokumen2 halamanGobi 3000 Product SheetresistanceisfutileBelum ada peringkat

- MCQ For WC PDFDokumen66 halamanMCQ For WC PDFyarmeena78% (23)

- Antenas AllgonDokumen49 halamanAntenas AllgonhectorVRBelum ada peringkat

- Day3-1000-1100-Civil UAV Monitoring techniques-JiWeilin PDFDokumen42 halamanDay3-1000-1100-Civil UAV Monitoring techniques-JiWeilin PDFPete AirBelum ada peringkat

- Wireless Underwater CommunicationDokumen20 halamanWireless Underwater Communicationangelcrystl4774Belum ada peringkat

- RadarDokumen40 halamanRadar.cheng.100% (1)

- AMB4521R0 - (Tri Beam)Dokumen2 halamanAMB4521R0 - (Tri Beam)Thaw Gyi100% (2)

- Microstrip Patch Array Antenna Pattern Design With Active ElementDokumen5 halamanMicrostrip Patch Array Antenna Pattern Design With Active ElementShakeel RanaBelum ada peringkat

- FRGQ Nokia Flexi RRUDokumen6 halamanFRGQ Nokia Flexi RRUMiau HuLaaBelum ada peringkat

- BRT WP 001 Smart Home GatewaysDokumen18 halamanBRT WP 001 Smart Home GatewaysLee yi kangBelum ada peringkat

- 3.5G Packages - Robi TelecomDokumen2 halaman3.5G Packages - Robi TelecomNazia AhmedBelum ada peringkat

- Design and Simulation of E-Shape Microstrip Patch Antenna For Wideband ApplicationsDokumen6 halamanDesign and Simulation of E-Shape Microstrip Patch Antenna For Wideband ApplicationshosseinBelum ada peringkat

- Baseband Questions StudentsDokumen3 halamanBaseband Questions StudentsRishi JhaBelum ada peringkat

- Micro and Macro DiversityDokumen46 halamanMicro and Macro DiversityNandhini PBelum ada peringkat

- SINCGARS Operations SOPDokumen1 halamanSINCGARS Operations SOPAndrew MarshBelum ada peringkat

- PROCOM r-70-7Dokumen2 halamanPROCOM r-70-7Milic MilicevicBelum ada peringkat

- Lecture 6 Multipath FadingDokumen37 halamanLecture 6 Multipath FadingWajeeha_Khan1Belum ada peringkat

- Devices Test 19052017 LTE SpeedDokumen53 halamanDevices Test 19052017 LTE SpeedThierry Rome JojoBelum ada peringkat

- 5.8 Yagi Antennas - DatasheetDokumen1 halaman5.8 Yagi Antennas - DatasheetYenifer CahuanaBelum ada peringkat

- Monitoring Times 1998 12Dokumen108 halamanMonitoring Times 1998 12Benjamin DoverBelum ada peringkat

- RW 2954 T100Dokumen3 halamanRW 2954 T100Christian Javier Lopez DuranBelum ada peringkat

- Juniper - Mist AP32 Access Point PDFDokumen6 halamanJuniper - Mist AP32 Access Point PDFBullzeye StrategyBelum ada peringkat

- GMDSS-STCW-GOC-FCC-El-7: Test Pool, Questions and Answers. (Answers, Bottom of Page) July 2006Dokumen100 halamanGMDSS-STCW-GOC-FCC-El-7: Test Pool, Questions and Answers. (Answers, Bottom of Page) July 2006Lokesh KumarBelum ada peringkat

- What Is A Rank Indication in LTE - PDFDokumen2 halamanWhat Is A Rank Indication in LTE - PDFabhishek agarwalBelum ada peringkat

- C-BXD-65606580-M: Mechanical SpecificationsDokumen1 halamanC-BXD-65606580-M: Mechanical Specificationsmegamaster0987654321Belum ada peringkat

- Detach, Timers & RealTime QXDM LogDokumen16 halamanDetach, Timers & RealTime QXDM Logakash kumarBelum ada peringkat

- Sprpackagereport 2434200900Dokumen135 halamanSprpackagereport 2434200900msureshmuthuvelBelum ada peringkat

- Plasma Antenna: Under The Guidance of Presented byDokumen20 halamanPlasma Antenna: Under The Guidance of Presented bySuneel NerreBelum ada peringkat

- Brochure - Catapult VectorDokumen24 halamanBrochure - Catapult VectorNicholas AndryievichBelum ada peringkat

- Kdfwkbfi PDF 1606941136Dokumen31 halamanKdfwkbfi PDF 1606941136Artem PavlovBelum ada peringkat