FS7M0680

Diunggah oleh

asr2972Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

FS7M0680

Diunggah oleh

asr2972Hak Cipta:

Format Tersedia

www.fairchildsemi.

com

FS7M0680, FS7M0880

Features

Pulse by Pulse Current Limit Over load protection (OLP) - Latch Over voltage protection (OVP) - Latch Internal Thermal Shutdown (TSD) - Latch Under Voltage Lock Out (UVLO) with hysteresis Internal High Voltage SenseFET (800V rated) User defined Soft Start Precision Fixed Operating Frequency (66kHz)

Fairchild Power Switch (FPSTM)

Table 1. Maximum Output Power OUTPUT POWER TABLE

PRODUCT 230VAC 15%(2) Open Frame(1) 80W (Flyback) 150W (Forward) 180W (Forward) (3) 110W (Flyback) 200W (Forward) 250W (Forward) (3) 85-265VAC Open Frame(1) 65W (Flyback)

FS7M0680

FS7M0880

85W (Flyback)

Application

PC power supply PDP

Notes: 1. Maximum practical continuous power in an open frame design at 50C ambient. 2. 230 VAC or 100/115 VAC with doubler. 3. When the cooling fan is used.

Description

The Fairchild Power Switch FS7M-series is an integrated Pulse Width Modulator (PWM) and Sense FET specifically designed for high performance offline Switch Mode Power Supplies (SMPS) with minimal external components. This device is an integrated high voltage power switching regulator which combine an avalanche rugged Sense FET with a current mode PWM control block. The PWM controller includes integrated fixed frequency oscillator, under voltage lockout, leading edge blanking (LEB), optimized gate driver, soft start, temperature compensated precise current sources for a loop compensation and self protection circuitry. Compared with discrete MOSFET and PWM controller solution, it can reduce total cost, component count, size and weight simultaneously increasing efficiency, productivity, and system reliability. This device is a basic platform well suited for cost effective designs of flyback and forward converters.

Typical Circuit

Vo

AC IN

S/S

FS7M-series

PWM

Drain GND

VFB

Vcc

Figure 1. Typical Forward Application

Rev.1.0.2

2005 Fairchild Semiconductor Corporation

FS7M0680, FS7M0880

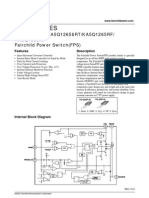

Internal Block Diagram

Vcc 3

Vref

Drain 1 Vcc good

Vref

9V/15V Soft start 5

Reset OSC

Internal Bias

Vcc Idelay

Vref IFB

PWM 2.5R R

S R

Q Q

FB 4

Gate driver

LEB VSD Vcc

S Q

Vovp TSD

Vcc Reset (Vcc<6V)

R Q

2 GND AOCP Vocp

Figure 2. Functional Block Diagram of FS7M0680 and FS7M0880

FS7M0680, FS7M0880

Pin Definitions

Pin Number 1 2 3 Pin Name Drain GND Vcc Pin Function Description High voltage power SenseFET drain connection. This pin is the control ground and the SenseFET source. This pin is the positive supply input. This pin provides internal operating current for both start-up and steady-state operation. This pin is internally connected to the inverting input of the PWM comparator. The collector of an opto-coupler is typically tied to this pin. For stable operation, a capacitor should be placed between this pin and GND. If the voltage of this pin reaches 7.5V, the over load protection triggers resulting in shutdown of the FPS. This pin is for the soft start. Soft start time is programmed by a capacitor on this pin.

Vfb

Soft-start

Pin Configuration

TO-3P-5L

5.S/S 4.Vfb 3.Vcc 2.GND 1.Drain

Figure 3. Pin Configuration (Top View)

FS7M0680, FS7M0880

Absolute Maximum Ratings

FS7M0680 Parameter Maximum Drain Voltage

(1)

Symbol VD,MAX VDGR VGS IDM

(3)

Value 800 800 30 24.0 455 20 6.0 3.8 30 -0.3 to VSD 150 1.21 -25 to +85 -55 to +150

Unit V V V ADC mJ A ADC ADC V V W W/C C C

Drain-Gate Voltage (RGS=1M) Gate-Source (GND) Voltage Drain Current Pulsed Avalanche Current

(4) (2)

Single Pulsed Avalanche Energy

EAS IAS ID ID VCC,MAX VFB PD Derating TA TSTG

Continuous Drain Current (TC=25C) Continuous Drain Current (TC=100C) Maximum Supply Voltage Input Voltage Range Total Power Dissipation Operating Ambient Temperature Storage Temperature

FS7M0880 Parameter Maximum Drain Voltage

(1)

Symbol VD,MAX VDGR VGS IDM EAS IAS ID ID VCC,MAX VFB PD Derating TA TSTG

Value 800 800 30 32.0 810 15 8.0 5.6 30 -0.3 to VSD 190 1.54 -25 to +85 -55 to +150

Unit V V V ADC mJ A ADC ADC V V W W/C C C

Drain-Gate Voltage (RGS=1M) Gate-Source (GND) Voltage Drain Current Pulsed Avalanche Current

(4) (2)

Single Pulsed Avalanche Energy (3) Continuous Drain Current (TC=25C) Continuous Drain Current (TC=100C) Maximum Supply Voltage Input Voltage Range Total Power Dissipation Operating Ambient Temperature Storage Temperature

Note: 1. Tj = 25C to 150C 2. Repetitive rating: Pulse width limited by maximum junction temperature 3. L = 24mH, VDD = 50V, RG = 25, starting Tj =25C 4. L = 13H, starting Tj = 25C

FS7M0680, FS7M0880

Electrical Characteristics (SenseFET Part)

(Ta=25C unless otherwise specified) FS7M0680 Parameter Drain-Source Breakdown Voltage Zero Gate Voltage Drain Current Symbol BVDSS IDSS Condition VGS=0V, ID=50A VDS=Max., Rating, VGS=0V VDS=0.8Max., Rating, VGS=0V, TC=125C VGS=10V, ID=5.0A VGS=0V, VDS=25V, f=1MHz VDD=0.5BVDSS, ID=8.0A (MOSFET switching time are essentially independent of operating temperature) VGS=10V, ID=8.0A, VDS=0.5BVDSS (MOSFET switching time are essentially independent of operating temperature) Min. 800 Typ. 1.6 1600 140 42 60 150 300 130 70 16 27 Max. 50 200 2.0 nC nS pF Unit V A A

Static Drain-Source On Resistance (note1) RDS(ON) Input Capacitance Output Capacitance Reverse Transfer Capacitance Turn On Delay Time Rise Time Turn Off Delay Time Fall Time Total Gate Charge (Gate-Source+Gate-Drain) Gate-Source Charge Gate-Drain (Miller) Charge Ciss Coss Crss td(on) tr td(off) tf Qg Qgs Qgd

FS7M0880 Parameter Drain-Source Breakdown Voltage Zero Gate Voltage Drain Current Symbol BVDSS IDSS Condition VGS=0V, ID=50A VDS=Max., Rating, VGS=0V VDS=0.8Max., Rating, VGS=0V, TC=125C VGS=10V, ID=5.0A VGS=0V, VDS=25V, f=1MHz VDD=0.5BVDSS, ID=8.0A (MOSFET switching time are essentially independent of operating temperature) VGS=10V, ID=8.0A, VDS=0.5BVDSS (MOSFET switching time are essentially independent of operating temperature) Min. 800 Typ. 1.2 2460 210 64 95 150 60 20 70 Max. 50 200 1.5 90 200 450 150 150 nC nS pF Unit V A A

Static Drain-Source On Resistance (note1) RDS(ON) Input Capacitance Output Capacitance Reverse Transfer Capacitance Turn On Delay Time Rise Time Turn Off Delay Time Fall Time Total Gate Charge (Gate-Source+Gate-Drain) Gate-Source Charge Gate-Drain (Miller) Charge

Note: 1. Pulse test: Pulse width 300S, duty cycle 2%

Ciss Coss Crss td(on) tr td(off) tf Qg Qgs Qgd

FS7M0680, FS7M0880

Electrical Characteristics (Continued)

(Ta=25C unless otherwise specified) Parameter UVLO SECTION Start Threshold Voltage Stop Threshold Voltage OSCILLATOR SECTION Initial Frequency Frequency Change With Temperature Maximum Duty Cycle FEEDBACK SECTION Feedback Source Current Shutdown Delay Current SOFT START SECTION Soft Start Voltage Soft Start Current FS7M0680 FS7M0880 PROTECTION SECTION Thermal Shutdown Temperature (Tj) (1) Over Voltage Protection Voltage Over Current Protection Voltage TOTAL DEVICE SECTION Start Up Current Operating Supply Current (Control Part Only) Shutdown Feedback Voltage ISTART IOP Iop(lat) VSD VCC=14V Ta=25C After latch, Vcc=Vstop-0.1V 150 6.9 40 8 250 7.5 80 12 350 8.1 uA mA uA V TSD VOVP VOCP 140 25 1.05 28 1.10 31 1.15 C V V VSS ISS IOVER IOVER VFB =2V Sync & S/S=GND Max. inductor current Max. inductor current 4.7 0.8 3.52 4.40 5.0 1.0 4.00 5.00 5.3 1.2 4.48 5.60 V mA A A IFB Idelay Ta=25C, 0V Vfb 3V Ta=25C, 5V Vfb VSD 0.7 4.0 0.9 5.0 1.1 6.0 mA A

(2)

Symbol VSTART VSTOP FOSC F/T Dmax

Condition After turn on -25C Ta +85C -

Min. 14 8 60 45

Typ. 15 9 66 5 50

Max. 16 10 72 10 55

Unit V V kHz % %

CURRENT LIMIT (SELT-PROTECTION)SECTION

Note: 1. These parameters, although guaranteed, are not 100% tested in production 2. These parameters, although guaranteed, are tested in EDS (wafer test) process

FS7M0680, FS7M0880

Electrical characteristics

1.20 1.15

1.20 1.15

Normalized to 25C

Normalized to 25C

-20 0 20 40 60 80 Temperature [C] 100 120 140 160

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160

Temperature [C]

Operating Supply Current vs. Temp.

Start up Current vs. Temp.

1.20 1.15

1.20 1.15

Normalized to 25C

Normalized to 25C

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160

Temperature [C]

Temperature [C]

Vcc Start Threshold Voltage vs. Temp.

Vcc Stop Threshold Voltage vs. Temp.

1.20 1.15

1.20 1.15 1.10

Normalized to 25C

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160

Dmax [%]

1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160 Temperature [C]

Temperature [C]

Operating Frequency vs. Temp.

Maximum Duty Cycle vs. Temp.

FS7M0680, FS7M0880

Electrical characteristics

1.20 1.15

Normalized to 25C

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160

1.7 1.6 1.5 1.4 1.3 1.2 1.1 1.0 0.9 0.8 0.7 0.6 0.5 -40

Normalized to 25C

-20

20

40

60

80

100 120 140 160

Temperature [C]

Temperature [C]

Minimum Duty Cycle vs. Temp.

Feedback Offset Voltage vs. Temp.

1.20 1.15

1.20 1.15

Normalized to 25C

Normalized to 25C

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160

Temperature [C]

Temperature [C]

Shutdown Feedback Voltage vs. Temp.

Shutdown Delay Current vs. Temp.

1.20 1.15

1.20 1.15

Normalized to 25C

Normalized to 25C

-20 0 20 40 60 80 100 120 140 160

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160

Temperature [C]

Temperature [C]

SoftStart Voltage vs. Temp.

Over Voltage Protection vs. Temp.

FS7M0680, FS7M0880

Electrical characteristics

1.4 1.3

1.20 1.15

Normalized to 25C

1.2 1.1 1.0 0.9 0.8 -40

Normalized to 25C

-20 0 20 40 60 80 100 120 140 160

1.10 1.05 1.00 0.95 0.90 0.85 0.80 -40 -20 0 20 40 60 80 100 120 140 160

Temperature [C]

Temperature [C]

Feedback Current vs. Temp.

Pulse-by-pulse Current limit vs. Temp.

FS7M0680, FS7M0880

Functional Description

1. Startup : Figure 4 shows the typical startup circuit and transformer auxiliary winding for FS7M-series. Because all the protections are implemented as latch mode, AC startup is typically used to provide a fast reset as shown in Figure 4. Before FPS begins switching operation, only startup current (typically 40uA) is consumed and the current supplied from the AC line charges the external capacitor (Ca) that is connected to the Vcc pin. When Vcc reaches start voltage of 15V (VSTART), FPS begins switching, and the current consumed by FPS increases to 8mA. Then, FPS continues its normal switching operation and the power required for this device is supplied from the transformer auxiliary winding, unless Vcc drops below the stop voltage of 9V (VSTOP). To guarantee the stable operation of the control IC, Vcc has under voltage lockout (UVLO) with 6V hysteresis. Figure 5 shows the relation between the FPS operating supply current and the supply voltage (Vcc).

The minimum average of the current supplied from the AC is given by

avg

I sup

2 V ac V start 1 - --------= ----------------------------- ------------2 R str

min

where Vacmin is the minimum input voltage, Vstart is the Vcc start voltage (15V) and Rstr is the startup resistor. The startup resistor should be chosen so that Isupavg is larger than the maximum startup current (80uA). Once the resistor value is determined, the maximum loss in the startup resistor is obtained as

) + V start 2 2 V start V ac 1 - ( V ac - - ----------------------------------------------------Loss = -------- -------------------------------------------------R str 2

max 2 2 max

where Vacmax is the maximum input voltage. The startup resistor should have proper rated dissipation wattage.

CDC

1N4007 AC line (Va cm in - Vacm ax) Rs tr Da Isup

Vcc

FS7M -series

Ca

2. Feedback Control : FS7M-series employs current mode control, as shown in Figure 6. An opto-coupler (such as the H11A817A) and shunt regulator (such as the KA431) are typically used to implement the feedback network. Comparing the feedback voltage with the voltage across the Rsense resistor plus an offset voltage makes it possible to control the switching duty cycle. When the reference pin voltage of the KA431 exceeds the internal reference voltage of 2.5V, the H11A817A LED current increases, thus pulling down the feedback voltage and reducing the duty cycle. This event typically happens when the input voltage is increased or the output load is decreased. 2.1 Pulse-by-pulse current limit: Because current mode control is employed, the peak current through the Sense FET is limited by the inverting input of PWM comparator (Vfb*) as shown in Figure 6. The feedback current (IFB) and internal resistors are designed so that the maximum cathode voltage of diode D2 is about 2.8V, which occurs when all IFB flows through the internal resistors. Since D1 is blocked when the feedback voltage (Vfb) exceeds 2.8V, the maximum voltage of the cathode of D2 is clamped at this voltage, thus clamping Vfb*. Therefore, the peak value of the current through the Sense FET is limited. 2.2 Leading edge blanking (LEB) : At the instant the internal Sense FET is turned on, there usually exists a high current spike through the Sense FET, caused by external resonant capacitor across the MOSFET and secondary-side rectifier reverse recovery. Excessive voltage across the Rsense resistor would lead to incorrect feedback operation in the current mode PWM control. To counter this effect, the FPS employs a leading edge blanking (LEB) circuit. This circuit inhibits the PWM comparator for a short time (TLEB) after the Sense FET is turned on.

Figure 4. Startup circuit

Icc

8mA

Power Down 40uA Vstop=9V

Power Up

Vcc Vstart=15V Vz

Figure 5. Relation between operating supply current and Vcc voltage

10

FS7M0680, FS7M0880

Vcc Idelay

Vref IFB

OSC

Vo

Vfb

H11A817A

CB

4 D1 D2 + Vfb* 2.5R

SenseFET

Gate driver

KA431

VSD

OLP

Rsense

Figure 6. Pulse width modulation (PWM) circuit

3. Protection Circuit : The FS7M-series has several self protective functions such as over load protection (OLP), abnormal over current protection (AOCP), over voltage protection (OVP) and thermal shutdown (TSD). All the protections are latch mode protection. Because these protection circuits are fully integrated into the IC without external components, the reliability can be improved without increasing cost. Once protection triggers, switching is terminated and Vcc continues charging and discharging between 9V and 15V until the AC power line is un-plugged. The latch is reset only when Vcc is fully discharged by un-plugging the Ac power line.

3.1 Over Load Protection (OLP) : Overload is defined as the load current exceeding its normal level due to an unexpected abnormal event. In this situation, the protection circuit should trigger in order to protect the SMPS. However, even when the SMPS is in the normal operation, the over load protection circuit can be triggered during the load transition. In order to avoid this undesired operation, the over load protection circuit is designed to trigger after a specified time to determine whether it is a transient situation or an overload situation. Because of the pulse-by-pulse current limit capability, the maximum peak current through the Sense FET is limited, and therefore the maximum input power is restricted with a given input voltage. If the output consumes more than this maximum power, the output voltage (Vo) decreases below the set voltage. This reduces the current through the opto-coupler LED, which also reduces the opto-coupler transistor current, thus increasing the feedback voltage (Vfb). If Vfb exceeds 2.8V, D1 is blocked and the 5uA current source starts to charge CB slowly up to Vcc. In this condition, Vfb continues increasing until it reaches 7.5V, when the switching operation is terminated as shown in Figure 8. The delay time for shutdown is the time required to charge CB from 2.8V to 7.5V with 5uA. In general, a 20 ~ 50 ms delay time is typical for most applications. This protection is implemented in auto restart mode.

V FB

7.5V

Over load protection

AC line plugged-in

Vds

Fault occurs

AC line un-plugged

AC line plugged-in Vcc reset

2.8V

T12= CB*(7.5-2.8)/Idelay

T1

T2

Figure 8. Over load protection

Vcc

15V 9V 6V

t

Normal operation

Normal operation

Latch

Figure 7. Auto restart mode protection

3.2 Abnormal Over Current Protection (AOCP) : When the secondary rectifier diodes or the transformer pins are shorted, a steep current with extremely high di/dt can flow through the SenseFET during the LEB time. Even though the FS7M-series has OLP (Over Load Protection), it is not enough to protect the FPS in that abnormal case, since sever current stress will be imposed on the SenseFET until OLP triggers. The FS7M-series has an internal AOCP (Abnormal Over Current Protection) circuit as shown in Figure 9. When the gate turn-on signal is applied to the power Sense FET, the AOCP block is enabled and monitors the current through the sensing resistor. The voltage across the resistor is then 11

FS7M0680, FS7M0880

compared with a preset AOCP level. If the sensing resistor voltage is greater than the AOCP level, the set signal is applied to the latch, resulting in the shutdown of SMPS. This protection is implemented in latch mode.

2.5R

OSC

PWM

Gate driver

LEB

Rsense AOCP Vaocp

+

2 GND

Figure 9. AOCP block

3.3 Over voltage Protection (OVP) : If the secondary side feedback circuit were to malfunction or a solder defect caused an open in the feedback path, the current through the opto-coupler transistor becomes almost zero. Then, Vfb climbs up in a similar manner to the over load situation, forcing the preset maximum current to be supplied to the SMPS until the over load protection is activated. Because more energy than required is provided to the output, the output voltage may exceed the rated voltage before the over load protection is activated, resulting in the breakdown of the devices in the secondary side. In order to prevent this situation, an over voltage protection (OVP) circuit is employed. In general, Vcc is proportional to the output voltage and the FPS uses Vcc instead of directly monitoring the output voltage. If VCC exceeds 28V, an OVP circuit is activated resulting in the termination of the switching operation. In order to avoid undesired activation of OVP during normal operation, Vcc should be designed to be below OVP threshold. 3.4 Thermal Shutdown (TSD) : The SenseFET and the control IC are built in one package. This makes it easy for the control IC to detect the abnormal over temperature of the SenseFET. When the temperature exceeds approximately 150C, the thermal shutdown triggers. This protection is implemented in latch mode. 4. Soft Start : The FS7M-series has a soft start circuit that increases PWM comparator inverting input voltage together with the SenseFET current slowly after it starts up. The soft start time can be programmed using a capacitor on the softstart pin. The pulse width to the power switching device is progressively increased to establish the correct working conditions for transformers, inductors, and capacitors. It also helps to prevent transformer saturation and reduce the stress on the secondary diode during startup. 12

FS7M0680, FS7M0880

Typical application circuit I (7M0880 : Forward)

Application PC Power 1. Schematic

D5 T1 MBRF30H100CT EER3542 13,14 1 R3 56k 2W R4 56k 2W C6 22nF 630V C18 R13

Output power 250W (Cooling Fan)

Input voltage Universal input with voltage doubler

Output voltage (Max current) 5V (26A), 12V (10A)

L1 12V, 10A C12 2200uF 16V C11 1000uF 16V

C4 470uF 200V

R5 220k 1W

R1 50k 0.5W R2 50k 0.5W D1 UF4007 IC1 FS7M0880

8, 9 D2 FR257 3 D4 MBR3060PT 10,11,12 C13 3300uF 10V C14 1000uF 10V

5V, 26A

C5 470uF 200V

R6 220k 1W

BD1 GDB206 C2 4.7nF 1kV C3 4.7nF 1kV

5 S/S 4 C10 1uF 16V C9 33nF

Drain 1 3 C7 33uF 35V D3 UF4007 R7 10 6 GND 2

FB

Vcc

7 OP1 PC817

R11 1k

LF1 R12 820 C17 100nF R9 1k

C15 10nF 1kV

C16 IC3 10nF KA431 1kV

R10 1k

C1 470nF 275VAC

RT1 10D-11 F101 FUSE 250V 5.0A

2.Transformer Specification (CORE : EER 3542 , BOBBIN : EER3542) No. NP/2 N+5V N+12V NP/2 NVCC PIN(S F) 13 8, 9 10, 11, 12 13, 14 9 13 76 WIRE 0.65 1 15mm 0.15mm 1 0.65 3 0.65 1 0.6 1 TURNS 50T 4T 5T 50T 6T WINDING METHOD SOLENOID WINDING COPPER FOIL WINDING SOLENOID WINDING SOLENOID WINDING SOLENOID WINDING

Transformer Electrical Characteristics Pin Inductance Leakage Inductance 1-3 1-3

Specification 6mH 5% 15uH Max

Remarks @70kHz, 1V 2nd all short

3. Secondary Inductor(L1) Specification

Core : Power Core 27 16 Grade 5V : 12T (1 2) 10V : 27T (1.2 1) 13

FS7M0680, FS7M0880

Typical application circuit II (7M0880 : Flyback)

Application Adaptor Output power 108W Input voltage European Input Output voltage (Max current) 12V (9A)

1. Schematic

EER4042 NTC 10D-11 47k 2W 100uF 400V 100k 1W UF 4007 IC1 FS7M0880 5 S/S 2.2nF 250VAC 2.2nF 250VAC 1uF 50V 22nF 4 Drain 1 UF4004 FB GND 2 Vcc 3 12 7 47uF 50V 8 LF1 20mH PC817 7.6k 2.2k 100nF 275VAC 3.3nF IC3 KA431 1k 4.7k 47nF 4 1 22nF 630V 3 12 2200uF / 25V X3 MBR30100CT 13 2200uF 25V 9uH 12V, 9A

2KBP06M3N257

1k

FUSE 250V 2.0A

2. Transformer Specification

Winding Specification

No. NP/2 N+12V NB NP/2 PIN(S F) 13 12 13 87 34 WIRE 0.4 1 14mm 0.15mm 1 0.3 1 0.4 1 TURNS 42 8 9 42 WINDING METHOD SOLENOID WINDING COPPER WINDING SOLENOID WINDING SOLENOID WINDING

INSULATION : POLYESTER TAPE t = 0.050mm, 1Layer INSULATION : POLYESTER TAPE t = 0.050mm, 3Layer INSULATION : POLYESTER TAPE t = 0.050mm, 1Layer OUTER INSULATION : POLYESTER TAPE t = 0.050mm, 3Layer

Electrical Characteristic

CLOSURE INDUCTANCE LEAKAGE L PIN 1-4 1-4 SPEC. 700uH 10% 10uH MAX. REMARKS 1kHz, 1V 2nd ALL SHORT

Core & Bobbin

CORE : EER 4042 , BOBBIN : EER4042

14

FS7M0680, FS7M0880

Package Dimensions

TO-3P-5L

15

FS7M0680, FS7M0880

Package Dimensions (Continued)

TO-3P-5L(Forming)

16

FS7M0680, FS7M0880

Ordering Information

Product Number FS7M0680TU FS7M0680YDTU FS7M0880TU FS7M0880YDTU

TU : Non Forming Type YDTU : Forming type

Package TO-3P-5L TO-3P-5L(Forming) TO-3P-5L TO-3P-5L(Forming)

Rating 800V, 6A 800V, 8A

Fosc 66kHz 66kHz

17

FS7M0680, FS7M0880

DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

www.fairchildsemi.com 5/4/05 0.0m 001 2005 Fairchild Semiconductor Corporation

2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Anda mungkin juga menyukai

- T-CON Schematic PDFDokumen138 halamanT-CON Schematic PDFMahmoued Yasin78% (51)

- T-CON Schematic PDFDokumen138 halamanT-CON Schematic PDFMahmoued Yasin78% (51)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDari EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsBelum ada peringkat

- Analog Circuit Design Volume Three: Design Note CollectionDari EverandAnalog Circuit Design Volume Three: Design Note CollectionPenilaian: 3 dari 5 bintang3/5 (2)

- KA5Q1265RFDokumen17 halamanKA5Q1265RFLudwig Sohn GottesBelum ada peringkat

- 5Q1265RFDokumen16 halaman5Q1265RFAron Indra Lezcano GalvezBelum ada peringkat

- Ka5S-Series: KA5S0765C/KA5S0965/KA5S12656/KA5S1265 Fairchild Power Switch (FPS)Dokumen16 halamanKa5S-Series: KA5S0765C/KA5S0965/KA5S12656/KA5S1265 Fairchild Power Switch (FPS)Buga BuniciBelum ada peringkat

- 5 M 0965 QT UDokumen12 halaman5 M 0965 QT UcesarlcaBelum ada peringkat

- Fs6s1265re PDFDokumen11 halamanFs6s1265re PDFHelton AmorimBelum ada peringkat

- 5MO365R Datasheet 234274 - DSDokumen21 halaman5MO365R Datasheet 234274 - DSjoaocarlos1705Belum ada peringkat

- 5M0380RDokumen20 halaman5M0380RGenaro Santiago MartinezBelum ada peringkat

- DM 0565 RDokumen20 halamanDM 0565 R81968Belum ada peringkat

- Datasheet 5m0965Dokumen14 halamanDatasheet 5m0965Carlos GoncalvezBelum ada peringkat

- Irf4104Gpbf: FeaturesDokumen9 halamanIrf4104Gpbf: FeaturesAdam StevensonBelum ada peringkat

- CS2841BD14Dokumen10 halamanCS2841BD14giapy0000Belum ada peringkat

- IC KA3S0680RF DatasheetDokumen12 halamanIC KA3S0680RF Datasheetnaupas007Belum ada peringkat

- 1M0365RDokumen11 halaman1M0365RAndro DackBelum ada peringkat

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDokumen10 halamanSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiBelum ada peringkat

- 161 20551 0 FS7M0880Dokumen16 halaman161 20551 0 FS7M0880Edwin Vitovis TorresBelum ada peringkat

- KA5H0380R/KA5M0380R/KA5L0380R: Features DescriptionDokumen14 halamanKA5H0380R/KA5M0380R/KA5L0380R: Features DescriptionVidal VelasquezBelum ada peringkat

- KA1H0165RDokumen12 halamanKA1H0165RJtzabalaBelum ada peringkat

- Irfp2907Pbf: Typical ApplicationsDokumen9 halamanIrfp2907Pbf: Typical Applicationsrajeev_kumar_1231852Belum ada peringkat

- International Rectifier IRFP2907Dokumen9 halamanInternational Rectifier IRFP2907scribd20110526Belum ada peringkat

- FSDM07652R DatasheetDokumen16 halamanFSDM07652R Datasheetmarianos67Belum ada peringkat

- MAX038Dokumen17 halamanMAX038Brane PetkoskiBelum ada peringkat

- 1565 RTDokumen24 halaman1565 RTJose Samuel Robelto RBelum ada peringkat

- CD4047Dokumen9 halamanCD4047Haryadi VjBelum ada peringkat

- CQ 0765RTDokumen24 halamanCQ 0765RTsonivitel100% (2)

- Viper 53Dokumen24 halamanViper 53Cadena CesarBelum ada peringkat

- LTC 1625Dokumen24 halamanLTC 1625Sakura KunBelum ada peringkat

- IRF8788Dokumen9 halamanIRF8788Robert KovacsBelum ada peringkat

- MC33153 DDokumen14 halamanMC33153 DPham LongBelum ada peringkat

- 5Q1265RT - CD1265RTDokumen6 halaman5Q1265RT - CD1265RTJulian Andres Rozo100% (1)

- Tps 40057 PWPDokumen33 halamanTps 40057 PWPcatsoithahuong84Belum ada peringkat

- Irfp 2907Dokumen9 halamanIrfp 2907Anonymous u8GkNaBelum ada peringkat

- Green Current Mode PWM Controller: Features DescriptionDokumen12 halamanGreen Current Mode PWM Controller: Features Descriptionceny123Belum ada peringkat

- Irf640a PDFDokumen7 halamanIrf640a PDFXavier CastilloBelum ada peringkat

- Fan 7530Dokumen20 halamanFan 7530aldo_suviBelum ada peringkat

- TL062CPDokumen12 halamanTL062CPCleison FerreiraBelum ada peringkat

- Irfb4410Zgpbf: V 100V R Typ. 7.2M Max. 9.0M I 97ADokumen8 halamanIrfb4410Zgpbf: V 100V R Typ. 7.2M Max. 9.0M I 97AWalter Hurtado ToroBelum ada peringkat

- Ic 3843Dokumen4 halamanIc 3843nishatiwari82Belum ada peringkat

- Irfp 260 NDokumen9 halamanIrfp 260 NJolaine MojicaBelum ada peringkat

- Aplicacion Note UC3843Dokumen11 halamanAplicacion Note UC3843Luis PapaBelum ada peringkat

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDari EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsPenilaian: 3.5 dari 5 bintang3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorDari Everand110 Waveform Generator Projects for the Home ConstructorPenilaian: 4 dari 5 bintang4/5 (1)

- Analog Circuit Design Volume 2: Immersion in the Black Art of Analog DesignDari EverandAnalog Circuit Design Volume 2: Immersion in the Black Art of Analog DesignBelum ada peringkat

- Digital Power Electronics and ApplicationsDari EverandDigital Power Electronics and ApplicationsPenilaian: 3.5 dari 5 bintang3.5/5 (3)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetDari EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetPenilaian: 2 dari 5 bintang2/5 (1)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetDari EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetBelum ada peringkat

- Operational Amplifier Circuits: Analysis and DesignDari EverandOperational Amplifier Circuits: Analysis and DesignPenilaian: 4.5 dari 5 bintang4.5/5 (2)

- 44-136839TCH Validating UV VisibleDokumen12 halaman44-136839TCH Validating UV VisibleMahmoued YasinBelum ada peringkat

- 2PG009 AED DisconDokumen4 halaman2PG009 AED DisconMahmoued YasinBelum ada peringkat

- 2 On 60Dokumen6 halaman2 On 60Mahmoued YasinBelum ada peringkat

- FQPF17P06: 60V P-Channel MOSFETDokumen8 halamanFQPF17P06: 60V P-Channel MOSFETMahmoued YasinBelum ada peringkat

- Ms6m48 SemaDokumen7 halamanMs6m48 SemaMahmoued Yasin100% (1)

- Half-Bridge Driver (S) : Features Product SummaryDokumen9 halamanHalf-Bridge Driver (S) : Features Product SummaryMahmoued YasinBelum ada peringkat

- TV Control Board SpecificationDokumen11 halamanTV Control Board SpecificationMahmoued YasinBelum ada peringkat

- TDA8925Dokumen23 halamanTDA8925Mahmoued YasinBelum ada peringkat

- FQPF17P06: 60V P-Channel MOSFETDokumen8 halamanFQPF17P06: 60V P-Channel MOSFETMahmoued YasinBelum ada peringkat

- RJH30Dokumen8 halamanRJH30Mahmoued YasinBelum ada peringkat

- P2003BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDokumen5 halamanP2003BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorMahmoued YasinBelum ada peringkat

- Icpoes PDFDokumen53 halamanIcpoes PDFMahmoued YasinBelum ada peringkat

- W2a SMD Transistor PDFDokumen86 halamanW2a SMD Transistor PDFMahmoued YasinBelum ada peringkat

- 3 N 80Dokumen6 halaman3 N 80Mahmoued YasinBelum ada peringkat

- F13NK50 PDFDokumen15 halamanF13NK50 PDFMahmoued YasinBelum ada peringkat

- ELECTRONICDokumen13 halamanELECTRONICMahmoued YasinBelum ada peringkat

- LNBP 20 ADokumen18 halamanLNBP 20 AMahmoued YasinBelum ada peringkat