Implementation of Sigma-Delta ADC With ST7FLITE05-09-CD00010935

Diunggah oleh

Dan EsentherHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Implementation of Sigma-Delta ADC With ST7FLITE05-09-CD00010935

Diunggah oleh

Dan EsentherHak Cipta:

Format Tersedia

AN1827 APPLICATION NOTE

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

INTRODUCTION

The purpose of this document is to describe how to implement a 10-bit Sigma-Delta A/D converter using a simple external circuit and a Sigma-Delta conversion program. The ST7FLITE05(09) has an on-chip ADC with 8-bit resolution and an input range of 0-VCC. The external Sigma-Delta ADC described in this application is designed for relatively slow alternating signals (0,2 - 5Hz) in the range 0 - 10mV(p-p). The focus of the project is to provide good relative accuracy, repeatable parameters and simplicity, resulting therefore a low cost of the device (in its simplest form, apart from the microcontroller, only three RC elements are necessary).

Rev. 1.0

AN1827/0304 1/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

1 SIGMA-DELTA CONVERTER THEORY

The basic Sigma-Delta converter (Figure 1) is built of 2 basic circuits: a modulator and a digital filter. In the modulator the input signal is summarised with the signal of negative feedback from the D/A converter. The signals difference, after passing through the integrating circuit, reaches the input of the comparator, where it is compared to the reference voltage (the comparator works as a 1-bit quantizator). The input signal from the comparator controls the 1-bit converter and reaches the input of the digital filter, which decreases flowability and transforms the 1-bit stream into 10-bit words. Figure 1. Sigma-Delta Conversion

+ -

!

VREF

+ -

DIGITAL FILTER

1 BIT DAC

Figure 2 shows the general scheme of the microcontroller implementation. Within the system the function of an integrator is fulfilled by the Ci capacitor, and the range of converted voltages depends on the resistance ratio R1 and R2. The principle of operation is as follows: from the moment of setting the high status on the output, the voltage on the Ci capacitor and simultaneously on the input of the comparator begins to rise. As soon as the reference voltage is reached the output status is altered and the voltage decreases. After falling below the reference voltage the output status is altered to the high one and the cycle repeats. Provision of the state of balance and the correct conversion of signal into its digital form is realised by a program-operated feedback loop and digital filter.

2/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

Figure 2. Sigma-Delta Implementation with Microcontroller

SERIAL OUTPUT PORT I/O

R2 FIRMWARE VIN R1 Ci + VREF COMPARATOR

3/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

2 REALISATION WITH THE USE OF THE MICROCONTROLLER ST7FLITE05(09)

The practical realisation of the Sigma-Delta converter has been used with our passive infrared detector. A sensor of passive infrared characterises with a low output voltage (below 10mV) as well as with a usable range of frequencies from 0,2Hz to 7Hz. Therefore the Sigma-Delta converter is a perfect solution. It provides an accurate enough conversion of a signal into its digital form with use of a minimal number of external elements. That means simplicity of construction, relatively low production costs and good using properties. Figure 3 presents the block diagram of the detector. Figure 3. ST7FLITE05 interfacing with PIR Sensor

VCC LD2980 POWER

VCC PA 0 PA 1 TP SERIAL OUTPUT

ST7FLITE05

PA 4 ANALOG PB 0 INPUT VCC ANALOG PB 1 INPUT PB 4 OUTPUT CONFIGURATION ADC PA 7 OUTPUT REL ELEMENT PIR PA 5 PA 6

x8

A signal from the sensor passes through the capacitor to the input of the converter. The A/D converter has been used as a comparator in the microcontroller as well as the source of the reference voltage. By enabling the internal x8 amplifier, the amplitude of an output signal has been decreased 20 times to provide correct operation of the amplifier. This allows a decrease in the resistors value span in the same ratio and to increase the operational accuracy of the A/D converter working as a comparator. Additionally the temperature compensation of sensitivity has been introduced. Figure 4 shows the work algorithm of the Sigma-Delta converter.

4/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

Figure 4. Flow Chart (Sigma-Delta Conversion)

A/D conversion from AIN1 channel, amplifier x8 included

True UAIN1>037h Dlt_out:=0 inc Adc

False

Dlt_out:=1

inc Loop

True

Loop = 1024?

False

Initiation of a new conversion Nw_adc := 1 Rez := Adc Loop := 0 Adc := 0

End of interrupt

End of interrupt

5/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

3 THE DESCRIPTION OF THE SIGMA-DELTA CONVERSION PROGRAM

The Sigma-Delta conversion procedure is executed cyclically in an interrupt from the AT timer with a period of 50s. The result of the Sigma-Delta conversion (a 10-bit word) is achieved every 1024 interrupts, that is to say every 51.2ms. The main loop of the program awaits the Sigma-Delta conversion result and sends it through the RS serial interface to the computer. The start of the Sigma-Delta conversion is preceded with clearing of the loop conversion counter Loop_h, Loop_l and the result registry Adc_h, Adc_l. At the first stage, the service routine of the AT timer interrupt clears the marker of request and executes the A/D conversion from the AIN1 channel (the x8 amplifier is on). Following this, the result of conversion is compared with the constant value represented by the reference voltage 037h). If, in the result of comparison, the voltage from the AIN1 channel is lower than the reference voltage, then the B-Dlt port line will be set and the loop conversions counter will be increased. Loop_h, Loop_l. In a reverse situation, when the voltage from the AIN1 channel is higher than the reference voltage, the B-Dlt port line will be set to zero, and the Adc_h,Adc_l result registry as well as the Loop_h, Loop_l. loop conversion counter will be increased. The next task of the interrupt is to check whether the Loop_h, Loop_l loop conversion counter has reached the value 1024. When the Loop_h, Loop_l loop conversion counter is lower than 1024, the service routine of the interrupt finishes. If this condition is fulfilled the value of the result registry is rewritten into the result Rez_h, Rez_l buffer and a request of a new result to the main loop is set and the start of a new conversion is initiated (clearing of the Loop_h, Loop_l counter and of the Adc_h,Adc_l.result registry) The period of an AT timer interrupt is not critical. In the below example, because of the frequency of the signal from the passive infrared detector and the speed of RS communication (19200bps), it has been defined at 50s.

;********************************************************************** ;Listing of S-D conversion program. ;********************************************************************** st7/ TITLE "pir.asm" #INCLUDE "st72flt0.inc" ; definitions of registers st72lite ;********************************************************************** ;The program that realises the sigma/delta conversion ;sends the results of conversion to PC through the RS port ;********************************************************************** ;Definitions of variables

6/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

;********************************************************************** Rez_h equ $80 ; conversion result buffer H Rez_l equ $81 ; conversion result buffer L Loop_h equ $82 ; loop conversions counter H Loop_l equ $83 ; loop conversions counter L Adc_h equ $84 ; conversion result H Adc_l equ $85 ; conversion result L FLAGS0 equ $90 ; binary variables Nw_adc equ 7 ; new data from the conversion m50us equ 6 ; marker 50us ;********************************************************************** ;Definitions of constants ;********************************************************************** ;port A ; destination of bits in port A RS equ 6 ;********************************************************************** ;port B ; destination of bits in port B Adc_in equ 1 Dlt_out equ 4 ;********************************************************************** ;Processor initiation segment 'rom' ;********************************************************************** INIT: sim rsp ld a,$FFDE ld RCCR,a ; oscillator frequency calibrator RC ld a,#%01000000 ; settings of ports ld PADDR,a ld a,#%01000000 ld PAOR,a ld PADR,a ld a,#%00010000 ld PBDDR,a ld a,#%00010000 ld PBOR,a ld PBDR,a ld x,#$80 clr (x) inc x jrne loop_clrRAM ld a,#$0E ; All RAM clearing (80-FF)

loop_clrRAM:

; initiation of an AT timer interrupt with ; the period of 50us

7/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

ld ATRH,a ld a,#$70 ld ATRL,a ld a,#%00010010 ld ATCSR,a rim ;********************************************************************** ;Main loop of the program ;********************************************************************** IDLE: btjf FLAGS0,#Nw_adc,Idle ; waiting for the conversion result bres FLAGS0,#Nw_adc ; new result ; sending the conversion result ; through RS ; frame format: ;0FFh,0FFh,Rez_H,Rez_L

ld a,#$FF call Send_rs ld a,#$FF call Send_rs ld a,Rez_h call Send_rs ld a,Rez_l call Send_rs jra IDLE ;********************************************************************** ;Interrupts ;********************************************************************** ; delta/sigma conversion ; sampling of 1 bit with period of 50us ; conversion result- 10 bit word, received every (1024*50us)=51,2ms ;********************************************************************** timoverfl_rt: bres ATCSR,#2 ; cancelling of the interrupt re; quest ld a,#00000100 ; adding the amplifier into the A/D ; processing ld ADCCAMP,a ld a,#%01100001 ; voltage measurement at AIN1 ld ADCCSR,a loop_adc: btjf ADCCSR,#7,loop_adc ld a,ADCDR cp a,#$37 ; comparison U_ain1 z 037h jrc set_Dlt bres PBDR,#Dlt_out ; U_ain1>037h inc Adc_l ; increase of the conversion result

8/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

set_Dlt: inc_loop:

jrne inc_loop inc Adc_h jra inc_loop bset PBDR,#Dlt_out bset FLAGS0,#m50us inc Loop_l jrne tst_loop inc Loop_h ld a,Loop_l jreq tst_loopH iret ld a,Loop_h cp a,#$04 jreq ok_knw iret clr Loop_l clr Loop_h ld a,Adc_h ld Rez_h,a ld a,Adc_l ld Rez_l,a clr Adc_l

; U_ain1<037h ; setting of a marker 50us ; increase of the samples counter

tst_loop:

; is the samples counter equal to ; 1024?

tst_loopH:

; yes ; ; ; ; ; conversion completed initiating of the loop conversion counter rewriting of the result into Rez_h,Rez_l

ok_knw:

; initiating of the conversion re; sult variable

clr Adc_h bset FLAGS0,#Nw_adc ; marker for IDLE (data ready) iret ;********************************************************************** spi_rt iret lttimrtc_rt iret ltimoutcmp_rt iret timoutcmp_rt iret lvd_rt iret ext3_rt iret ext2_rt iret ext1_rt iret ext0_rt iret sw_rt iret dummy iret ;********************************************************************** ;Procedures and subprograms ;**********************************************************************

9/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

Send_rs:

loop_snd:

Send_bt:

sd_H: wait:

bres FLAGS0,#m50us call wait bres PADR,#RS call wait ld x,#$08 rrc a call Send_bt dec x jrne loop_snd bset PADR,#RS jra wait jrc sd_H bres PADR,#RS jra wait bset PADR,#RS

; procedure of RS data byte sending ; 19200bps,1b start,1b stop,8b data ; setting of a start bit

; setting of 8 data bits

; setting of a stop bit ; setting of a data bit at the port

btjf FLAGS0,#m50us,wait ; latency for the duration of the ; data bit bres FLAGS0,#m50us ret ;********************************************************************** ;Interrupt vectors segment 'vectit' ;********************************************************************** DC.W dummy ; FFE0-FFF1h location spi_it DC.W spi_rt ; FFE2-FFE3h location lttimrtc_it DC.W lttimrtc_rt ; FFE4-FFE5h location ltimoutcmp_it DC.W ltimoutcmp_rt ; FFE6-FFE7h location timoverfl_it DC.W timoverfl_rt ; FFE8-FFE9h location timoutcmp_it DC.W timoutcmp_rt ; FFEA-FFEBh location lvd_it DC.W lvd_rt ; FFEC-FFEDh location DC.W dummy ; FFEE-FFEFh location DC.W dummy ; FFF0-FFF1h location ext3_it DC.W ext3_rt ; FFF2-FFF3h location ext2_it DC.W ext2_rt ; FFF4-FFF5h location ext1_it DC.W ext1_rt ; FFF6-FFF7h location ext0_it DC.W ext0_rt ; FFF8-FFF9h location DC.W dummy ; FFFA-FFFBh location softit DC.W sw_rt ; FFFC-FFFDh location reset DC.W INIT ; FFFE-FFFFh location end

10/11

IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09

THE PRESENT NOTE WHICH IS FOR GUIDANCE ONLY AIMS AT PROVIDING CUSTOMERS WITH INFORMATION REGARDING THEIR PRODUCTS IN ORDER FOR THEM TO SAVE TIME. AS A RESULT, STMICROELECTRONICS SHALL NOT BE HELD LIABLE FOR ANY DIRECT, INDIRECT OR CONSEQUENTIAL DAMAGES WITH RESPECT TO ANY CLAIMS ARISING FROM THE CONTENT OF SUCH A NOTE AND/OR THE USE MADE BY CUSTOMERS OF THE INFORMATION CONTAINED HEREIN IN CONNECTION WITH THEIR PRODUCTS.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners 2004 STMicroelectronics - All rights reserved STMicroelectronics GROUP OF COMPANIES Australia Belgium - Brazil - Canada - China Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States www.st.com

11/11

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Hiquad 64Dokumen1 halamanHiquad 64Dan EsentherBelum ada peringkat

- Powerso16: Outline and Mechanical DataDokumen1 halamanPowerso16: Outline and Mechanical DataDan EsentherBelum ada peringkat

- Pso 36Dokumen1 halamanPso 36Dan EsentherBelum ada peringkat

- PSSO-12 Mechanical Data: Dim. Mm. Min. TYP MaxDokumen1 halamanPSSO-12 Mechanical Data: Dim. Mm. Min. TYP MaxDan EsentherBelum ada peringkat

- Powersso-24 Mechanical Data: Dim. Mm. Min. Typ MaxDokumen1 halamanPowersso-24 Mechanical Data: Dim. Mm. Min. Typ MaxDan EsentherBelum ada peringkat

- Powerso-20 Mechanical Data: Dim. Mm. Inch Min. TYP Max. Min. Typ. MaxDokumen1 halamanPowerso-20 Mechanical Data: Dim. Mm. Inch Min. TYP Max. Min. Typ. MaxDan EsentherBelum ada peringkat

- 10833Dokumen18 halaman10833Dan EsentherBelum ada peringkat

- Ppak Mechanical Data: Dim. Min. TYP MaxDokumen1 halamanPpak Mechanical Data: Dim. Min. TYP MaxDan EsentherBelum ada peringkat

- Powerso-10 Mechanical Data: Dim. Mm. Inch Min. Typ Max. Min. Typ. MaxDokumen1 halamanPowerso-10 Mechanical Data: Dim. Mm. Inch Min. Typ Max. Min. Typ. MaxDan EsentherBelum ada peringkat

- L9929Dokumen3 halamanL9929Dan EsentherBelum ada peringkat

- 10832Dokumen26 halaman10832Dan EsentherBelum ada peringkat

- 9696Dokumen17 halaman9696Dan EsentherBelum ada peringkat

- Multipowerso-30 Mechanical Data: Dim. Mm. Min. Typ MaxDokumen1 halamanMultipowerso-30 Mechanical Data: Dim. Mm. Min. Typ MaxDan EsentherBelum ada peringkat

- Fully Integrated H-Bridge Motor Driver: VNH3SP30Dokumen26 halamanFully Integrated H-Bridge Motor Driver: VNH3SP30Dan EsentherBelum ada peringkat

- Uh 30Dokumen10 halamanUh 30Dan EsentherBelum ada peringkat

- VNQ830A-E: Quad Channel High Side DriverDokumen17 halamanVNQ830A-E: Quad Channel High Side DriverDan EsentherBelum ada peringkat

- 10831Dokumen21 halaman10831Dan EsentherBelum ada peringkat

- 10683Dokumen19 halaman10683Dan EsentherBelum ada peringkat

- 10311Dokumen23 halaman10311Dan Esenther100% (1)

- 10830Dokumen21 halaman10830Dan EsentherBelum ada peringkat

- 10302Dokumen4 halaman10302Dan EsentherBelum ada peringkat

- 10022Dokumen262 halaman10022Dan EsentherBelum ada peringkat

- 10303Dokumen5 halaman10303Dan EsentherBelum ada peringkat

- VND830PEP-E: Double Channel High Side DriverDokumen13 halamanVND830PEP-E: Double Channel High Side DriverDan EsentherBelum ada peringkat

- 10640Dokumen22 halaman10640Dan EsentherBelum ada peringkat

- 10261Dokumen10 halaman10261Dan EsentherBelum ada peringkat

- 9927Dokumen11 halaman9927Dan EsentherBelum ada peringkat

- 9934Dokumen11 halaman9934Dan EsentherBelum ada peringkat

- 9933Dokumen11 halaman9933Dan EsentherBelum ada peringkat

- 9792Dokumen21 halaman9792Dan EsentherBelum ada peringkat

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (120)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- JFET Voltage-Controlled ResistorsDokumen4 halamanJFET Voltage-Controlled ResistorsfdmoitaBelum ada peringkat

- Roland - Support - Aerophone AE-10 - Support Documents04Dokumen5 halamanRoland - Support - Aerophone AE-10 - Support Documents04em4guBelum ada peringkat

- Vienna in Your PocketDokumen68 halamanVienna in Your PocketccoccinellaBelum ada peringkat

- 10ec71 NotesDokumen129 halaman10ec71 NotesMSAMHOURIBelum ada peringkat

- Yann Tiersen - Comptine D'un Autre Été PDFDokumen2 halamanYann Tiersen - Comptine D'un Autre Été PDFkinBelum ada peringkat

- Quick Minds 4 Test U0-1Dokumen3 halamanQuick Minds 4 Test U0-1jarranbo725% (4)

- Mku ChaplaincyDokumen13 halamanMku ChaplaincyPeterson AbugaBelum ada peringkat

- 6Dokumen36 halaman6nuno almeidaBelum ada peringkat

- Class Activity 012 - Unit 6-Lesson A-B-Life 3 (1) GermaniaDokumen8 halamanClass Activity 012 - Unit 6-Lesson A-B-Life 3 (1) GermaniaALONSO JARAMILLO HIDALGOBelum ada peringkat

- En Iniya Pon Nilave - Guitar Notes PDFDokumen2 halamanEn Iniya Pon Nilave - Guitar Notes PDFitzarun83% (6)

- District Supervisor of Polomolok East District, Mrs. Ramona C Bangoc.. Ma'amDokumen2 halamanDistrict Supervisor of Polomolok East District, Mrs. Ramona C Bangoc.. Ma'amLoraine DiazonBelum ada peringkat

- Khatib Dissertation FinalDokumen193 halamanKhatib Dissertation FinalMonalisa MohantyBelum ada peringkat

- TMEG 211 Teaching MUSICDokumen8 halamanTMEG 211 Teaching MUSICAngel ChiutenaBelum ada peringkat

- Face Your Fears: From Crazy Ex-Girlfriend Season 1Dokumen11 halamanFace Your Fears: From Crazy Ex-Girlfriend Season 1nitsuj888Belum ada peringkat

- TD Acentic IntegrationDokumen3 halamanTD Acentic IntegrationVishal SuryawaniBelum ada peringkat

- Marcha - Nupcial Violin and CelloDokumen1 halamanMarcha - Nupcial Violin and CelloRene Victor Adm ABelum ada peringkat

- 11 06 2017 Eo4 Ge PDFDokumen25 halaman11 06 2017 Eo4 Ge PDFAlex PrabhuBelum ada peringkat

- 7SJ80xx TechDaten V0470 EnUSDokumen80 halaman7SJ80xx TechDaten V0470 EnUSPrabhu ChandranBelum ada peringkat

- 2302 01329 PDFDokumen18 halaman2302 01329 PDFAsusBelum ada peringkat

- 3003 Augmented Intervals - MusDokumen1 halaman3003 Augmented Intervals - Mussummerludlow100% (1)

- Musical Instrument LPDokumen4 halamanMusical Instrument LPAdrian Zack ArcillaBelum ada peringkat

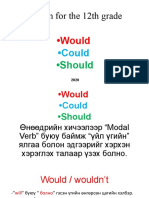

- Lesson For The 12th Grade: - WouldDokumen15 halamanLesson For The 12th Grade: - WouldDulamsuren DulmaaBelum ada peringkat

- Electricity & Magnetism-Basic PrinciplesDokumen21 halamanElectricity & Magnetism-Basic PrinciplesJunimar AggabaoBelum ada peringkat

- Top 200 Dance Hits of The 80'sDokumen4 halamanTop 200 Dance Hits of The 80'sHoracio MarmotoBelum ada peringkat

- Who Lives in A Pineapple Under The SeaDokumen3 halamanWho Lives in A Pineapple Under The Seashamaya fraserBelum ada peringkat

- New York Bus MapDokumen1 halamanNew York Bus MapSzabBelum ada peringkat

- Bahasa Indonesia - Indonesian Traditional DanceDokumen38 halamanBahasa Indonesia - Indonesian Traditional Dancelukman_filesBelum ada peringkat

- There Will Never Be - BassDokumen3 halamanThere Will Never Be - BasseugenioBelum ada peringkat

- Name: - Date: - Grade and Section: - ScoreDokumen2 halamanName: - Date: - Grade and Section: - Scoregabby ilaganBelum ada peringkat

- Life of Waheed Murad (In English)Dokumen36 halamanLife of Waheed Murad (In English)PlatonicBelum ada peringkat