Automatic Teller Machine For Visually Impaired: Muthyammal Engineering College

Diunggah oleh

kvinothscetDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Automatic Teller Machine For Visually Impaired: Muthyammal Engineering College

Diunggah oleh

kvinothscetHak Cipta:

Format Tersedia

AUTOMATIC TELLER

MACHINE FOR

VISUALLY IMPAIRED

MUTHYAMMAL ENGINEERING COLLEGE

SUBMITTED BY

CONTACT NO:

7418128674

S.Monish Kumar,

(monishkumar.17@gmail.com).

T.Santhosh Kumar,

(santhoshgoolyy@gmail.com).

ABSTRACT

also helps them to hear a clear recorded

This paper is designed in a

voice for any transactions in ATM. Its

manner which enhances the social

more secure when head phone is

awareness and even leads physically

introduced to maintain security. This

challenged people can come across the

system can also be used by the aged

improvement in current technologies.

people and normal people

We here by introduce this system for the

gifted

people

to

operate

in

their

EMBEDDED SYSTEM

convenience. It is a secure method of

An embedded system is a

performing financial transactions in a

special-purpose computer controlled

public place without the need from

electro-mechanical system in which

others. There is no need to carry cash in

the

their hands.

encapsulated

compared

ATM is safer when

with

ordinary

banking

transaction.

computer

by

is

completely

the

device

it

controls. An embedded system has

specific requirements and performs

In normal ATM,

pre-defined tasks, unlike a general-

all the functions are performed through

purpose personal computer. The

text format and balance amount is in the

core of any embedded system is a

form

microprocessor,

of

printed

format.

Visually

programmed

to

impaired cant recognize those formats.

perform a few tasks (often just one

For that Braille keypad is used in the

task).

place of normal keypad. This project

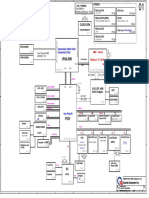

BLOCK DIAGRAM OF ATM FOR VISUALLY IMPAIRED

LCD

ATM CARD

(EEPROM)

PIC

16F877A

CHIPCORDER

(ISD 2560)

4

7

A

5

8

0

6

9

B

HEAD PHONE

Braille keyboard

ATM card (EEPROM card) is

BLOCK DIAGRAM DESCRIPTION

AND EXPLANATION

provided to the visually impaired and by

inserting it into card reader to check

Our aim is to make the proper use

their identification. PIC can identify the

of ATM for visually impaired. They are

entered user is blind or normal people by

in need to perform money transactions

the user number which is stored in

like money withdrawal and Balance

EEPROM. For more security, the LCD

checking. Normal people can perform

will turns OFF for the blind people.

these transactions with the help of

Liquid Crystal Display.

With

the

help

of

Braille

(specially designed for the visually

impaired) keypad they can enter their pin

the amount, the controller makes sure

number. The controller checks whether

whether the amount is sufficient to

the typed pin number is matched with

withdraw or not. If it is insufficient it

the user ID and if it is not matched it will

will say that the amount is insufficient.

ask to repeat the process once again with

The typed amount is less than the

the help of audio interface.

savings amount and minimum balance

Now the visually impaired can

amount, the money withdrawal takes

hear the passage which is stored in CHIP

place. After the money transaction the

CORDER, whether they are going to

amount is reduced from the savings

check the balance or money withdrawal.

account of the customer.

This can be accessed by pressing

1 for balance

checking and

2 for money

withdrawal.

MICROCONTROLLER

A microcontroller is a computer.

All computers - whether we are talking

about a personal desktop computer or a

large mainframe computer or a

microcontroller have several things in

common

CHIP CORDER is interfaced

with

microcontroller.

The

visually

impaired can hear the voice through

head phone. When the key1 is pressed

16F877A PIC

MICROCONTROLLER

the

This device is one of the most

customer needs to check the balance

popular microcontrollers in use today.

amount and it says the balance with the

Appropriately, the term PIC stands for

help of head phone.

Programmable Interface Controller Most

the

controller

recognizes

that,

When the person presses the key

2 the controller performs the money

withdrawal operation. The controller

checks the accounts of the particular

customer and asks the customer to type

the amount for withdrawal. After typing

desktop computers use von Neumann

architecture, which means that programs

and data share a single memory area that

is accessed over a common bus. This

scheme works well for general use

computers but may not be of particular

advantage for microcontrollers. This is

An EEPROM (also called an

one reason that the PIC microcontroller

E2PROM) or Electronically Erasable

uses Harvard architecture. This design

Programmable Read-Only Memory is a

uses separate memory areas and buses

non-volatile

for data and programs.

Harvard

computers and other devices to store

architecture allows the instruction bus to

small amounts of volatile (configuration)

be a different width than the data bus.

data. When larger amounts of more

According to Microchip instruction can

static data are to be stored (such as in

execute while the next one is being

USB flash drives) other memory types

fetched, all while data memory is

like flash memory are more economical.

storage

chip

used

in

simultaneously being accessed.

Pin Diagram of 16F877A

IC93C56 EEPROM

General description

The AT93C46/56/66 provides

1024/2048/4096 bits of serial electrically

erasable

programmable

memory

(EEPROM)

read

organized

only

as

64/128/256 words of 16 bits each.

When the ORG pin is connected

to VCC and 128/256/512 words of 8 bits

each when it is tied to ground. The

Fig. no: 1.2

device is optimized for use in many

industrial and commercial applications

where low power and low voltage

EEPROM

operations are essential.

The AT93C46/56/66 is enabled

through the Chip Select pin (CS), and

accessed via a 3-wire serial interface

Fig. no: 1.3

consisting of Data Input (DI), Data

Output (DO), and Shift Clock (SK)

Upon receiving a READ instruction at

DI, the address is decoded and the data

is clocked out serially on the data output

pin DO. The WRITE cycle is completely

self-timed and no separate ERASE cycle

is required before WRITE. The WRITE

Pin Diagram

cycle is only enabled when the part is in

the ERASE/WRITE ENABLE state.

When CS is brought high following

the initiation of a WRITE cycle, the DO

pin

outputs the READY/BUSY status of the

part.

This is one type of serial

communication module in the PIC. For

writing into the EEPROM initially the

3.2.3 CONNECTIONS BETWEEN

SPI initialization has to be done.

EEPROM AND PIC 16F877A

This is the module into which we

permanently write the user number, PIN

number

and

balance

amount.

The

EEPROM is an SPI module i.e. special

peripheral interface module.

We have connected four pins of

PORT C for specific purposes such as

1. Port C, 3rd pin for clock signal.

2. Port C, 5th pin for data output.

3. Port C, 4th pin for data input.

4. Port E, 2nd pin for chip select.

BRALLIE KEYBOARD:

VCC

10

RE2

CS

18

PIC 16F877A

24

SCK

SK

23

SD0

D1

RE2

SDI

D2

8

7

93C56

Braille can be seen as the world's

first binary encoding scheme for

representing the characters of a writing

system for visually impaired.

CONNECTION DIAGRAM

Fig. no: 1.5

3. Encode the key press(produce a

standard code for the press key)

The three tasks can be done with

hardware, software, or a combination of

the two, depending on the application.

We will first show you how they can be

done with software, as might be done in

a microprocessor-based grosery scale

where the microprocessor is not pressed

for time. Later we describe some

hardware devices which do these tasks.

The rows of the matrix are

connected to four output port lines. The

column lines of the matrix are connected

to four input-port lines. To make the

program simpler, the row lines are also

Description

connected to four input lines.

In most keyboards, the key

When no keys are pressed, the

switches are connected in a matrix of

column lines are held high by the pull-up

rows and columns. We will use simple

resistors connected to +5v. Pressing a

mechanical switches for our examples

key connects a row to a column. If a low

here, but the principle is the same for

is output on a row and key in that row is

other

Getting

pressed, then the low will appear on the

meaningful data from a keyboard such as

column which contains that key and can

this requires the following three major

be detected on the input port. If the row

tasks

and the column of the pressed key is

types

of

switches.

known,

then

it

can

convert

this

1. Detect a key press

information into any code to represent

2. Debounce the key press

that key. An easy way to detect if any

key in the matrix is pressed is to output

columns are read. If none of the columns

0's to all the rows and

is low, the pressed key is not in that row,

then check the columns to see if a

so the low is rotated to the next row and

pressed key has connected a low to a

the columns are checked again.

column. First output lows to all the rows

The process is repeated until a

and check the columns over and over

low on a row produces a low on one of

until the columns are all high. This is

the columns. The pressed key then is in

done to make sure a previous key has

the row which is low at that time. The

been released before looking for the next

byte read in from the input port will

one. In standard keyboard terminology,

contain a 4-bit code which represents the

this is called two-key lockout. Once the

row of the pressed key and a 4-bit code

columns are found to be all high, the

which represents the column of the

program enters another loop, which

pressed key.

waits until a low appears on one of the

columns, indicating that a key has been

pressed. This second loop does the

detect task for us. A simple 20-ms delay

procedure then does the Debounce task.

CHIP CORDER

INTRODUCTION

After the Debounce time, another

Chip Corder is a voice IC used to

check is made to see if the key is still

record audio signals. In this project it

pressed. If the columns are now all high,

plays the major role. Visually impaired

then no key is pressed. If any of the

can hear a clear recorded voice with the

columns

the

help of this IC. Winbonds ISD 2560 is

assumption is made that it was a valid

an IC which is capable of recording data

keypress.

of 60 seconds.

are

still

low,

then

The final task is to determine the

OPERATIONAL MODES

row and column of the pressed key and

The ISD 2560 is designed with

convert this row and column information

several built in operational modes that

to the hex code for the pressed key. To

provides maximum functionality with

get the row and column information, a

minimum external components. The

low is output to one row and the

modes are accessed via the address pins

& mapped beyond the normal message

address range. There are two important

M5

considerations for using operational

modes.

CE level

message

Allows

activated

message

M6

All operations begin initially at

address 0 of its memory. The

Push

pausing

Simplified

Button

device

control

interface

address pointer is resets to 0when

the device is changed record to

playback.

Operational modes description

Operational modes are executed

M0 and M6 modes are more

when CE goes LOW. This mode

convenient

to

interface

with

remains in effect until the next

microcontroller for record and playback

LOW going CE signal ,at which

applications.

point the current modes are

sampled & executed

M0-message cueing

It allows the user to skip through

messages, without knowing the actual

Various modes

Mode

M0

address of each message. Each CE pulse

Function

Message

Typical use

Fast

cueing

forwarding

causes the internal address pointer to skip

to the next message. This mode is used for

playback only.

through

M1

Delete EOM

message

EOM at the

end of last

M2

Not

M3

applicable

Looping

M4

Consecutive

addressing

message

Reserved

M6 Push Button mode

It

external

is

designed

circuitry

and

to

minimize

components,

thereby reducing system cost. In order to

configure the device in M6 mode, the

Continuous

two MSB bits must be HIGH and M6

playback

mode pin must also be HIGH. When this

from addr 0

P/R multiple

Operational mode is implemented, three

consecutive

of the pins on the device have alternative

or a record cycle is in progress and a

functionality as given

HIGH going pulse is observed on PD,

the current cycle is terminated and the

CE^

Start/Pause Push-

Button (low pulse activated)

PD

the beginning of the message space.

Stop/reset Push-

Button (high pulse activated)

EOM^

address pointer is reset to address zero,

EOM^ (RUN)

In push button operational mode

Active HIGH run

indicator

EOM^ becomes an active HIGH run

signal which can be used to drive an

CE^ (START/PAUSE)

In push button operational mode,

CE^ acts as low going pulse-activated

LED or other external device. It is HIGH

whenever a record or playback operation

is in progress.

START/PAUSE signal. If no operation

is currently in progress, a LOW-going

pulse on this signal will initiate a

CONCLUSION

playback or record cycle according to

the level on the P/R^ pin. A subsequent

pulse on the CE^ pin, before an EOM^ is

Our project ATM for

reached in playback or an overflow

visually impaired is designed in a

condition occurs, will pause the current

manner which enhances with social

operation, and the address counter is not

awareness and even leads physically

reset. Another CE^ pulse will cause the

challenged people can come across the

device to continue the operation from the

improvement in current technologies.

place where it is paused.

We here by introduce this system for the

gifted

people

convenience.

PD (STOP/RESET)

to

If

operate

Banks

in

starts

their

to

implement this latest feature, this project

In push button operational mode,

gains more importance and there is a

PD acts as a HIGH going pulse-activated

chance for further enhancements and

STOP/RESET signal. When a playback

developments in the future.

Anda mungkin juga menyukai

- Understanding Computers, Smartphones and the InternetDari EverandUnderstanding Computers, Smartphones and the InternetPenilaian: 5 dari 5 bintang5/5 (1)

- Scanning and Identifying The KeyDokumen9 halamanScanning and Identifying The Keyniravsoni001Belum ada peringkat

- Unit V Peripheral InterfacingDokumen38 halamanUnit V Peripheral Interfacingsuperkan61950% (2)

- Peripheral Interfacing: Dr.P.Yogesh, Senior Lecturer, DCSE, CEG Campus, Anna University, Chennai-25Dokumen57 halamanPeripheral Interfacing: Dr.P.Yogesh, Senior Lecturer, DCSE, CEG Campus, Anna University, Chennai-25Mansoor AliBelum ada peringkat

- Unit 5Dokumen62 halamanUnit 5aravind981Belum ada peringkat

- Intefacing Avr Keyboard Doc2532Dokumen11 halamanIntefacing Avr Keyboard Doc2532Andy MarioBelum ada peringkat

- Keypad ScanningDokumen11 halamanKeypad Scanningrose8051Belum ada peringkat

- Programmable Number Lock SystemDokumen19 halamanProgrammable Number Lock Systemchetan379Belum ada peringkat

- MPMCDokumen19 halamanMPMCsietkspot23Belum ada peringkat

- Index: S.No Experiment Name Date SignDokumen42 halamanIndex: S.No Experiment Name Date SignSushant TanejaBelum ada peringkat

- Microcontroller PartsDokumen6 halamanMicrocontroller Partsapi-195761152Belum ada peringkat

- Vending MachineDokumen12 halamanVending MachineChetan PatilBelum ada peringkat

- Microcontroller Based Digital Code LockDokumen2 halamanMicrocontroller Based Digital Code LockHcv Prasad KacharlaBelum ada peringkat

- BVM-Seminar PPT NEWDokumen29 halamanBVM-Seminar PPT NEWSandeep JonathanBelum ada peringkat

- Carmely - Using Finite State Machines To Design Software PDFDokumen8 halamanCarmely - Using Finite State Machines To Design Software PDFRodrigo CedrimBelum ada peringkat

- Generalities On UcsDokumen11 halamanGeneralities On Ucsmarshal galilee djitsaBelum ada peringkat

- E-Wallet PPT 1Dokumen28 halamanE-Wallet PPT 1Javvadi Jyothi Prasad100% (1)

- GSM Based Electronic Voting Machine (Autosaved)Dokumen17 halamanGSM Based Electronic Voting Machine (Autosaved)Abhishek IyengarBelum ada peringkat

- Computer Organization and ArchitectureDokumen55 halamanComputer Organization and ArchitectureArdale PalilloBelum ada peringkat

- EDSIMDokumen44 halamanEDSIMsania20110% (1)

- IvrsDokumen11 halamanIvrsMuskan JainBelum ada peringkat

- Microcontroller Tutorials 1: What Is An Embedded System?Dokumen12 halamanMicrocontroller Tutorials 1: What Is An Embedded System?KBSMANITBelum ada peringkat

- Quiz BuzzerDokumen18 halamanQuiz BuzzerSatyam Lala100% (1)

- PLC IntroductionDokumen18 halamanPLC IntroductionVictorBelum ada peringkat

- 8 TemparatureDokumen31 halaman8 TemparatureDemonfox NarutoUzumakiBelum ada peringkat

- E Wallet PPT 1Dokumen29 halamanE Wallet PPT 1narwanimonishBelum ada peringkat

- Sms Based Notice BoardDokumen39 halamanSms Based Notice Boardreddu143Belum ada peringkat

- Microcontroller Based System Design: Programmable Number Lock SystemDokumen4 halamanMicrocontroller Based System Design: Programmable Number Lock Systemthamaraiselvi40Belum ada peringkat

- Department of Engineering Project Report Title:-8051 Based Digital Code LockDokumen18 halamanDepartment of Engineering Project Report Title:-8051 Based Digital Code LockamitmaheshpurBelum ada peringkat

- PYE 422 Lecture NoteDokumen11 halamanPYE 422 Lecture Notecoker yusufBelum ada peringkat

- Architecture of Specific PLC ControllerDokumen11 halamanArchitecture of Specific PLC ControllerDazuky UkyBelum ada peringkat

- 8051 Micro Controller HandbookDokumen109 halaman8051 Micro Controller HandbookSanthosh sBelum ada peringkat

- Machine CrusherDokumen37 halamanMachine CrusherImin GundamBelum ada peringkat

- Password Based Door LockingDokumen4 halamanPassword Based Door LockingAswathi SruthiBelum ada peringkat

- WIRELESS GESTURE CONTROLLED ROBOT WITH VOICE AND VIDEO CAMERA NewDokumen83 halamanWIRELESS GESTURE CONTROLLED ROBOT WITH VOICE AND VIDEO CAMERA NewSuchitra SwarnaBelum ada peringkat

- B.ram Lecture 1 2Dokumen11 halamanB.ram Lecture 1 2Yamini GollepallyBelum ada peringkat

- Learning Path and Time: B010-PLC BasicsDokumen10 halamanLearning Path and Time: B010-PLC BasicsPratab VijayanBelum ada peringkat

- Special Function RegisterDokumen44 halamanSpecial Function Registercoolkanna100% (2)

- Presented By:: Charanjit. Vig Chetna - Bhat Devdatt - Kamble Meghna - Pednekar Satinder - Aggarwal Sumeet - SinghDokumen60 halamanPresented By:: Charanjit. Vig Chetna - Bhat Devdatt - Kamble Meghna - Pednekar Satinder - Aggarwal Sumeet - SinghaveegoBelum ada peringkat

- Automatas Curso PLC Basico Siemens PDFDokumen27 halamanAutomatas Curso PLC Basico Siemens PDFClaudio PerezBelum ada peringkat

- Lab 01 - Introduction To PLC Hardware and SoftwareDokumen18 halamanLab 01 - Introduction To PLC Hardware and SoftwareSyed Abdullah Hasan Chishti100% (1)

- PLC Software: Hand Held ProgrammerDokumen11 halamanPLC Software: Hand Held Programmervamsidar47Belum ada peringkat

- NTCC Report by Vivek, Enrollment No - A7605216081Dokumen24 halamanNTCC Report by Vivek, Enrollment No - A7605216081Vivek SinghBelum ada peringkat

- E Wallet PPT 1Dokumen30 halamanE Wallet PPT 1Adam BookerBelum ada peringkat

- Door Locking SystemDokumen19 halamanDoor Locking SystemChandra Mouli Reddy DasariBelum ada peringkat

- PBX V600 ManualDokumen55 halamanPBX V600 Manualpeugeniu_1Belum ada peringkat

- Microcontroller Based Digital Lock SystemDokumen40 halamanMicrocontroller Based Digital Lock Systemajayjhajhria21100% (1)

- Pic Based LockDokumen5 halamanPic Based LockamshahidBelum ada peringkat

- Shuffling of Keypad For Securing Electronic GadgetsDokumen87 halamanShuffling of Keypad For Securing Electronic GadgetsMadhurendra Kumar Madhukar100% (1)

- Manual PLC - SiemensDokumen39 halamanManual PLC - SiemensFederico Siojrin100% (1)

- PROJECT Report On Digital Code LockDokumen21 halamanPROJECT Report On Digital Code LockVishu GroverBelum ada peringkat

- D 1295042413Dokumen4 halamanD 1295042413Norbert DeakBelum ada peringkat

- Introduction To Computer Architecture What Is The Computer Architecture?Dokumen7 halamanIntroduction To Computer Architecture What Is The Computer Architecture?alinma76Belum ada peringkat

- Microprocessor and Assembly Language Lecture Note For Ndii Computer EngineeringDokumen25 halamanMicroprocessor and Assembly Language Lecture Note For Ndii Computer EngineeringAbdulhamid DaudaBelum ada peringkat

- Peripheral Interfacing: 1 Parallel Interface AdapterDokumen5 halamanPeripheral Interfacing: 1 Parallel Interface Adapteratmroo9Belum ada peringkat

- Multibank Account With Single Pin Access Smart Card Using Lab ViewDokumen4 halamanMultibank Account With Single Pin Access Smart Card Using Lab ViewSrinivasan SubramanianBelum ada peringkat

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Dari EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Belum ada peringkat

- Constitution Assembly Features and Sources of Constitution Citizenship 1 70Dokumen52 halamanConstitution Assembly Features and Sources of Constitution Citizenship 1 70kvinothscetBelum ada peringkat

- Single Answer Type Questions Photoelectric Effect:: Dual NatureDokumen16 halamanSingle Answer Type Questions Photoelectric Effect:: Dual NaturekvinothscetBelum ada peringkat

- List of Chief Ministers & Governors of Indian StatesDokumen3 halamanList of Chief Ministers & Governors of Indian StateskvinothscetBelum ada peringkat

- 7-Bahmani and Vijayanagar Kingdom - EMDokumen10 halaman7-Bahmani and Vijayanagar Kingdom - EMkvinothscetBelum ada peringkat

- Illumination Invariant Face Detection Using Viola Jones AlgorithmDokumen4 halamanIllumination Invariant Face Detection Using Viola Jones AlgorithmkvinothscetBelum ada peringkat

- Unit - 3: State GovernmentDokumen14 halamanUnit - 3: State GovernmentkvinothscetBelum ada peringkat

- 11-Bahmani and Vijayanagar Kingdom - EMDokumen13 halaman11-Bahmani and Vijayanagar Kingdom - EMkvinothscetBelum ada peringkat

- Objective Questions:: Prepared by K.VinothkumarDokumen8 halamanObjective Questions:: Prepared by K.VinothkumarkvinothscetBelum ada peringkat

- 1 Mukherjee2017 PDFDokumen5 halaman1 Mukherjee2017 PDFkvinothscetBelum ada peringkat

- 4 Ozdil2014Dokumen3 halaman4 Ozdil2014kvinothscetBelum ada peringkat

- EE6201Circuit Theory Unit 1,2,3,4,5Dokumen37 halamanEE6201Circuit Theory Unit 1,2,3,4,5kvinothscetBelum ada peringkat

- 7 Bioinfo - Mi 2011 PDFDokumen5 halaman7 Bioinfo - Mi 2011 PDFkvinothscetBelum ada peringkat

- Salem College of Engineering and Technology SALEM - 636111Dokumen85 halamanSalem College of Engineering and Technology SALEM - 636111kvinothscetBelum ada peringkat

- Fiberoptic Light SourcesDokumen15 halamanFiberoptic Light SourceskvinothscetBelum ada peringkat

- DC I-II Completed K.vinothDokumen9 halamanDC I-II Completed K.vinothkvinothscetBelum ada peringkat

- 2 Fault Types ModelingDokumen9 halaman2 Fault Types ModelingkvinothscetBelum ada peringkat

- Basic FPGA Architectures: Altera XilinxDokumen8 halamanBasic FPGA Architectures: Altera XilinxkvinothscetBelum ada peringkat

- EeeDokumen14 halamanEeekvinothscetBelum ada peringkat

- SIMATIC-SIMOTION Sample ProjectsDokumen2 halamanSIMATIC-SIMOTION Sample ProjectsdracuojiBelum ada peringkat

- 1.4.2.python SlidesDokumen39 halaman1.4.2.python SlidesemilronnbackBelum ada peringkat

- MN CDMQXDokumen260 halamanMN CDMQXJackson Dias RochaBelum ada peringkat

- Oric Tap File FormatDokumen4 halamanOric Tap File Formatrc3molinaBelum ada peringkat

- Saudi Arabia CNA ReportDokumen22 halamanSaudi Arabia CNA ReportCatalin Cimpanu [ZDNet]80% (5)

- DOPUZDokumen3 halamanDOPUZMamanya Kenzie0% (1)

- White Paper Shingled Magnetic Recording Helioseal TechnologyDokumen5 halamanWhite Paper Shingled Magnetic Recording Helioseal TechnologyAlan KonkalBelum ada peringkat

- Software Service Kit For Vacon 100 - User Manual: Received All The Necessary Parts!Dokumen2 halamanSoftware Service Kit For Vacon 100 - User Manual: Received All The Necessary Parts!قلمي كنزىBelum ada peringkat

- Quanta Kl3a R1a 20091223 SchematicsDokumen54 halamanQuanta Kl3a R1a 20091223 SchematicsAlex AlexBelum ada peringkat

- Eckel Torque Control Systems PDFDokumen7 halamanEckel Torque Control Systems PDFMayna Mare100% (2)

- Imaq PrintDokumen314 halamanImaq PrintRebecca RogersBelum ada peringkat

- The Most Complete Starter Kit For UNODokumen158 halamanThe Most Complete Starter Kit For UNOShantan KajjamBelum ada peringkat

- AZ-104 Exam TopicsDokumen208 halamanAZ-104 Exam TopicsSaif Islam100% (1)

- Chapter 1Dokumen45 halamanChapter 1Sou MiaaBelum ada peringkat

- Scripts To Mitigate RisksDokumen26 halamanScripts To Mitigate RisksAbdul Rehman MotanBelum ada peringkat

- Bluetooth Devices Based Access Control System Without Built-In ApplicationDokumen3 halamanBluetooth Devices Based Access Control System Without Built-In ApplicationSiva KanagaSabapathyBelum ada peringkat

- 8.3.3.3 Lab - Collecting and Analyzing NetFlow Data - ILM PDFDokumen13 halaman8.3.3.3 Lab - Collecting and Analyzing NetFlow Data - ILM PDFEl Amrani MoutiaBelum ada peringkat

- What Is The Difference Between A 32 64 BitDokumen2 halamanWhat Is The Difference Between A 32 64 BitDavid SofitaBelum ada peringkat

- Selenium Interview Questions For Experienced and FreshersDokumen24 halamanSelenium Interview Questions For Experienced and FresherssachinBelum ada peringkat

- Power Logger Viewer: Instruction ManualDokumen118 halamanPower Logger Viewer: Instruction ManualjoseBelum ada peringkat

- 2.4G Transceiver NRF24L01 Module User's Manual v2.0Dokumen12 halaman2.4G Transceiver NRF24L01 Module User's Manual v2.0Nina FloydBelum ada peringkat

- C Tadm51 731Dokumen4 halamanC Tadm51 731we003820% (5)

- Technical Documentation: Product Application Programming Interface (English)Dokumen50 halamanTechnical Documentation: Product Application Programming Interface (English)Pamungkas JayudaBelum ada peringkat

- Computer Abbreviations in PDFDokumen4 halamanComputer Abbreviations in PDFMarian Jakielou Leona SomeraBelum ada peringkat

- Css Computer Science 2021Dokumen2 halamanCss Computer Science 2021Hamza KhanBelum ada peringkat

- Emulex Drivers For Vmware Esxi For Lightpulse Adapters Release NotesDokumen5 halamanEmulex Drivers For Vmware Esxi For Lightpulse Adapters Release NotesJohanz RoqueBelum ada peringkat

- Chapter 5 - Cookies and SessionsDokumen12 halamanChapter 5 - Cookies and Sessionsወንድወሰን እርገጤBelum ada peringkat

- DIT 0305 Object Oriented Analysis and DesignDokumen2 halamanDIT 0305 Object Oriented Analysis and DesignIANBelum ada peringkat

- RP DatasheetDokumen128 halamanRP DatasheetJonathan Cando100% (1)

- Mounting and Unmounting The CD-ROM Drive OnDokumen8 halamanMounting and Unmounting The CD-ROM Drive OnMira NayrouzBelum ada peringkat