Special Issue On Networks-on-Chip: Call For Papers

Diunggah oleh

Jit JagDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Special Issue On Networks-on-Chip: Call For Papers

Diunggah oleh

Jit JagHak Cipta:

Format Tersedia

VLSI Design

Special Issue on Networks-on-Chip

Call for Papers

While semiconductor device scaling continues providing greater transistor counts, much of the traditional power benet of scaling has ceased, leading to the current proliferation of parallel computing architectures. To cope with power consumption challenges without sacricing performance in these architectures, Networks-on-Chip (NoC) architectures have replaced bus-based and point-to-point (P2P) interconnect designs. As we approach hundreds and even a thousand cores on the same chip, there are several open problems across all design layers (technology, circuit, microarchitecture, and application) that require revolutionary approaches from a wide range of disciplines. This special issue on Networks-on-Chip, scheduled to appear in March 2013, seeks original and ambitious manuscripts advancing the state of the art in both theory and practice of designing and analyzing NoCs for the many-core era. Potential topics include, but are not limited to:

NoC architectures for CMP/MPSoCs (topology, rout

Verication, debug, and test of NoCs Modeling, simulation, and synthesis of NoCs Metrics and benchmarks for NoCs NoC performance analysis NoC case studies, application-specic NoC design

Before submission authors should carefully read over the journals Author Guidelines, which are located at http://www.hindawi.com/journals/vlsi/guidelines/. Prospective authors should submit an electronic copy of their complete manuscript through the journal Manuscript Tracking System at http://mts.hindawi.com/ according to the following timetable: Manuscript Due First Round of Reviews Publication Date Lead Guest Editor Paul Bogdan, Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA, USA; paulbogdan2010@gmail.com Guest Editors Siddharth Garg, Electrical and Computer Engineering, University of Waterloo, Waterloo, ON, Canada; s6garg@ecemail.uwaterloo.ca Paul V. Gratz, Department of Electrical and Computer Engineering, Texas A&M University, College Station, TX, USA; pgratz@gratz1.com Zhonghai Lu, Department of Electronic Systems, KTH Royal Institute of Technology, Stockholm, Sweden; zhonghai@kth.se Friday, 5 October 2012 Friday, 28 December 2012 Friday, 22 February 2013

ing, switching, ow control, etc.) NoC support for memory and cache access Workload characterization and evaluation Novel interconnect link/switch/router designs Timing, synchronous/asynchronous communication Signaling and circuit design for NoC links Physical design of interconnect and NoC Power, energy, and thermal issues Quality of Service NoCs for real-time multicore systems Network interface issues NoCs for FPGAs and structured ASICs OS support for NoCs and programming models Mapping of applications onto NoCs NoC design for 3D stacked logic and memory Optical and RF for on-chip/in-package interconnects NoC reliability issues Impact of process variations on NoC power/- performance Design methodologies and tools

Hindawi Publishing Corporation http://www.hindawi.com/

Anda mungkin juga menyukai

- Managerial EconomicsDokumen305 halamanManagerial EconomicsDeepu Deepak100% (5)

- Deictic Projection Speakers Being Able To Project Themselves Into Other Locations, Time or Shift Person ReferenceDokumen5 halamanDeictic Projection Speakers Being Able To Project Themselves Into Other Locations, Time or Shift Person ReferencePhan Nguyên50% (2)

- Entrepreneurship DevelopmentDokumen10 halamanEntrepreneurship DevelopmentchecklogsBelum ada peringkat

- Low-Power Variation-Tolerant Design in Nanometer Silicon (Bhunia) (2010)Dokumen456 halamanLow-Power Variation-Tolerant Design in Nanometer Silicon (Bhunia) (2010)Jon HimesBelum ada peringkat

- VLSI Design Lab NewDokumen45 halamanVLSI Design Lab NewmtariqanwarBelum ada peringkat

- Alberto Scandurra Auth., Ian OConnor, Gabriela Nicolescu Eds. Integrated Optical Interconnect Architectures For Embedded Systems1Dokumen276 halamanAlberto Scandurra Auth., Ian OConnor, Gabriela Nicolescu Eds. Integrated Optical Interconnect Architectures For Embedded Systems1Anurag KumarBelum ada peringkat

- School Learning and Development Plan For Head TeachersDokumen3 halamanSchool Learning and Development Plan For Head TeachersLiza Bacudo100% (1)

- Networks-on-Chip: From Implementations to Programming ParadigmsDari EverandNetworks-on-Chip: From Implementations to Programming ParadigmsBelum ada peringkat

- Non-Verbal Communication: by V P BhagatDokumen14 halamanNon-Verbal Communication: by V P BhagatSat SharmaBelum ada peringkat

- Ielts Speaking Part One Long Short Answers PDFDokumen7 halamanIelts Speaking Part One Long Short Answers PDFKaran JariwalaBelum ada peringkat

- Teaching Language in ContextDokumen41 halamanTeaching Language in ContextMárcio da Silva SantosBelum ada peringkat

- Comparative Analysis of Different Topologies Based On Network-on-Chip ArchitecturesDokumen6 halamanComparative Analysis of Different Topologies Based On Network-on-Chip ArchitecturesIJERDBelum ada peringkat

- An Automatic Circuit Design Framework For Level Shifter CircuitsDokumen13 halamanAn Automatic Circuit Design Framework For Level Shifter CircuitsVani YamaniBelum ada peringkat

- Network On-Chip and Its Research Challenges: K. ParamasivamDokumen5 halamanNetwork On-Chip and Its Research Challenges: K. ParamasivamFawaz Labeeb100% (1)

- 1-s2.0-S0167926022000025-mainDokumen10 halaman1-s2.0-S0167926022000025-mainMadhusmita PandaBelum ada peringkat

- PCX - ManishDokumen16 halamanPCX - ManishmanishBelum ada peringkat

- Lords Institute of Engineering & Technology For Women, Chikani (Alwar)Dokumen36 halamanLords Institute of Engineering & Technology For Women, Chikani (Alwar)Sandeep SharmaBelum ada peringkat

- Compare Performance of 2D and 3D Mesh Architectures in Network-On-ChipDokumen5 halamanCompare Performance of 2D and 3D Mesh Architectures in Network-On-ChipJournal of ComputingBelum ada peringkat

- Huang J.+++ (Ed.), Lombardi F. (Ed.) - Design and Test of Digital Circuits by Quantum-DOT Cellular Automata (2007) PDFDokumen380 halamanHuang J.+++ (Ed.), Lombardi F. (Ed.) - Design and Test of Digital Circuits by Quantum-DOT Cellular Automata (2007) PDFSupravatAppaBelum ada peringkat

- FPGA Implementation ON-Chip Communication Using Implementation of 9 Port Router For Ommunication Using V Outer For 3D VerilogDokumen6 halamanFPGA Implementation ON-Chip Communication Using Implementation of 9 Port Router For Ommunication Using V Outer For 3D VerilogPraveen Kumar RBelum ada peringkat

- Vlsi Design - Ec - 701 - Unit - IDokumen37 halamanVlsi Design - Ec - 701 - Unit - Iangelcrystl4774Belum ada peringkat

- NoC Architecture OverviewDokumen5 halamanNoC Architecture OverviewMitali DixitBelum ada peringkat

- Opportunities and Challenges For Photonics in Next-Generation Data Centers - Clint SchowDokumen53 halamanOpportunities and Challenges For Photonics in Next-Generation Data Centers - Clint SchowUCSBieeBelum ada peringkat

- Digital Circuit Design Challenges and Opportunities in The Era of Nanoscale CMOSDokumen23 halamanDigital Circuit Design Challenges and Opportunities in The Era of Nanoscale CMOSTravis BerkBelum ada peringkat

- A Survey On SoCDokumen51 halamanA Survey On SoCLEE KAH YI -Belum ada peringkat

- Noc Topologies01Dokumen16 halamanNoc Topologies01Alex HillBelum ada peringkat

- PHD Thesis On Vlsi DesignDokumen5 halamanPHD Thesis On Vlsi DesignBuyEssaysTulsa100% (2)

- 3 - D ICsDokumen35 halaman3 - D ICsSamhith ReddyBelum ada peringkat

- 3-D Ics Seminar Report 2011-2012Dokumen29 halaman3-D Ics Seminar Report 2011-2012Jamsheer KpBelum ada peringkat

- 3D ICs Reduce Interconnect DelaysDokumen35 halaman3D ICs Reduce Interconnect DelaysKhusi ArnavBelum ada peringkat

- 3 - D ICsDokumen31 halaman3 - D ICsSudheesh VsBelum ada peringkat

- Analog Design Issues in Digital VLSI Circuits and Systems: S.S.JangamDokumen3 halamanAnalog Design Issues in Digital VLSI Circuits and Systems: S.S.JangamMandar MuleBelum ada peringkat

- Design of Efficient Mirror Adder in Quantum-Dot Cellular AutomataDokumen10 halamanDesign of Efficient Mirror Adder in Quantum-Dot Cellular Automataayush srivastavaBelum ada peringkat

- Design and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueDokumen7 halamanDesign and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueGRD JournalsBelum ada peringkat

- No Care A PowerDokumen7 halamanNo Care A PowerVenkateswararao MusalaBelum ada peringkat

- Design of Fault Tolerant Algorithm For Network On Chip Router Using Field Programmable Gate ArrayDokumen8 halamanDesign of Fault Tolerant Algorithm For Network On Chip Router Using Field Programmable Gate ArrayIJRES teamBelum ada peringkat

- Low Power Vlsi Design ThesisDokumen8 halamanLow Power Vlsi Design Thesisafbtabxds100% (1)

- Semi PDFDokumen37 halamanSemi PDFShiva Kumar MkrBelum ada peringkat

- Modified Gdi Technique - A Power Efficient Method For Digital Circuit DesignDokumen23 halamanModified Gdi Technique - A Power Efficient Method For Digital Circuit DesignswathiBelum ada peringkat

- High Performance ALU Design Using Energy Efficient Borrow Select SubtractorDokumen65 halamanHigh Performance ALU Design Using Energy Efficient Borrow Select SubtractorKarthiga MuruganBelum ada peringkat

- Automating Wire Harness Design in Today's Automotive, Aerospace and Marine IndustryDokumen8 halamanAutomating Wire Harness Design in Today's Automotive, Aerospace and Marine IndustryMos CraciunBelum ada peringkat

- Comparative Study of Modern Optical Data Centers DesignDokumen5 halamanComparative Study of Modern Optical Data Centers DesignDr. Arunendra SinghBelum ada peringkat

- 3D ICs Reduce Interconnect DelaysDokumen31 halaman3D ICs Reduce Interconnect DelaysShweta R Burli0% (1)

- PHD Thesis On Wireless Mesh NetworksDokumen5 halamanPHD Thesis On Wireless Mesh Networksdnqkxm09100% (1)

- C. Laxmikanth ReddyDokumen26 halamanC. Laxmikanth ReddymritBelum ada peringkat

- System-on-chip Research Leads to Hardware/Software Co-design DegreeDokumen14 halamanSystem-on-chip Research Leads to Hardware/Software Co-design DegreeSamir TabibBelum ada peringkat

- 3D ICs Reduce Interconnect Delays Less Than 40 CharactersDokumen35 halaman3D ICs Reduce Interconnect Delays Less Than 40 CharactersJnaresh NareshBelum ada peringkat

- 3 - D ICsDokumen35 halaman3 - D ICsBibinMathewBelum ada peringkat

- Part Time Optics in Data CenterDokumen12 halamanPart Time Optics in Data CenterVivekBelum ada peringkat

- VLSIDokumen188 halamanVLSIDipu ShahBelum ada peringkat

- Research Paper VlsiDokumen6 halamanResearch Paper Vlsiafedsxmai100% (1)

- 3-D ICsDokumen35 halaman3-D ICsNikitha GBelum ada peringkat

- Research Statement: Patrick ChiangDokumen3 halamanResearch Statement: Patrick ChiangPardhasaradhi DamarlaBelum ada peringkat

- CnuDokumen27 halamanCnuMahesh BejgumBelum ada peringkat

- VLSI Design Fault Tolerant Network On Chip: IPASJ International Journal of Electronics & Communication (IIJEC)Dokumen3 halamanVLSI Design Fault Tolerant Network On Chip: IPASJ International Journal of Electronics & Communication (IIJEC)IPASJBelum ada peringkat

- A Network-On Chip Architecture For Optimization of Area and Power With Reconfigurable Topology On Cyclone II Specific DeviceDokumen9 halamanA Network-On Chip Architecture For Optimization of Area and Power With Reconfigurable Topology On Cyclone II Specific DeviceinventionjournalsBelum ada peringkat

- Technology Independent Yield-Aware Place & Route Strategy For Printed Electronics Gate Array CircuitsDokumen1 halamanTechnology Independent Yield-Aware Place & Route Strategy For Printed Electronics Gate Array CircuitsThanh HàBelum ada peringkat

- Network On A Chip: An Architecture For Billion Transistor EraDokumen8 halamanNetwork On A Chip: An Architecture For Billion Transistor EraMohod AbhayBelum ada peringkat

- Computer Network LabDokumen34 halamanComputer Network LabSouvik MondalBelum ada peringkat

- CAD Algorithms: Physical Design Automation of VLSI SystemsDokumen20 halamanCAD Algorithms: Physical Design Automation of VLSI SystemsjeevithaBelum ada peringkat

- 3D ICsDokumen34 halaman3D ICsapi-3827000100% (1)

- Design and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesDari EverandDesign and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesBelum ada peringkat

- Embedded System Interfacing: Design for the Internet-of-Things (IoT) and Cyber-Physical Systems (CPS)Dari EverandEmbedded System Interfacing: Design for the Internet-of-Things (IoT) and Cyber-Physical Systems (CPS)Belum ada peringkat

- Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsDari EverandTop-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsBelum ada peringkat

- Design for High Performance, Low Power, and Reliable 3D Integrated CircuitsDari EverandDesign for High Performance, Low Power, and Reliable 3D Integrated CircuitsBelum ada peringkat

- JEEMain2016Bulletin PDFDokumen55 halamanJEEMain2016Bulletin PDFmir shifayatBelum ada peringkat

- Power Energy Delay1234Dokumen7 halamanPower Energy Delay1234Sudheer RajaBelum ada peringkat

- Managerial Economics QuestionBankDokumen27 halamanManagerial Economics QuestionBankJit JagBelum ada peringkat

- CH1 MCQ AnswergridDokumen1 halamanCH1 MCQ AnswergridJit JagBelum ada peringkat

- Cad 2160911Dokumen3 halamanCad 2160911Jit JagBelum ada peringkat

- Types of Chopper CircuitsDokumen26 halamanTypes of Chopper CircuitsJit JagBelum ada peringkat

- Speed Control of DC Motor Using IGBT TailorDokumen9 halamanSpeed Control of DC Motor Using IGBT TailorJit JagBelum ada peringkat

- 10 1 1 43 902Dokumen140 halaman10 1 1 43 902Jit JagBelum ada peringkat

- ChoppersDokumen34 halamanChoppersMohEladibBelum ada peringkat

- Timingdiagram 1Dokumen14 halamanTimingdiagram 1Jit JagBelum ada peringkat

- Engineering DrawingDokumen8 halamanEngineering DrawingJit JagBelum ada peringkat

- 2160902Dokumen2 halaman2160902Jit JagBelum ada peringkat

- HAGERR Protection DevicesDokumen92 halamanHAGERR Protection DevicesJit JagBelum ada peringkat

- GTU MODEL QUESTION PAPER – BASIC ELECTRONICSDokumen3 halamanGTU MODEL QUESTION PAPER – BASIC ELECTRONICSJit JagBelum ada peringkat

- Rishmulti 12s 18sDokumen10 halamanRishmulti 12s 18sJit JagBelum ada peringkat

- Electrical (09) /power Electronics (24) : Gujarat Technological UniversityDokumen4 halamanElectrical (09) /power Electronics (24) : Gujarat Technological UniversityKeyur PatelBelum ada peringkat

- Basic Electronics49984Dokumen19 halamanBasic Electronics49984Fahad AmjadBelum ada peringkat

- Basic Electronic & Transistor Circuits PDFDokumen54 halamanBasic Electronic & Transistor Circuits PDFSandeep GoyalBelum ada peringkat

- Energy Conservation & Audit Course Code: 3350902Dokumen7 halamanEnergy Conservation & Audit Course Code: 3350902Rahul ChauhanBelum ada peringkat

- 150704Dokumen4 halaman150704Jit JagBelum ada peringkat

- Basic Electronic & Transistor Circuits PDFDokumen54 halamanBasic Electronic & Transistor Circuits PDFSandeep GoyalBelum ada peringkat

- Basic Electronic & Transistor Circuits PDFDokumen54 halamanBasic Electronic & Transistor Circuits PDFSandeep GoyalBelum ada peringkat

- Srno Sanctioned Intake First Shift Second Shift Total A Government Institute 14205 6360 20565 B Government - Aided Institute 1200 0 1200Dokumen1 halamanSrno Sanctioned Intake First Shift Second Shift Total A Government Institute 14205 6360 20565 B Government - Aided Institute 1200 0 1200Jit JagBelum ada peringkat

- Seats Vacant Due To Non-Allotment in BE Mock Round: Inst - Name Course - Name VacancyDokumen14 halamanSeats Vacant Due To Non-Allotment in BE Mock Round: Inst - Name Course - Name VacancyJit JagBelum ada peringkat

- Seats Vacant Due To Non-Allotment in BE Mock Round: Inst - Name Course - Name VacancyDokumen14 halamanSeats Vacant Due To Non-Allotment in BE Mock Round: Inst - Name Course - Name VacancyJit JagBelum ada peringkat

- CapacitorDokumen12 halamanCapacitorJit JagBelum ada peringkat

- Dhoom OfferDokumen2 halamanDhoom OfferJit JagBelum ada peringkat

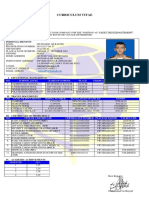

- Curriculum Vitae: To: Crewing Manager Subject: Deck Cadet Application Dear Sir or MadamDokumen1 halamanCurriculum Vitae: To: Crewing Manager Subject: Deck Cadet Application Dear Sir or MadamWiwit PrihatiniBelum ada peringkat

- Linking The Van Hiele Theory To Instruction 2015Dokumen11 halamanLinking The Van Hiele Theory To Instruction 2015Oliver IpoBelum ada peringkat

- Tutorial Letter 103/0/2020 Teaching Practice For Intermediate Phase (Grades 4-6) Assignment 50 Year Module Department of Curriculum and Instructional StudiesDokumen94 halamanTutorial Letter 103/0/2020 Teaching Practice For Intermediate Phase (Grades 4-6) Assignment 50 Year Module Department of Curriculum and Instructional StudiesMandisaBelum ada peringkat

- The Training of Football Players in BrazilDokumen3 halamanThe Training of Football Players in BrazilFeranmi OgunrotimiBelum ada peringkat

- Co Lesson Plan Math Q3Dokumen6 halamanCo Lesson Plan Math Q3Consuegra Elementary SchoolBelum ada peringkat

- Summary of PBB 2019 data for Region IX elementary schoolsDokumen35 halamanSummary of PBB 2019 data for Region IX elementary schoolsVIRGILIO GUZONBelum ada peringkat

- For More Information: WWW - Kimiafarma.co - IdDokumen2 halamanFor More Information: WWW - Kimiafarma.co - IdcucuBelum ada peringkat

- E LearningDokumen58 halamanE Learningtummalapalli venkateswara rao100% (1)

- Perceptual Learning: An IntroductionDokumen476 halamanPerceptual Learning: An IntroductionVíctor FuentesBelum ada peringkat

- Duolingo Homework PDF 22 MayDokumen6 halamanDuolingo Homework PDF 22 MayPriya PriyaBelum ada peringkat

- Resume of Arindam PalDokumen8 halamanResume of Arindam PalKrishna Moorthy GanesanBelum ada peringkat

- Daftar PustakaDokumen7 halamanDaftar PustakaZulaicha MumarridzohBelum ada peringkat

- Civil Service ExamDokumen3 halamanCivil Service ExamKaren Gina Dupra100% (1)

- EASTC Course ListingDokumen6 halamanEASTC Course ListingTHABISILE MBATHABelum ada peringkat

- Emirates Future International Academy Grade-5 WorksheetDokumen2 halamanEmirates Future International Academy Grade-5 WorksheetSajir ThiyamBelum ada peringkat

- Edtpa Lesson Plan Guide LPGDokumen5 halamanEdtpa Lesson Plan Guide LPGapi-660566244Belum ada peringkat

- Presentacin Intro Distribucin Por Variables A Taste of The MoonDokumen8 halamanPresentacin Intro Distribucin Por Variables A Taste of The MoonClemente TorresBelum ada peringkat

- ECON2206 Course OutlineDokumen12 halamanECON2206 Course OutlineChris Bury0% (1)

- JNTU-HYD: B.Tech/B.Pharmacy 2,3,4 Years Regular (I & II Semester) Academic Calendar 2010-11Dokumen3 halamanJNTU-HYD: B.Tech/B.Pharmacy 2,3,4 Years Regular (I & II Semester) Academic Calendar 2010-11rocky4bestBelum ada peringkat

- DocumentDokumen5 halamanDocumentLovely Anne MamarilBelum ada peringkat

- Nota:: What Does She Dislike About Her Job?Dokumen7 halamanNota:: What Does She Dislike About Her Job?JosefaBelum ada peringkat

- NSTP-CWTS GraduationDokumen4 halamanNSTP-CWTS GraduationAngie Esponilla100% (1)

- European Project Semester MinorDokumen3 halamanEuropean Project Semester MinorIrving Delgado SilvaBelum ada peringkat

- Managing Stress: Individual vs Organizational ApproachesDokumen4 halamanManaging Stress: Individual vs Organizational ApproachesMuhammad Hashim MemonBelum ada peringkat

- Today.: Technology For The Next DecadeDokumen26 halamanToday.: Technology For The Next DecadeBschool caseBelum ada peringkat