FDMC8200S

Diunggah oleh

dreyes3773Deskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

FDMC8200S

Diunggah oleh

dreyes3773Hak Cipta:

Format Tersedia

FDMC8200S Dual N-Channel PowerTrench MOSFET

March 2011

FDMC8200S

Dual N-Channel PowerTrench MOSFET

30 V, 10 m, 20 m Features

Q1: N-Channel � Max rDS(on) = 20 m at VGS = 10 V, ID = 6 A � Max rDS(on) = 32 m at VGS = 4.5 V, ID = 5 A Q2: N-Channel � Max rDS(on) = 10 m at VGS = 10 V, ID = 8.5 A � Max rDS(on) = 13.5 m at VGS = 4.5 V, ID = 7.2 A � RoHS Compliant

General Description

This device includes two specialized N-Channel MOSFETs in a due power33(3mm X 3mm MLP) package. The switch node has been internally connected to enable easy placement and routing of synchronous buck converters. The control MOSFET (Q1) and synchronous MOSFET (Q2) have been designed to provide optimal power efficiency.

Applications

� Mobile Computing � Mobile Internet Devices � General Purpose Point of Load

Bottom D1 G1 D1 D1

S1 D2/

Bottom VIN VIN

D1 V GHS IN

Pin 1

5

E OD HN C T I

Q2

4 3 2

Q1

VIN

SW

6 7

S2 G2 S2

S2

GLS

GND GND GND

Power33

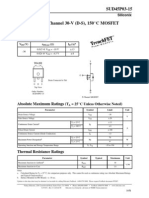

MOSFET Maximum Ratings TC = 25C unless otherwise noted

Symbol VDS VGS Parameter Drain to Source Voltage Gate to Source Voltage Drain Current -Continuous (Package limited) ID -Continuous (Silicon limited) -Continuous -Pulsed EAS PD TJ, TSTG Single Pulse Avalanche Energy Power Dissipation for Single Operation Power Dissipation for Single Operation TA = 25C TA = 25C (Note 3) TC = 25 C TC = 25 C TA = 25 C (Note 4) Q1 30 20 18 23 6 1a 40 12 1.9 1a 0.7 1c Q2 30 20 13 46 8.5 1b 27 32 2.5 1b 1.0 1d W C A Units V V

Operating and Storage Junction Temperature Range

-55 to +150

Thermal Characteristics

RJA RJA RJC Thermal Resistance, Junction to Ambient Thermal Resistance, Junction to Ambient Thermal Resistance, Junction to Case 65 1a 180 1c 7.5 50 1b 125 1d 4.2 C/W

Package Marking and Ordering Information

Device Marking FDMC8200S Device FDMC8200S Package Power 33

1

Reel Size 13

Tape Width 12 mm

Quantity 3000 units

www.fairchildsemi.com

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

FDMC8200S Dual N-Channel PowerTrench MOSFET

Electrical Characteristics TJ = 25C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Off Characteristics

BVDSS BVDSS TJ IDSS IGSS Drain to Source Breakdown Voltage Breakdown Voltage Temperature Coefficient Zero Gate Voltage Drain Current Gate to Source Leakage Current ID = 250 A, VGS = 0 V ID = 1mA, VGS = 0 V ID = 250 A, referenced to 25C ID = 1mA, referenced to 25C VDS = 24 V, VGS = 0 V VGS = 20 V, VDS = 0 V Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 30 30 14 13 1 500 100 100 V mV/C A nA nA

On Characteristics

VGS(th) VGS(th) TJ Gate to Source Threshold Voltage Gate to Source Threshold Voltage Temperature Coefficient VGS = VDS, ID = 250 A VGS = VDS, ID = 1mA ID = 250 A, referenced to 25C ID = 1mA, referenced to 25C VGS = 10 V, ID = 6 A VGS = 4.5 V, ID = 5 A VGS = 10 V, ID = 6 A, TJ = 125C VGS = 10 V, ID = 8.5 A VGS = 4.5 V, ID = 7.2 A VGS = 10 V, ID = 8.5 A, TJ = 125C VDD = 5 V, ID = 6 A VDD = 5 V, ID = 8.5 A Q1 Q2 Q1 Q2 Q1 1.0 1.0 2.3 2.0 -5 -6 16 24 22 7.8 10.3 11.4 29 43 20 32 28 10.0 13.5 13.1 3.0 3.0 V mV/C

rDS(on)

Static Drain to Source On Resistance

Q2 Q1 Q2

gFS

Forward Transconductance

Dynamic Characteristics

Ciss Coss Crss Rg Input Capacitance Output Capacitance Reverse Transfer Capacitance Gate Resistance VDS = 15 V, VGS = 0 V, f = 1 MHZ Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 0.2 0.2 495 1080 145 373 20 35 1.4 1.2 660 1436 195 495 30 52 4.2 3.6 pF pF pF

Switching Characteristics

td(on) tr td(off) tf Qg(TOT) Qg(TOT) Qgs Qgd Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time Total Gate Charge Total Gate Charge Gate to Source Charge Gate to Drain Miller Charge Q1 VDD = 15 V, ID = 1 A, VGS = 10 V, RGEN = 6 Q2 VDD = 15 V, ID = 1 A, VGS = 10 V, RGEN = 6 VGS = 0 V to 10 V Q1 VDD = 15 V, VGS = 0 V to 4.5 V ID = 6 A Q2 VDD = 15 V ID = 8.5 A Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 11 7.6 3.1 1.8 35 21 1.3 8.5 7.3 15.7 3.1 7.2 1.8 3 1 1.9 20 15 10 10 56 34 10 17 10 22 4.3 10 ns ns ns ns nC nC nC nC

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

Electrical Characteristics TJ = 25C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Drain-Source Diode Characteristics

VSD trr Qrr

Notes: 1. RJA is determined with the device mounted on a 1in2 pad 2 oz copper pad on a 1.5 x 1.5 in. board of FR-4 material. RJC is guaranteed by design while RCA is determined by the user's board design.

VGS = 0 V, IS = 6 A Source-Drain Diode Forward Voltage VGS = 0 V, IS = 8.5 A VGS = 0 V, IS = 1.3 A Reverse Recovery Time Reverse Recovery Charge Q1 IF = 6 A, di/dt = 100 A/s Q2 IF = 8.5 A, di/dt = 300 A/s

(Note 2) (Note 2) (Note 2)

Q1 Q2 Q2 Q1 Q2 Q1 Q2

0.8 0.8 0.6 13 20 2.3 15

1.2 1.2 0.8 24 32 10 24

V ns nC

a.65 C/W when mounted on a 1 in2 pad of 2 oz copper

b.50 C/W when mounted on a 1 in2 pad of 2 oz copper

c. 180 C/W when mounted on a minimum pad of 2 oz copper

d. 125 C/W when mounted on a minimum pad of 2 oz copper

2. Pulse Test: Pulse Width < 300 s, Duty cycle < 2.0%. 3.Starting Q1: T = 25 C, L = 1 mH, I = 5 A, Vgs = 10V, Vdd = 27V, 100% test at L = 3 mH, I = 4 A; Q2: T = 25C, L = 1 mH, I = 8 A, Vgs = 10V, Vdd = 27V, 100% test at L = 3 mH, I = 3.2 A. 4. As an N-ch device, the negative Vgs rating is for low duty cycle pulse ocurrence only. No continuous rating is implied.

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

Typical Characteristics (Q1 N-Channel) TJ = 25C unless otherwise noted

40

VGS = 6 V ID, DRAIN CURRENT (A)

NORMALIZED DRAIN TO SOURCE ON-RESISTANCE

4

VGS = 10 V

PULSE DURATION = 80 s DUTY CYCLE = 0.5% MAX

30

VGS = 4.5 V

3

VGS = 3.5 V VGS = 4 V VGS = 4.5 V

20

VGS = 4 V

10

VGS = 3.5 V PULSE DURATION = 80 s DUTY CYCLE = 0.5% MAX

1

VGS = 6 V VGS = 10 V

0 0.0

0 0 10 20 30 40

ID, DRAIN CURRENT (A)

0.5

1.0

1.5

2.0

2.5

3.0

VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 1. On Region Characteristics

Figure 2. Normalized On-Resistance vs Drain Current and Gate Voltage

100

rDS(on), DRAIN TO SOURCE ON-RESISTANCE (m)

1.6

NORMALIZED DRAIN TO SOURCE ON-RESISTANCE ID = 6 A VGS = 10 V

PULSE DURATION = 80 s DUTY CYCLE = 0.5% MAX

1.4

80

ID = 6 A

60

TJ = 125 oC

1.2

40 20

TJ = 25 oC

1.0

0.8 -75

-50

-25

25

50

75

100 125 150

0 2 4 6 8 10

VGS, GATE TO SOURCE VOLTAGE (V)

TJ, JUNCTION TEMPERATURE (oC)

Figure 3. Normalized On Resistance vs Junction Temperature

40

IS, REVERSE DRAIN CURRENT (A) PULSE DURATION = 80 s DUTY CYCLE = 0.5% MAX

Figure 4. On-Resistance vs Gate to Source Voltage

40

VGS = 0 V

10

ID, DRAIN CURRENT (A)

30

VDS = 5 V

1

TJ = 150 oC

20

TJ = 150 oC TJ = 25 oC

0.1

TJ = 25 oC

10

0.01

TJ = -55 oC

TJ = -55 oC

0 2.0

2.5

3.0

3.5

4.0

4.5

0.001 0.2

0.4

0.6

0.8

1.0

1.2

VGS, GATE TO SOURCE VOLTAGE (V)

VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 5. Transfer Characteristics

Figure 6. Source to Drain Diode Forward Voltage vs Source Current

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

Typical Characteristics (Q1 N-Channel) TJ = 25C unless otherwise noted

10

VGS, GATE TO SOURCE VOLTAGE (V) ID = 6 A

1000

Ciss

8

VDD = 15 V VDD = 20 V

CAPACITANCE (pF)

Coss

6

VDD = 10 V

100

4 2

Crss

f = 1 MHz VGS = 0 V

0 0 2 4

Qg, GATE CHARGE (nC)

10 0.1

10

30

VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Gate Charge Characteristics

Figure 8. Capacitance vs Drain to Source Voltage

25

RJC = 7.5 C/W

o

IAS, AVALANCHE CURRENT (A)

ID, DRAIN CURRENT (A)

8 7 6 5 4

TJ = 25 oC

20

VGS = 10 V

15

Limited by Package

3

TJ = 100 oC TJ = 125 oC

10

VGS = 4.5 V

5 0 25

1 0.01

0.1

50

75

100

o

125

150

tAV, TIME IN AVALANCHE (ms)

Tc, CASE TEMPERATURE ( C)

Figure 9. Unclamped Inductive Switching Capability

100 50

10 10

P(PK), PEAK TRANSIENT POWER (W)

Figure 10. Maximum Continuous Drain Current vs Case Temperature

100

VGS = 10 V

, DRAINCURRENT CURRENT (A) (A) IDI,DDRAIN

100 100 usus 1 ms

1 ms

10

1

THIS AREA ISIS THIS AREA LIMITED BY rDS(on) LIMITED BY r

DS(on)

10 ms

10100 ms ms

0.1

0.1

1s 100 ms 10 s 1s

10 s DC

0.01

SINGLE PULSE SINGLE PULSE TJ = MAX RATED TJ = MAX RATED

1

SINGLE PULSE RJA = 125 oC/W TA = 25 oC

0.01 0.001 0.01

RJA = 180 o TC = 25 oC TA = 25 C

oR JA = C/W

125 oC/W

DC

0.01

0.1

VDS, DRAIN to SOURCE VOLTAGE (V)

0.1

10

10

100200

100200

0.1 0.001

0.01

0.1

10

100

1000

t, PULSE WIDTH (sec)

VDS, DRAIN to SOURCE VOLTAGE (V)

Figure 11. Forward Bias Safe Operating Area

Figure 12. Single Pulse Maximum Power Dissipation

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

Typical Characteristics (Q1 N-Channel) TJ = 25C unless otherwise noted

2

DUTY CYCLE-DESCENDING ORDER

1

NORMALIZED THERMAL IMPEDANCE, ZJA

0.1

D = 0.5 0.2 0.1 0.05 0.02 0.01

PDM

t1 t2 NOTES: DUTY FACTOR: D = t1/t2 PEAK TJ = PDM x ZJC x RJc + TC

0.01 0.003 -4 10

SINGLE PULSE RJA = 180 C/W

-3 -2 -1

10

10

10

10

100

1000

t, RECTANGULAR PULSE DURATION (sec)

Figure 13. Junction-to-Ambient Transient Thermal Response Curve

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

Typical Characteristics (Q2 N-Channel) TJ = 25 C unless otherwise noted

27

NORMALIZED DRAIN TO SOURCE ON-RESISTANCE

VGS = 10 V VGS = 4.5 V VGS = 4 V VGS = 3.5 V

4

PULSE DURATION = 80 s DUTY CYCLE = 0.5% MAX

ID, DRAIN CURRENT (A)

VGS = 3 V

18

3

VGS = 3.5 V

VGS = 3 V

2

VGS = 4 V

9

PULSE DURATION = 80 s DUTY CYCLE = 0.5% MAX

1

VGS = 4.5 V VGS = 10 V

0 0.0

0.5

1.0

1.5

9

ID, DRAIN CURRENT (A)

18

27

VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 14. On- Region Characteristics

Figure 15. Normalized on-Resistance vs Drain Current and Gate Voltage

100

SOURCE ON-RESISTANCE (m)

1.6

NORMALIZED DRAIN TO SOURCE ON-RESISTANCE

ID = 8.5 A VGS = 10 V

ID = 8.5 A

PULSE DURATION = 80 s DUTY CYCLE = 0.5% MAX

1.4

rDS(on), DRAIN TO

80 60 40 20 0 2 4 6 8 10

VGS, GATE TO SOURCE VOLTAGE (V)

1.2

1.0

TJ = 125 oC

TJ = 25 oC

0.8 -75

-50

-25 0 25 50 75 100 125 150 TJ, JUNCTION TEMPERATURE (oC)

Figure 16. Normalized On-Resistance vs Junction Temperature

Figure 17. On-Resistance vs Gate to Source Voltage

27

IS, REVERSE DRAIN CURRENT (A) PULSE DURATION = 80 s DUTY CYCLE = 0.5% MAX

30 10

VGS = 0 V

ID, DRAIN CURRENT (A)

VDS = 5 V

TJ = 150 oC

18

TJ = 150 oC

1

TJ = 25 oC

TJ

= 25 oC

0.1

TJ = -55 oC

0.01

TJ = -55 oC

0 1.0

1.5

2.0

2.5

3.0

3.5

4.0

0.001 0.0

0.2

0.4

0.6

0.8

1.0

1.2

VGS, GATE TO SOURCE VOLTAGE (V)

VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 18. Transfer Characteristics

Figure 19. Source to Drain Diode Forward Voltage vs Source Current

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

Typical Characteristics (Q2 N-Channel) TJ = 25C unless otherwise noted

10

VGS, GATE TO SOURCE VOLTAGE (V) ID = 8.5 A

3000 1000

CAPACITANCE (pF) VDD = 15 V

8 6

VDD = 10 V VDD = 20 V

Ciss

Coss

4 2 0 0 2 4 6 8 10 12 14 16

Qg, GATE CHARGE (nC)

100

f = 1 MHz VGS = 0 V

Crss

10 0.1

10

30

VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 20. Gate Charge Characteristics

Figure 21. Capacitance vs Drain to Source Voltage

15

ID, DRAIN CURRENT (A)

20

IAS, AVALANCHE CURRENT (A)

10

TJ = 25 oC TJ = 100 oC

12

VGS = 10 V

9 6 3

RJA = 50 C/W

o

VGS = 4.5 V Limited by package

TJ = 125 oC

1 0.01

0.1

10

30

0 25

50

75

100

o

125

150

tAV, TIME IN AVALANCHE (ms)

TA, CASE TEMPERATURE ( C)

Figure 22. Unclamped Inductive Switching Capability

50 10

P(PK), PEAK TRANSIENT POWER (W)

Figure 23. Maximum Continuous Drain Current vs Case Temperature

100

VGS = 10 V

ID, DRAIN CURRENT (A)

100 us 1 ms

10

THIS AREA IS LIMITED BY rDS(on)

10 ms 100 ms 1s 10 s DC

0.1

SINGLE PULSE TJ = MAX RATED RJA = 125 oC/W TA = 25 oC

1

SINGLE PULSE RJA = 125 oC/W TA = 25 oC

0.01 0.01

0.1

10

100200

0.1 0.001

0.01

0.1

10

100

1000

VDS, DRAIN to SOURCE VOLTAGE (V)

t, PULSE WIDTH (sec)

Figure 24. Forward Bias Safe Operating Area

Figure 25. Single Pulse Maximum Power Dissipation

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

Typical Characteristics (Q2 N-Channel) TJ = 25 C unless otherwise noted

2

1

NORMALIZED THERMAL IMPEDANCE, ZJA

DUTY CYCLE-DESCENDING ORDER

0.1

D = 0.5 0.2 0.1 0.05 0.02 0.01

PDM

t1 t2

0.01

SINGLE PULSE RJA = 125 C/W

(Note 1b)

o

NOTES: DUTY FACTOR: D = t1/t2 PEAK TJ = PDM x ZJC x RJC + TC

0.001 -4 10

10

-3

10

-2

10

-1

10

100

1000

t, RECTANGULAR PULSE DURATION (sec)

Figure 26. Junction-to-Ambient Transient Thermal Response Curve

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

Typical Characteristics (continued)

SyncFET Schottky body diode Characteristics

Fairchilds SyncFET process embeds a Schottky diode in parallel with PowerTrench MOSFET. This diode exhibits similar characteristics to a discrete external Schottky diode in parallel with a MOSFET. Figure 14 shows the reverses recovery characteristic of the FDMC8200S.

7 6 5

CURRENT (A)

Schottky barrier diodes exhibit significant leakage at high temperature and high reverse voltage. This will increase the power in the device.

0.01

IDSS, REVERSE LEAKAGE CURRENT (A)

TJ = 125 oC

0.001

TJ = 100 oC

4 3 2 1 0 -1 -2 0 20 40

TIME (ns)

di/dt = 300 A/s

0.0001

0.00001

TJ = 25 oC

60

80

100

0.000001 0 5 10 15 20 25 30

VDS, REVERSE VOLTAGE (V)

Figure 27. FDMC8200S SyncFET body diode reverse recovery characteristic

Figure 28. SyncFET body diode reverses leakage versus drain-source voltage

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

10

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

Dimensional Outline and Pad Layout

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

11

www.fairchildsemi.com

FDMC8200S Dual N-Channel PowerTrench MOSFET

TRADEMARKS The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks. AccuPower Power-SPM F-PFS The Power Franchise Auto-SPM PowerTrench The Right Technology for Your Success FRFET AX-CAP* Global Power ResourceSM PowerXS Build it Now Green FPS Programmable Active Droop Green FPS e-Series CorePLUS QFET TinyBoost Gmax QS CorePOWER TinyBuck GTO Quiet Series CROSSVOLT TinyCalc IntelliMAX RapidConfigure CTL TinyLogic ISOPLANAR Current Transfer Logic TINYOPTO MegaBuck DEUXPEED TinyPower MICROCOUPLER Saving our world, 1mW/W/kW at a time Dual Cool TinyPWM MicroFET SignalWise EcoSPARK TinyWire MicroPak SmartMax EfficentMax TriFault Detect MicroPak2 SMART START ESBC TRUECURRENT* MillerDrive SPM SerDes STEALTH MotionMax SuperFET Motion-SPM Fairchild SuperSOT-3 mWSaver Fairchild Semiconductor UHC SuperSOT-6 OptiHiT FACT Quiet Series Ultra FRFET SuperSOT-8 OPTOLOGIC FACT UniFET OPTOPLANAR SupreMOS FAST VCX SyncFET FastvCore VisualMax Sync-Lock FETBench XS * FlashWriter * PDP SPM FPS

tm

tm

tm

*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILDS WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used here in: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ANTI-COUNTERFEITING POLICY Fairchild Semiconductor Corporations Anti-Counterfeiting Policy. Fairchilds Anti-Counterfeiting Policy is also stated on our external website, www.Fairchildsemi.com, under Sales Support. Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchilds quality standards for handing and storage and provide access to Fairchilds full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification

Advance Information

Product Status

Formative / In Design

Definition

Datasheet contains the design specifications for product development. Specifications may change in any manner without notice. Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design. Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.

Rev. I53

Preliminary

First Production

No Identification Needed Obsolete

Full Production Not In Production

2011 Fairchild Semiconductor Corporation FDMC8200S Rev.C4

12

www.fairchildsemi.com

Anda mungkin juga menyukai

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesDari EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesPenilaian: 4.5 dari 5 bintang4.5/5 (7)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDari EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsPenilaian: 3.5 dari 5 bintang3.5/5 (6)

- Automotive Microelectronics 2001Dokumen93 halamanAutomotive Microelectronics 2001sayapopai100% (16)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDari EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsBelum ada peringkat

- PFC Boost Converter Design Guide - Infineon - Infineon-ApplicationNote - PFCCCMBoostConverterDesignGuide-An-V02 - 00-EnDokumen31 halamanPFC Boost Converter Design Guide - Infineon - Infineon-ApplicationNote - PFCCCMBoostConverterDesignGuide-An-V02 - 00-Enkik020Belum ada peringkat

- DCM Flyback DesignDokumen16 halamanDCM Flyback Designsai_ravichandraBelum ada peringkat

- 430 15EC73 Power Electronics Notes (Vtupro Com) 2Dokumen100 halaman430 15EC73 Power Electronics Notes (Vtupro Com) 2KN DEEPSHIBelum ada peringkat

- FDMS3604SDokumen12 halamanFDMS3604Sg_alinBelum ada peringkat

- Fdms0308Cs: N-Channel Powertrench SyncfetDokumen8 halamanFdms0308Cs: N-Channel Powertrench Syncfetdreyes3773Belum ada peringkat

- FDMC86240 DatasheetDokumen7 halamanFDMC86240 DatasheetYiannis PapadopoulosBelum ada peringkat

- FDS4435BZDokumen6 halamanFDS4435BZCornel PislaruBelum ada peringkat

- AO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect TransistorDokumen8 halamanAO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect Transistordreyes3773Belum ada peringkat

- Dual N-Channel, Notebook Power Supply MOSFET: June 1999Dokumen9 halamanDual N-Channel, Notebook Power Supply MOSFET: June 1999dreyes3773Belum ada peringkat

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETDokumen9 halamanFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloBelum ada peringkat

- Dual N-Channel Enhancement Mode Field Effect Transistor: FeaturesDokumen5 halamanDual N-Channel Enhancement Mode Field Effect Transistor: FeaturesBvm BvmmBelum ada peringkat

- FQB8N60C / FQI8N60C: 600V N-Channel MOSFETDokumen9 halamanFQB8N60C / FQI8N60C: 600V N-Channel MOSFETemelchor57Belum ada peringkat

- 50N06 Mosfet Datasheet PDFDokumen8 halaman50N06 Mosfet Datasheet PDFjoshomecBelum ada peringkat

- Fds8958A: Dual N & P-Channel Powertrench MosfetDokumen11 halamanFds8958A: Dual N & P-Channel Powertrench MosfetbyronzapetaBelum ada peringkat

- 30V Dual N-Channel MOSFET with Schottky Diode CharacteristicsDokumen9 halaman30V Dual N-Channel MOSFET with Schottky Diode CharacteristicsRafael HurtadoBelum ada peringkat

- FDD8780Dokumen6 halamanFDD8780Cadena CesarBelum ada peringkat

- FET 75N75 TransistorDokumen8 halamanFET 75N75 Transistorshahid iqbalBelum ada peringkat

- AO4900 Dual N-Channel Enhancement Mode Field Effect Transistor With Schottky DiodeDokumen5 halamanAO4900 Dual N-Channel Enhancement Mode Field Effect Transistor With Schottky Diodedreyes3773Belum ada peringkat

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MDokumen11 halamanFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MKevin TateBelum ada peringkat

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Dokumen11 halamanN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TateBelum ada peringkat

- 4800 AgmDokumen5 halaman4800 AgmaluiznetBelum ada peringkat

- Datasheet PDFDokumen5 halamanDatasheet PDFDaniel MernesBelum ada peringkat

- 2N60Dokumen8 halaman2N60vdăduicăBelum ada peringkat

- Dual N-Channel Enhancement Mode FET Technical DocDokumen6 halamanDual N-Channel Enhancement Mode FET Technical Docdreyes3773Belum ada peringkat

- N Mosfet Fdv303nDokumen4 halamanN Mosfet Fdv303nxlam99Belum ada peringkat

- FQPF17P06: 60V P-Channel MOSFETDokumen8 halamanFQPF17P06: 60V P-Channel MOSFETMahmoued YasinBelum ada peringkat

- Unisonic Technologies Co., LTD: 30 Amps, 60 Volts N-Channel Power MosfetDokumen8 halamanUnisonic Technologies Co., LTD: 30 Amps, 60 Volts N-Channel Power Mosfetperro sBelum ada peringkat

- FQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETDokumen10 halamanFQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETJavier Ayerdis NarváezBelum ada peringkat

- IRFP360LCDokumen8 halamanIRFP360LCΗρακλης ΖερκελιδηςBelum ada peringkat

- N 308 ApDokumen11 halamanN 308 Apdragon-red0816Belum ada peringkat

- FQD2N60C / FQU2N60C: N-Channel Qfet MosfetDokumen9 halamanFQD2N60C / FQU2N60C: N-Channel Qfet MosfetTomescu MarianBelum ada peringkat

- Irf 730 ADokumen9 halamanIrf 730 Ajose_mamani_51Belum ada peringkat

- K4143Dokumen8 halamanK4143eddy54Belum ada peringkat

- Datasheet PDFDokumen6 halamanDatasheet PDFAmer HodzicBelum ada peringkat

- Radiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELDokumen8 halamanRadiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELbmmostefaBelum ada peringkat

- 500V 20A 0.27Ω N-Channel MOSFETDokumen6 halaman500V 20A 0.27Ω N-Channel MOSFETfilibertooBelum ada peringkat

- Fds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetDokumen12 halamanFds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetAlejandro DelgadoBelum ada peringkat

- P605Dokumen7 halamanP605Octavio RamirezBelum ada peringkat

- IRF830A: Smps MosfetDokumen8 halamanIRF830A: Smps MosfetRICHIHOTS2Belum ada peringkat

- IRF360Dokumen7 halamanIRF360Miloud ChouguiBelum ada peringkat

- Sss7n60b (7n60b) MosfetDokumen11 halamanSss7n60b (7n60b) MosfetCamilo AldanaBelum ada peringkat

- IRF650B / IRFS650B: 200V N-Channel MOSFETDokumen11 halamanIRF650B / IRFS650B: 200V N-Channel MOSFETMiloud ChouguiBelum ada peringkat

- Irfp 260 NDokumen9 halamanIrfp 260 NJolaine MojicaBelum ada peringkat

- FQP6N60C/FQPF6N60C: 600V N-Channel MOSFETDokumen10 halamanFQP6N60C/FQPF6N60C: 600V N-Channel MOSFETBiswajit SarkarBelum ada peringkat

- Mosfet 10NM60NDokumen19 halamanMosfet 10NM60NRicardo Misael Torres0% (1)

- AO4410 N-Channel FET SpecsDokumen4 halamanAO4410 N-Channel FET Specsdreyes3773Belum ada peringkat

- Irfp 2907Dokumen9 halamanIrfp 2907Anonymous u8GkNaBelum ada peringkat

- Fds 3890Dokumen5 halamanFds 3890Raina VijayBelum ada peringkat

- 600V 12A Silicon MOSFET Datasheet CS12N60F A9RDokumen10 halaman600V 12A Silicon MOSFET Datasheet CS12N60F A9RJosé Miguel Barbosa HernándezBelum ada peringkat

- AON6290 (Transistor Vds 100V)Dokumen6 halamanAON6290 (Transistor Vds 100V)Kc UachBelum ada peringkat

- Irfb4020Pbf: Digital Audio MosfetDokumen8 halamanIrfb4020Pbf: Digital Audio Mosfetto_netiksBelum ada peringkat

- 2N60 PDFDokumen7 halaman2N60 PDFFady HachemBelum ada peringkat

- AO4800B, AO4800BL Dual N-Channel Enhancement Mode Field Effect TransistorDokumen4 halamanAO4800B, AO4800BL Dual N-Channel Enhancement Mode Field Effect Transistorjavierrincon800Belum ada peringkat

- Jan 2003 AO4422 N-Channel Enhancement Mode Field Effect TransistorDokumen4 halamanJan 2003 AO4422 N-Channel Enhancement Mode Field Effect TransistorHabib AlbiBelum ada peringkat

- Radiation Hardened Power Mosfet THRU-HOLE (T0-204AE) I R H 9 1 5 0 100V, P-CHANNELDokumen8 halamanRadiation Hardened Power Mosfet THRU-HOLE (T0-204AE) I R H 9 1 5 0 100V, P-CHANNELDeepa DevarajBelum ada peringkat

- Irf 340Dokumen8 halamanIrf 340Miloud ChouguiBelum ada peringkat

- 4N65Dokumen8 halaman4N65Vicente MalvicaBelum ada peringkat

- AO4488 N-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionDokumen4 halamanAO4488 N-Channel Enhancement Mode Field Effect Transistor: Features General Descriptionjavierrincon800Belum ada peringkat

- OTA5180ADokumen34 halamanOTA5180Adreyes3773Belum ada peringkat

- Multi Sim 9 QSGuideDokumen8 halamanMulti Sim 9 QSGuideAhmad AlHouraniBelum ada peringkat

- Fds 6875Dokumen5 halamanFds 6875dreyes3773Belum ada peringkat

- FW342Dokumen6 halamanFW342dreyes3773Belum ada peringkat

- EulaDokumen5 halamanEulaRafael MolinaBelum ada peringkat

- AO4600 Complementary Enhancement Mode Field Effect Transistor Spec SheetDokumen10 halamanAO4600 Complementary Enhancement Mode Field Effect Transistor Spec SheetFidel ArroyoBelum ada peringkat

- Deh 3550uiDokumen65 halamanDeh 3550uiReyes Aguilar MarioBelum ada peringkat

- Multisim ManualDokumen800 halamanMultisim ManualBaljit Singh SainiBelum ada peringkat

- AR3011 Bluetooth Users GD PCDokumen74 halamanAR3011 Bluetooth Users GD PCHajar Norasyikin Abu BakarBelum ada peringkat

- 316273Dokumen0 halaman316273ramesh2440Belum ada peringkat

- FW342Dokumen6 halamanFW342dreyes3773Belum ada peringkat

- Fds 6875Dokumen5 halamanFds 6875dreyes3773Belum ada peringkat

- VDS-30V P-Channel MOSFETDokumen5 halamanVDS-30V P-Channel MOSFETElisabeth BaraBelum ada peringkat

- TPC8103Dokumen8 halamanTPC8103dreyes3773Belum ada peringkat

- 4407 DatasheetDokumen5 halaman4407 DatasheetsunitbhaumikBelum ada peringkat

- DS Am3423p BDokumen5 halamanDS Am3423p Bdreyes3773Belum ada peringkat

- Srovnani Transil-TrisilDokumen6 halamanSrovnani Transil-TrisilJunis07Belum ada peringkat

- FDS6675BZDokumen6 halamanFDS6675BZeinstein6Belum ada peringkat

- 4400Dokumen6 halaman4400dreyes3773Belum ada peringkat

- Sud45p03 15 MosfetDokumen4 halamanSud45p03 15 Mosfetdreyes3773Belum ada peringkat

- Fds8958A: Dual N & P-Channel Powertrench MosfetDokumen11 halamanFds8958A: Dual N & P-Channel Powertrench MosfetbyronzapetaBelum ada peringkat

- Si4814DY Dual N-Channel 30-V (D-S) MOSFET With Schottky DiodeDokumen8 halamanSi4814DY Dual N-Channel 30-V (D-S) MOSFET With Schottky Diodedreyes3773Belum ada peringkat

- FDS6912ADokumen4 halamanFDS6912Adreyes3773Belum ada peringkat

- SI9945Dokumen4 halamanSI9945dreyes3773Belum ada peringkat

- Dual N-Channel, Notebook Power Supply MOSFET: June 1999Dokumen9 halamanDual N-Channel, Notebook Power Supply MOSFET: June 1999dreyes3773Belum ada peringkat

- AO4914Dokumen8 halamanAO4914dreyes3773Belum ada peringkat

- Dual N-Channel, Notebook Power Supply MOSFET: June 1999Dokumen9 halamanDual N-Channel, Notebook Power Supply MOSFET: June 1999dreyes3773Belum ada peringkat

- FDS6900ASDokumen10 halamanFDS6900ASdreyes3773Belum ada peringkat

- AP4232GMDokumen4 halamanAP4232GMdreyes3773Belum ada peringkat

- Jomo Kenyatta University EEE Revision QuestionsDokumen9 halamanJomo Kenyatta University EEE Revision QuestionsIAMMARKSBelum ada peringkat

- SS32 THRU SS310: 3.0 AMPS. Surface Mount Schottky Barrier RectifiersDokumen3 halamanSS32 THRU SS310: 3.0 AMPS. Surface Mount Schottky Barrier RectifiersericBelum ada peringkat

- Erl e PDFDokumen15 halamanErl e PDFbahmanBelum ada peringkat

- Fdq7238S: Dual Notebook Power Supply N Channel Powertrench in So-14 PackageDokumen10 halamanFdq7238S: Dual Notebook Power Supply N Channel Powertrench in So-14 PackageEdy Valeriano ChicllaBelum ada peringkat

- Electronics Symbol and DescriptionDokumen3 halamanElectronics Symbol and DescriptionShiela SalvillaBelum ada peringkat

- LM - 396 PDFDokumen14 halamanLM - 396 PDFDaniel Arcia JiménezBelum ada peringkat

- DatasheetDokumen9 halamanDatasheetloisaomBelum ada peringkat

- Fundamentals of The RectennaDokumen37 halamanFundamentals of The RectennaWilfredo A MolinaBelum ada peringkat

- SB1020CTDokumen4 halamanSB1020CTMarek DabrowskiBelum ada peringkat

- Max17126 Max17126a PDFDokumen34 halamanMax17126 Max17126a PDFVukica IvicBelum ada peringkat

- Datasheet Diode Power Schottky Rectifier STPS80L60CY PDFDokumen4 halamanDatasheet Diode Power Schottky Rectifier STPS80L60CY PDFHưng HQBelum ada peringkat

- BAS40-00-V To BAS40-06-V: Small Signal Schottky Diodes, Single & DualDokumen5 halamanBAS40-00-V To BAS40-06-V: Small Signal Schottky Diodes, Single & DualtomscribdasdfBelum ada peringkat

- Ec2254 NolDokumen85 halamanEc2254 Nolsudha_monisha16Belum ada peringkat

- High Power Schottky Barrier Rectifier: SoonerDokumen4 halamanHigh Power Schottky Barrier Rectifier: SoonerPablo AllosiaBelum ada peringkat

- 1N5712Dokumen7 halaman1N5712Jeetu AnjanaBelum ada peringkat

- Physics and Modeling of Microelectronic Devices: BITS PilaniDokumen17 halamanPhysics and Modeling of Microelectronic Devices: BITS PilaniKrunalKapadiya1Belum ada peringkat

- Power DiodeDokumen28 halamanPower DiodeabubakarshaBelum ada peringkat

- Tak Cheong: 10A Schottky Barrier DiodeDokumen4 halamanTak Cheong: 10A Schottky Barrier DiodeSaid Khamis MbaroukBelum ada peringkat

- Adding A Current Limit Feature To A BuckBoost ConvDokumen7 halamanAdding A Current Limit Feature To A BuckBoost ConvYung SangBelum ada peringkat

- Sic Schottky Diode Device Design Characterizing Performance ReliabilityDokumen8 halamanSic Schottky Diode Device Design Characterizing Performance Reliabilitymahesh babuBelum ada peringkat

- PN JunctionsDokumen4 halamanPN JunctionsKancharana SarathchandraBelum ada peringkat

- A02 SOW Appendix 3 IMSE Master Part ListDokumen134 halamanA02 SOW Appendix 3 IMSE Master Part ListrizkyBelum ada peringkat

- 5.0amp Schottky Barrier Rectifiers: Voltage Range FeaturesDokumen2 halaman5.0amp Schottky Barrier Rectifiers: Voltage Range Featuresيوكي آنى سانBelum ada peringkat

- Data Sheet: HSMS-8101, 8202, 8207, 8209Dokumen6 halamanData Sheet: HSMS-8101, 8202, 8207, 8209nad_chadi8816Belum ada peringkat

- Power Diodes Nascene and CliftonDokumen12 halamanPower Diodes Nascene and CliftonSnehasis BarikBelum ada peringkat

- Low Forward Voltage Schottky RectifierDokumen7 halamanLow Forward Voltage Schottky RectifierTahar BenacherineBelum ada peringkat