AL422B Data Sheets

Diunggah oleh

juenkkinDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

AL422B Data Sheets

Diunggah oleh

juenkkinHak Cipta:

Format Tersedia

AL422B Data Sheets

(Revision V1.01)

AL422B

Amendments (Since April 2, 1999)

99.05.13 99.07.02 99.08.03 99.09.02 99.10.26 99.12.15 01.01.18 DC/AC characteristics (including current consumption) updated. Pinout diagram (5.0) and DC external load (7.4) modified. Description about TST pin added in sections 6.0 & 8.1. 8.3.2 rewritten. Capacitance provided in the AC characteristics section. Remove TST pin restriction. 1. Revised section 8.3.2 Read Enable during Reset Cycles to 8.3.2 The Proper 2. Add section 8.3.3 Single Field Write with Multiple Read Operation 3. Add section 8.3.4 One Field Delay Line (The Old Data Read)

AL422B

January 23, 2001

AL422B

AL422B 3M-Bits FIFO Field Memory

Contents:

1.0 Description _________________________________________________________________ 4 2.0 Features____________________________________________________________________ 4 3.0 Applications_________________________________________________________________ 4 4.0 Ordering Information _________________________________________________________ 4 5.0 Pinout Diagram _____________________________________________________________ 5 6.0 Pin Description ______________________________________________________________ 5 7.0 Electrical Characteristics ______________________________________________________ 6

7.1 Absolute Maximum Ratings _________________________________________________________ 6 7.2 Recommended Operating Conditions _________________________________________________ 6 7.3 DC Characteristics ________________________________________________________________ 6 7.4 AC Characteristics ________________________________________________________________ 7 7.5 Timing Diagrams__________________________________________________________________ 9

8.0 Functional Description_______________________________________________________ 13

8.1 Memory Operation _______________________________________________________________ 14 8.2 5V and 3.3V applications __________________________________________________________ 15 8.3 Application Notes ________________________________________________________________ 16

8.3.1 Irregular Read/Write __________________________________________________________________ 16 8.3.2 The Proper Manipulation of FIFO Access __________________________________________________ 17 8.3.3 Single Field Write with Multiple Read Operation____________________________________________ 17 8.3.4 One Field Delay Line (The Old Data Read) ________________________________________________ 17

9.0 Mechanical Drawing ________________________________________________________ 19

AL422B

January 23, 2001

AL422B

1.0 Description

The AL422B consists of 3M-bits of DRAM, and is configured as 393,216 words x 8 bit FIFO (first in first out). The interface is very user-friendly since all complicated DRAM operations are already managed by the internal DRAM controller. Current sources of similar memory (field memory) in the market provide limited memory size which is only enough for holding one TV field, but not enough to hold a whole PC video frame which normally contains 640x480 or 720x480 bytes. The AverLogic AL422B provides 50% more memory to support high resolution for digital PC graphics or video applications. The 50% increase in speed also expands the range of applications.

2.0 Features

384K (393,216) x 8 bits FIFO organization Support VGA, CCIR, NTSC, PAL and HDTV resolutions Independent read/write operations (different I/O data rates acceptable) High speed asynchronous serial access Read/write cycle time: 20ns Access time: 15ns Output enable control (data skipping) 5V or 3.3V power supply Standard 28-pin SOP package

Multimedia systems Video capture systems Video editing systems Scan rate converters TVs picture in picture feature Time base correction (TBC) Frame synchronizer Digital video camera Buffer for communications systems

3.0 Applications

4.0 Ordering Information

Part number AL422B AL422V5 AL422V3 Package 28-pin plastic SOP 28-pin plastic SOP 28-pin plastic SOP Power Supply +5/+3.3 volt +5 volt +3.3 volt Status Shipping Replaced by AL422B Replaced by AL422B

AL422B

January 23, 2001

AL422B

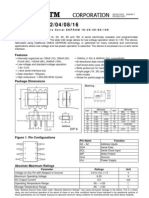

5.0 Pinout Diagram

/RRST GND RCK DEC DO0 DO1 DO2 DO3 DO4 DO5 DO6

16

28

27

26

25

24

23

22

21

20

19

18

17

AVERLOGIC AL422B XXXXX XXXX

10 11 12 13 14 1 2 3 4 5 6 7 8 9

15

DO7

/OE

/RE

Lot Number Date Code

/WRST

WCK

VDD

/WE

TST

DI0

DI1

DI2

DI3

DI4

DI5

DI6

6.0 Pin Description

Pin name DI0~DI7 WCK /WE /WRST DO0~DO7 RCK /RE /RRST /OE TST VDD DEC/VDD GND Pin # 1~4, 11~14 9 5 8 15~18, 25~28 20 24 21 22 7 10 19 6, 23 I/O type input Input Input (active low) Input (active low) Output (tristate) Input Input (active low) Input (active low) Input (active low) Input Function Data input Write clock Write enable Write reset Data output Read clock Read enable Read reset Output enable Test pin (pulled-down)* 5V or 3.3V Decoupling cap input Ground

GND

DI7

AL422B

January 23, 2001

AL422B

7.0 Electrical Characteristics

7.1 Absolute Maximum Ratings

Parameter VDD VP IO TAMB Tstg Supply Voltage Pin Voltage Output Current Ambient Op. Temperature Storage temperature -1.0 ~ +4.5 -1.0 ~ +5.5 -20 ~ +20 0 ~ +70 -55 ~ +125 Ratings 3.3V application 5V application -1.0 ~ +7.0 -1.0 ~ VDD +0.5 -20 ~ +20 0 ~ +70 -55 ~ +125 V V mA C C Unit

7.2 Recommended Operating Conditions

Parameter VDD VIH VIL Supply Voltage High Level Input Voltage Low Level Input Voltage 3.3V application Min +3.0 +2.0 -1.0 Max +3.6 +5.5 +0.8 5V application Min +4.5 +3.0 -1.0 Max +5.25 VDD +0.5 +0.8 V V V Unit

7.3 DC Characteristics

(VDD =5V or 3.3V, Vss=0V. TAMB = 0 to 70C)

Parameter IDD IDD IDD IDD IDDS VOH VOL ILI ILO Operating Current @20MHz Operating Current @30MHz Operating Current @40MHz Operating Current @50MHz Standby Current Hi-level Output Voltage Lo-level Output Voltage Input Leakage Current Output Leakage Current 0.7VDD -10 -10 3.3V application Min Typ 33 45 57 68 7 Max VDD +0.4 +10 +10 5V application Min +3.0 -10 -10 Typ 50 66 82 97 12 Max VDD +0.4 +10 +10 mA mA mA mA mA V V A A Unit

AL422B

January 23, 2001

AL422B

7.4 AC Characteristics

(VDD =5V or 3.3V, Vss=0V, TAMB = 0 to 70C)

Parameter TWC TWPH TWPL TRC TRPH TRPL TAC TOH THZ TLZ TWRS TWRH TRRS TRRH TDS TDH TWES TWEH TWPW TRES TREH TRPW TOES TOEH TOPW TTR CI CO WCK Cycle Time WCK High Pulse Width WCK Low Pulse Width RCK Cycle Time RCK High Pulse Width RCK Low Pulse Width Access Time Output Hold Time Output High-Z Setup Time Output Low-Z Setup Time /WRST Setup Time /WRST Hold Time /RRST Setup Time /RRST Hold Time Input Data Setup Time Input Data Hold Time /WE Setup Time /WE Hold Time /WE Pulse Width /RE Setup Time /RE Hold Time /RE Pulse Width /OE Setup Time /OE Hold Time /OE Pulse Width Transition Time Input Capacitance Output Capacitance 3.3V application Min 20 7 7 20 7 7 4 3 3 5 2 5 2 5 2 5 2 10 5 2 10 5 2 10 2 Max 1000 1000 15 15 15 20 7 7 5V application Min 20 7 7 20 7 7 4 4 4 6 3 6 3 6 3 6 3 10 6 3 10 6 3 10 3 Max 1000 1000 15 15 15 20 7 7 ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns pF pF Unit

AL422B

January 23, 2001

AL422B

Input voltage levels are defined as VIH=3.0V and VIL=0.4V. The read address needs to be at least 128 cycles after the write address.

DO external load:

AL422B

January 23, 2001

AL422B

7.5 Timing Diagrams

cycle n

Reset cycle (s)

cycle 0

cycle 1

WCK

TTR TWRS TWRH

/WRST

TDS

TDH

DI7~0 /WE = "L"

n-1

AL422-05 Write Cycle Timing (Write Reset)

cycle n TRPL

Reset cycle (s)

cycle 0

cycle 1

RCK

TRPH

TRRS

TRRH

/RRST

TAC TOH

DO7~0

n-1

/RE = /OE = "L" AL422-07 Read Cycle Timing (Read Reset)

AL422B

January 23, 2001

AL422B

cycle n TRPL

cycle n+1

Disable cycle (s)

cycle n+2

RCK

TRPH TRC TRES TREH

/RE

TRPW TAC TOH

DO7~0 /OE = "L"

n-1

n+1

n+2

AL422-08 Read Cycle Timing (Read Enable)

cycle n TRPL

cycle n+1

cycle n+2

cycle n+3

cycle n+4

RCK

TRPH TRC TOES TOEH

/OE

TOPW TAC TOH THZ Hi-Z TLZ

DO7~0 /RE = "L"

n-1

n+1

n+4

AL422-09 Read Cycle Timing (Output Enable)

AL422B January 23, 2001

10

AL422B

cycle n TWPL

cycle n+1

Disable cycle (s)

cycle n+2

WCK

TWPH TWC TWES TWEH

/WE

TWPW TDS TDH

DI7~0

n-1

n+1

n+2

AL422-06 Write Cycle Timing (Write Enable)

cycle n TRPL

cycle n+1

Disable cycle (s)

cycle 0

RCK

TRPH TRC TRRS TRRH

/RRST

TRES

TREH

/RE

TRPW TAC TOH

DO7~0 /OE = "L"

n-1

n+1

AL422-14 Read Cycle Timing (RE, RRST)

AL422B

January 23, 2001

11

AL422B

cycle n TWPL

cycle n+1

Disable cycle (s)

cycle 0

cycle 1

WCK

TWPH

TWC

TWRS

TWRH

/WRST

TWES

TWEH

/WE

TWPW TDS TDH

DI7~0

n-1

n+1

AL422-15 Write Cycle Timing (WE, WRST)

AL422B

January 23, 2001

12

AL422B

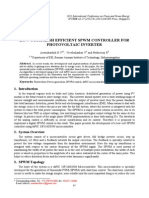

8.0 Functional Description

The AL422B is a video frame buffer consisting of DRAM that works like a FIFO which is long enough to hold up to 819x480 bytes of picture information and fast enough to operate at 50MHz. The functional block diagram is as follows:

SRAM Cache Write Data Register Read Data Register

DI7~ DI0

Input Buffer

384k x8 Memory Cell Array

Output Buffer

DO7~ DO0 /OE

WCK /WRST /WE

Write Address Counter

Timing Generator & Arbiter

Read Address Counter

RCK /RRST /RE

Refresh Address Counter

AL422-03 Block Diagram

The I/O pinouts and functions are described as follows: DI7~DI0 Data Input: Data is input on the rising edge of the cycle of WCK when /WE is pulled low

(enabled).

DO7~DO0 Data Output: Data output is synchronized with the RCK clock. Data is obtained at the rising edge of the RCK clock when /RE is pulled low. The access time is defined from the rising edge of the RCK cycle. WCK Write Clock Input: The write data input is synchronized with this clock. Write data is input at the rising edge of the WCK cycle when /WE is pulled low (enabled). The internal write address pointer is incremented automatically with this clock input. RCK Read Clock Input: The read data output is synchronized with this clock. Read data output at the rising edge of the RCK cycle when /OE is pulled low (enabled). The internal read address pointer is incremented with this clock input. /WE Write Enable Input: /WE controls the enabling/disabling of the data input. When /WE is pulled low, input data is acquired at the rising edge of the WCK cycle. When /WE is pulled high, the

AL422B

January 23, 2001

13

AL422B

memory does not accept data input. The write address pointer is stopped at the current position. /WE signal is fetched at the rising edge of the WCK cycle. /RE Read Enable Input: /RE controls the operation of the data output. When /RE is pulled low, output data is provided at the rising edge of the RCK cycle and the internal read address is incremented automatically. /RE signal is fetched at the rising edge of the RCK cycle. /OE Output Enable Input: /OE controls the enabling/disabling of the data output. When /OE is pulled low, output data is provided at the rising edge of the RCK cycle. When /OE is pulled high, data output is disabled and the output pins remain at high impedance status. /OE signal is fetched at the rising edge of RCK cycle. /WRST Write Reset Input: This reset signal initializes the write address to 0, and is fetched at the rising edge of the WCK input cycle. /RRST Write Reset Input: This reset signal initializes the read address to 0, and is fetched at the rising edge of the RCK input cycle. TST Test Pin: For testing purpose only. It should be pulled low for normal applications. DEC: Decoupling cap pin, should be connected to a 1F or 2.2F capacitor to ground for 5V application. For 3.3V application, the DEC pin can be simply connected to the 3.3V power with regular 0.1F bypass capacitor.

8.1 Memory Operation

Initialization Apply /WRST and /RRST 0.1ms after power on, then follow the following instructions for normal operation. Reset Operation The reset signal can be given at any time regardless of the /WE, /RE and /OE status, however, they still need to meet the setup time and hold time requirements with reference to the clock input. When the reset signal is provided during disabled cycles, the reset operation is not executed until cycles are enabled again. When /WRST signal is pulled low, the data input address will be set to 0 and the data in the Input Buffer will be flushed into memory cell array. When /RRST signal is pulled low, the data output address will be set to 0 and pre-fetch the data from memory cell array to Output Buffer.

AL422B

January 23, 2001

14

AL422B

Write Operation Data input DI7~DI0 is written into the write register at the WCK input when /WE is pulled low. The write data should meet the setup time and hold time requirements with reference to the WCK input cycle. Write operation is prohibited when /WE is pulled high, and the write address pointer is stopped at the current position. The write address starts from there when the /WE is pulled low again. The /WE signal needs to meet the setup time and hold time requirements with reference to the WCK input cycle. Read Operation Data output DO7~DO0 is written into the read register at the RCK input when both /RE and /OE are pulled low. The output data is ready after TAC (access time) from the rising edge of the RCK input cycle. The read address pointer is stopped at the current position when /RE is pulled high, and starts there when /RE is pulled low again. /OE needs to be pulled low for read operations. When /OE is pulled high, the data outputs will be at high impedance stage. The read address pointer still increases synchronously with RCK regardless of the /OE status. The /RE and /OE signals need to meet the setup time and hold time requirements with reference to the RCK input cycle. When the new data is read, the read address should be between 128 to 393,247 cycles after the write address, otherwise the output may not be new data.

8.2 5V and 3.3V applications

The AL422B can accept either 3.3V or 5V power with slightly different external configuration. The internal voltage regulator can convert 5V power to 3.3V for the embedded DRAM and logic circuitry when 5V power is applied to VDD pin (#10) only and leave the DEC pin (#19) decoupled by a capacitor of 1F or 2.2F to ground. The regulator can also be bypassed when 3.3V power is applied to both VDD and DEC pins. In either case the AL422B is 5V or 3.3V I/O tolerant. The 3.3V configuration consumes less power and is free from noise interference from the voltage regulator so may be more ideal for high-speed applications. Please note that using the AL422B with 5V configuration can directly replace the previous AL422V5; using it with 3.3V configuration can directly replace the previous AL422V3. No additional modification is required.

AL422B

January 23, 2001

15

AL422B

The 5V configuration (direct replacement of the previous AL422V5) is as follows:

5V

AL422B

VDD 0.1uF DEC 2.2uF

The 3.3V configuration (direct replacement of the previous AL422V3) is as follows:

3.3V 3.3V

AL422B

10 0.1uF VDD DEC 19 0.1uF

8.3 Application Notes

8.3.1 Irregular Read/Write It is recommended that the WCK and RCK are kept running at least 1MHz at all times. The faster one of WCK and RCK is used as the DRAM refresh timing clock and has to be kept free running. When irregular FIFO I/O control is needed, keep the clock free running and use /WE or /RE to control the I/O as follows:

WCK

Data

/WE

AL422-17 Slow Write - Correct

The following drawing shows irregular clock and should be avoided:

AL422B

January 23, 2001

16

AL422B

WCK

Data

/WE

AL422-16 Slow Write - Incorrect

8.3.2 The Proper Manipulation of FIFO Access The FIFO memory is designed to allow easy field delay, time-base conversion, and other types of signal processing. To ensure the expectant data can be read out from the AL422B FIFO, the proper manipulation on the AL422B FIFO memory is highly recommended 1. The read address should be between 128 to 393,247 cycles after the write address to read the current field data. (The restriction is indicated in the Read Operation Section). 2. The proper FIFO access must make sure after read reset, the read operation will either read all the old data (last field data) until next read reset, or follow the constraint 1 above to read newly update data. In any 2 read resets interval, the FIFO access can not read old data (the field data are written before last write reset), and stop for a period then read the newly update data (even at that time, write counter is ahead of read counter by more than 128 cycles). If the FIFO memory manipulations violate the above conditions, some amount of consecutive unexpected data (old data) will be read at the FIFO data bus. 8.3.3 Single Field Write with Multiple Read Operation It is one of the functions for FIFO memory that can buffer a field data and do multiple times of fields read access. In some applications, such as still image capturing, require one field write and multiple field data read operations. In order not to violate the 128 cycles of write to read delay latency rule, the write address (pointer) needs to be reset to 0 for the coming multiple read operations so that FIFO can provide the expectant data at DO bus. 8.3.4 One Field Delay Line (The Old Data Read) As the design shown in diagram by applying the reset every 1-field cycle (with the common signal for /WRST and /RRST) and a constant read/write operation (with all /WE, /RE and /OE are tied to ground), 1 field delay line timing is shown in timing chart below. When the difference between the

AL422B

January 23, 2001

17

AL422B

write address and the read address is 0 (the read address and the write address are the same), the old field data are read as shown in the timing chart.

Reset

AL422

/WRST 8-bit Input DI[7:0] /RRST DO[7:0] /OE /RE RCK Clock 8-bit Output

/WE

WCK

AL422 1 Field Delay Line Diagram

Field m cycle 0 cycle 1 cycle n cycle 0

Field m + 1 cycle 1

RCK WCK

/RRST /WRST DI7~0

tAC

DO7~0

0 Data of field m

AL422-08 1 Field Delay Line Timing Diagram

AL422B

January 23, 2001

18

AL422B

9.0 Mechanical Drawing

28 PIN PLASTIC SOP:

AL422B

January 23, 2001

19

CONTACT INFORMATION

AverLogic Technologies, Inc. 90 Great Oaks Blvd. Suite 204 San Jose, CA 95119 USA

Tel Fax E-mail URL

: 1 408 361-0400 : 1 408 361-0404 : sales@averlogic.com : www.averlogic.com

Anda mungkin juga menyukai

- 135128 - Generali - Sống - Như - Ý - - - Live - The Life You DesireDokumen6 halaman135128 - Generali - Sống - Như - Ý - - - Live - The Life You DesireHue TruongBelum ada peringkat

- (PDF) The Digital Einstein Papers - The Collected Papers of Albert EinsteinDokumen6 halaman(PDF) The Digital Einstein Papers - The Collected Papers of Albert EinsteinjuenkkinBelum ada peringkat

- Godwin Okebaram Uwah - Pirandellism and Samuel Beckett's Plays (Scripta Humanistica, Volume 48) (1989)Dokumen147 halamanGodwin Okebaram Uwah - Pirandellism and Samuel Beckett's Plays (Scripta Humanistica, Volume 48) (1989)AniBelum ada peringkat

- Merengue - Dominican Music and IdentityDokumen25 halamanMerengue - Dominican Music and IdentityLUIS FERNANDO MURO MONREALBelum ada peringkat

- Two-Wire Serial EEPROM: FeaturesDokumen28 halamanTwo-Wire Serial EEPROM: FeaturesdobsrdjanBelum ada peringkat

- 2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial InterfaceDokumen20 halaman2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial Interfacejoseleomi_limaBelum ada peringkat

- 2M X 32 Sdram: 512K X 32bit X 4 Banks Synchronous DRAM LVTTL (3.3V)Dokumen12 halaman2M X 32 Sdram: 512K X 32bit X 4 Banks Synchronous DRAM LVTTL (3.3V)vsc2012Belum ada peringkat

- IN44780U Dot Matrix Liquid Crystal Display Controller & DriverDokumen10 halamanIN44780U Dot Matrix Liquid Crystal Display Controller & DriverSilviu AdgjBelum ada peringkat

- 4-Mbit (256 K × 16) Static RAM: Features Functional DescriptionDokumen18 halaman4-Mbit (256 K × 16) Static RAM: Features Functional Descriptionprasanna_npBelum ada peringkat

- LCD Module Specs and InstructionsDokumen21 halamanLCD Module Specs and InstructionsjohnluzardoBelum ada peringkat

- 2, 4 and 8 Mutiplex LCD Driver: em MicroelectronicDokumen15 halaman2, 4 and 8 Mutiplex LCD Driver: em MicroelectronicKrzysztof BondkaBelum ada peringkat

- M U Iti-Character lED Display/lamp Driver Cmos: Motorola Semiconductor Technical DataDokumen22 halamanM U Iti-Character lED Display/lamp Driver Cmos: Motorola Semiconductor Technical DataNayeem MamunBelum ada peringkat

- 32kx8bit CMOS SRAM: HY62256B SeriesDokumen9 halaman32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsrieBelum ada peringkat

- La7693X Series: Built-In CTV Microcontroller Video and Sound Processing Ics (Vif/Sif/Y/C/Deflection/Cbcr In)Dokumen6 halamanLa7693X Series: Built-In CTV Microcontroller Video and Sound Processing Ics (Vif/Sif/Y/C/Deflection/Cbcr In)amadou1Belum ada peringkat

- FOR EEPROM DOCUMENTDokumen9 halamanFOR EEPROM DOCUMENTIram Loya ValladaresBelum ada peringkat

- Ad7524 Ep PDFDokumen8 halamanAd7524 Ep PDFjlfepeBelum ada peringkat

- 24 LC 16Dokumen32 halaman24 LC 16Jos RoBelum ada peringkat

- Agm 0070WTDokumen27 halamanAgm 0070WTbrandt_br7991Belum ada peringkat

- 128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLDokumen11 halaman128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLThiago Cristiano TavaresBelum ada peringkat

- 24AA512/24LC512/24FC512: 512K I C Cmos Serial EepromDokumen28 halaman24AA512/24LC512/24FC512: 512K I C Cmos Serial EepromAitor DuoBelum ada peringkat

- TLC 5540Dokumen18 halamanTLC 5540EdgarJCBelum ada peringkat

- Cypress SRAM CY62256Dokumen11 halamanCypress SRAM CY62256MicroemissionBelum ada peringkat

- DS1307 Real Time ClockDokumen14 halamanDS1307 Real Time Clockpraveen_kodgirwarBelum ada peringkat

- Datasheet CY62146DV30LDokumen11 halamanDatasheet CY62146DV30LedgarlibanioBelum ada peringkat

- Lc470wul Sbm1 DatasheetDokumen41 halamanLc470wul Sbm1 DatasheetsorosororiBelum ada peringkat

- At93c46d TH B AtmelDokumen6 halamanAt93c46d TH B Atmelatorresh090675Belum ada peringkat

- Ca3306 (A, C)Dokumen17 halamanCa3306 (A, C)notaden1849Belum ada peringkat

- Irs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICDokumen29 halamanIrs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICAnonymous R0s4q9X8Belum ada peringkat

- DS1307 Datasheet FullDokumen15 halamanDS1307 Datasheet FulllamanzanadeadanBelum ada peringkat

- Displaytech 162ADokumen17 halamanDisplaytech 162AjanepriceBelum ada peringkat

- 24 LC 2561Dokumen12 halaman24 LC 2561ricardo_MassisBelum ada peringkat

- Atmel 24C02Dokumen26 halamanAtmel 24C02kukinjosBelum ada peringkat

- N156B6 L08Dokumen31 halamanN156B6 L08JozefBelum ada peringkat

- U34 - Dram Hy57v641620ftp7Dokumen13 halamanU34 - Dram Hy57v641620ftp7qwertyuBelum ada peringkat

- 24 LC 64Dokumen12 halaman24 LC 64achuthkumarBelum ada peringkat

- LA76933JDokumen6 halamanLA76933JAbid KhanBelum ada peringkat

- Cmos Asynchronous Fifo 256 X 9, 512 X 9 and 1,024 X 9 IDT7200L IDT7201LA IDT7202LADokumen14 halamanCmos Asynchronous Fifo 256 X 9, 512 X 9 and 1,024 X 9 IDT7200L IDT7201LA IDT7202LAnevdullBelum ada peringkat

- At25f512a 844895Dokumen19 halamanAt25f512a 844895mirage0706Belum ada peringkat

- 24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsDokumen12 halaman24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsBoris PopovBelum ada peringkat

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesDokumen14 halamanDS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesAn TrìnhBelum ada peringkat

- 24lc08 EepromDokumen27 halaman24lc08 EepromIsmael Minchola CarhuasBelum ada peringkat

- 24 LC 128Dokumen26 halaman24 LC 128Santiago DiosdadoBelum ada peringkat

- Document Title: GM76C256CDokumen11 halamanDocument Title: GM76C256CFrenk EndyBelum ada peringkat

- Atmel 24C1024Dokumen19 halamanAtmel 24C1024vax1Belum ada peringkat

- CD4047Dokumen9 halamanCD4047Haryadi VjBelum ada peringkat

- Ltn154at01 001 PDFDokumen13 halamanLtn154at01 001 PDFreddogsfpBelum ada peringkat

- Ads 7870Dokumen43 halamanAds 7870Moorthy VenkatachalamBelum ada peringkat

- 256K X 16 4Mb Asynchronous SRAMDokumen12 halaman256K X 16 4Mb Asynchronous SRAMRyanBelum ada peringkat

- Display 16230 Datasheet.Dokumen16 halamanDisplay 16230 Datasheet.José DalmiBelum ada peringkat

- IS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplyDokumen17 halamanIS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplywarekinBelum ada peringkat

- MemoriaDokumen7 halamanMemoriaEduardo TaglialavoreBelum ada peringkat

- Hanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDokumen9 halamanHanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDeepa DevarajBelum ada peringkat

- 89v51Rd2 Microcontroller: Appendix 1Dokumen10 halaman89v51Rd2 Microcontroller: Appendix 1AmrutanarkhedeBelum ada peringkat

- 24LC024Dokumen22 halaman24LC024David ChaoBelum ada peringkat

- aIVR1004 2104 4208Dokumen8 halamanaIVR1004 2104 4208huytung1501Belum ada peringkat

- 128K X 8 Static RAM: PreliminaryDokumen8 halaman128K X 8 Static RAM: PreliminaryRoozbeh BahmanyarBelum ada peringkat

- LCD Module Specification Sheet for MTC-C162DPLY-2N DisplayDokumen17 halamanLCD Module Specification Sheet for MTC-C162DPLY-2N Displayashwin_mcseBelum ada peringkat

- 24LC02BDokumen26 halaman24LC02Bjab_arx1Belum ada peringkat

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxDari EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxPenilaian: 4 dari 5 bintang4/5 (2)

- Digital Power Electronics and ApplicationsDari EverandDigital Power Electronics and ApplicationsPenilaian: 3.5 dari 5 bintang3.5/5 (3)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDari EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsPenilaian: 3.5 dari 5 bintang3.5/5 (6)

- TN Appsvr144 Overview of Scripting in System Platform - InSource KnowledgeCenterDokumen5 halamanTN Appsvr144 Overview of Scripting in System Platform - InSource KnowledgeCenterjuenkkinBelum ada peringkat

- 8-/10-Channel, Low Voltage, Low Power,: - AdcsDokumen44 halaman8-/10-Channel, Low Voltage, Low Power,: - AdcsjuenkkinBelum ada peringkat

- A Scheme For A Flexible Classification of Dietary and Health Biomarkers2017Genes and NutritionOpen AccessDokumen15 halamanA Scheme For A Flexible Classification of Dietary and Health Biomarkers2017Genes and NutritionOpen AccessjuenkkinBelum ada peringkat

- 4 Methods To Fix Toshiba External Hard Drive Not Working Error - EaseUSDokumen14 halaman4 Methods To Fix Toshiba External Hard Drive Not Working Error - EaseUSjuenkkinBelum ada peringkat

- Solved - Shown in The Figure Below Is A Simplified Dynamic ...Dokumen2 halamanSolved - Shown in The Figure Below Is A Simplified Dynamic ...juenkkinBelum ada peringkat

- Quiz 1Dokumen6 halamanQuiz 1juenkkinBelum ada peringkat

- I Am Lacking The WinCC Component Object Manager PackageDokumen3 halamanI Am Lacking The WinCC Component Object Manager PackagejuenkkinBelum ada peringkat

- Why Can Projects, Blocks or The HW Config Either Not Be Opened at All or Only Open... - ID - 22809379 - Industry Support SiemensDokumen2 halamanWhy Can Projects, Blocks or The HW Config Either Not Be Opened at All or Only Open... - ID - 22809379 - Industry Support Siemensjuenkkin100% (1)

- Configurint MBTCP DAServerDokumen11 halamanConfigurint MBTCP DAServerHenrique TrebilcockBelum ada peringkat

- 4 Methods To Fix Toshiba External Hard Drive Not Working Error - EaseUSDokumen14 halaman4 Methods To Fix Toshiba External Hard Drive Not Working Error - EaseUSjuenkkinBelum ada peringkat

- (SOLVED) Data Error (Cyclic Redundancy Check) - Driver EasyDokumen10 halaman(SOLVED) Data Error (Cyclic Redundancy Check) - Driver EasyjuenkkinBelum ada peringkat

- SHT 3Dokumen5 halamanSHT 3juenkkinBelum ada peringkat

- Free HDD Utility Scans Drives for Bad Blocks & Displays S.M.A.R.T. DataDokumen24 halamanFree HDD Utility Scans Drives for Bad Blocks & Displays S.M.A.R.T. DataOscar Alfonso Hernandez NiklitschekBelum ada peringkat

- STM32 PeripheralsDokumen91 halamanSTM32 Peripheralschaouachitaoufik100% (4)

- Description Wincc Project Scanner en PDFDokumen9 halamanDescription Wincc Project Scanner en PDFjuenkkinBelum ada peringkat

- An Archestra Object Can't Be C... Her User... - InSource KnowledgeCenterDokumen2 halamanAn Archestra Object Can't Be C... Her User... - InSource KnowledgeCenterjuenkkinBelum ada peringkat

- 13 Iccge2012l30007Dokumen5 halaman13 Iccge2012l30007L30N1Belum ada peringkat

- 2711pc-Um001 - En-P (PanelView Plus Compact Terminals - User Manual), 2009-03Dokumen132 halaman2711pc-Um001 - En-P (PanelView Plus Compact Terminals - User Manual), 2009-03MancamiaicuruBelum ada peringkat

- Viewme-In003 - En-E (FactoryTalk View Machine Edition - Installation Guide, 2013-01)Dokumen50 halamanViewme-In003 - En-E (FactoryTalk View Machine Edition - Installation Guide, 2013-01)MancamiaicuruBelum ada peringkat

- WinCC Communication en-US en-US PDFDokumen554 halamanWinCC Communication en-US en-US PDFjuenkkinBelum ada peringkat

- PCS7 Tips&TricksDokumen618 halamanPCS7 Tips&TricksJorge50% (2)

- Webinar stm32 20170511 PDFDokumen141 halamanWebinar stm32 20170511 PDFsushisenseiBelum ada peringkat

- Description Wincc Project Scanner en PDFDokumen9 halamanDescription Wincc Project Scanner en PDFjuenkkinBelum ada peringkat

- Lista de Verbos Regulares e IrregularesDokumen11 halamanLista de Verbos Regulares e IrregularesHenry Valverde100% (1)

- NetToPLCsim Extends PLCsim for Network TestingDokumen11 halamanNetToPLCsim Extends PLCsim for Network Testingjuenkkin100% (1)

- Truyenthong CPNet FC, FBDokumen334 halamanTruyenthong CPNet FC, FBNguyễn Anh TúBelum ada peringkat

- PCS7 Tips&TricksDokumen618 halamanPCS7 Tips&TricksJorge50% (2)

- DasSIDirect PDFDokumen156 halamanDasSIDirect PDFjuenkkinBelum ada peringkat

- HistClient SP1Dokumen874 halamanHistClient SP1sexybeest3384Belum ada peringkat

- CertsDokumen8 halamanCertsJomar Mapue PormentoBelum ada peringkat

- Surviving (Surrender #2) by Ahren Sanders PDFDokumen281 halamanSurviving (Surrender #2) by Ahren Sanders PDFDinu Catalina80% (5)

- WX NotamsDokumen37 halamanWX NotamsJohn AngusBelum ada peringkat

- 12 51 Lyrics With ChordsDokumen3 halaman12 51 Lyrics With ChordsQuenn Rose ToslocBelum ada peringkat

- 20 - 01-01 Q MagazineDokumen132 halaman20 - 01-01 Q MagazineM BBelum ada peringkat

- Perusal Script: Chip Deffaa Irving Berlin Chip DeffaaDokumen77 halamanPerusal Script: Chip Deffaa Irving Berlin Chip DeffaaJoeHodgesBelum ada peringkat

- Using Mis 5th Edition Kroenke Solutions ManuaDwnload Full Using Mis 5th Edition Kroenke Solutions Manual PDFDokumen35 halamanUsing Mis 5th Edition Kroenke Solutions ManuaDwnload Full Using Mis 5th Edition Kroenke Solutions Manual PDFmicrondeafen.4dw0p100% (9)

- Ivan KUZMINSKYI History of The Origin of The Bogurodzica Song. A Musical Monument of 1407Dokumen15 halamanIvan KUZMINSKYI History of The Origin of The Bogurodzica Song. A Musical Monument of 1407Іван КузьмінськийBelum ada peringkat

- Noa-Am - Folk Dance Videos - International Folk Dancing in IsraelDokumen4 halamanNoa-Am - Folk Dance Videos - International Folk Dancing in IsraelSalvatore BonaffinoBelum ada peringkat

- N 12 Electrical Experi 06 GernDokumen92 halamanN 12 Electrical Experi 06 GernfabiormatosBelum ada peringkat

- Sloop John B PDFDokumen1 halamanSloop John B PDFWatila Ramos GrachetBelum ada peringkat

- Mplayer CommandsDokumen11 halamanMplayer CommandsadministradorxBelum ada peringkat

- TM11-2654 Vacuum Tube Voltmeter Hickok Model 110-B, 1945Dokumen89 halamanTM11-2654 Vacuum Tube Voltmeter Hickok Model 110-B, 1945david_graves_okstateBelum ada peringkat

- DxdiagDokumen29 halamanDxdiagFlorim RamadaniBelum ada peringkat

- Beethoven Sonata 19Dokumen4 halamanBeethoven Sonata 19MorlaBelum ada peringkat

- An Introduction to Fire Detection SystemsDokumen59 halamanAn Introduction to Fire Detection SystemsMihai MateiBelum ada peringkat

- Percussion Nomenclature PDFDokumen3 halamanPercussion Nomenclature PDFGiovanniBelum ada peringkat

- Juaranya GAMING Bintangnya STREAMINGDokumen1 halamanJuaranya GAMING Bintangnya STREAMINGDwi JanuarBelum ada peringkat

- Lecture 8. IntonationDokumen70 halamanLecture 8. IntonationNguyễn Thị Thuỳ ThươngBelum ada peringkat

- Waves EQ MSDokumen42 halamanWaves EQ MSnchauhan2120% (1)

- Oye Como Va: Alto SaxophoneDokumen1 halamanOye Como Va: Alto SaxophoneAgnes ChekalinaBelum ada peringkat

- ProLaser III Users Manual 2006-05-08 PDFDokumen47 halamanProLaser III Users Manual 2006-05-08 PDFPeter Shearer100% (1)

- Multiple Intelligences SurveyDokumen5 halamanMultiple Intelligences SurveyDianne Marie MartinezBelum ada peringkat

- YAMAHA YAS-62 ManualDokumen12 halamanYAMAHA YAS-62 ManualTimikiti JaronitiBelum ada peringkat

- Luna Benamor by Blasco Ibáñez, Vicente, 1867-1928Dokumen57 halamanLuna Benamor by Blasco Ibáñez, Vicente, 1867-1928Gutenberg.orgBelum ada peringkat

- Deh-X9550bt Deh-X9550sd Operating Manual Eng-Esp-PorDokumen156 halamanDeh-X9550bt Deh-X9550sd Operating Manual Eng-Esp-PorBernabe AcostaBelum ada peringkat

- Every Major and Minor Chord: C Major C E G C Minor C E GDokumen4 halamanEvery Major and Minor Chord: C Major C E G C Minor C E GAn Phạm Thị Phước100% (1)