Tutorial08 Solution

Diunggah oleh

Bobby BeamanHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Tutorial08 Solution

Diunggah oleh

Bobby BeamanHak Cipta:

Format Tersedia

Technische Universitt Mnchen

Chip Multicore Processors

Tutorial 8

S. Wallentowitz

Institute for Integrated Systems Theresienstr. 90 Building N1 www.lis.ei.tum.de

Technische Universitt Mnchen

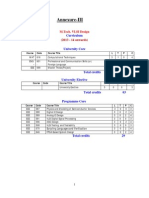

Task 8.1: Performance of Snooping-based Cache Cohereny

0 1 2 3 I S M I 408 410 54 | 04 20 | 01 400 408 0 1 2 3 I M I S 418 0a | 00 428 00 | 20 410 ... 00 | 00 54 | 04 03 | 00

418

420 428 430

00 | 00

01 | 02 0c | d0 00 | ff 00 | 00 ...

0 1 2 3

S S M I

420 408 430

01 | 02 54 | 04 00 | 00

438

Chip Multicore Processors Tutorial 8 2 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

a) sequence 1

1: (P1) read 410 2: (P2) read 410 3: (P0) read 430 3: replace

0 1 I S M I 408 410 S 430 54 | 04 20 | 01 00 | 00 ... 400 408 00 | 00 54 | 04 20 | 01 03 | 00

1: write back

2 3

1: 2: 3:

+ + 200 cycles

2: write back and load 1: read miss

0 1 2 3

I M I S S 428 410 418 00 | 20 20 | 01 0a | 00

410

418

420 428 430

00 | 00

01 | 02 0c | d0 00 | ff 00 | 00 00 | 00 ...

0 1 2 3

S S M I S

420 408 430 410

01 | 02 54 | 04 00 | 00 20 | 01

438

Chip Multicore Processors Tutorial 8 3 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

a) sequence 2

1: write miss 1: (P0) write 420, 42 2: (P2) read 424 3: (P2) write 424, 23 2: write back 3: invalidate

0 1 2 3 I 420 MS I S 408 M I 410 01 | 42 54 | 04 20 | 01 400 408 ... 00 | 00 54 | 04 03 | 00

1: 2: 3:

+ 124 cycles

1: snoop WM 2: read miss

0 1 2 3

I M I S 418 0a | 00 23 | 42 01 | 02 01 | 42 54 | 04 00 | 00 428 00 | 20

410

418

420 428 430

00 | 00

01 | 02 01 | 42 0c | d0 00 | ff 00 | 00 ...

0 1 2 3

420 ISM S 408 M I 430

438

3: invalidate

Chip Multicore Processors Tutorial 8 4 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

a) sequence 3

1: (P0) write 420, 42 2: (P2) read 424 3: (P2) write 424, 23

0 1 2 3 I S M I 408 410 54 | 04 20 | 01 400 408 ... 00 | 00 54 | 04 03 | 00

Self Study

0 1 2 3

I M I S 418 0a | 00 428 00 | 20

410

418

420 428 430

00 | 00

01 | 02 0c | d0 00 | ff 00 | 00 ...

0 1 2 3

S S M I

420 408 430

01 | 02 54 | 04 00 | 00

438

Chip Multicore Processors Tutorial 8 5 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

8.1 b)

To optimize the external accesses an owner state (O) is added to the cache coherency protocol. On a write, all other cache entries should be invalidated (write-invalidate). Instead of the memory the current owner will give the data on a read access of another cache. Sketch the modified diagramm of the MOSI protocol.

Chip Multicore Processors Tutorial 8 6 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

Example Coherency Protocol (MSI)

Invalidate Write Miss Read Hit

Invalid

CPU Write Miss (Place write miss on bus)

CPU Read Miss (Place read miss on bus)

Shared

Read Miss

Write Miss (Write Back)

All actions on cache lines Write-back cache Processor triggered

Events Cache actions

Modified

Hit

Bus triggered

Events Cache actions

Chip Multicore Processors Tutorial 8 7 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

MOSI

Invalidate Write Miss Read Hit

Invalid

Write Miss (Write Back)

Read Miss (Read Miss)

Shared

Read Miss Write (Invalidate)

Write Miss (Write miss)

Eviction (Write Back)

Read Miss (Provide Data) Write (Invalidate) Read Miss (Provide Data)

Modified

Read/Write Hit

Owner

Read Hit

Chip Multicore Processors Tutorial 8 8 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

c) sequence 1

1: (P1) read 410 2: (P2) read 410 3: (P0) read 430 3: replace

0 1 I S M 408 54 | 04 20 | 01 00 | 00 ... 400 408 0 1 I M I S S 428 410 418 00 | 20 20 | 01 0a | 00 410 00 | 00 54 | 04 20 | 01 03 | 00

1: provide data 2: provide data

2 3

410 O 430 I S

1: 2: 3:

+ + 152 cycles

2: write back and load 1: read miss

418

420 428 430

00 | 00

01 | 02 0c | d0 00 | ff 00 | 00 00 | 00 ...

2 3

0 1 2 3

S S M I S

420 408 430 410

01 | 02 54 | 04 00 | 00 20 | 01

438

Chip Multicore Processors Tutorial 8 9 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

c) sequence 2

1: write miss 1: (P0) write 420, 42 2: (P2) read 424 3: (P2) write 424, 23 2: provide data 3: invalidate

0 1 2 3 I 420 MO I S 408 M I 410 01 | 42 54 | 04 20 | 01 400 408 ... 00 | 00 54 | 04 03 | 00

1: 2: 3:

60 cycles

1: snoop WM, dont provide 2: read miss

0 1 2 3

I M I S 418 0a | 00 23 | 42 01 | 02 01 | 42 54 | 04 00 | 00 428 00 | 20

410

418

420 428 430

00 | 00

01 | 02 0c | d0 00 | ff 00 | 00 ...

0 1 2 3

420 ISM S 408 M I 430

438

3: invalidate

Chip Multicore Processors Tutorial 8 10 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

a) sequence 3

1: (P0) write 420, 42 2: (P2) read 424 3: (P2) write 424, 23

0 1 2 3 I S M I 408 410 54 | 04 20 | 01 400 408 ... 00 | 00 54 | 04 03 | 00

Self Study: Will be online

0 1 2 3

I M I S 418 0a | 00 428 00 | 20

410

418

420 428 430

00 | 00

01 | 02 0c | d0 00 | ff 00 | 00 ...

0 1 2 3

S S M I

420 408 430

01 | 02 54 | 04 00 | 00

438

Chip Multicore Processors Tutorial 8 11 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

8.2

Read the article Memory Performance and Cache Coherency Effects on an Intel Nehalem Multiprocessor System, Daniel Molka et al., PACT 2009. Shortly describe the investigated architecture? What is decribed by the term ccNUMA? How do the information in the L3 cache relate to the other levels and how precise is it? Shortly describe the executed benchmarks and central findings of the article.

Chip Multicore Processors Tutorial 8 12 S. Wallentowitz

Institute for Integrated Systems

Technische Universitt Mnchen

ccNUMA: non-uniform memory access, cache coherent L3: inclusive last level, core valid bits are imprecise

0: core does for sure not hold a copy 1: core may hold a copy

Benchmarks: latency, local and global bandwidth

Chip Multicore Processors Tutorial 8 13 S. Wallentowitz

Institute for Integrated Systems

Anda mungkin juga menyukai

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureDari EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitecturePenilaian: 1 dari 5 bintang1/5 (1)

- Design of Robotic ARM Controller Using MatlabDokumen24 halamanDesign of Robotic ARM Controller Using MatlabMada Sanjaya WsBelum ada peringkat

- 184 PDFDokumen116 halaman184 PDFcalciumblessingBelum ada peringkat

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationDari EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationBelum ada peringkat

- HackSpaceMagazine21 PDFDokumen132 halamanHackSpaceMagazine21 PDFSky King100% (1)

- Interfacing PIC Microcontrollers: Embedded Design by Interactive SimulationDari EverandInterfacing PIC Microcontrollers: Embedded Design by Interactive SimulationBelum ada peringkat

- 800 KV TL DesignDokumen67 halaman800 KV TL Designravi0312150% (2)

- Lab3 PDFDokumen34 halamanLab3 PDFVõ Bá Quang Duy100% (1)

- 3-Emebbedd Question BankDokumen31 halaman3-Emebbedd Question BankamulumullaiBelum ada peringkat

- XP Series Parts ListDokumen45 halamanXP Series Parts ListspirisBelum ada peringkat

- HPE Proliant Server Foundation TestDokumen13 halamanHPE Proliant Server Foundation Test3amer10% (10)

- Chip Multicore Processors: Tutorial 9Dokumen19 halamanChip Multicore Processors: Tutorial 9Bobby BeamanBelum ada peringkat

- VLSI SyllabusDokumen57 halamanVLSI SyllabusAkshay DeshpandeBelum ada peringkat

- Abes Engineering College, Ghaziabad: Department of Electronics & Communication EngineeringDokumen80 halamanAbes Engineering College, Ghaziabad: Department of Electronics & Communication EngineeringJayan GoelBelum ada peringkat

- Scheme of B - Tech ECE Batch 2011 - Uploaded - 06 - 06 - 13 PDFDokumen34 halamanScheme of B - Tech ECE Batch 2011 - Uploaded - 06 - 06 - 13 PDFdilpalsBelum ada peringkat

- Ptu Syllabus For Bath 2011 OnwardsDokumen34 halamanPtu Syllabus For Bath 2011 Onwardsjassi7010Belum ada peringkat

- ECE - (4 Year B.Tech Programme) - COURSE CURRICULUM R-19Dokumen18 halamanECE - (4 Year B.Tech Programme) - COURSE CURRICULUM R-19320126512L20 yerramsettibhaskarBelum ada peringkat

- Syllabus MecveDokumen44 halamanSyllabus MecveronpeterpBelum ada peringkat

- Vlsi Design ECE5014Dokumen5 halamanVlsi Design ECE5014SriramBelum ada peringkat

- M.E. Applied ElectronicsDokumen40 halamanM.E. Applied ElectronicsRaja RamachandranBelum ada peringkat

- R-20 3-4 SyllabusDokumen93 halamanR-20 3-4 SyllabusrishiBelum ada peringkat

- B. Tech. (H) SyllabusDokumen42 halamanB. Tech. (H) SyllabusMahendra DhadweBelum ada peringkat

- Activity 1.1.3 - Scientific & Engineering Notation - Digital ElectronicsDokumen4 halamanActivity 1.1.3 - Scientific & Engineering Notation - Digital ElectronicsKatherine ZwienerBelum ada peringkat

- MEBD Embedded Systems Scheme With Syllabus - 2011Dokumen40 halamanMEBD Embedded Systems Scheme With Syllabus - 2011imbharteshBelum ada peringkat

- Vlsi PT 2nd Year SyllabusDokumen20 halamanVlsi PT 2nd Year SyllabusMANGAL KUMAR MOHAPATRABelum ada peringkat

- Unit 2 - Embedded SystemDokumen75 halamanUnit 2 - Embedded Systemsujith100% (4)

- Digital Design Lec1 IntroductionDokumen43 halamanDigital Design Lec1 IntroductionAnh TấnBelum ada peringkat

- 8086 Hardware SpecificationsDokumen21 halaman8086 Hardware SpecificationsAYSHA AKMAL 183-15-11959Belum ada peringkat

- ObjectsDokumen385 halamanObjectsSerkalem TayeBelum ada peringkat

- R18 B.tech 3-1 ECE SyllabusDokumen18 halamanR18 B.tech 3-1 ECE SyllabusNikhil SadhulaBelum ada peringkat

- Cukurova University Faculty of Engineering and Architecture Department of Mechanical Engineering Experiment ReportDokumen8 halamanCukurova University Faculty of Engineering and Architecture Department of Mechanical Engineering Experiment ReportSülbiye İşçi TemizciBelum ada peringkat

- Cmos7 Feb June15Dokumen60 halamanCmos7 Feb June15senthilBelum ada peringkat

- M.S Ramaiah School of Advanced Studies: Postgraduate Engineering and Management Programme (Pemp)Dokumen5 halamanM.S Ramaiah School of Advanced Studies: Postgraduate Engineering and Management Programme (Pemp)Subin PuthanBelum ada peringkat

- M.E VlsiDokumen25 halamanM.E VlsiDurai SelvanBelum ada peringkat

- Etc-1111-Sem 7Dokumen14 halamanEtc-1111-Sem 7Vivek SoniBelum ada peringkat

- MCU MSE 8510 Getting StartedDokumen16 halamanMCU MSE 8510 Getting StartedGhislain GorissenBelum ada peringkat

- Ac31b GBDokumen221 halamanAc31b GBSihamaSihamBelum ada peringkat

- 2008 Lab SyllabusDokumen22 halaman2008 Lab SyllabusAshok VaradarajanBelum ada peringkat

- Aust Fall06 ReferredDokumen3 halamanAust Fall06 ReferredAbir LovesickBelum ada peringkat

- M.tech-ECE-Embedded Systems (ES) - SEM1 Course Structure & SyllabiDokumen8 halamanM.tech-ECE-Embedded Systems (ES) - SEM1 Course Structure & Syllabisatraj5Belum ada peringkat

- Analysis of the Fastest Worm in History - The W32.Slammer WormDokumen17 halamanAnalysis of the Fastest Worm in History - The W32.Slammer WormVamsi ReddyBelum ada peringkat

- A Course PlanECE521 Sept2011Dokumen4 halamanA Course PlanECE521 Sept2011silentsioBelum ada peringkat

- M.E. Applied Electronics Curriculum and SyllabusDokumen39 halamanM.E. Applied Electronics Curriculum and SyllabusVENKIBelum ada peringkat

- CPE 014 Activity 5 1 PDFDokumen9 halamanCPE 014 Activity 5 1 PDFshi unlockBelum ada peringkat

- Department of Technology Mission and Program ObjectivesDokumen61 halamanDepartment of Technology Mission and Program ObjectivesUsman ZahidBelum ada peringkat

- RMK Group A4 PPT - MPMC - Ec8691 - Unit 1Dokumen127 halamanRMK Group A4 PPT - MPMC - Ec8691 - Unit 1Gowtham Reddy Rekkala100% (1)

- Tutorial10 SolutionDokumen14 halamanTutorial10 SolutionBobby BeamanBelum ada peringkat

- CMOS Digital I C Analysis & DesignDokumen7 halamanCMOS Digital I C Analysis & DesignTarun TyagiBelum ada peringkat

- 15EC62T - Embedded Systems Electronics 6th Sem Syllabus For Diploma DTE Karnataka C15 Scheme - All About VTUDokumen11 halaman15EC62T - Embedded Systems Electronics 6th Sem Syllabus For Diploma DTE Karnataka C15 Scheme - All About VTURajesh KumarBelum ada peringkat

- Modicon Quantum 140 CPU 651 60 Automation ControllerDokumen3 halamanModicon Quantum 140 CPU 651 60 Automation ControllerMehtab AhmedBelum ada peringkat

- M.Tech 2nd SemesterDokumen14 halamanM.Tech 2nd SemesterSivaramsharma RupavathamBelum ada peringkat

- M.Tech Microelectronics and VLSI Design CurriculumDokumen31 halamanM.Tech Microelectronics and VLSI Design CurriculumEC ROCKERSBelum ada peringkat

- PESIT Bangalore South Campus: Internal Assessment Test 1Dokumen8 halamanPESIT Bangalore South Campus: Internal Assessment Test 1UdupiSri groupBelum ada peringkat

- Core Categories Course Name Course Code Stream Core (SC) : VDTT Department Subjects (Design Stream)Dokumen3 halamanCore Categories Course Name Course Code Stream Core (SC) : VDTT Department Subjects (Design Stream)Vijit GadiBelum ada peringkat

- IC Syllabus For Calicut UniversityDokumen135 halamanIC Syllabus For Calicut UniversityAnith MohanBelum ada peringkat

- ESD Manual StudentsDokumen55 halamanESD Manual StudentsNimesh PrajapatiBelum ada peringkat

- Syllabus 3 Year (Effective From Session 2016-17) : Dr. A.P.J. Abdul Kalam Technical University Uttar Pradesh, LucknowDokumen24 halamanSyllabus 3 Year (Effective From Session 2016-17) : Dr. A.P.J. Abdul Kalam Technical University Uttar Pradesh, LucknowAvnishBelum ada peringkat

- JNTUA ECE Regulations R20Dokumen25 halamanJNTUA ECE Regulations R20Kondativenugopal ChowdaryBelum ada peringkat

- JNTUA ECE Regulations R20Dokumen48 halamanJNTUA ECE Regulations R20SalindramTharunkumar SalindramTharunkumarBelum ada peringkat

- B.Tech - ECE R15 Regulations Dec 171Dokumen90 halamanB.Tech - ECE R15 Regulations Dec 171Jayasimha ThummalaBelum ada peringkat

- Bachelor of Technology (Electronics and Communication Engg.) Scheme of Courses/Examination (Iii - Semester)Dokumen6 halamanBachelor of Technology (Electronics and Communication Engg.) Scheme of Courses/Examination (Iii - Semester)Gudda LalaBelum ada peringkat

- M Tech VLSI Design SyllabusDokumen46 halamanM Tech VLSI Design SyllabusVirupakshi MadhurimaBelum ada peringkat

- SE Syllabus DTUDokumen152 halamanSE Syllabus DTUMayukh MaitraBelum ada peringkat

- Vlsi NotesDokumen5 halamanVlsi NotesDiwakar TiwaryBelum ada peringkat

- Tutorial10 SolutionDokumen14 halamanTutorial10 SolutionBobby BeamanBelum ada peringkat

- Chip Multicore Processors - Tutorial 11: Task 11.1: RoutingDokumen2 halamanChip Multicore Processors - Tutorial 11: Task 11.1: RoutingBobby BeamanBelum ada peringkat

- Chip Multicore Processors - Tutorial 10: Task 10.1: Why On-Chip Coherence Is Here To StayDokumen2 halamanChip Multicore Processors - Tutorial 10: Task 10.1: Why On-Chip Coherence Is Here To StayBobby BeamanBelum ada peringkat

- Tutorial11 SolutionDokumen38 halamanTutorial11 SolutionBobby BeamanBelum ada peringkat

- Tutorial 09Dokumen5 halamanTutorial 09Bobby BeamanBelum ada peringkat

- Chip Multicore Processors - Tutorial 6: Task 6.1: Cache MissesDokumen1 halamanChip Multicore Processors - Tutorial 6: Task 6.1: Cache MissesBobby BeamanBelum ada peringkat

- Chip Multicore Processors: Tutorial 7Dokumen12 halamanChip Multicore Processors: Tutorial 7Bobby BeamanBelum ada peringkat

- Chip Multicore Processors - Tutorial 8: Task 8.1: Performance of Snooping-Based Cache CoherencyDokumen3 halamanChip Multicore Processors - Tutorial 8: Task 8.1: Performance of Snooping-Based Cache CoherencyBobby BeamanBelum ada peringkat

- Tutorial05 SolutionDokumen23 halamanTutorial05 SolutionBobby BeamanBelum ada peringkat

- Tutorial06 SolutionDokumen16 halamanTutorial06 SolutionBobby BeamanBelum ada peringkat

- Memory Overhead of Cache Coherency TutorialDokumen2 halamanMemory Overhead of Cache Coherency TutorialBobby BeamanBelum ada peringkat

- Chip Multicore Processors - Tutorial 5: Task 5.1: SemaphoresDokumen1 halamanChip Multicore Processors - Tutorial 5: Task 5.1: SemaphoresBobby BeamanBelum ada peringkat

- Tutorial03 SolutionDokumen21 halamanTutorial03 SolutionBobby BeamanBelum ada peringkat

- Chip Multicore Processors - Tutorial 4: Task 4.1: Counter ImplementationDokumen1 halamanChip Multicore Processors - Tutorial 4: Task 4.1: Counter ImplementationBobby BeamanBelum ada peringkat

- Chip Multicore Processors: Tutorial 4Dokumen21 halamanChip Multicore Processors: Tutorial 4Bobby BeamanBelum ada peringkat

- Simple Chocolate Cupcakes Recipe - Best RecipesDokumen1 halamanSimple Chocolate Cupcakes Recipe - Best RecipesBobby BeamanBelum ada peringkat

- Chip Multicore Processors - Tutorial 3: 3.1: 3-Thread LockDokumen2 halamanChip Multicore Processors - Tutorial 3: 3.1: 3-Thread LockBobby BeamanBelum ada peringkat

- 2008 FinalExam SoCN Final Master SolutionDokumen10 halaman2008 FinalExam SoCN Final Master SolutionBobby BeamanBelum ada peringkat

- 2010 FinalExam SoCN SolutionDokumen12 halaman2010 FinalExam SoCN SolutionBobby BeamanBelum ada peringkat

- Chip Multicore Processors - Tutorial 2: 2.1: Frequency and Voltage Scaling, Amdahl's LawDokumen2 halamanChip Multicore Processors - Tutorial 2: 2.1: Frequency and Voltage Scaling, Amdahl's LawBobby BeamanBelum ada peringkat

- Tutorial 1 - IntroductionDokumen4 halamanTutorial 1 - IntroductionBobby BeamanBelum ada peringkat

- SoC Solutions in Networking Final ExamDokumen10 halamanSoC Solutions in Networking Final ExamBobby BeamanBelum ada peringkat

- Network Processor Packet Processing RatesDokumen12 halamanNetwork Processor Packet Processing RatesBobby BeamanBelum ada peringkat

- 2008 FinalExam SoCN Final Master SolutionDokumen10 halaman2008 FinalExam SoCN Final Master SolutionBobby BeamanBelum ada peringkat

- 2008 FinalExam SoCNDokumen10 halaman2008 FinalExam SoCNBobby BeamanBelum ada peringkat

- Simple Chocolate Cupcakes Recipe - Best RecipesDokumen1 halamanSimple Chocolate Cupcakes Recipe - Best RecipesBobby BeamanBelum ada peringkat

- Firefox Shortcuts WinDokumen4 halamanFirefox Shortcuts Winmourya2175Belum ada peringkat

- Akiyama ASIO Driver A101 ManualDokumen8 halamanAkiyama ASIO Driver A101 ManualNicolás Gómez ÁlvarezBelum ada peringkat

- Chapter 19 Testing and Troubleshooting NetworksDokumen39 halamanChapter 19 Testing and Troubleshooting Networkshclraj406Belum ada peringkat

- ProfibusResistance TestDokumen6 halamanProfibusResistance Testplazmorezka74Belum ada peringkat

- Daikin Siesta Error Code PDFDokumen169 halamanDaikin Siesta Error Code PDFfuturamsBelum ada peringkat

- 15.0 The Round and Chamfer CommandsDokumen10 halaman15.0 The Round and Chamfer CommandsfabrcadBelum ada peringkat

- The Innovative New NOVA Series NIR TransmitterDokumen4 halamanThe Innovative New NOVA Series NIR TransmitterDwi April YantoBelum ada peringkat

- UNIT II - Multi Core ArchitectureDokumen102 halamanUNIT II - Multi Core ArchitectureVivek DubeyBelum ada peringkat

- 17078EN TLMP SeriesDokumen2 halaman17078EN TLMP Seriesxuanphuong2710Belum ada peringkat

- Taiwan Kolin V. Kolin ElectronicsDokumen10 halamanTaiwan Kolin V. Kolin ElectronicsZmr Situation PulveraBelum ada peringkat

- Arfa KarimDokumen3 halamanArfa KarimSyed HussainiBelum ada peringkat

- 37pfl5604h 12 Pss EngDokumen3 halaman37pfl5604h 12 Pss EnguhvhhhBelum ada peringkat

- Evermotion Evermotion Archmodels All Vol PDFDokumen2 halamanEvermotion Evermotion Archmodels All Vol PDFBellaBelum ada peringkat

- Understanding I2C BusDokumen8 halamanUnderstanding I2C BusMai Khoa100% (1)

- 8049Dokumen239 halaman8049adnantanBelum ada peringkat

- Digital ClockDokumen6 halamanDigital ClockAlex Xander AcayenBelum ada peringkat

- RRU3824&RRU3826 Hardware Description (04) (PDF) - EN PDFDokumen34 halamanRRU3824&RRU3826 Hardware Description (04) (PDF) - EN PDFJubril Akinwande100% (5)

- DataGuard T5R Vs Iomega 1Dokumen2 halamanDataGuard T5R Vs Iomega 1RedingtonValueBelum ada peringkat

- Alat SMK 2018Dokumen16 halamanAlat SMK 2018Jae Tama Grand'sBelum ada peringkat

- IPLINFODokumen61 halamanIPLINFOabhinavs_95Belum ada peringkat

- Star Memory SystemDokumen10 halamanStar Memory SystemRochelle LewisBelum ada peringkat

- BK Precision CatalogDokumen118 halamanBK Precision CatalogTony WilliamsBelum ada peringkat

- Stahl HMI Operating InstructionsDokumen60 halamanStahl HMI Operating InstructionsJaysonBelum ada peringkat

- SA7454 Datasheet - Eeworld.com - CNDokumen6 halamanSA7454 Datasheet - Eeworld.com - CNManuel PradoBelum ada peringkat

- Mikroc ManualDokumen391 halamanMikroc ManualtoredaBelum ada peringkat