JK Flip Flop and The Master-Slave JK Flip Flop Tutorial

Diunggah oleh

Sai SaiJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

JK Flip Flop and The Master-Slave JK Flip Flop Tutorial

Diunggah oleh

Sai SaiHak Cipta:

Format Tersedia

3/22/2014

JK Flip Flop and the Master-Slave JK Flip Flop Tutorial

Home (http://www.electronics-tutorials.ws) Sequential Logic (http://www.electronicstutorials.ws/category/sequential) The JK Flip Flop

Search

PDF Tutorial Flip Flop JK JK JK

The JK Flip Flop

The JK Flip Flop

From the previous tutorial we now know that the basic gated SR NAND flip flop suffers from two basic problems: number one, the S = 0 and R = 0 condition (S = R = 0) must always be avoided, and number two, if S or R change state while the enable input is high the correct latching action may not occur. Then to overcome these two fundamental design problems with the SR flip-flop design, the JK flip Flop was developed. This simple JK flip Flop is the most widely used of all the flip-flop designs and is considered to be a universal flip-flop circuit. The sequential operation of the JK flip flop is exactly the same as for the previous SR flip-flop with the same Set and Reset inputs. The difference this time is that the JK flip flop has no invalid or forbidden input states of the SR Latch even when S and R are both at logic 1 . The JK flip flop is basically a gated SR flip flop with the addition of a clock input circuitry that prevents the illegal or invalid output condition that can occur when both inputs S and R are equal to logic level 1 . Due to this additional clocked input, a JK flip-flop has four possible input combinations, logic 1 , logic 0 , no change and toggle. The symbol for a JK flip flop is similar to that of an SR Bistable Latch (http://www.electronicstutorials.ws/sequential/seq_1.html) as seen in the previous tutorial except for the addition of a clock input.

The Basic JK Flip-flop

http://www.electronics-tutorials.ws/sequential/seq_2.html

1/7

3/22/2014

JK Flip Flop and the Master-Slave JK Flip Flop Tutorial

Both the S and the R inputs of the previous SR bistable have now been replaced by two inputs called the J and K inputs, respectively after its inventor Jack Kilby. Then this equates to: J = S and K = R. The two 2-input AND gates of the gated SR bistable have now been replaced by two 3-input NAND gates with the third input of each gate connected to the outputs at Q and Q. This cross coupling of the SR flip-flop allows the previously invalid condition of S = 1 and R = 1 state to be used to produce a toggle action as the two inputs are now interlocked. If the circuit is now SET the J input is inhibited by the 0 status of Q through the lower NAND gate. If the circuit is RESET the K input is inhibited by the 0 status of Q through the upper NAND gate. As Q and Q are always different we can use them to control the input. When both inputs J and K are equal to logic 1 , the JK flip flop toggles as shown in the following truth table.

The Truth Table for the JK Function

Input J 0 same as for the SR Latch 0 0 0 1 1 toggle action 1 1 K 0 0 1 1 0 0 1 1 Output Q 0 0 1 0 0 1 0 1

Q

Description Memory no change Reset Q 0

0 1 0 1 1 0 1 0

Set Q 1

Toggle

Then the JK flip-flop is basically an SR flip flop with feedback which enables only one of its two input terminals, either SET or RESET to be active at any one time thereby eliminating the invalid condition seen previously in the SR flip flop circuit. Also when both the J and the K inputs are at logic level 1 at the same time, and the clock input is pulsed either HIGH, the circuit will toggle from its SET state to a RESET state, or visa-versa. This results in the JK flip flop acting more like a T-type toggle flip-flop when both terminals are HIGH.

http://www.electronics-tutorials.ws/sequential/seq_2.html

2/7

3/22/2014

JK Flip Flop and the Master-Slave JK Flip Flop Tutorial

Although this circuit is an improvement on the clocked SR flip-flop it still suffers from timing problems called race if the output Q changes state before the timing pulse of the clock input has time to go OFF. To avoid this the timing pulse period ( T ) must be kept as short as possible (high frequency). As this is sometimes not possible with modern TTL ICs the much improved Master-Slave JK Flip-flop was developed. The master-slave flip-flop eliminates all the timing problems by using two SR flip-flops connected together in a series configuration. One flip-flop acts as the Master circuit, which triggers on the leading edge of the clock pulse while the other acts as the Slave circuit, which triggers on the falling edge of the clock pulse. This results in the two sections, the master section and the slave section being enabled during opposite half-cycles of the clock signal. The 74LS73 is a Dual JK flip-flop IC, which contains two individual JK type bistables within a single chip enabling single or master-slave toggle flip-flops to be made. Other JK flip flop ICs include the 74LS107 Dual JK flip-flop with clear, the 74LS109 Dual positive-edge triggered JK flip flop and the 74LS112 Dual negative-edge triggered flip-flop with both preset and clear inputs.

Dual JK Flip-flop 74LS73

The Master-Slave JK Flip-flop

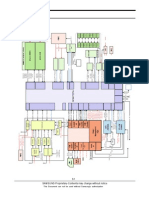

The Master-Slave Flip-Flop is basically two gated SR flip-flops connected together in a series configuration with the slave having an inverted clock pulse. The outputs from Q and Q from the Slave flip-flop are fed back to the inputs of the Master with the outputs of the Master flip flop being connected to the two inputs of the Slave flip flop. This feedback configuration from the slaves output to the masters input gives the characteristic toggle of the JK flip flop as shown below.

The Master-Slave JK Flip Flop

http://www.electronics-tutorials.ws/sequential/seq_2.html

3/7

3/22/2014

JK Flip Flop and the Master-Slave JK Flip Flop Tutorial

The input signals J and K are connected to the gated master SR flip flop which locks the input condition while the clock (Clk) input is HIGH at logic level 1 . As the clock input of the slave flip flop is the inverse (complement) of the master clock input, the slave SR flip flop does not toggle. The outputs from the master flip flop are only seen by the gated slave flip flop when the clock input goes LOW to logic level 0 . When the clock is LOW, the outputs from the master flip flop are latched and any additional changes to its inputs are ignored. The gated slave flip flop now responds to the state of its inputs passed over by the master section. Then on the Low-to-High transition of the clock pulse the inputs of the master flip flop are fed through to the gated inputs of the slave flip flop and on the High-to-Low transition the same inputs are reflected on the output of the slave making this type of flip flop edge or pulse-triggered. Then, the circuit accepts input data when the clock signal is HIGH, and passes the data to the output on the fallingedge of the clock signal. In other words, the Master-Slave JK Flip flop is a Synchronous device as it only passes data with the timing of the clock signal. In the next tutorial about Sequential Logic Circuits, we will look at Multivibrators (http://www.electronicstutorials.ws/sequential/seq_3.html) that are used as waveform generators to produce the clock signals to switch sequential circuits.

Circuit

Electronics

IC Circuit

D Flip Flop

Sequential Logic Circuits (http://www.electronics-tutorials.ws/sequential/seq_1.html) | Multivibrators (http://www.electronics-tutorials.ws/sequential/seq_3.html)

Other Good Tutorials in this Category

Johnson Ring Counter (http://www.electronics-tutorials.ws/sequential/seq_6.html) Multivibrators (http://www.electronics-tutorials.ws/sequential/seq_3.html) Sequential Logic Circuits (http://www.electronics-tutorials.ws/sequential/seq_1.html) The D-type Flip Flop (http://www.electronics-tutorials.ws/sequential/seq_4.html) The JK Flip Flop (http://www.electronics-tutorials.ws/sequential/seq_2.html) The Shift Register (http://www.electronics-tutorials.ws/sequential/seq_5.html)

http://www.electronics-tutorials.ws/sequential/seq_2.html

4/7

3/22/2014

JK Flip Flop and the Master-Slave JK Flip Flop Tutorial

Tags:

Digital

Logic

(http://www.electronics-tutorials.ws/tag/digital-logic)

Sequential (http://www.electronics-tutorials.ws/tag/sequential-logic)

Leave a Reply

Your email address will not be published. Required fields are marked * Name *

Email *

Website

What's the Sum * three + Comment = 11

You may use these HTML (HyperText Markup Language) tags and attributes: < a h r e f = " " t i t l e = " " > < a b b r

t i t l e = " " >< a c r o n y mt i t l e = " " >< b >< b l o c k q u o t ec i t e = " " >< c i t e >< c o d e >< d e ld a t e t i m e = " " >< e m >< i >< q c i t e = " " >< s t r i k e >< s t r o n g >

Post Comment

79

http://www.electronics-tutorials.ws/sequential/seq_2.html

5/7

3/22/2014

JK Flip Flop and the Master-Slave JK Flip Flop Tutorial

( http://schematics.com/)

http://www.electronics-tutorials.ws/sequential/seq_2.html

6/7

3/22/2014

JK Flip Flop and the Master-Slave JK Flip Flop Tutorial

Amazon.co.uk Hozelock 2-in-1 Compact Enclosed Hose Reel with 25 m H... Hozelock Ltd New 34.53 Best 27.00 Vax W90-RU-P Rapide Ultra 2 Pre-Treatment Upright Carp... Vax New 129.99 Best 94.99 Shaver Adaptor BML New 1.15 Best 0.01

Cable Ties 4.8 x 300mm Pack of 100 Sealey Tools New 2.00 Best 0.01

Privacy Information

Find us on Facebook

Electronics Tutorials Fan Page

Like

598 people like Electronics Tutorials Fan Page.

Facebook social plugin

Basic Electronics Tutorials Site by Wayne Storr. Last updated 14th March 2014, Copyright 1999 2014, All Rights Reserved - Basic Electronics Tutorials. | RSS (http://feeds.feedburner.com/electronics-tutorials) | Privacy Policy (http://www.electronicstutorials.ws/privacypolicy) | Terms of Use (http://www.electronics-tutorials.ws/terms) | Site Map (http://www.electronics-tutorials.ws/sitemap) | Contact Us (http://www.electronics-tutorials.ws/contact) | Find us on Google+ (https://plus.google.com/+Electronics-tutorialsWs/posts) | Electronics Tutorials (http://www.electronics-tutorials.ws/) |

http://www.electronics-tutorials.ws/sequential/seq_2.html

7/7

Anda mungkin juga menyukai

- 3eurec 405Dokumen4 halaman3eurec 405Sai SaiBelum ada peringkat

- AEC AssignmentDokumen9 halamanAEC AssignmentSai SaiBelum ada peringkat

- Memory and Programmable LogicDokumen94 halamanMemory and Programmable LogicSai SaiBelum ada peringkat

- ControlsDokumen3 halamanControlsstormskyeBelum ada peringkat

- Digital Smell Technology Seminar ReportDokumen23 halamanDigital Smell Technology Seminar ReportAnanth Kumar0% (1)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Tiernan TDR4022 Data SheetDokumen2 halamanTiernan TDR4022 Data SheetGromit32Belum ada peringkat

- Epa242 PDFDokumen4 halamanEpa242 PDFpapadafiBelum ada peringkat

- Philips HTS3455Dokumen53 halamanPhilips HTS3455KAZIMALI2575% (4)

- Listen To You Gut Chapter 1Dokumen44 halamanListen To You Gut Chapter 1stamos9900% (1)

- DRamDokumen16 halamanDRamshastryBelum ada peringkat

- P-Channel MOSFET Technical DocumentDokumen7 halamanP-Channel MOSFET Technical DocumentXavi SegarraBelum ada peringkat

- Using an oscilloscope to analyze audio signalsDokumen25 halamanUsing an oscilloscope to analyze audio signalsFnd MuorBelum ada peringkat

- Internship Report in PTCL, WLL DepartmentDokumen34 halamanInternship Report in PTCL, WLL Departmentansari_86Belum ada peringkat

- PW 1984 01Dokumen100 halamanPW 1984 01Peter Mulder67% (3)

- COS/MOS Series in 1968, As A Lower Power and More Versatile Alternative To TheDokumen7 halamanCOS/MOS Series in 1968, As A Lower Power and More Versatile Alternative To Theprateek154uBelum ada peringkat

- 74F175, 74F175A Quad D Flip-Flop: Integrated CircuitsDokumen11 halaman74F175, 74F175A Quad D Flip-Flop: Integrated CircuitsroozbehxoxBelum ada peringkat

- Microwave CommunicationsDokumen79 halamanMicrowave CommunicationsKatyrynne GarciaBelum ada peringkat

- William's Strangest StoryDokumen8 halamanWilliam's Strangest StoryPei Hwee TanBelum ada peringkat

- Alineadores de Banda KiepeDokumen4 halamanAlineadores de Banda KiepeJuan Manuel TorresBelum ada peringkat

- ComplianceDokumen10 halamanComplianceCaptainBelum ada peringkat

- Decca NavigatorDokumen5 halamanDecca NavigatorJayson DiazenBelum ada peringkat

- 8000 Falling Weight Deflectometer (FWD) - A4 - WebDokumen2 halaman8000 Falling Weight Deflectometer (FWD) - A4 - WebRijal Psalmen HasibuanBelum ada peringkat

- Update Asset Details for COL_Fairmount-IBS_GC SiteDokumen13 halamanUpdate Asset Details for COL_Fairmount-IBS_GC SiterageendrathasBelum ada peringkat

- IcaroDokumen110 halamanIcaroBibiBelum ada peringkat

- IEEE Paper On Mobile and Cellular Technologies Based On The Title Gi FiDokumen9 halamanIEEE Paper On Mobile and Cellular Technologies Based On The Title Gi FiSuganya Periasamy100% (2)

- Building Blocks of An OpampDokumen11 halamanBuilding Blocks of An OpampChathunikaBelum ada peringkat

- VREG and LCD ChecksDokumen53 halamanVREG and LCD ChecksYe Yint AungBelum ada peringkat

- V T-7 3 7 S P: Operation ManualDokumen58 halamanV T-7 3 7 S P: Operation ManualJuan Carlos FiallosBelum ada peringkat

- Perbedaan SFH Dan BBDokumen2 halamanPerbedaan SFH Dan BBpsquallBelum ada peringkat

- 15175fs Marking SMD CodeDokumen8 halaman15175fs Marking SMD Code2dmsBelum ada peringkat

- NFC TechnologyDokumen10 halamanNFC TechnologySachin ShedoleBelum ada peringkat

- E5566 - MX6021 Sell Sheet R01Dokumen2 halamanE5566 - MX6021 Sell Sheet R01Demo MxBelum ada peringkat

- Pre Test: Multiple Choices: Circle The Letter That Corresponds The Correct AnswerDokumen2 halamanPre Test: Multiple Choices: Circle The Letter That Corresponds The Correct AnswerBianca MonteverdeBelum ada peringkat

- Datasheet PDFDokumen16 halamanDatasheet PDFJoseGyEjBelum ada peringkat