Asteroids Deluxe (Signature Analysis Guide) (English)

Diunggah oleh

Darryl RheaDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Asteroids Deluxe (Signature Analysis Guide) (English)

Diunggah oleh

Darryl RheaHak Cipta:

Format Tersedia

ASTEROIDS DELUXE SIGNATURE ANALYSIS GUIDE

Introduction

This guide is intended as an aid to troubleshooting the Asteroids Deluxe video game PCB. The Signature Analyzer used to produce this guide was an HP5004a. If it is found that the signatures hold up for other makes/models of Signature Analyzers then please let me know and I can add some kind of compatibility list to the document. Suggestions of any kind to improve this document are always welcome. To get the most out of the guide youll need Signature Analyzer (HP5004a) Schematics for Asteroids Deluxe 6502 NOP card (See the separate document 6502NOP for instructions on how to build your own NOP card) IC Clips Some jumper wires (3 or 4 should be sufficient) The scope of the guide is limited in that it will not enable you to fault find the entire PCB. It should, however, be good for the following sections of the PCB: Address Bus Buffers, Address Decoding Circuitry, Clock Circuit, Program ROMs and Data Buffer, Vector Generator Address Selector, Vector Generator RAM Select, Vector Generator ROMs and the Vector Generator Data Buffer. The Clock Circuit test is very limited. The reason being is that I much prefer to check the clock chain with a scope. If you want to figure out the signatures for the Clock Circuit then pass on the information and Ill include it in the document. If you want a detailed description of these sections (and more) please refer to the Asteroids Deluxe schematic / drawing package.

Using The Guide

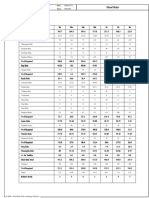

For those of you who have used Atari Signature Analysis guides before then this should look familiar and theres probably no need to read through this section. For the rest of you, heres a quick run down. Every section should start with the settings for the Analyzer, something like this A. SA Settings for xxxxx Test Probe Start Stop Clock Trigger +ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

The probe column refers to either the Start, Stop or Clock probes from the Signature Analyzer. The trigger column sets up the Start/Stop/Clock buttons on the front of the Analyzer. I have used ve to indicate the negative going edge of the pulse (or the falling edge). I have used +ve to indicate the positive going edge of the pulse (or the rising edge). The IC Pin column refers to the point where the appropriate probe should be attached. The Test Pt. column refers to an equivalent Test Point on the boards where the probe may be attached. For example, in the example above the Start probe should be connected to pin 25 of IC C2. The Start button on the front of the Analyzer should be in the fully out position to indicate a positive going edge. Similarly, the Stop probe should be connected to the same IC/Pin as the Start probe but the Stop button on the Analyzer should be pressed in to indicate a negative going edge. The section immediately following the set up procedure contains the signatures for that part of the test. The same structure for the Set Up was employed as explained below. B. Signatures Logic Probe On IC/Pin C1-20 C1-9 C1-12 Signal Name +5V AB0 AB1 Signature

0003 UUUU FFFF

Here, with the Analyzer probe on pin 20 of IC C1 you should get a reading of 0003. On pin 9 of IC C1 you should get a reading of UUUU. And so on. A signature denoted by an (*) indicates that signature may be unstable. Try taking the signature with a 1Kohm resistor connected between the probe tip and +5V.

Down To Business

One of the things I like about this testing method is that you dont need to have the PCB in the cabinet. If you prefer to work in the back of the cabinet then thats fine. If you have a bench/test area with a +5V PSU (as Im sure most of you have), then you can sit comfortably at the bench. Simply connect Ground (pins 1 and 22 on the edge connector) and +5V (pins 2 and 21 on the edge connector) to the PCB and youre ready to start. Just set up the Analyzer as indicated and start probing for those signatures. Always remember to have the Watchdog disabled as this will lead to permanently unstable signatures.

What To Do When You Find An Incorrect Signature

If you find a signature that doesnt match the guide, check your set up first. If your set up is OK then youll need to trace the fault. Rather than having a long winded ramble from me it would be better to look at the following link on Al Kossows page. If you havent already had a look at his site then Id definitely recommend having a look as its a bit of a gold mine. http://www.spies.com/arcade/TE/SigAnalNotes.pdf After youve had a look through the document then you should know enough to start tracing the fault. It should also give you a bit more information on Signature Analysis in general.

Some Common Faults

The two most common faults Ive come across are bad sockets and shorted traces. During the Signature Analysis the bad socket problem is highlighted by the fact that the signatures are unstable. You may get some stable and some not. When you get unstable signatures whilst doing the ROM tests it does not necessarily indicate a bad ROM. Reseating the ROM or replacing the socket is usually a good place to start. The problem of shorted traces is usually down to something being dragged across the board. Sometimes they can be quite hard to see but Signature Analysis shows it up quite good.

Disclaimer

If you toast yourself, your house, your dog, your family or more importantly your video game, then its not my fault. You use the information contained in this guide at your own risk. Good luck.

Document Author

Peter Fyfe

Email (Home) peter@bombjack.freeserve.co.uk Email (Work) peter.fyfe@honeywell.com 6th February 2000

** Tie the Watchdog Disable test point to ground **

2. Address Decoding

A. SA Settings for Address Decoder Test

1. Address Lines

A. SA Settings for Address Buffer Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

Probe Start Stop Clock

Trigger -ve -ve -ve

IC Pin C2-25 C2-25 C2-39

Test Pt.

B. Signatures 2 Logic Probe On IC/Pin Signal Name SINP0 SINP1 OPTS PMEM VMEM ZPAGE PKYDCD Signature

B. Signatures Logic Probe On IC/Pin C1-20 C1-9 C1-12 C1-7 C1-14 C1-5 C1-16 C1-3 C1-18 B1-18 B1-14 B1-9 B1-5 B1-7 C2-23 C2-24 C2-25 Signal Name +5V AB0 AB1 AB2 AB3 AB4 AB5 AB6 AB7 AB8 AB9 AB10 AB11 AB12 A13 A14 A15 Signature

0003 UUUU FFFF 8484 P763 1U5P 0356 U759 6F9A 7791 6321 37C5 6U28 4FCA 4868 9UP1 0001

E3-4 E3-5 E3-6 E3-9 E3-10 E3-11 E3-12 D5-10 C5-8 L2-4 L2-5 L2-6 L2-7

AF76 6913 13HP 3282 AH63 7APA P508 3H01 3H02 P933 UH4P A04H 86C1

PROM0 PROM1 PROM2 PROM3

C. SA Settings for Address Decoder Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C3-14 Test Pt.

6MHz

** Tie R/W test point to ground ** D. Signatures Logic Probe On IC/Pin D5-14 Signal Name +5V Signature

00UP

D5-4 E4-8 L5-1 L5-2 L5-3 L5-4 L5-5 L5-6 L5-7 L5-9 B8-13 B8-12 B8-11

0066 (*) 7U7C DMAGO 383U EAADDRL P759 WDCLR 90P8 EXPLODE UA0P A43F EACONTROL U5FA AUDIO 81F6 NOISERESET 1A35 00UP A43F DMARESET A43F

4..Clock Circuit

A. SA Settings for Clock Circuit Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

B. Signatures Logic Probe On IC/Pin B3-6 B3-8 B3-10 Signal Name Signature

** Remove jumper from R/W test point **

3KHz 12KHz

763H 8A4U 9720

3..Watchdog Circuit

A. SA Settings for Watchdog Circuit Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

5 ROM And Data Lines

A. SA Settings for ROM0 Test (D1) Probe Trigger -ve +ve -ve IC Pin L2-4 L2-4 C2-39 Test Pt.

** Tie L5-12 to ground ** B. Signatures Logic Probe On IC/Pin C5-14 C5-6 D4-6 D4-8 Signal Name +5V Signature

Start Stop Clock

B. Signatures Logic Probe On IC/Pin D1-24 D1-9 D1-10 D1-11 D1-13 D1-14 D1-15 D1-16 D1-17 Signal Name +5V DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature

0003 752C 0398 0000

** Remove jumper from L5-12 **

826P 4869 995C F0AH UF20 A17H 232H 4590 99P1

C. SA Settings for ROM1 Test (E/F1) Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-5 L2-5 C2-39 Test Pt.

G. SA Settings for ROM3 Test (J1) Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-7 L2-7 C2-39 Test Pt.

D. Signatures Logic Probe On IC/Pin E/F1-9 E/F1-10 E/F1-11 E/F1-13 E/F1-14 E/F1-15 E/F1-16 E/F1-17 Signal Name DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature

H. Signatures Logic Probe On IC/Pin J1-9 J1-10 J1-11 J1-13 J1-14 J1-15 J1-16 J1-17 Signal Name DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature

UOF3 0UCU 0CA5 A391 7F79 U77P H494 052H

373U U96F 76U1 91PP 9P50 A126 10A0 F002

E. SA Settings for ROM2 Test (F/H1)

6. Data Buffer

Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-6 L2-6 C2-39 Test Pt. A. SA Settings for data buffer test. 2 Probe Start Stop Clock Signal Name DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature B. Signatures P65C 6FH0 7C88 PC19 94HP CP77 4AF2 7P08 Logic Probe On IC/Pin E2-18 (19) E2-17 (18) E2-16 (17) E2-15 (16) E2-14 (15) E2-13 (14) E2-12 (13) E2-11 (12) Signal Name D0 D1 D2 D3 D4 D5 D6 D7 Signature Trigger -ve +ve -ve IC Pin L2-7 L2-7 C2-39 Test Pt.

F. Signatures Logic Probe On IC/Pin F/H1-9 F/H1-10 F/H1-11 F/H1-13 F/H1-14 F/H1-15 F/H1-16 F/H1-17

373U U96F 76U1 91PP 9P50 A126 10A0 F002

** The numbers in brackets are the pin assignments when an AM8304B is used as opposed to a 74LS245 **

8. Vector Generator RAM

A. SA Settings for VG RAM Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

7. Vector Generator Address Selector

A. SA Settings for VG Address Sel Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

** Tie K2-1 to ground ** 2 B Signatures Logic Probe On IC/Pin M4-3 M4-6 L4-4 Signal Name Signature

** Tie K2-1 to ground ** B Signatures Logic Probe On IC/Pin K2-1 K2-4 K2-12 L2-10 L2-11 L2-12 F2-9 F2-7 F2-4 F2-12 H2-12 H2-4 H2-7 H2-9 J2-9 J2-12 J2-4 Signal Name +5V AM11 AM12 VROM2 VROM1 VRAM AM0 AM1 AM2 AM3 AM4 AM5 AM6 AM7 AM8 AM9 AM10 Signature

98H1 32U8 37C6

0003 6U28 4FCA F501 P693 AA2A UUUU FFFF 8484 P763 1U5P 0356 U759 6F9A 7791 6321 37C5

9. Vector Generator ROM

A. SA Settings for VG ROM1 Test (R2) Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-11 L2-11 C2-39 Test Pt.

** Tie K2-1 to ground ** B Signatures Logic Probe On IC/Pin R2-24 R2-9 R2-10 R2-11 R2-13 R2-14 R2-15

4

Signal Name +5V DDMA0 DDMA1 DDMA2 DDMA3 DDMA4 DDMA5

Signature

826P A13F 37H3 9F59 69HU 9277 5530

R2-16 R2-17

DDMA6 DDMA7

725P 2604

10. Vector Generator Data Buffer

A. SA Settings for VG Data Buffer test

C. SA Settings for ROM2 Test (N/P2) Probe Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-10 L2-10 C2-39 Test Pt. Start Stop Clock -ve +ve -ve L2-10 L2-10 C2-39 Trigger IC Pin Test Pt.

B Signatures ** Tie K2-1 to ground ** D Signatures Logic Probe On IC/Pin N/P2-9 N/P2-10 N/P2-11 N/P2-13 N/P2-14 N/P2-15 N/P2-16 N/P2-17 Signal Name Signature Logic Probe On IC/Pin P1-18 (19) P1-17 (18) P1-16 (17) P1-15 (16) P1-14 (15) P1-13 (14) P1-12 (13) P1-11 (12) Signal Name DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature

DDMA0 6334 DDMA1 2AH5 DDMA2 3431 DDMA3 F67C DDMA4 5H7C DDMA5 7FFH DDMA6 88U2 DDMA7 A433

6334 2AH5 3431 F67C 5H7C 7FFH 88U2 A433

* The numbers in brackets are the pin assignments when an AM8304B is used as opposed to a 74LS245 *

Anda mungkin juga menyukai

- SkyGazer - Chapter 14Dokumen11 halamanSkyGazer - Chapter 14MediaPirate9787100% (1)

- The Fifth HouseDokumen10 halamanThe Fifth HouseYo DraBelum ada peringkat

- EMI Recording Console Handbook+Mk2Dokumen71 halamanEMI Recording Console Handbook+Mk2Zack Dagoba100% (2)

- 101 ObservationsoftheEffectsoftheMoonsNodesonthePersonalityDokumen4 halaman101 ObservationsoftheEffectsoftheMoonsNodesonthePersonalitySachin MathurBelum ada peringkat

- Lucky Stars NumberDokumen215 halamanLucky Stars NumbersadrotgasBelum ada peringkat

- Karma and AstrologyDokumen3 halamanKarma and AstrologyproddaturBelum ada peringkat

- SEGINUSDokumen7 halamanSEGINUSNina Elezovic SimunovicBelum ada peringkat

- Nanotechnology and VaccinesDokumen11 halamanNanotechnology and Vaccinespranchish100% (1)

- Retrograde Planets: What They Show About Past Lives by Judy CollinsDokumen3 halamanRetrograde Planets: What They Show About Past Lives by Judy CollinsRao LakkojuBelum ada peringkat

- Mars Activation of Eclipse Points NodesDokumen32 halamanMars Activation of Eclipse Points NodesmichaBelum ada peringkat

- Saturn UranusDokumen11 halamanSaturn Uranusdositheus11100% (1)

- Saturn 11thDokumen7 halamanSaturn 11thRacheBelum ada peringkat

- Kaal Sarp YogDokumen2 halamanKaal Sarp YogsainergyBelum ada peringkat

- EclipsesDokumen6 halamanEclipsesAycan ÖzenbaşBelum ada peringkat

- Harness House 12Dokumen3 halamanHarness House 12Dayakar Devaru100% (2)

- Beginning CosmodynesDokumen2 halamanBeginning CosmodynesDilip KiningeBelum ada peringkat

- AstrologyDokumen331 halamanAstrologySuraj GuptaBelum ada peringkat

- Conversing With Heaven Carter Memorial Lecture 2010Dokumen10 halamanConversing With Heaven Carter Memorial Lecture 2010shadowgraphBelum ada peringkat

- Astrological Ages As An Accurate and Effective Model of HistoryDokumen15 halamanAstrological Ages As An Accurate and Effective Model of HistoryMerlin PitBelum ada peringkat

- Mystic Powers of KalSarp YogaDokumen2 halamanMystic Powers of KalSarp Yogaगणेश पराजुलीBelum ada peringkat

- The Jupiter-Saturn ConjunctionDokumen7 halamanThe Jupiter-Saturn Conjunctionmurx2100% (1)

- The Messageofthe StarsDokumen703 halamanThe Messageofthe StarsAbhi AbhijithBelum ada peringkat

- The Harmonic Concordance 1Dokumen56 halamanThe Harmonic Concordance 1lionroadBelum ada peringkat

- Cause For Delay in MarriageDokumen7 halamanCause For Delay in Marriagedeepak joshiBelum ada peringkat

- The Cosmic T Square 240510Dokumen8 halamanThe Cosmic T Square 240510Anthony Writer0% (1)

- Astrology Lesson 1Dokumen4 halamanAstrology Lesson 1Valentin BadeaBelum ada peringkat

- Pitru PakshaDokumen3 halamanPitru PakshanieotyagiBelum ada peringkat

- 7th Degree of Aquarius-Leo Axis PDFDokumen9 halaman7th Degree of Aquarius-Leo Axis PDFahaBelum ada peringkat

- The Science of Astrology.Dokumen9 halamanThe Science of Astrology.Dinesh Vallecha0% (1)

- Astrological Articles - 49Dokumen27 halamanAstrological Articles - 49Mehul JaniBelum ada peringkat

- Salvador Dali: Strong Medium WeakDokumen5 halamanSalvador Dali: Strong Medium WeaknikirajendranBelum ada peringkat

- Astrology, Guns, America and The Future - Jessica Adams Psychic AstrologerDokumen1 halamanAstrology, Guns, America and The Future - Jessica Adams Psychic AstrologerJiaqing ZhangBelum ada peringkat

- Year of The Water Dragon Yearly Forecast-2011-12!31!14!29!39Dokumen3 halamanYear of The Water Dragon Yearly Forecast-2011-12!31!14!29!39nikkig1982Belum ada peringkat

- Angelina Jolie Shad BalaDokumen1 halamanAngelina Jolie Shad BalaGanesan S100% (1)

- Wikipedia - List of Greek Mythological FiguresDokumen29 halamanWikipedia - List of Greek Mythological FiguresXangotBelum ada peringkat

- Jupiter UranusDokumen2 halamanJupiter UranusPhalgun BalaajiBelum ada peringkat

- Astrological Keyword System of Analyzing Character and Dest 1Dokumen10 halamanAstrological Keyword System of Analyzing Character and Dest 1Maha DeviBelum ada peringkat

- Magical Aspects - Pat GeislerDokumen2 halamanMagical Aspects - Pat GeislerJust_BojanaBelum ada peringkat

- The Fallen Madonna Story of Zosma: by Miloš TomićDokumen4 halamanThe Fallen Madonna Story of Zosma: by Miloš TomićMilos TomicBelum ada peringkat

- Astrological TermsDokumen11 halamanAstrological Termssonali_krishBelum ada peringkat

- Narada Purana 2 (AITM)Dokumen432 halamanNarada Purana 2 (AITM)SubalBelum ada peringkat

- Solar Fire Interpretations Report Transits To Natal InterpretationsDokumen14 halamanSolar Fire Interpretations Report Transits To Natal Interpretationswww_sickmandanBelum ada peringkat

- Elemental Imbalances: Fire ImbalanceDokumen3 halamanElemental Imbalances: Fire ImbalanceeyeoftaurusBelum ada peringkat

- The Weather Guide BookDokumen153 halamanThe Weather Guide BookPlamena KolevaBelum ada peringkat

- Agender Astrology - Deon MitchellDokumen39 halamanAgender Astrology - Deon MitchellGigiBelum ada peringkat

- Carter Principles2Dokumen6 halamanCarter Principles2ddum292Belum ada peringkat

- AccidentsDokumen6 halamanAccidentsHoracio TackanooBelum ada peringkat

- Aninomo - An Introduction To Mundane AstrologyDokumen9 halamanAninomo - An Introduction To Mundane AstrologyjcluBelum ada peringkat

- Excerpted & Revised Section On: Leo,: Original Obsolete Reference: Astrology Class A-4, Session 3Dokumen24 halamanExcerpted & Revised Section On: Leo,: Original Obsolete Reference: Astrology Class A-4, Session 3OmSilence2651Belum ada peringkat

- Balbillus and The Method of AphesisDokumen16 halamanBalbillus and The Method of AphesisAna Paula Rodrigues100% (1)

- Classical Planets: Block Book German Renaissance Hausbuch Hans TalhofferDokumen19 halamanClassical Planets: Block Book German Renaissance Hausbuch Hans TalhoffersharathVEM0% (1)

- Planetary Glyph MeaningsDokumen2 halamanPlanetary Glyph MeaningseyeoftaurusBelum ada peringkat

- Physical Studies of Minor Planets Asteroids. 1971. 595 Kessler & ForwardDokumen720 halamanPhysical Studies of Minor Planets Asteroids. 1971. 595 Kessler & ForwardjleydencoBelum ada peringkat

- Venus-Neptune-Inharmonious AspectsDokumen2 halamanVenus-Neptune-Inharmonious AspectsPhalgun Balaaji100% (1)

- AstroDokumen5 halamanAstroMicaComBelum ada peringkat

- 0 - TablesDokumen1 halaman0 - TablesMia BukovskyBelum ada peringkat

- An Astrological Judgement Touching Theft Retyped and Extended by Anthony GriffinDokumen57 halamanAn Astrological Judgement Touching Theft Retyped and Extended by Anthony GriffinPaulo Alexandre SilvaBelum ada peringkat

- As Teroid S: BymaryestherandrewsDokumen7 halamanAs Teroid S: BymaryestherandrewsturtlespiritflutesBelum ada peringkat

- Astrology For The Weak . . . The World's First and Only Multiple Choice HoroscopesDari EverandAstrology For The Weak . . . The World's First and Only Multiple Choice HoroscopesBelum ada peringkat

- Science Newsletter LatestDokumen2 halamanScience Newsletter LatestDarryl RheaBelum ada peringkat

- Joint Release U.S. Department of Housing and Urban DevelopmentDokumen6 halamanJoint Release U.S. Department of Housing and Urban DevelopmentDarryl RheaBelum ada peringkat

- Pa 2014seasonchangesDokumen5 halamanPa 2014seasonchangesDarryl RheaBelum ada peringkat

- The End of Amnesty in Uganda: Implications For LRA DefectionsDokumen8 halamanThe End of Amnesty in Uganda: Implications For LRA DefectionsDarryl RheaBelum ada peringkat

- S O S Europe Report Web 02Dokumen24 halamanS O S Europe Report Web 02Darryl RheaBelum ada peringkat

- Fact Sheet: A O C - U SDokumen2 halamanFact Sheet: A O C - U SDarryl RheaBelum ada peringkat

- The Week at Fuller Village March 24 - 30Dokumen8 halamanThe Week at Fuller Village March 24 - 30Darryl RheaBelum ada peringkat

- United States Marine MRCP 3-1a - 23 Feb 1999 - Part01Dokumen124 halamanUnited States Marine MRCP 3-1a - 23 Feb 1999 - Part01Darryl Rhea100% (1)

- Public NoticesDokumen1 halamanPublic NoticesDarryl RheaBelum ada peringkat

- Think HackerDokumen10 halamanThink HackerDarryl RheaBelum ada peringkat

- The Bomb For Beginners: Michael RühleDokumen4 halamanThe Bomb For Beginners: Michael RühleDarryl RheaBelum ada peringkat

- United Sataes Army FM 21-11-27 October 1988 - Part03Dokumen44 halamanUnited Sataes Army FM 21-11-27 October 1988 - Part03Darryl RheaBelum ada peringkat

- United Sataes Army FM 21-11-27 October 1988 - Part02Dokumen42 halamanUnited Sataes Army FM 21-11-27 October 1988 - Part02Darryl RheaBelum ada peringkat

- Omron PLCDokumen275 halamanOmron PLCFrank FicheraBelum ada peringkat

- LogcatDokumen197 halamanLogcatAdheShenzaBelum ada peringkat

- M241 HARD GuideDokumen250 halamanM241 HARD Guideoprea vasileBelum ada peringkat

- 2.1.1 Computer Organization AutosavedDokumen15 halaman2.1.1 Computer Organization AutosavedSnigdha KodipyakaBelum ada peringkat

- Specular Tempus: User ManualDokumen19 halamanSpecular Tempus: User ManualMarc RöntschBelum ada peringkat

- Digital Systems 002Dokumen10 halamanDigital Systems 002David B MwathyBelum ada peringkat

- Smart Car Kit For Arduino User ManualDokumen82 halamanSmart Car Kit For Arduino User ManualSWBelum ada peringkat

- TLC 5615Dokumen25 halamanTLC 5615Muhammad Ahsan AkramBelum ada peringkat

- Computer Systems Unit 2 - Fill The BlanksDokumen7 halamanComputer Systems Unit 2 - Fill The BlanksDavidoffBelum ada peringkat

- 1 Intro To TIA PortalDokumen87 halaman1 Intro To TIA PortalRaff100% (3)

- Hardware TroubleshootingDokumen13 halamanHardware TroubleshootingAamirPathanBelum ada peringkat

- GLOFADokumen60 halamanGLOFArobertoBelum ada peringkat

- CV ExampleDokumen1 halamanCV ExampleIgor SavchukBelum ada peringkat

- Trooper Max: Combination Antenna - 5G Cellular, Wi-Fi, GNSS With LMR OptionDokumen5 halamanTrooper Max: Combination Antenna - 5G Cellular, Wi-Fi, GNSS With LMR OptionAnonymous TMW33SkgBelum ada peringkat

- BỘ ĐIỀU CHỈNH ĐIỆN ÁP LOCONTDokumen4 halamanBỘ ĐIỀU CHỈNH ĐIỆN ÁP LOCONTNguyễn Hào QuangBelum ada peringkat

- QueueDokumen26 halamanQueuevishnu neupane100% (1)

- LogcatDokumen4.798 halamanLogcatabdifatahboykaBelum ada peringkat

- TK 8160H (B51 8708 00)Dokumen52 halamanTK 8160H (B51 8708 00)bankienBelum ada peringkat

- Clock SynchronizationDokumen6 halamanClock Synchronizationudit_mca_blyBelum ada peringkat

- Manual pm5drhDokumen5 halamanManual pm5drhFabiano SilvaBelum ada peringkat

- Transistor Operation 1 PDFDokumen24 halamanTransistor Operation 1 PDFKavooBelum ada peringkat

- Exam Seating Arrangement ProjectDokumen18 halamanExam Seating Arrangement ProjectPragya Tripathi40% (5)

- Digital Electronics Full Lab ManualDokumen51 halamanDigital Electronics Full Lab ManualSayak MitraBelum ada peringkat

- x86 StderrDokumen1 halamanx86 StderrXyza Glyze OrtezaBelum ada peringkat

- CS304 IMP Short NotesDokumen39 halamanCS304 IMP Short Notesbc210403173 AHMAD ZIAMBelum ada peringkat

- Appinfo LogDokumen44 halamanAppinfo LogRomo Domínguez Luis ManuelBelum ada peringkat

- Lenovo 3000 H Series ManualDokumen29 halamanLenovo 3000 H Series ManualSofia Gomez LopezBelum ada peringkat

- Future Trends in Fiber Optics CommunicationDokumen6 halamanFuture Trends in Fiber Optics CommunicationKoustav MondalBelum ada peringkat

- Computer Fundamentals and Logic Circuits Part 1Dokumen13 halamanComputer Fundamentals and Logic Circuits Part 1Joshua RefeBelum ada peringkat