Relatorio Final Digital 2

Diunggah oleh

André Carvalho CamargoHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Relatorio Final Digital 2

Diunggah oleh

André Carvalho CamargoHak Cipta:

Format Tersedia

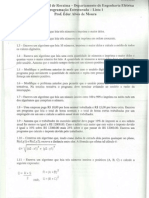

UNIVERSIDADE FEDERAL DE RORAIMA DEPARTAMENTO DE ENG.

ELTRICA ELETRNICA DIGITAL

RELATRIO DE AULA PRTICA

BOA VISTA- RORAIMA 27/06/2013

AULA PRTICA 01

DISCIPLINA: ELETRNICA DIGITAL PROF: JEOVANE SOUSA

ALUNOS: ANDR CARVALHO CAMARGO HIAGO SENA MARCUS CAMPOS

BOA VISTA-RORAIMA 27/06/2013

SUMRIO

1. INTRODUO: ................................................................................................................................................. 4 OBJETIVOS: ........................................................................................................................................................... 4 MATERIAIS UTILIZADOS: ....................................................................................................................................... 4 METODOLOGIA ..................................................................................................................................................... 4 2. DESENVOLVIMENTO .................................................................................................................................... 4 2.1. FUNDAMENTAO TERICA ........................................................................................................................ 4 2.2. PROCEDIMENTOS .......................................................................................................................................... 9 CONCLUSO ....................................................................................................................................................... 17 BIBLIOGRAFIA .................................................................................................................................................... 18

1. INTRODUO: OBJETIVOS: Projetar circuitos lgicos combinacionais a partir de descries comportamentais; Aplicar tcnicas de otimizao de circuitos digitais; Implementar e fazer verificao prtica do circuito implementado Construir e interpretar tabelas-verdade (TV) e implementar circuitos lgicos combinacionais Aplicar a teoria da lgebra de Boole. Utilizar softwares de simulao para auxiliar o projeto.

MATERIAIS UTILIZADOS: Software Simulador de Construccin de Circuitos Digitales con Escenarios Virtuales y Tutoriales Interactivos Software logisim verso 2.7.1.

METODOLOGIA Para estudar o comportamento de um determinado circuito lgico combinacional, o circuito ser implementado e o seu funcionamento ser registrado em uma tabela, denominada tabela verdade (TV) do circuito. O resultado ser utilizado para escrever a expresso lgica do circuito. As Tabelas da Verdade (TVs) devem ser preenchidas e verificadas para cada circuito proposto. 2. Esboce o circuito e escreva a respectiva TV antes da implementao. 3. Aps cada atividade prtica deve-se: a) Elaborar a TV relativa situao problema a ser resolvida! Quantas variveis de entrada? Quantas sadas esta tabela conter? Quantas linhas esta tabela contm? b) Escreva a funo relativa a cada sada! Simplifique a funo! Esboce os circuitos! Implemente os circuitos! Utilizando os programas de simulao, teste e analise o resultado confrontando com a TV. c) Elabore uma concluso sobre o aprendizado realizado! 4. Ao final do roteiro de experincia deve-se estabelecer uma concluso que demonstre a aprendizagem obtida com o experimento. 5. Em seguida h uma lista de exerccios e questionamentos que deve ser respondida como atividade de fixao ou ampliao de conhecimentos construdos. 2. DESENVOLVIMENTO 2.1. FUNDAMENTAO TERICA PORTAS LGICAS Portas lgicas ou circuitos lgicos, so dispositivos que operam um ou mais sinais lgicos de entrada para produzir uma e somente uma sada, dependente da funo implementada no circuito. So geralmente usadas em circuitos eletrnicos, por causa das situaes que os sinais deste tipo de circuito podem apresentar: presena de sinal, ou "1"; e ausncia de sinal, ou "0". As situaes "Mentirosas" e "Falsa" so estudadas na Lgica Matemtica ou Lgica de Boole; origem do nome destas portas. O comportamento das portas lgicas conhecido pela tabela verdade que apresenta os estados lgicos das entradas e das sadas. 1.

TABELA VERDADE Tabela verdade, tabela de verdade ou tabela veritativa um tipo de tabela matemtica usada em Lgica para determinar se uma frmula vlida ou se um sequente correto. As tabelas verdade derivam do trabalho de Gottlob Frege, Charles Peirce e outros da dcada de 1880, e tomaram a forma atual em 1922 atravs dos trabalhos de Emil Post e Ludwig Wittgenstein. A publicao do Tractatus Logico-Philosophicus, de Wittgenstein, utilizava as mesmas para classificar funes veritativas em uma srie. A vasta influncia de seu trabalho levou, ento, difuso do uso de tabelas verdade. FAMLIA LGICA TTL Famlias lgicas TTL: Os transstores bipolares permitem maior rapidez (maior frequncia), mas custa de maior consumo. TTL e CMOS constituram as alternativas principais durante muitos anos, mas a evoluo tecnolgica permitiu o aparecimento regular de outras solues de compromisso entre a velocidade e o consumo: Em TTL temos as variantes L (low power), S (Schottky), LS (low-power Schottky), etc. TTL significa Transistor-Transistor Logic (Lgica Transistor-Transistor). A tenso de alimentao se restringe a 5V contnuos, tendo, porm, uma faixa de tenso correspondente aos nveis lgicos 0 e 1. A figura a seguir mostra as faixas de tenso correspondentes aos nveis lgicos de entrada de um circuito integrado da famlia TTL.

VIH Tenso de entrada correspondente ao nvel lgico alto (1). VIL Tenso de entrada correspondente ao nvel lgico baixo (0).

Observa-se, na figura, que existe uma faixa de tenso entre 0,8V e 2V na qual o componente TTL no reconhece os nveis lgicos 0 e 1, devendo, portanto, ser evitados em projetos de circuitos digitais. A figura a seguir mostra as faixas de tenso correspondentes aos nveis lgicos de sada de um circuito integrado da famlia TTL.

V0H Tenso de sada correspondente ao nvel lgico alto (1). V0L Tenso de sada correspondente ao nvel lgico baixo (0).

FAMLIA LGICA CMOS Famlias lgicas CMOS: A tecnologia MOS normalmente a preferida para a implementao de circuitos mais complexos, quer por apresentar menores requisitos de rea por transstor, quer por apresentar menor consumo. TTL e CMOS constituram as alternativas principais durante muitos anos, mas a evoluo tecnolgica permitiu o aparecimento regular de outras solues de compromisso entre a velocidade e o consumo: Em CMOS, temos as variantes HC (high-speed CMOS) e HCT (compatvel pino a pino com os TTL). CMOS significa Complementary Metal Oxide Semiconductor (Semicondutor de xido-Metal Complementar), usa tanto FETs canal-N quanto canal-P no mesmo circuito, de forma a aproveitar as vantagens de ambas s famlias lgicas. As caractersticas principais desta famlia so o reduzido consumo de corrente (baixa potncia), alta imunidade a rudos e uma faixa de alimentao que se estende de 3V a 15V ou 18V dependendo do modelo. O processo de fabricao do CMOS mais simples que o do TTL, possuindo tambm uma densidade de integrao maior, porm so mais lentos do que os TTL, apesar da nova srie CMOS de alta velocidade competir em p de igualdade com as sries TTL 74 e 74LS. A famlia CMOS possui, tambm, uma determinada faixa de tenso para representar os nveis lgicos de entrada e de sada, porm estes valores dependem da tenso de alimentao e da temperatura ambiente. LGEBRA DE BOOLE (OU BOLEANA).

Desenvolvida pelo matemtico George Boole para estudo da lgica. Definida sobre um conjunto de dois elementos: (falso, verdadeiro) (0, 1) (baixo alto) Seus elementos, a princpio, no tem significado numrico. Postulados: se x uma varivel boleana ento: Se x = 0 => x = 1 Se x = 1 => x = 0 lgebra de Boole: operaes So definidas algumas operaes elementares na lgebra boleana: Operao No (NOT) operador barra 0=1 1=0 Operao E (AND) operador ponto 0.0=0 0.1=0 1.0=0 1.1=1 Operao Ou (OR) operador + 0+0=0 0+1=1 1+0=1 1+1=1

Operao Ou-Exclusivo (XOR) operador (+) 0 (+) 0 = 0 0 (+) 1 = 1 1 (+) 0 = 1 1 (+) 1 = 0 lgebra de Boole: funes Uma varivel boleana s pode assumir apenas um dos valores possveis (0 e 1) Uma ou mais variveis e operadores podem ser combinados formando uma funo lgica Z1(A) = f(A) = (expresso usando var. A) Z2(A,B) = f(A,B) = (expr. usando var. A e B) Resultados de uma funo lgica podem ser expressos numa tabela relacionando todas as combinaes possveis dos valores que suas variveis podem assumir e seus resultados correspondentes: a Tabela-Verdade. lgebra de Boole: Tabela Verdade

Tabela-Verdade relaciona os resultados (sada) de uma funo lgica para todas as combinaes possveis de suas variveis (entrada). Na Tabela-Verdade acima a funo lgica Z possui duas variveis A e B, sendo Z = f(A, B) =A+B. lgebra de Boole: precedncia Precedncia das Operaes (0) parntesis (1) Negao (2) E (3) Ou, Ou-exclusivo O uso de parntesis altera a precedncia normal dos operadores, como na lgebra comum. lgebra de Boole: propriedades Sendo A, B e C variveis boleanas Propriedade Comutativa A.B=B.A A+B=B+A A (+) B = B (+) A Propriedade Associativa (A.B).C=A.(B.C)=A.B.C (A+B)+C=A+(B+C)=A+B+C ( A (+) B ) (+) C = A (+) ( B (+) C ) = A (+) B (+) C

Propriedade Distributiva A . (B + C ) = A . B + A . C A + B . C = (A + B) . (A + C)

Propriedades (Leis) de Absoro A + A.B = A A + A.B = A + B (A + B).B = A.B Identidades importantes NOT 0=1 1=0 A=A AND A.1=A A.0=0 A.A=A A.A=0 OR A+1=1 A+0=A A+A=A A+A=1 lgebra de Boole: dualidade Existe um princpio especial na lgebra boleana denominado princpio da dualidade: Para uma equao boleana qualquer, se trocarmos as operaes E (.) e operaes OU (+) entre si assim como os valores 0s e 1s entre si, obteremos uma equao igualmente vlida. A+0=A A+1=1 A+A=A A+A=1 => => => => A.1=A A.0=0 A.A=A A.A=0

Teorema de De Morgan Primeira Lei A.B=A+B Segunda Lei A+B=A.B Estas leis permitem mudar de operador sem que seja alterada a funo. Ambas as leis podem ser estendidas para n variveis.

MAPA DE VEITCH-KARNAUGH O Mapa de Veitch-Karnaugh, ou simplesmente Mapa de Karnaugh um mtodo grfico para simplificar uma expresso lgica ou para converter uma tabela-verdade em seu circuito lgico correspondente. formado por uma tabela contendo clulas, onde n o nmero de variveis de entrada. O nmero de clulas do mapa de Karnaugh corresponde ao mesmo nmero de linhas da tabela verdade. Na prtica a utilizao do mapa de Karnaugh se limita a 5 variveis de entrada, sem uso de computador. A diferena entre uma tabela verdade e um mapa de Karnaugh reside na forma de representar as relaes entre as variveis de entrada e suas sadas correspondentes. Cada clula corresponde ao uma entrada diferente. As sadas so indicadas dentro das clulas correspondentes. A disposio das clulas entre si tal que facilite o agrupamento de clulas adjacentes. O agrupamento o enlace de clulas adjacentes, com sadas iguais, do qual se pode extrair uma expresso simplificada. A simplificao advm, basicamente, do Teorema de Adjacncia. Assim, no agrupamento de clulas adjacentes pode-se extrair uma expresso simplificada, j que a(s) varivel (eis) que muda(m) de valor (es) desaparece(m). A expresso de um agrupamento depende das sadas consideradas e das variveis de entrada, a qual obtida a partir das variveis que no mudam de valor. Sada = 1 (Soma de Produtos): Cada agrupamento um produto (AND) entre as variveis; A expresso resultante uma soma (OR) das expresses obtidas em cada agrupamento. Sada = 0 (Produto de Somas): Cada agrupamento uma soma (OR) entre as variveis; A expresso resultante um produto (AND) das expresses obtidas em cada agrupamento. Logo, a resoluo de um mapa de Karnaugh pode ser feita por sadas iguais a 1 ou 0.

2.2. PROCEDIMENTOS P1 INTERPRETE e RESOLVA A SITUAO APRESENTADA A SEGUIR Um jri de programa de calouros composto por quatro membros (A, B, C e D), cada jurado dispe de uma chave que acionada quando julgar que a apresentao do candidato foi aprovada. Se a metade dos jurados aprovarem o desempenho do(a) candidato(a) acende-se uma luz amarela indicando que ele(a) poder participar de um processo de repescagem, a critrio de uma comisso organizada pela direo do programa. Se a maioria do jri aprovar o desempenho do candidato (a) ele(a) permanece no programa, neste caso apaga-se a luz amarela e acende-se uma luz verde. Se a totalidade do jri aprovar o desempenho do candidato(a) ento acende-se mais uma segunda luz verde indicando que o candidato(a) receber um bnus oferecido pela organizao do programa.

Tabela Verdade:

Mapas de Karnaugh (note pela tabela da verdade que no necessitamos fazer o mapa de Karnaugh para a sada S3, pois seu comportamento e de uma porta logica AND de quatro entradas).

P2 INTERPRETE e RESOLVA A SITUAO APRESENTADA A SEGUIR 1) Utilize o software Simulador Digital para montar os circuitos digitais a seguir e levante suas respectivas tabelas verdade. Consulte os manuais dos componentes para uma montagem correta. b)

a)

c)

d)

2) Escolha um dos circuitos acima para fazer a minimizao utilizando mapa de Karnaugh.

3) Desenhe e monte o circuito da expresso lgica S= (A + B)(CD+CD )(AD+AD ), usando as propriedades, identidades e/ou teoremas vistos em sala de aula se necessrio.

P3 INTERPRETE e RESOLVA A SITUAO APRESENTADA A SEGUIR Para consolidar seus conhecimentos, projeto um circuito para atender o problema: A figura ao lado mostra o cruzamento de uma rodovia com uma via de acesso. Sensores detectores de veculos so colocados ao longo das pistas C e D (rodovia) e nas pistas A e B (via de acesso). As sadas desses sensores sero nvel BAIXO (0) quando nenhum veculo estiver presente e nvel ALTO (1) quando um veculo estiver presente. O sinal de trnsito no cruzamento controlado de acordo com a seguinte lgica:

a) O sinal da direo Leste-Oeste (L/O) ser verde quando as duas pistas C e D estiverem ocupadas. b) O sinal da direo L/O ser verde sempre que as pistas C ou D estiverem ocupadas, mas com as A e B desocupadas. c) O sinal da direo norte-sul (N/S) ser verde sempre que as duas pistas A e B estiverem ocupadas, mas as pistas C ou D estiverem desocupadas. d) O sinal da direo N/S ser verde quando as pistas A ou B estiverem ocupadas e enquanto ambas as pistas C e D estiverem vazias. e) O sinal da direo Leste-Oeste ser verde quando no houver veculo presente. f)Nos casos omissos, C e D tem preferncia sobre A e B. Usando as sadas dos sensores A, B, C e D como entradas, projete e simule um circuito lgico para controlar o semforo, utilizando os softwares apresentados. Devem existir duas sadas N/S e L/O, que sero nvel alto quando a luz correspondente for verde. Ligue a cada uma das sadas do circuito um LED para indicar o estado destas sadas. Tabela Verdade:

Notamos pela tabela da verdade que para implementar uma sada basta utilizar a sada da outra invertida.

Mapas de Karnaugh:

P4 INTERPRETE e RESOLVA A SITUAO APRESENTADA A SEGUIR A Figura ao lado mostra um diagrama para um circuito de alarme de automvel usado para detectar uma determinada condio indesejada. As trs chaves so usadas para indicar, respectivamente, o estado da porta do motorista, o estado da ignio e o estado dos faris. Projete um circuito lgico com essas trs chaves como entrada, de forma que o alarme seja ativado sempre que ocorrer uma das seguintes condies: a) Os faris esto acesos e a ignio est desligada b) A porta est aberta e a ignio est ligada

Tabela Verdade:

Mapa de Karnaugh:

P5 INTERPRETE e RESOLVA A SITUAO APRESENTADA A SEGUIR No reino dos SOSUFARAP SOXUORF h um galo com predilees por pular o alambrado do galinheiro e dar umas pastadas nas circunvizinhanas. Porm, em seu territrio ronda um papagaio deveras bulioso, do qual o Senhor Galo nutre certo cime. Sempre que o galo d a sua contumaz escapada arde-lhe o pensamento de que o papagaio pode estar cortejando as suas prendadas penosas. O galo ouvindo comentrios que nas proximidades do reino h um especialista em eletrnica digital que poderia colocar um alarme para denunciar a possvel invaso do seu territrio pelo papagaio, o galo resolveu pedir-lhe um projeto. Especificando: 1. O galo presente no seu territrio nenhum sinal especial necessrio. 2. Com o galo ausente e o papagaio no se fazendo presente acende uma luz verde indicando que o alarme est ok, galo confiante. 3. Se o galo estiver presente, junto com as galinhas, com a aproximao do papagaio, deve acender uma luz amarela de ateno, papagaio na periferia. 4. Com o galo ausente, se o papagaio invadir o galinheiro, ento deve soar o alarme,

acendendo uma luz vermelha, que significa uma ligao automtica para o RALULEC do galo. Nota: Se o galo estiver presente nada acontece, alm da luz amarela quando da aproximao do papagaio. Sendo a sua equipe desafiada a auxiliar o projetista contratado pelo galo, qual seria a soluo.

CONCLUSO Existem vrios softwares que ajudam o projetista na elaborao de projetos desd resolues de mapas de Karnaugh a visualizao do projeto em um protoboard, todos os softwares usados foram escolhidos por preferencia do projetista, cada software tem suas qualidades e defeitos, o software usado deve ser uma escolha pessoal ao que mais agradar o projetista. Entretanto no foi achado nenhum software que minimizasse as equaes booleanas para portas XOR e XNOR, outro fato observado e que independente do software adotado o projeto ainda e altamente depende do projetista, dependendo apenas do mesmo a qualidade do projeto.

BIBLIOGRAFIA lgebra de Boole. Disponvel em: <

http://download.wlsv.com.br/FG/06_introducaoInformatica_algebra_boole.pdf> Acesso em: 23 jul. 2013. Portas lgicas. Disponvel em: < http://www.prof2000.pt/users/lpa > Acesso em: 23 jul. 2013. Tabela verdade. Disponvel em: < http://pt.wikipedia.org/wiki/Tabela_verdade> Acesso em: 23 jul. 2013. Porta lgica. Disponvel em: < http://pt.wikipedia.org/wiki/Porta_l%C3%B3gica> Acesso em: 23 jul. 2013. Nepomuceno, Rogrio Melo, MAPA DE KARNAUGH. Disponvel em: <

http://pt.wikipedia.org/wiki/Porta_l%C3%B3gica> Acesso em: 23 jul. 2013.

Anda mungkin juga menyukai

- Mmy-Map1201ht7 - Condensadora Toshiba PDFDokumen288 halamanMmy-Map1201ht7 - Condensadora Toshiba PDFCelso Brasil78% (9)

- BT Anexo III Minuta Contrato Adesão Ao Sistema de Compensação de Energia ElétricaDokumen2 halamanBT Anexo III Minuta Contrato Adesão Ao Sistema de Compensação de Energia ElétricaAndré Carvalho CamargoBelum ada peringkat

- Analise VRF X SplitDokumen8 halamanAnalise VRF X SplitVictor Almeida Bressiani100% (2)

- A Construção de Valas para Redes Subterrâneas de Distribuição Será DispostaDokumen2 halamanA Construção de Valas para Redes Subterrâneas de Distribuição Será DispostaAndré Carvalho CamargoBelum ada peringkat

- D&D 5E - Resumo Das Classes - Biblioteca Élfica PDFDokumen53 halamanD&D 5E - Resumo Das Classes - Biblioteca Élfica PDFleo_san_rj67% (3)

- Cálculo Luminotécnico - André Carvalho CamargoDokumen1 halamanCálculo Luminotécnico - André Carvalho CamargoAndré Carvalho CamargoBelum ada peringkat

- D&D 5E - Resumo Das Classes - Biblioteca Élfica PDFDokumen53 halamanD&D 5E - Resumo Das Classes - Biblioteca Élfica PDFleo_san_rj67% (3)

- TCC - André Carvalho CamargoDokumen70 halamanTCC - André Carvalho CamargoAndré Carvalho Camargo0% (1)

- Conte UdoDokumen1 halamanConte UdoAndré Carvalho CamargoBelum ada peringkat

- Aterramento Elétrico 01Dokumen23 halamanAterramento Elétrico 01André Carvalho CamargoBelum ada peringkat

- ArtigoDokumen6 halamanArtigoAndré Carvalho CamargoBelum ada peringkat

- Relatorio 2Dokumen12 halamanRelatorio 2André Carvalho CamargoBelum ada peringkat

- ExercicioDokumen11 halamanExercicioAndré Carvalho CamargoBelum ada peringkat

- Resenha: O Cérebro Do FuturoDokumen5 halamanResenha: O Cérebro Do FuturoAndré Carvalho Camargo100% (1)

- Thomas Alva EdisonDokumen7 halamanThomas Alva EdisonAndré Carvalho CamargoBelum ada peringkat

- Exercicio Programaçao EstruturadaDokumen6 halamanExercicio Programaçao EstruturadaAndré Carvalho CamargoBelum ada peringkat

- 2.5 Revisar Envio Do Teste - QUESTIONÁRIO UNIDADE II - 5387-..Dokumen7 halaman2.5 Revisar Envio Do Teste - QUESTIONÁRIO UNIDADE II - 5387-..daniela2019 MuryBelum ada peringkat

- K100 v3.0 - Manual de ConfiguracaoDokumen21 halamanK100 v3.0 - Manual de ConfiguracaoLeandro LopesBelum ada peringkat

- Rando Super HDW 46Dokumen2 halamanRando Super HDW 46Thiago MolverstetBelum ada peringkat

- Caderno 08 Saude Mental PDFDokumen44 halamanCaderno 08 Saude Mental PDFbibiasilva100% (1)

- Apostila de Hidronicos e Bombas Ime Sindratar 2013 - Passei Direto 25Dokumen1 halamanApostila de Hidronicos e Bombas Ime Sindratar 2013 - Passei Direto 25mydearteacherBelum ada peringkat

- OlfatoDokumen6 halamanOlfatoCamila MendesBelum ada peringkat

- Diego Boffi ENTREVISTA - "QUANDONDE - HAITI2015, UM RELATO DE EXPERIÊNCIA EM INTERVENÇÃO URBANA"Dokumen15 halamanDiego Boffi ENTREVISTA - "QUANDONDE - HAITI2015, UM RELATO DE EXPERIÊNCIA EM INTERVENÇÃO URBANA"Vitoria CarineBelum ada peringkat

- Igualdade Entre Homens e Mulheres 1Dokumen17 halamanIgualdade Entre Homens e Mulheres 1Bruno EduardoBelum ada peringkat

- Portugal e Nápoles Na Época Do Absolutismo ReformistaDokumen554 halamanPortugal e Nápoles Na Época Do Absolutismo ReformistaDermeval MarinsBelum ada peringkat

- Pré - Uni 2009 - FÍSICA II - 2º ANO Caderno - TÉRMICA - OPTICA I-1 ParteDokumen30 halamanPré - Uni 2009 - FÍSICA II - 2º ANO Caderno - TÉRMICA - OPTICA I-1 ParteIsabela ChagasBelum ada peringkat

- Perfilados Eletrocalhas Leitos AcessoriosDokumen37 halamanPerfilados Eletrocalhas Leitos AcessoriosFabio Verdiana100% (1)

- A Dimensão Subjetiva Da Subcidadania: Considerações Sobre A Desigualdade Social BrasileiraDokumen23 halamanA Dimensão Subjetiva Da Subcidadania: Considerações Sobre A Desigualdade Social BrasileiraMarcus MatragaBelum ada peringkat

- Portfolio Eletrica SennacamposDokumen8 halamanPortfolio Eletrica SennacamposMarciel UnepróBelum ada peringkat

- Abraham Maslow SinteseDokumen18 halamanAbraham Maslow SinteseIsraelBelum ada peringkat

- 1 AV ESTRUTURADA - MATEMÁTICA - 6° ANO FINAL-oficialDokumen4 halaman1 AV ESTRUTURADA - MATEMÁTICA - 6° ANO FINAL-oficialHamilton RibeiroBelum ada peringkat

- 102 - Regressão Linear Simples IIDokumen9 halaman102 - Regressão Linear Simples IIjunior freitas tavaresBelum ada peringkat

- 0758a Manual MT 516Dokumen1 halaman0758a Manual MT 516Lucas FernandesBelum ada peringkat

- A Contribuição de Karl PolanyiDokumen40 halamanA Contribuição de Karl PolanyiLucas BalconiBelum ada peringkat

- LIVRO Pesquisa Qualitativa Na Atenção À Saúde (Cap 1)Dokumen11 halamanLIVRO Pesquisa Qualitativa Na Atenção À Saúde (Cap 1)GTGTBelum ada peringkat

- Dicas de Segurança Fogos de ArtificioDokumen16 halamanDicas de Segurança Fogos de ArtificioMaicon BonilhaBelum ada peringkat

- Instrumento de Categorizaã Ã oDokumen3 halamanInstrumento de Categorizaã Ã othamiresvasconcelosBelum ada peringkat

- Antonio AleixoDokumen74 halamanAntonio Aleixodavidaaduarte100% (1)

- Dark KitchensDokumen4 halamanDark KitchensCarolina HolzmannBelum ada peringkat

- Curso Wordpress Modulo 1Dokumen70 halamanCurso Wordpress Modulo 1nelmiBelum ada peringkat

- Resumo de Introdução Ao Estudo Do Direito IIDokumen119 halamanResumo de Introdução Ao Estudo Do Direito IIFilipe Mimoso83% (6)

- QUESTIONÁRIO - Projetos e Planejamento - Aprendizagem Por Projetos Com Foco Pedagógico. - Meio Ambiente Nas EscolasDokumen8 halamanQUESTIONÁRIO - Projetos e Planejamento - Aprendizagem Por Projetos Com Foco Pedagógico. - Meio Ambiente Nas EscolasJosiane LinoBelum ada peringkat

- Aula 5 - Serviços Auxiliares Da SEDokumen73 halamanAula 5 - Serviços Auxiliares Da SEJOAO VICTOR MENDES MELO100% (1)

- Celta 2014Dokumen4 halamanCelta 2014Dexter Furia80% (5)

- Projeto Festival Da Musica Estudantil PDFDokumen9 halamanProjeto Festival Da Musica Estudantil PDFLyvia L LageBelum ada peringkat

- S CRIANÇA Pronto - CópiaDokumen17 halamanS CRIANÇA Pronto - CópiaEleucione da CostaBelum ada peringkat