Lecture 4 Differential Amplifiers

Diunggah oleh

tranhieu_hcmutDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Lecture 4 Differential Amplifiers

Diunggah oleh

tranhieu_hcmutHak Cipta:

Format Tersedia

Dr.

Cuong Huynh Telecommunications DepartmentHCMUT

CMOS ANALOG IC DESIGN

Spring 2013

1

Dr. Cuong Huynh

cuonghpm@yahoo.com

Department of Telecommunications

Faculty of Electrical and Electronics Engineering

Ho Chi Minh city University of Technology

Dr. Cuong Huynh Telecommunications DepartmentHCMUT

CMOS ANALOG IC DESIGN

Spring 2013

2

Dr. Cuong Huynh

cuonghpm@yahoo.com

Department of Telecommunications

Faculty of Electrical and Electronics Engineering

Ho Chi Minh city University of Technology

Lecture 4: Differential Amplifiers

A single-ended signal is measured with respect to a fixed

potential (ground)

A differential signal is measured between two equal and

opposite signals which swing around a fixed potential

(common-mode level)

You can decompose differential signals into a differential

mode (difference) and a common-mode (average

Single-Ended & Differential Signals

3

2

+

+

+

= =

out out

CM out out DM

V V

V V V V

Differential Signal Single-Ended Signal

Single-Ended & Differential Amplifiers

4

Differential signaling

advantages

Common-mode noise

rejection

Higher (ideally double)

potential output swing

Simpler biasing

Improved linearity

Main disadvantage is area,

which is roughly double

Although, to get the same

performance in single-ended

designs, we often have to

increase the area

dramatically

( )

Tn GS DD

V V V

Swing Output Max

( ) ( )

Tn GS DD

V V V 2

Swing Output Max

Common-Mode Level Sensitivity

5

A design which uses two single-ended amplifiers to realize a

differential amplifier is very sensitive to the common-mode

input level

The transistors bias current and transconductance can vary

dramatically with the common-mode input

Impacts small-signal gain

Changes the output common-mode, which impacts the maximum

output swing

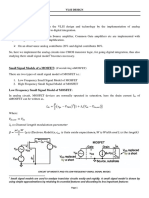

Differential Pair

6

An improved differential amplifier topology utilizes a tail

current source to keep the transistor bias current ideally

constant over the common-mode input range

Allows for a constant small-signal gain and output common-

mode level

Note, you still have to have keep the input pair and tail current

source transistors in saturation

D

SS

DD CM O

D D D m m m

D m

in in

out out

DM

R

I

V V

R R R g g g

R g

V V

V V

A

|

\

|

=

= = = =

=

=

2

and where

,

2 1 2 1

2 1

2 1

Differential Pair Input-Output Characteristics

7

For large-signal differential inputs, the maximum output

levels are well defined and ideally independent of the input

common-mode

For small-signal differential inputs, the small-signal gain is

maximum at low-input signal levels

As the differential input level increases, the circuit becomes more

nonlinear and the gain decreases

Differential Pair I-V Characteristics

8

( ) ( )

( ) ( )

( )

( ) ( ) ( )

( ) ( ) ( )

2

2 1

4

2 1

2

2

2 1

2

2 1

2

2

2 1

2

2 1 2 1

2 1

2

2 1

2 1

2

2 1

2 1

2 1

2 1

2 1 2 1 2 1

4

1

4 using and sides both Squaring

2

2

1

2

2

using and sides both Squaring

2 2

: Difference Voltage Input

in in ox n SS in in ox n D D

D D ss D D D D D D

D D SS in in ox n

D D SS

ox n

in in

SS D D

ox n

D

ox n

D

in in

T GS T GS GS GS in in

V V

L

W

C I V V

L

W

C I I

I I I I I I I I I

I I I V V

L

W

C

I I I

L

W

C

V V

I I I

L

W

C

I

L

W

C

I

V V

V V V V V V V V

+

|

\

|

=

= + =

=

=

= +

=

= =

( ) ( )

2

2 1 2 1 2 1

4

2

1

in in

ox n

ss

in in ox n D D

V V

L

W

C

I

V V

L

W

C I I =

Differential Pair I-V Characteristics

9

( ) ( )

2

2 1 2 1 2 1

4

2

1

in in

ox n

ss

in in ox n D D

V V

L

W

C

I

V V

L

W

C I I =

The differential current is an odd function

of the differential input voltage which

increases linearly for small inputs

For large differential input voltages, the

output differential current compresses due

to the sqrt term

The differential output current maxes out

when all the current flows through one

transistor at AV

in1

L

W

C

I

V

ox n

ss

in

2

1

= A

Differential Pair I-V Characteristics

10

The differential output current will saturate if

the differential input voltage exceeds sqrt(2)

times the equilibrium input overdrive voltage

( )

2

: Overdrive Input al Differenti Zero

overdrive input al differenti zero the to this relate can We

2

: Input al Differenti Maximum

of all support must M1 , At this

ideally , 0 For

0

M1 through flows current all when case he consider t range current maximum For the

1

2 , 1

1 1

1

1 1 2 1

2 2

1 1 2 1

in

ox n

SS

T GS

ox n

SS

T GS in

SS in

in T GS GS GS in

T GS D

SS D SS D D D

V

L

W

C

I

V V

L

W

C

I

V V V

I V

V V V V V V

V V I

I I I I I I

A

= =

= = A

A

A = = = A

= =

= = =

Differential Pair Transconductance

11

The differential pair transconductance and gain is maximum near zero

input differential voltage

( ) ( )

D ss ox n D m v

D

ss ox n m

in

in

ox n

ss

in

ox n

ss

ox n

in

D

m

in in in D D D

in in

ox n

ss

in in ox n D D

R I

L

W

C R G A

R

I

L

W

C G

V

V

L

W

C

I

V

L

W

C

I

L

W

C

V

I

G

V V V I I I

V V

L

W

C

I

V V

L

W

C I I

= =

=

= A

A

A

=

A c

A c

=

= A = A

=

is gain signal - small the , resistors load the g Considerin

is 0 at uctance transcond signal - small The

4

2

4

2

1

and Define

4

2

1

2

2

2 1 2 1

2

2 1 2 1 2 1

Differential Pair Small-Signal Analysis

Method 1 - Superposition

12

The X output from Vin1 is modeled as a

degenerated CS amplifier

Find V

out

(V

in1

)

2

1

and that Note

2

1

1 1

1

2 1 2 1

D m

m

m

D m

in

X

D D D m m m

R g

g

g

R g

V

V

R R R g g g

=

+

=

= = = =

Differential Pair Small-Signal Analysis

Method 1 - Superposition

13

The Y output from Vin1 is modeled as a

Thevenin equivalent driving a CG amplifier

Find V

out

(V

in1

)

2

1

and that Note

1

2

1 2

1

2 1 2 1

D m

m

m

D m

in

Y

D D D m m m

R g

g

g

R g

V

V

R R R g g g

=

+

=

= = = =

Differential Pair Small-Signal Analysis

Method 1 - Superposition

14

( )

( )

( ) ( )

D m

in in

in in D m

in in

tot Y X

in D m

V

Y X

V

out

V

out

V

out

in D m in

D m D m

in

m

m

D m

m

m

D m

V

Y X

V

out

V

out

R g

V V

V V R g

V V

V V

V R g V V V

V V

V R g V

R g R g

V

g

g

R g

g

g

R g

V V V

V

in in

in in

in in

in

=

= =

=

=

|

\

|

=

|

|

|

|

\

|

+

= =

2 1

2 1

2 1

2

1 1 1

1

2

1 2

2

1

1 1

: Gain al Differenti

symmetry, circuit the From

2 2

1 1

total the find To

2 2

1 2

1 1

1

Differential Pair Small-Signal Analysis

Method 2 Half Circuit

The symmetric differential pair can be modeled as a

Thevenin equivalent to observe how the tail node P

changes with the differential input signal

If R

T1

=R

T2

and the input is a truly differential signal, node

P remains constant

This allows the tail node to be treated as a virtual ground

15

Differential Pair Small-Signal Analysis

Method 2 Half Circuit

16

( )

( )

D m

in

in D m

in in

Y X

D m

in

Y

D m

in

X

R g

V

V R g

V V

V V

R g

V

V

R g

V

V

= =

=

=

1

1

1 1

1

1

2

2

: Gain al Differenti

Applying the virtual ground concept allows modeling as

two half circuits

Differential Pair Common-Mode Response

Ideally, a differential amplifier completely rejects

common-mode signals, i.e. A

v,CM

=0

In reality, the finite tail current source impedance results

in a finite common-mode gain

17

SS m

D m

SS m

D

m

CM in

out

CM v

R g

R g

R g

R

g

V

V

A

2 1 2 1

2

2

,

,

+

=

+

|

\

|

= =

Differential Pair with Diode Loads

While the gain of this amplifier is relatively small,

it is somewhat predictable, as it is defined by the

ratio of the transistor sizes and the n/p mobility

18

3

1

3

1

3

1

3

1

3 3 1

1

0 Assuming

|

\

|

|

\

|

=

|

\

|

|

\

|

= ~

~

+ +

=

=

L

W

C

L

W

C

I

L

W

C

I

L

W

C

g

g

A

g

g

g g g

g

A

ox p

ox n

SS ox p

SS ox n

m

m

v

m

m

o m o

m

v

Differential Pair w/ Current-Source Loads

While the gain of this amplifier is higher, it is somewhat

unpredictable, as it is defined by the transistor output

resistance, which changes dramatically with process

variations

19

3 1

1

0 Assuming

o o

m

v

g g

g

A

+

=

=

Differential Pair w/

Diode & Parallel Current-Source Loads

Adding a parallel current source to a diode connected load

allows for increase gain which is still somewhat predictable

20

( )

load diode the from steals" " source current that the percentage current the is where

1

0 Assuming

3

1

3

1

3

1

5 3 3 1

1

o

o

SS ox p

SS ox n

m

m

v

m

m

o o m o

m

v

I

L

W

C

I

L

W

C

g

g

A

g

g

g g g g

g

A

\

|

|

\

|

= ~

~

+ + +

=

=

Cascode Differential Pair

21

( ) ( ) ( )

( )

5 7 5 3 1 3 1

5 7 5 7 5 3 1 3 1 3 1

0 Assuming

o o m o o m m v

o o m o o o o m o o m v

r r g r r g g A

r r g r r r r g r r g A

~

+ + + + =

=

Using a cascode differential

pair and cascode current-

source loads allows for a

considerable increase in gain

However, a relatively large

power supply may be required

to supply the necessary voltage

headroom to keep all the

transistors in saturation

Anda mungkin juga menyukai

- VCO Produces Positive and Negative Output Frequencies PDFDokumen4 halamanVCO Produces Positive and Negative Output Frequencies PDFagmnm1962100% (1)

- Ece-Vii-optical Fiber Communication NotesDokumen254 halamanEce-Vii-optical Fiber Communication NotesLokesh100% (1)

- Lecture09 Ee474 Diff AmpsDokumen23 halamanLecture09 Ee474 Diff AmpsSushma ReddyBelum ada peringkat

- Devices and Circuits Ii: Lecture GoalsDokumen6 halamanDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnBelum ada peringkat

- CukonverterDokumen30 halamanCukonverterPowersavvyBelum ada peringkat

- Lecture 3 Single Stage AmplifiersDokumen76 halamanLecture 3 Single Stage Amplifierstranhieu_hcmutBelum ada peringkat

- Mosfet BasicsDokumen51 halamanMosfet BasicsRaghava KatreepalliBelum ada peringkat

- Lec. 2 Differential Amplifier (Part One)Dokumen22 halamanLec. 2 Differential Amplifier (Part One)Sara Bahaa EldinBelum ada peringkat

- Lect 3Dokumen42 halamanLect 3Supriya Rakshit0% (1)

- Chapter 2-1Dokumen9 halamanChapter 2-1Tibebu Xibe TeBelum ada peringkat

- Lec 11 Sequential Logic CircuitsDokumen49 halamanLec 11 Sequential Logic CircuitsDeependra NigamBelum ada peringkat

- Chapter 4. Multi-Stage AmplifiersDokumen62 halamanChapter 4. Multi-Stage AmplifiersAnh Ha Duy AnhBelum ada peringkat

- Electronic Instrumentation: Experiment 6 - Digital SwitchingDokumen38 halamanElectronic Instrumentation: Experiment 6 - Digital SwitchingEng-Mohammed KayedBelum ada peringkat

- Differential Amplifiers 10Dokumen74 halamanDifferential Amplifiers 10Miguel Ángel MerinoBelum ada peringkat

- Single-Phase Half-Bridge InverterDokumen29 halamanSingle-Phase Half-Bridge InverterSwati MishraBelum ada peringkat

- 1diode PN SKDokumen37 halaman1diode PN SKKurma RaoBelum ada peringkat

- Chapter 4Dokumen61 halamanChapter 4Tuấn NguyễnBelum ada peringkat

- 28.BJT Differential PairDokumen4 halaman28.BJT Differential PairThomas SmithBelum ada peringkat

- Digital To Analog: R R D V 2R DDokumen13 halamanDigital To Analog: R R D V 2R DRudra MishraBelum ada peringkat

- Unit 4 InvertersDokumen86 halamanUnit 4 InvertersHaritha RkBelum ada peringkat

- Electronic Circuits - II Lab ManualDokumen26 halamanElectronic Circuits - II Lab Manualbalabasker100% (1)

- Design of Rogowski Coil With IntegratorDokumen32 halamanDesign of Rogowski Coil With Integratorourbobby100% (1)

- Operational Amplifier: Op Amp High Input Impedance Low Output ImpedanceDokumen18 halamanOperational Amplifier: Op Amp High Input Impedance Low Output ImpedanceUditha MuthumalaBelum ada peringkat

- Single-Stage BJT Amplifiers: Experiment-2Dokumen19 halamanSingle-Stage BJT Amplifiers: Experiment-2karan007_mBelum ada peringkat

- Single-Phase Half-Bridge InverterDokumen29 halamanSingle-Phase Half-Bridge InverterNoureddine BounaslaBelum ada peringkat

- Applications of Op Amp: Unit-IiDokumen79 halamanApplications of Op Amp: Unit-Iimanoj1316kumar_63152Belum ada peringkat

- Ecen 607 CMFB-2011Dokumen44 halamanEcen 607 CMFB-2011Girish K NathBelum ada peringkat

- Signal ProcessingDokumen47 halamanSignal ProcessingAthira rcBelum ada peringkat

- Experiment-1 Power ElectronicsDokumen7 halamanExperiment-1 Power ElectronicsMedhavi RajvanshyBelum ada peringkat

- Designing Combinational Logic CircuitsDokumen127 halamanDesigning Combinational Logic CircuitsAnurag LaddhaBelum ada peringkat

- Ics Basic SimulaDokumen47 halamanIcs Basic Simulasumi36117Belum ada peringkat

- 3.1 Analog MultipliersDokumen17 halaman3.1 Analog MultipliersMarykutty CyriacBelum ada peringkat

- EE2003-E03 Operational AmplifierDokumen6 halamanEE2003-E03 Operational AmplifierntldvlaiBelum ada peringkat

- Lec 1 Introduction Frequencty ResponseDokumen61 halamanLec 1 Introduction Frequencty ResponseAli AhmadBelum ada peringkat

- Lab 4 - Push-Pull Biasing, Buck Converter, ECGDokumen20 halamanLab 4 - Push-Pull Biasing, Buck Converter, ECGcrackintheshatBelum ada peringkat

- Inverter (Konverter DC - AC) : Pekik Argo DahonoDokumen35 halamanInverter (Konverter DC - AC) : Pekik Argo Dahonouyung_mustofaBelum ada peringkat

- Edited - VLSI DESIGN U5Dokumen21 halamanEdited - VLSI DESIGN U5rahul singhBelum ada peringkat

- Buck-Boost and Flyback ConverterDokumen30 halamanBuck-Boost and Flyback Converterlambanaveen123Belum ada peringkat

- Chapter 2 - L1Dokumen20 halamanChapter 2 - L1Markos NiguseBelum ada peringkat

- Current SourcesDokumen17 halamanCurrent SourcesJesse StoutBelum ada peringkat

- Quaid-E-Awam University of Engg., Sci. & Tech., Nawabshah Department of Telecommunication Engineering Amplifiers & OscillatorsDokumen5 halamanQuaid-E-Awam University of Engg., Sci. & Tech., Nawabshah Department of Telecommunication Engineering Amplifiers & Oscillatorsakjan303Belum ada peringkat

- Single Stage Limitations Multi-Stage Amplifiers FeedbackDokumen17 halamanSingle Stage Limitations Multi-Stage Amplifiers FeedbackJoshua DuffyBelum ada peringkat

- Analog Circuits K-NotesDokumen42 halamanAnalog Circuits K-NotesNitin TembhurnikarBelum ada peringkat

- Small-Signal Modeling and Linear AmplificationDokumen30 halamanSmall-Signal Modeling and Linear AmplificationMohammad Gulam AhamadBelum ada peringkat

- Lect 07 Differential AmpDokumen36 halamanLect 07 Differential AmpRogerZhangBelum ada peringkat

- EDC Lab 4Dokumen10 halamanEDC Lab 4Z S PlaysBelum ada peringkat

- Small-Signal Modeling and Linear AmplificationDokumen30 halamanSmall-Signal Modeling and Linear AmplificationTaufique ZamanBelum ada peringkat

- EE42 100 Wb-Lecture19 080713-FDokumen37 halamanEE42 100 Wb-Lecture19 080713-FozanistzBelum ada peringkat

- Dual ConverterDokumen16 halamanDual ConverterUdayakumar VengatesanBelum ada peringkat

- BEE Small Signl ModelDokumen13 halamanBEE Small Signl ModelalysonmicheaalaBelum ada peringkat

- Intro To OpampDokumen20 halamanIntro To OpampmaryambaoBelum ada peringkat

- AC PPTDokumen28 halamanAC PPTPrajwal BirwadkarBelum ada peringkat

- INA128Dokumen6 halamanINA128katalina GarayBelum ada peringkat

- Fundamentals of Mixed Signals and SensorsDokumen4 halamanFundamentals of Mixed Signals and SensorsMaryjane PayaoBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Dari EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Belum ada peringkat

- Thesis Rhee PDFDokumen128 halamanThesis Rhee PDFtranhieu_hcmutBelum ada peringkat

- TTQ 2-4 Type of FibersDokumen15 halamanTTQ 2-4 Type of Fiberstranhieu_hcmutBelum ada peringkat

- Optical Communications: Pham Quang ThaiDokumen13 halamanOptical Communications: Pham Quang Thaitranhieu_hcmutBelum ada peringkat

- TTQ 5-3 Attenuation LimitDokumen19 halamanTTQ 5-3 Attenuation Limittranhieu_hcmutBelum ada peringkat

- TTQ 2-3 Signal DegradationDokumen27 halamanTTQ 2-3 Signal Degradationtranhieu_hcmutBelum ada peringkat

- Optical Communications: Chapter 1: IntroductionDokumen16 halamanOptical Communications: Chapter 1: Introductiontranhieu_hcmutBelum ada peringkat

- TTQ 2-1 Geometrical OpticsDokumen12 halamanTTQ 2-1 Geometrical Opticstranhieu_hcmutBelum ada peringkat

- TTQ 2-2 Light PropagationDokumen36 halamanTTQ 2-2 Light Propagationtranhieu_hcmutBelum ada peringkat

- OP03b-Graident Methods PDFDokumen22 halamanOP03b-Graident Methods PDFtranhieu_hcmutBelum ada peringkat

- OP03d Filter DesignDokumen23 halamanOP03d Filter Designtranhieu_hcmutBelum ada peringkat

- OP03b Graident MethodsDokumen22 halamanOP03b Graident Methodstranhieu_hcmutBelum ada peringkat

- Technological University (Meiktila) Department of Electronic EngineeringDokumen62 halamanTechnological University (Meiktila) Department of Electronic EngineeringdarkforceleaderBelum ada peringkat

- XX XX Xyb Xy: X XX X XX Xyyx Xyyx Xyz Xy XZ X Yz Xyxz XB XBDokumen14 halamanXX XX Xyb Xy: X XX X XX Xyyx Xyyx Xyz Xy XZ X Yz Xyxz XB XBsinemBelum ada peringkat

- Multiple-Module High-Gain High-Voltage DC-DC Transformers For Offshore Wind Energy SystemsDokumen10 halamanMultiple-Module High-Gain High-Voltage DC-DC Transformers For Offshore Wind Energy SystemsNguyễn Văn ĐạoBelum ada peringkat

- 09-MMA Welding 2006Dokumen19 halaman09-MMA Welding 2006Rob WillestoneBelum ada peringkat

- Pin Configuration of IC 7447Dokumen2 halamanPin Configuration of IC 7447Ahmar Niazi100% (1)

- Extending The Life of PF CapacitorsDokumen9 halamanExtending The Life of PF CapacitorsB K SinhaBelum ada peringkat

- Line Protection: 12.1 Classifications of Lines and FeedersDokumen8 halamanLine Protection: 12.1 Classifications of Lines and FeedersSebastian MezaBelum ada peringkat

- Debre Markos UniversityDokumen30 halamanDebre Markos UniversitylegasuBelum ada peringkat

- Assignment 2 Comparison of Incandescent Lamp/ CFL/LEDDokumen5 halamanAssignment 2 Comparison of Incandescent Lamp/ CFL/LEDVasheena MittalBelum ada peringkat

- Microprocessor 8080.Dokumen7 halamanMicroprocessor 8080.ضحى الغزيBelum ada peringkat

- Basic Electronics by Aggarwal IITR PDFDokumen192 halamanBasic Electronics by Aggarwal IITR PDFsamBelum ada peringkat

- Power Electronics Laboratory Nitt B.Tech EeeDokumen11 halamanPower Electronics Laboratory Nitt B.Tech EeeHahahBelum ada peringkat

- Nixie Clock IN14 Instruction Manual Rev 2 V42Dokumen34 halamanNixie Clock IN14 Instruction Manual Rev 2 V42ioan biscaBelum ada peringkat

- Nanocomputers: Michael Pan Meiya Li Rebecca StadlerDokumen55 halamanNanocomputers: Michael Pan Meiya Li Rebecca StadlerHarikesh RawatBelum ada peringkat

- Product Book February 2017Dokumen68 halamanProduct Book February 2017Sakib SayedBelum ada peringkat

- SN 74 HCT 245Dokumen22 halamanSN 74 HCT 245agiyafersyaBelum ada peringkat

- Electronic CKT Simulator ManualDokumen11 halamanElectronic CKT Simulator ManualSuraj SinghBelum ada peringkat

- ST312A Kiln Temperature ControllerDokumen2 halamanST312A Kiln Temperature ControllerDave WalkerBelum ada peringkat

- Air CompressorDokumen7 halamanAir CompressorNishant JeeBelum ada peringkat

- PLC - Input 2 Wire Proximity Switch PDFDokumen2 halamanPLC - Input 2 Wire Proximity Switch PDFCristopher EntenaBelum ada peringkat

- Components of System UnitDokumen8 halamanComponents of System UnitIvan Louie Cruto100% (1)

- Modeling and Simulation of Operational Amplifier Using Verilog - AmsDokumen5 halamanModeling and Simulation of Operational Amplifier Using Verilog - Amsangelo_lopez1993Belum ada peringkat

- The Micro Opto Electro Mechanical SystemsDokumen50 halamanThe Micro Opto Electro Mechanical SystemsRohith TitoBelum ada peringkat

- Seccionadores ABB PDFDokumen8 halamanSeccionadores ABB PDFLuisManuelTrujilloMartínezBelum ada peringkat

- MG University 7th Ece Full SyllabusDokumen12 halamanMG University 7th Ece Full SyllabusJinu MadhavanBelum ada peringkat

- ELSSG01Dokumen27 halamanELSSG01Ariel Anibal AparicioBelum ada peringkat

- Skhi 22B DatasheetDokumen9 halamanSkhi 22B DatasheetRakesh RoyBelum ada peringkat

- 1) Smps Using Viper22A: Circuit DiagramDokumen6 halaman1) Smps Using Viper22A: Circuit DiagramBhadreshkumar SharmaBelum ada peringkat