L190 CascodeOpAmps 2UP

Diunggah oleh

Van Nguyen Huu VanJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

L190 CascodeOpAmps 2UP

Diunggah oleh

Van Nguyen Huu VanHak Cipta:

Format Tersedia

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-1

LECTURE 190 CASCODE OP AMPS I

(READING: GHLM 443-453, AH 293-309) Objective The objective of this presentation is: 1.) Develop cascode op amp architectures 2.) Show how to design with the cascode op amps Outline Op amps with cascoding in the first stage Op amps with cascoding in the second stage Folded cascode op amp Summary

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02)

P.E. Allen - 2002 Page 190-2

Why Cascode Op Amps? Control of the frequency behavior Can get more gain by increasing the output resistance of a stage In the past section, PSRR of the two-stage op amp was insufficient for many applications A two-stage op amp can become unstable for large load capacitors (if nulling resistor is not used) We will see in future sections that the cascode op amp leads to wider ICMR and/or smaller power supply requirements Where Should the Cascode Technique be Used? First stage Good noise performance Requires level translation to second stage Degrades the Miller compensation Second stage Self compensating Increases the efficiency of the Miller compensation Increases PSRR

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-3

Use of Cascoding in the First Stage of the Two-Stage Op Amp

M3 VDD M4

Implementation of the floating voltage VBias.

VDD M3

MB3 MB4

M4

MC3 MC3 R MC1 M1

+v

in

MC4

vo1

MB5

MC4

vo1

R MC1 M1

+v

in

MC2

M2

VBias

vin + 2

MB1

+ VBias -

MC2

M2

MB2

2+ VBias -

2+ VBias -

vin + 2

M5 VSS

M5 VSS

Fig. 6.5-1

Rout of the first stage is RI (gmC2rdsC2rds2)||(gmC4rdsC4rds4) vo1 Voltage gain = v = gm1RI [The gain is increased by approximately 0.5(gMCrdsC)] in As a single stage op amp, the compensation capacitor becomes the load capacitor.

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02) P.E. Allen - 2002 Page 190-4

Example 1 Single-Stage, Cascode Op Amp Performance Assume that all W/L ratios are 10 m/1 m, and that IDS1 = IDS2 = 50 A of single stage op amp. Find the voltage gain of this op amp and the value of CI if GB = 10 MHz. Use the model parameters of Table 3.1-2. Solution The device transconductances are gm1 = gm2 = gmI = 331.7 S gmC2 = 331.7S gmC4 = 223.6 S. The output resistance of the NMOS and PMOS devices is 0.5 M and 0.4 M, respectively. RI = 25 M Av(0) = 8290 V/V. For a unity-gain bandwidth of 10 MHz, the value of CI is 5.28 pF. What happens if a 100pF capacitor is attached to this op amp? GB goes from 10MHz to 0.53MHz.

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-5

Two-Stage Op Amp with a Cascoded First-Stage

VDD M3

MB3 MB4

M4

MT2 MC3 R

MB5

MC4

vo1

M6 MT1 Cc

vout

MC1 M1

+v

in

MB1

+ VBias -

MC2

M2

MB2

2+ VBias -

vin + 2

M5 VSS

M7

Fig. 6.5-2

MT1 and MT2 are required for level shifting from the first-stage to the second. The PSRR+ is improved by the presence of MT1 p3 p2 Internal loop pole at the gate of M6 may cause the Miller compensation to fail. The voltage gain of this op amp could easily be 100,000V/V

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02)

p1

z1

Fig. 6.5-2

P.E. Allen - 2002 Page 190-6

Two-Stage Op Amp with a Cascode Second-Stage

VDD M6 M3 M4 VBP Cc VBN MC6

vout

Rz

vin +

M1

M2

MC7

CL

+ VBias -

M5 VSS

M7

Fig. 6.5-3

Av = gmIgmIIRIRII where gmI = gm1 = gm2, gmII = gm6, 1 2 RI = gds2 + gds4 = (2 + 4)ID5 and RII = (gmC6rdsC6rds6)||(gmC7rdsC7rds7) Comments: The second-stage gain has greatly increased improving the Miller compensation The overall gain is approximately (gmrds)3 or very large Output pole, p2, is approximately the same if Cc is constant The RHP is the same if Cc is constant

ECE 6412 - Analog Integrated Circuit Design - II P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-7

A Balanced, Two-Stage Op Amp using a Cascode Output Stage VDD gm1gm8 vin gm2gm6 vin vout = g + g RII 2 2 m 3 m 4 M6 M4

g m1 gm2 = + kvin RII = gm1kRII vin 2 2 R2 R1 vout where M1 M2 M9 vin CL M12 RII = (gm7rds7rds6)||(gm12rds12rds11) + M10 M11 M5 and + M13 VBias gm8 gm6 Fig. 6.5-4 k = gm3 = gm4 VSS Note that this op amp is balanced because the drain-to-ground loads for M1 and M2 are identical. TABLE 1 - Pertinent Design Relationships for Balanced, Cascode Output Stage Op Amp. g m 1g m 8 1 gm1gm8 gm2gm6 Iout GB = gm3CL Av = 2 + gm4 Slew rate = CL g RII m3 I5 1/2 I5 1/2 |V |(max) +V (min) Vin(max) = VDD V (min) = V + V + + VT1(min) TO3 T1 in SS DS5 3 1 M15

M3

M8

M14

M7

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02)

P.E. Allen - 2002 Page 190-8

Example 2 - Design of Balanced, Cascoded Output Stage Op Amp The balanced, cascoded output stage op amp is a useful alternative to the two-stage op amp. Its design will be illustrated by this example. The pertinent design equations for the op amp were given above. The specifications of the design are as follows: Slew rate = 5 V/s with a 50 pF load VDD = VSS = 2.5 V GB = 10 MHz with a 10 pF load Av 5000 Input CMR = 1V to +1.5 V Output swing = 1.5 V Use the parameters of Table 3.1-2 and let all device lengths be 1 m. Solution While numerous approaches can be taken, we shall follow one based on the above specifications. The steps will be numbered to help illustrate the procedure. 1.) The first step will be to find the maximum source/sink current. This is found from the slew rate. Isource/Isink = CL slew rate = 50 pF(5 V/s) = 250 A 2.) Next some W/L constraints based on the maximum output source/sink current are developed. Under dynamic conditions, all of I5 will flow in M4; thus we can write Max. Iout(source) = (S6/S4)I5 and Max. Iout(sink) = (S8/S3)I5 The maximum output sinking current is equal to the maximum output sourcing current if S3 = S4, S6 = S8, and S10 = S11

ECE 6412 - Analog Integrated Circuit Design - II P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-9

Example 2 - Continued 3.) Choose I5 as 100 A. This current (which can be changed later) gives S6 = 2.5S4 and S8 = 2.5S3 Note that S8 could equal S3 if S11 = 2.5S10. This would minimize the power dissipation. 4.) Next design for 1.5 V output capability. We shall assume that the output must source or sink the 250A at the peak values of output. First consider the negative output peak. Since there is 1 V difference between VSS and the minimum output, let VDS11(sat) = VDS12(sat) = 0.5 V (we continue to ignore the bulk effects). Under the maximum negative peak assume that I11 = I12 = 250 A. Therefore 2I11 2I12 500 A = = (110 A/V2)S11 K'NS11 K'NS12 which gives S11 = S12 = 18.2 and S9 = S10 = 18.2. For the positive peak, we get 0.5 = 2 I6 2 I7 500 A = = K'PS6 K'PS7 (50 A/V2)S6 which gives S6 = S7 = S8 = 40 and S3 = S4 = (40/2.5) = 16. 5.) Next the values of R1 and R2 are designed. For the resistor of the self-biased cascode we can write R1 = VDS12(sat)/250A = 2k and R2 = VSD7(sat)/250A = 2k 0.5 =

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02)

P.E. Allen - 2002 Page 190-10

Example 2 - Continued Using this value of R1 (R2) will cause M11 to slightly be in the active region under quiescent conditions. One could redesign R1 to avoid this but the minimum output voltage under maximum sinking current would not be realized. 6.) Now we must consider the possibility of conflict among the specifications. First consider the input CMR. S3 has already been designed as 16. Using ICMR relationship, we find that S3 should be at least 4.1. A larger value of S3 will give a higher value of Vin(max) so that we continue to use S3 = 16 which gives Vin(max) = 1.95V. Next, check to see if the larger W/L causes a pole below the gainbandwidth. Assuming a Cox of 0.4fF/m2 gives the first-stage pole of -g m 3 - 2KPS3I3 p3 = Cgs3+Cgs8 = (0.667)(W3L3+W8L8)Cox = 33.15x109 rads/sec or 5.275GHz which is much greater than 10GB. 7.) Next we find gm1 (gm2). There are two ways of calculating gm1. (a.) The first is from the Av specification. The gain is Av = (gm1/2gm4)(gm6 + gm8) RII Note, a current gain of k could be introduced by making S6/S4 (S8/S3 = S11/S3) equal to k. 2KPS6I6 gm6 gm11 = = gm4 gm3 2KPS4I4 = k

ECE 6412 - Analog Integrated Circuit Design - II P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-11

Example 2 - Continued Calculating the various transconductances we get gm4 = 282.4 S, gm6 = gm7 = gm8 = 707 S, gm11 = gm12 = 707 S, rds6 = rd7 = 0.16 M, and rds11 = rds12 = 0.2 M. Assuming that the gain Av must be greater than 5000 and k = 2.5 gives gm1 > 72.43 S. (b.) The second method of finding gm1 is from the GB specifications. Multiplying the gain by the dominant pole (1/CIIRII) gives gm1(gm6 + gm8) GB = 2gm4CL Assuming that CL= 10 pF and using the specified GB gives gm1 = 251 S. Since this is greater than 72.43S, we choose gm1 = gm2 = 251S. Knowing I5 gives S1 = S2 = 11.45 12. 8.) The next step is to check that S1 and S2 are large enough to meet the 1V input CMR specification. Use the saturation formula we find that VDS5 is 0.5248 V. This gives S5 = 6.6 7. The gain becomes Av = 6,925V/V and GB = 10 MHz for a 10 pF load. We shall assume that exceeding the specifications in this area is not detrimental to the performance of the op amp. 9.) With S5 = 7 then we can design S13 from the relationship I13 125A S13 = I S5 = 100A 7 = 8.75 5

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02) P.E. Allen - 2002 Page 190-12

Example 2 - Continued 10.) Finally we need to design the value of VBias, which can be done with the values of S5 and I5 known. However, M5 is usually biased from a current source flowing into a MOS diode in parallel with the gate-source of M5. The value of the current source compared with I5 would define the W/L ratio of the MOS diode. Table 2 summarizes the values of W /L that resulted from this design procedure. The power dissipation for this design is seen to be 2 mW. The next step would be begin simulation. Table 2 - Summary of W/L Ratios for Example 2 S1 = S2 = 12 S3 = S4 = 16 S5 = 7 S6 = S7 = S8 = S14 = S15 = 40 S9 = S10 = S11 = S12 = 18.2 S13 = 8.75

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-13

Technological Implications of the Cascode Configuration

A B Thin oxide A B C

C D

;; ;;; ;;

Poly I Poly II

n+

If a double poly CMOS process is available, internode parasitics can be minimized. As an alternative, one should keep the drain/source between the transistors to a minimum area.

A A B Thin oxide B

Minimum Poly separation

C D

;; ;; ;;; ;

Poly I Poly I

n+ n-channel n+ n-channel

p substrate/well

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02)

;; ; ;;

D

n-channel

n+

p substrate/well

Fig. 6.5-5

n+

Fig. 6.5-5A

P.E. Allen - 2002 Page 190-14

Input Common Mode Range for Two Types of Differential Amplifier Loads

VDD-VSG3+VTN + VSG3 Input - M3 Common Mode M1 Range VSS+VDS5+VGS1 + VBias VDD VDD-VSD3+VTN VDD

+ VSD4

M4 M2

+ V Input SD3 Common - M3 Mode Range M1

VSS+VDS5+VGS1

+ VSD4

M4 VBP M2

M5 vicm

VSS Differential amplifier with a current mirror load.

VSS Differential amplifier with Fig. 6.5-6 current source loads.

+ VBias -

M5 vicm

In order to improve the ICMR, it is desirable to use current source (sink) loads without losing half the gain. The resulting solution is the folded cascode op amp.

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-15

The Folded Cascode Op Amp

VDD

M14 M4 I4 M5 I5 A B RB RA

I1

+ vin -

I2

M13 M6 I6 M7 I7

M1

M2

R1 R2

vout

CL

M9 M11

Fig. 6.5-7

I3

+ VBias -

M8

M3

M12 M10 VSS

We have examined the small signal performance and the frequency response in an earlier lecture.

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02)

P.E. Allen - 2002 Page 190-16

PSRR of the Folded Cascode Op Amp Consider the following circuit used to model the PSRR-:

VDD

R

Vss

Cgd9 Cgd11 VGSG9 Vout rds9 Cgd9

M9 Vss

Vss

rds11

Vss

VGS11

Cout

Rout

+ Vout -

M11

Vss

Fig. 6.5-9A

This model assumes that gate, source and drain of M11 and the gate and source of M9 all vary with VSS. We shall examine Vout/Vss rather than PSRR-. (Small Vout/Vss will lead to large PSRR-.) The transfer function of Vout/Vss can be found as sCgd9Rout Vout Vss sCoutRout+1 for Cgd9 < Cout The approximate PSRR- is sketched on the next page.

ECE 6412 - Analog Integrated Circuit Design - II P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-17

Frequency Response of the PSRR- of the Folded Cascode Op Amp

dB

|PSRR-|

|Avd()|

1 Cgd9Rout

Dominant pole frequency

0dB Cgd9 Cout

GB

Vout Vss Other sources of Vss injection, i.e. rds9

log10()

Fig. 6.5-10A

We see that the PSRR of the cascode op amp is much better than the two-stage op amp.

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02)

P.E. Allen - 2002 Page 190-18

Design Approach for the Folded-Cascode Op Amp

Step Relationship/ Requirement Slew Rate 1 Bias currents in output 2 cascodes Maximum output 3 voltage, vout(max) Minimum output voltage, vout(min) Self-bias cascode gm 1 GB = C L Minimum input CM Design Equation/Constraint I3 = SRCL I4 = I5 = 1.2I3 to 1.5I3 2 I7 , S7= Let S4=S14=S5 & 2 KPVSD72 KPVSD5 S13=S6=S7 2 I9 2I11 , S9 = Let S10=S11 & S11= 2 KNVDS92 KNVDS11 S8=S9 R1 = VSD14(sat)/I14 and R2 = VDS8(sat)/I6 gm12 GB2CL2 S1=S2= K I = K I N 3 N 3 2 I3 S3 = I3 2 KNVin(min)-VSS- K S -VT1 N 1 S5= 2 I5 2 I4 S4 = S5 =K V -V (max)+V T1) P ( DD in gm2 vout gm1 2+k = + 2(1+k)Rout = 2+2k gmIRout vin 2 Pdiss = (VDD-VSS)(I3+I12+I10+I11)

P.E. Allen - 2002

Comments

Avoid zero current in cascodes VSD5(sat) = VSD7(sat) = 0.5[VDD-Vout(min)] VDS9(sat) = VDS11(sat) = 0.5(Vout(min)-|VSS|)

5 6

8 9 10

Maximum input CM Differential Voltage Gain Power dissipation

S4 and S5 must meet or exceed the value in step 3

ECE 6412 - Analog Integrated Circuit Design - II

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-19

Example 3 - Design of a Folded-Cascode Op Amp Follow the procedure given to design the folded-cascode op amp when the slew rate is 10V/s, the load capacitor is 10pF, the maximum and minimum output voltages are 2V for 2.5V power supplies, the GB is 10MHz, the minimum input common mode voltage is -1.5V and the maximum input common mode voltage is 2.5V. The differential voltage gain should be greater than 5,000V/V and the power dissipation should be less than 5mW. Use channel lengths of 1m. Solution Following the approach outlined above we obtain the following results. I3 = SRCL = 10x10610-11 = 100A Select I4 = I5 = 125A. Next, we see that the value of 0.5(VDD-Vout(max)) is 0.5V/2 or 0.25V. Thus, 2125A 212516 S4 = S5 = S14 = 50A/V2(0.25V)2 = 50 = 80 and assuming worst case currents in M6 and M7 gives, 2125A 212516 S6 = S7 = S13 = 50A/V2(0.25V)2 = 50 = 80 The value of 0.5(Vout(min)-|VSS|) is also 0.25V which gives the value of S8, S9, S10 and S11 2I8 2125 as S8 = S9 = S10 = S11 = K V 2 = 110(0.25)2 = 36.36 N DS8

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02) P.E. Allen - 2002 Page 190-20

Example 3 - Continued The value of R1 and R2 is equal to 0.25V/125A or 2k. In step 6, the value of GB gives S1 and S2 as GB2CL2 (20x106)2(10-11)2 S1 = S2 = KNI3 = 110x10-6100x10-6 = 35.9 The minimum input common mode voltage defines S3 as 2 I3 200x10-6 = S3 = = 20 I3 100 2 2 110x10-6 -1.5+2.5 -0.75 KNVin(min)-VSS- K S - VT1 11035.9

N 1

We need to check that the values of S4 and S5 are large enough to satisfy the maximum input common mode voltage. The maximum input common mode voltage of 2.5 requires 2 I4 2125A S4 = S5 K [V -V (max)+V ] = 50x10-6A/V2[0.7V]2 = 10.2 P DD in T1 which is much less than 80. In fact, with S4 = S5 = 80, the maximum input common mode voltage is 3V. Finally, S12, is given as 125 S12 = 100 S3 = 25 The power dissipation is found to be Pdiss = 5V(125A+125A+125A) = 1.875mW

ECE 6412 - Analog Integrated Circuit Design - II P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-21

Example 3 - Continued The small-signal voltage gain requires the following values to evaluate: S4, S5, S13, S14: S6, S7: S1, S2: Thus, S8, S9, S10, S11: gm = 21255080 = 1000S and gds = 125x10-60.05 = 6.25S and gds = 75x10-60.05 = 3.75S gm = 27511036.36 = 774.6S and gds = 75x10-60.04 = 3S gm = 2755080 = 774.6S

gmI = 25011035.9 = 628S and gds = 50x10-6(0.04) = 2S

1 1 = 86.07M RII gm9rds9rds11 = (774.6S)3S 3S 1 1 = 19.40M Rout 86.07M||(774.6S)3.75S 2S+6.25S

RII(gds2+gds4) 86.07M(2S+6.25S)(3.75S) = = 3.4375 gm7rds7 774.6S The small-signal, differential-input, voltage gain is 2+k 2+3.4375 g R 0.628x10-319.40x106 = 7,464 V/V = Avd = mI out 2+2 k 2+6.875 The gain is larger than required by the specifications which should be okay. k=

ECE 6412 - Analog Integrated Circuit Design - II Lecture 190 Cascode Op Amps - I (2/18/02) P.E. Allen - 2002 Page 190-22

Comments on Folded Cascode Op Amps Good PSRR Good ICMR Self compensated Can cascade an output stage to get extremely high gain with lower output resistance (use Miller compensation in this case) Need first stage gain for good noise performance Widely used in telecommunication circuits where large dynamic range is required

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 190 Cascode Op Amps - I (2/18/02)

Page 190-23

SUMMARY Cascode op amps offer an alternate architecture to the two-stage op amp The cascode op amp is typically self-compensating The cascode op amp generally has better PSRR

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- ComparatorDokumen32 halamanComparatorShiv MeenaBelum ada peringkat

- Calibration Procedure For Clamp Meters Fluke Models 333, 334, 335, 336 and 337 - Tb-9-6625-2408-24Dokumen15 halamanCalibration Procedure For Clamp Meters Fluke Models 333, 334, 335, 336 and 337 - Tb-9-6625-2408-24luroguita100% (1)

- Unit 12: The Right Approach: 1 ReadingDokumen5 halamanUnit 12: The Right Approach: 1 ReadingVan Nguyen Huu VanBelum ada peringkat

- Unit 9 8231Dokumen7 halamanUnit 9 8231Van Nguyen Huu VanBelum ada peringkat

- Unit 12: The Right Approach: 1 ReadingDokumen5 halamanUnit 12: The Right Approach: 1 ReadingVan Nguyen Huu VanBelum ada peringkat

- Unit 10: Hard To Believe?: Bi Li:vDokumen5 halamanUnit 10: Hard To Believe?: Bi Li:vVan Nguyen Huu VanBelum ada peringkat

- Unit 11 889Dokumen6 halamanUnit 11 889Van Nguyen Huu VanBelum ada peringkat

- Unit 5 566Dokumen6 halamanUnit 5 566Van Nguyen Huu VanBelum ada peringkat

- Lecture 410 - High-Speed Comparators: (READING: AH - 483-488) ObjectiveDokumen5 halamanLecture 410 - High-Speed Comparators: (READING: AH - 483-488) ObjectiveVan Nguyen Huu VanBelum ada peringkat

- L380 2StageOLCompII 2UPDokumen7 halamanL380 2StageOLCompII 2UPVan Nguyen Huu VanBelum ada peringkat

- L360 Char Com para Tors 2UPDokumen7 halamanL360 Char Com para Tors 2UPTaj TajuBelum ada peringkat

- L400 Discrete TimeComp 2UPDokumen6 halamanL400 Discrete TimeComp 2UPVan Nguyen Huu VanBelum ada peringkat

- L370 2StageOLCompI 2UPDokumen7 halamanL370 2StageOLCompI 2UPVan Nguyen Huu VanBelum ada peringkat

- L390 OpenLoopComp 2UPDokumen12 halamanL390 OpenLoopComp 2UPVan Nguyen Huu VanBelum ada peringkat

- L340 LowNoiseOpAmps 2UPDokumen10 halamanL340 LowNoiseOpAmps 2UPVan Nguyen Huu VanBelum ada peringkat

- L280 SerShnt SHNTSHNT 2UPDokumen5 halamanL280 SerShnt SHNTSHNT 2UPVan Nguyen Huu VanBelum ada peringkat

- L350 LowVoltOpAmps 2UPDokumen15 halamanL350 LowVoltOpAmps 2UPVan Nguyen Huu VanBelum ada peringkat

- L320 DiffOutputOpAmps 2UPDokumen9 halamanL320 DiffOutputOpAmps 2UPBiswajit BeheraBelum ada peringkat

- L310 HiSpeedOpAmps 2UPDokumen18 halamanL310 HiSpeedOpAmps 2UPVan Nguyen Huu VanBelum ada peringkat

- Lecture 250 - Introduction To Feedback Concepts: (READING: GHLM - 553-563) ObjectiveDokumen8 halamanLecture 250 - Introduction To Feedback Concepts: (READING: GHLM - 553-563) ObjectiveVan Nguyen Huu VanBelum ada peringkat

- L330 LowPowerOpAmps 2UPDokumen7 halamanL330 LowPowerOpAmps 2UPVan Nguyen Huu VanBelum ada peringkat

- L300 BufferedOpAmps 2UPDokumen12 halamanL300 BufferedOpAmps 2UPVan Nguyen Huu VanBelum ada peringkat

- L270 SeriesSeriesFb 2UPDokumen6 halamanL270 SeriesSeriesFb 2UPVan Nguyen Huu VanBelum ada peringkat

- L290 ReturnRatio 2UPDokumen7 halamanL290 ReturnRatio 2UPVan Nguyen Huu VanBelum ada peringkat

- Feedback TopologyDokumen6 halamanFeedback Topologyilg1Belum ada peringkat

- L220 ACAnalysisof741 2UPDokumen11 halamanL220 ACAnalysisof741 2UPVan Nguyen Huu VanBelum ada peringkat

- L200 CascodeOpAmps II 2UPDokumen6 halamanL200 CascodeOpAmps II 2UPVan Nguyen Huu VanBelum ada peringkat

- Lecture 230 - 741 Frequency Response: (READING: GHLM - 537-544) ObjectiveDokumen5 halamanLecture 230 - 741 Frequency Response: (READING: GHLM - 537-544) ObjectiveVan Nguyen Huu VanBelum ada peringkat

- Opamp Spice SimulationDokumen13 halamanOpamp Spice Simulationjitu_4Belum ada peringkat

- L180 PSRR 2upDokumen7 halamanL180 PSRR 2upVan Nguyen Huu VanBelum ada peringkat

- Cirrus MM Chapter 23-30Dokumen10 halamanCirrus MM Chapter 23-30A Sebastian Pastrana SBelum ada peringkat

- ESM740G TiristorDokumen2 halamanESM740G Tiristorjosenicolas12000Belum ada peringkat

- High RTWP 3GDokumen3 halamanHigh RTWP 3GHTMBelum ada peringkat

- MCP342X Datasheet PDFDokumen58 halamanMCP342X Datasheet PDFFelipePerezBelum ada peringkat

- P49 - Wireless Bipolar Electrosurgical Device by Using RF Energy Transfer PDFDokumen5 halamanP49 - Wireless Bipolar Electrosurgical Device by Using RF Energy Transfer PDFihsanbuBelum ada peringkat

- Ec6801 PDFDokumen101 halamanEc6801 PDFnandhaBelum ada peringkat

- DUdtFilters Rev6.PdDokumen4 halamanDUdtFilters Rev6.PdMuhammad ShuaibBelum ada peringkat

- Interim Standard 95Dokumen5 halamanInterim Standard 95Malgireddy RavireddyBelum ada peringkat

- Hemant PPT BJT Biasing H ParametersDokumen62 halamanHemant PPT BJT Biasing H ParametersHemant SaraswatBelum ada peringkat

- Macara Comedil CT 602-8Dokumen4 halamanMacara Comedil CT 602-8Andreea NanBelum ada peringkat

- Data Amplificador HFCDokumen7 halamanData Amplificador HFCMiguel VasBelum ada peringkat

- Radio Frequency BasicDokumen38 halamanRadio Frequency BasicKomkrit PonprachanuwatBelum ada peringkat

- C Band and Ext. C-BandDokumen4 halamanC Band and Ext. C-BandAwadalla JbooraBelum ada peringkat

- Counters and Shift RegDokumen24 halamanCounters and Shift RegRakesh Kumar D100% (1)

- IM31 SM3 2 1 0 0 System RegulatorDokumen32 halamanIM31 SM3 2 1 0 0 System RegulatorPete PearlBelum ada peringkat

- Acoustics LabDokumen4 halamanAcoustics LabRom PeDrazaBelum ada peringkat

- DPSKDokumen3 halamanDPSKరాహుల్ దేవ్Belum ada peringkat

- Functions of Digital Frequency MeterDokumen3 halamanFunctions of Digital Frequency MetersruthiBelum ada peringkat

- Oki Service ManualDokumen52 halamanOki Service ManualAnonymous siIkxcPLBelum ada peringkat

- Az 1575Dokumen41 halamanAz 1575Arleig Augusto de MatosBelum ada peringkat

- Omni AntennaDokumen2 halamanOmni AntennaDaniel ManoleBelum ada peringkat

- 74ALS374 - Dtype Flip FlopDokumen7 halaman74ALS374 - Dtype Flip FlopDwp BhaskaranBelum ada peringkat

- Four Quadrant Multiplier CmosDokumen11 halamanFour Quadrant Multiplier CmosRodrigo SantosBelum ada peringkat

- HUAWEI BTS3012AE Hardware Structure and Operating Principle-20061011-B-1.0Dokumen91 halamanHUAWEI BTS3012AE Hardware Structure and Operating Principle-20061011-B-1.0Ahmad ElhajBelum ada peringkat

- Sharp Lc32bd6x LCD TV SMDokumen212 halamanSharp Lc32bd6x LCD TV SMkothuraBelum ada peringkat

- Data Sheet Transformer Rectifier PDFDokumen3 halamanData Sheet Transformer Rectifier PDFBoussaid SouheilBelum ada peringkat

- Lab 10555 TimerDokumen10 halamanLab 10555 Timermanaj_mohapatra2041Belum ada peringkat

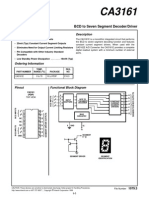

- Ca 3161Dokumen4 halamanCa 3161romanjoseBelum ada peringkat