Contadores Assíncronos

Diunggah oleh

Ivanir Ferreira da SilvaHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Contadores Assíncronos

Diunggah oleh

Ivanir Ferreira da SilvaHak Cipta:

Format Tersedia

66 CAPTULO 4 CIRCUITOS SEQUENCIAIS II: CONTADORES ASSNCRONOS Sumrio 4.1. Introduo ............................................................................................................................ 68 4.2. Contadores Assncronos Crescentes ....................................................................................

. 68 4.3. Contadores Assncronos Decrescentes ................................................................................. 72 4.4. Contador Assncrono Crescente / Decrescente de 3 bits ..................................................... 75 4.5. Exerccios de Fixao ........................................................................................................... 76

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

Prof. Marcelo Wendling

67 CAPTULO 4 CIRCUITOS SEQUENCIAIS II: CONTADORES ASSNCRONOS Estudando outra aplicao de flip-flops em circuitos sequenciais, partimos agora para circuitos contadores. O primeiro tipo a ser estudado so os Contadores Assncronos. Aps esse captulo voc dever ser capaz de: (1) Entender o funcionamento de circuitos contadores assncronos e suas topologias; e (2) Projetar um contador assncrono a partir das especificaes necessrias.

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

Prof. Marcelo Wendling

68 4.1. Introduo Contadores so circuitos digitais que variam seus estados, sob comando de um clock, de acordo com uma sequncia predeterminada. 1 So divididos em duas categorias: assncronos e sncronos.

4.2. Contadores Assncronos Crescentes Como caractersticas principais de contadores assncronos temos:

(1) Os FF no possuem as entradas clock em comum; (2) So arranjados de forma que a entrada clock do flip-flop de ordem n seja a sada do flip-flop de ordem n-1; (3) Possuem sada binria sequencial; e (4) O bit mais significativo da contagem (MSB) est sempre no ltimo flip-flop, considerando como primeiro flip-flop o que recebe os pulsos de clock.

Seu circuito bsico apresenta um grupo de flip-flops tipo T em de estado de comutao (T=1), ou seja, cada transio ativa na entrada clock de um flip-flop causa uma inverso no estado lgico da sada desse flip-flop: Qn1 Qn

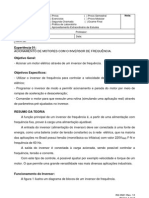

Exemplo 1: Contador de pulsos de 4 bits, figura 4.1.

Figura 4.1 Contador Assncrono Crescente de 4 bits.

IDOETA, I. V. CAPUANO, F. Q. Elementos de Eletrnica Digital. Ed. rica. | Prof. Marcelo Wendling

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

69 Assumindo inicialmente que Q0 = Q1 = Q2 = Q3 = 0, aplicando pulsos na entrada CLK do sistema, temos o mapa de pulsos representado na figura 4.2, onde conclumos que a cada transio ativa do clock, o estado das sadas Q so incrementados.

CLK Q0 Q1 Q2 Q3 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 1 0 1 1 0 0 1 1 0 1 1 0 0 0

Figura 4.2 Mapa de pulsos de um contador assncrono crescente de 4 bits.

Avaliando as sadas a partir de Q3 (MSB), temos uma contagem binria sequencial crescente: Aps X pulsos de clock 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 Q3 (MSB) 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 Q2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 Q1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 Q0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

Prof. Marcelo Wendling

16 clock

70 Outro fator notvel que o contador assncrono mostrado a partir de um divisor de frequncia, logo:

f Qn

onde n a ordem do flip-flop, a partir de Q0. Exemplo 2: Contador de dcada

f clk 2 n 1

o circuito que executa a contagem de 0 at 9 (0000 2 at 10012), ou seja, 10 algarismos. A base desse circuito a mesma apresentada no Exemplo 1, porm, para que o circuito no ultrapasse o nmero 9, utiliza-se um arranjo externo de forma a acionar as entradas CLR dos flip flops quando o circuito assumir o caso 10 (10102), ou seja, quando a sada for 10102 (um valor acima do valor desejado), CLR=0. Observe:

Aps X pulsos de clock 1 2 3 4 5 6 7 8 9 10 10

Q3 (MSB) 0 0 0 0 0 0 0 0 1 1 1 0

Q2 0 0 0 0 1 1 1 1 0 0 0 0

Q1 0 0 1 1 0 0 1 1 0 0 1 0

Q0 0 1 0 1 0 1 0 1 0 1 0 0

CLR 1 1 1 1 1 1 1 1 1 1 0 1

| Prof. Marcelo Wendling

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

71 Logo, quando o circuito assumir, por um curtssimo espao de tempo, o valor 1010 2, a entrada CLR do sistema ativada, forando o circuito a retornar ao estado inicial 0000 2.

Exemplo 3: Contador de dcada com reset inicial.

Exerccio: Implemente contadores assncronos que executem as seguintes sequncias:

(a) de 0 a 8; (b) de 0 a 12, com reset inicial; (c) de 0 a 14, com reset inicial; (d) de 2 a 8; (e) de 3 a 12, com reset inicial; e (f) de 5 a 14, com reset inicial.

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

Prof. Marcelo Wendling

72 4.3. Contadores Assncronos Decrescentes Existem dois mtodos para se obter a contagem decrescente em contadores assncronos. No exemplo abaixo verificamos o primeiro modo.

Exemplo 4: Contador decrescente de Fh 0h:

Analisando a contagem a partir das sadas Q dos flip-flops teramos: 0 0 0 0 0 0 0 0 0 0 1 1 ... 0 0 1 1 0 0 0 1 0 1 0 1 Enquanto nas sadas Q temos: Q3 Q2 Q1 Q0 1 1 1 1 1 1 1 0 1 1 0 1 1 1 0 0 1 0 1 1 1 0 1 0 ...

Podemos concluir que enquanto as sadas Q possuem sada sequencial crescente, as sadas Q possuem sada decrescente. Um grande inconveniente desse mtodo acontece quando queremos resetar o contador em valores que no so os extremos do circuito, como 0h e Fh no caso anterior.

Exemplo 5: Contador de Eh 2h.

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

Prof. Marcelo Wendling

73 Observando o circuito anterior, pode-se perceber que foi utilizada uma lgica inversa em todo o processo de reset do circuito. Isso se d pelo fato de buscarmos valores nas sadas Q dos flip-flops, ou seja, os valores complementares. Esse tipo de implementao pode acarretar em erros de projeto, pois facilmente confunde-se a lgica complementar com a lgica convencional utilizada em contadores assncronos crescentes. Uma maneira de evitar esse tipo de erro usando um segundo mtodo de contagem decrescente. Esse mtodo consiste em utilizar as sadas Q dos flip -flops como clock, no lugar das sadas Q.

Exemplo 6: Contador de Fh 0h, utilizando o segundo modo de contagem:

Neste circuito, as sadas Q1, Q2 e Q3 trocam seus estados quando as sadas Q0, Q1 e Q2 transitam de 0 para 1, respectivamente. Analisando o mapa de pulsos abaixo, considerando inicialmente Q0 = Q1 = Q2 = Q3 = 1, aplicando pulsos na entrada CLK do sistema, temos:

CLK Q0 Q1 Q2 Q3 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 0 1 0 0 1 1 0

|

1 0

16 clock

1 1 1

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

Prof. Marcelo Wendling

74 Assim, para implementarmos um contador decrescente qualquer, utilizamos a mesma lgica implementada nos contadores crescentes.

Exemplo 7: Contador de Eh 2h, utilizando o segundo modo de contagem e reset inicial:

Dessa maneira, utilizando essa mesma lgica podemos implementar um contador assncrono crescente / decrescente com uma varivel de controle.

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

Prof. Marcelo Wendling

75 4.4. Contador Assncrono Crescente / Decrescente de 3 bits

No circuito acima, quando X = 0, a contagem crescente e quando X = 1 a contagem decrescente.

Exerccio: Implemente contadores assncronos que executem as seguintes sequncias:

(a) de 8 a 0, com o primeiro modo de contagem; (b) de 8 a 0, com o segundo modo de contagem e reset inicial; (c) de 9 a 2, com o primeiro modo de contagem e reset inicial; (d) de 9 a 2, com o segundo modo de contagem e reset inicial; e (e) contagem de 4 bits crescente / decrescente, com uma varivel X de controle (se X = 0 contagem decrescente).

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

Prof. Marcelo Wendling

76 4.5. Exerccios de Fixao 1) Implemente um contador assncrono de 4 bits crescente, com reset automtico.

2)

Implemente um contador assncrono de mdulo 8.

3)

Implemente um contador assncrono, com reset automtico, de mdulo 22. Qual a frequncia de sada do flip-flop do dgito MSB.

4)

Implemente um contador assncrono, com reset, automtico, que conte de 12 at 31.

5)

Implemente um contador assncrono, que conte de 5 at 15.

6)

Implemente um contador assncrono decrescente de 4 bits.

7)

Implemente um contador assncrono, com reset automtico, que conte de 21 at 2.

8)

Implemente um contador assncrono, com reset automtico, que conte de 31 at 12.

9)

Implemente um contador assncrono, com reset automtico, que conte de 15 at 5.

10) Implemente um contador de 4 bits, crescente / decrescente, com uma varivel X de controle.

11) Implemente um contador assncrono decrescente, que conte de 3 h Ch, com reset inicial. (Contagem: 3 2 1 0 F E D C 3)

Curso de Lgica Sequencial Cap. 4: Circuitos Sequenciais II: Contadores Assncronos

Prof. Marcelo Wendling

Anda mungkin juga menyukai

- Configuração e programação CLP e IHMDokumen25 halamanConfiguração e programação CLP e IHMJuliano Marcio DA Silva78% (9)

- 810 D SERVICE START-UPDokumen4 halaman810 D SERVICE START-UPLincoln Antonio100% (1)

- Sub Rede Trabalho de SalaDokumen4 halamanSub Rede Trabalho de SalaargusBelum ada peringkat

- Philips Chasis LC4.3U AADokumen89 halamanPhilips Chasis LC4.3U AACarlos A. TorresBelum ada peringkat

- Slides de Eletrônica: Osciladores LC e Cristais de QuartzoDokumen67 halamanSlides de Eletrônica: Osciladores LC e Cristais de QuartzoOtavioBelum ada peringkat

- Tutorial Configuração Comunicação CLP OMRON SYSMAC CJ1M - CPU 13Dokumen13 halamanTutorial Configuração Comunicação CLP OMRON SYSMAC CJ1M - CPU 13nbj2350% (2)

- Eletricista Predial NovaDokumen150 halamanEletricista Predial NovadanielmottasilvaBelum ada peringkat

- Memórias Latch SR e Flip-Flop JK na práticaDokumen14 halamanMemórias Latch SR e Flip-Flop JK na práticaPaulo SilvaBelum ada peringkat

- Estudo de Transformadores TrifásicosbifásicosDokumen154 halamanEstudo de Transformadores TrifásicosbifásicosFrancisco SilvaBelum ada peringkat

- CP Duo e Elipse Scada via MODBUSDokumen32 halamanCP Duo e Elipse Scada via MODBUSVolnei Junior100% (2)

- Circuitos Logicos CombinacionaisDokumen184 halamanCircuitos Logicos CombinacionaisVagner VieiraBelum ada peringkat

- 03 Funcoes Logicas PDFDokumen47 halaman03 Funcoes Logicas PDFPedro ThiagoBelum ada peringkat

- Transmissão em Banda BaseDokumen49 halamanTransmissão em Banda BaseDaniel Sá Araújo100% (1)

- 09 Osciladores TransistorizadosDokumen8 halaman09 Osciladores TransistorizadosF LuiGui Quispe OchoaBelum ada peringkat

- Osciladores Capitulo 10 PDFDokumen11 halamanOsciladores Capitulo 10 PDFErickson Fabian CastilloBelum ada peringkat

- Exercícios de PneumáticaDokumen2 halamanExercícios de PneumáticaTecmecânico100% (1)

- Filtros RC passa-baixa e passa-altaDokumen6 halamanFiltros RC passa-baixa e passa-altaLeandro Gielow FerroBelum ada peringkat

- Checklist completo para avaliação de notebooksDokumen2 halamanChecklist completo para avaliação de notebooksIvanir Ferreira da Silva80% (5)

- Reguladores 78XX e 79XX para fontes de alimentaçãoDokumen4 halamanReguladores 78XX e 79XX para fontes de alimentaçãoPaulo RobertoBelum ada peringkat

- Osciladores Lineares: Circuitos e Princípios BásicosDokumen36 halamanOsciladores Lineares: Circuitos e Princípios BásicosRafael Baptista Brandão0% (1)

- Circuitos Lógicos Sequenciais e MemóriasDokumen69 halamanCircuitos Lógicos Sequenciais e MemóriasabednegoBelum ada peringkat

- Contadores AssíncronosDokumen3 halamanContadores AssíncronosFelipe Araújo Dos SantosBelum ada peringkat

- (ROM) Tablet Navcity NT1710 2º EdiçãoDokumen6 halaman(ROM) Tablet Navcity NT1710 2º EdiçãoDárcio MonteiroBelum ada peringkat

- Relatorio Contador OriginalDokumen12 halamanRelatorio Contador OriginalFofuchinho MphiliBelum ada peringkat

- Circuitos Digitais AnáliseDokumen78 halamanCircuitos Digitais AnálisePedro T V Souza100% (1)

- Sist Distrib MotivaçãoDokumen19 halamanSist Distrib MotivaçãoJoshuamiginola100% (1)

- Funcionamento e aplicações de sincros e servomecanismosDokumen102 halamanFuncionamento e aplicações de sincros e servomecanismosIsrael JuniorBelum ada peringkat

- Circuito lógico para controle de silo de grãosDokumen3 halamanCircuito lógico para controle de silo de grãosadriano santos50% (2)

- Máquinas Síncronas - 2016-2 PDFDokumen195 halamanMáquinas Síncronas - 2016-2 PDFRafael RoratoBelum ada peringkat

- TRB SDC-2022 S1 220623 192038Dokumen2 halamanTRB SDC-2022 S1 220623 192038Soares ViníciusBelum ada peringkat

- Relatório Projeto SemáforoDokumen7 halamanRelatório Projeto SemáforoJucelino JúniorBelum ada peringkat

- Flip Flop RelatorioDokumen23 halamanFlip Flop RelatorioLiana RitterBelum ada peringkat

- Homenagem à trajetória maçônica de Frank PerlimDokumen12 halamanHomenagem à trajetória maçônica de Frank PerlimRenato.'.Belum ada peringkat

- Introdução aos TransistoresDokumen79 halamanIntrodução aos TransistoresDaniel Bello BoaventuraBelum ada peringkat

- Somador Completo e Meio SomadorDokumen24 halamanSomador Completo e Meio SomadorKarinesaBelum ada peringkat

- Lógica Sequencial - CIs Contadores e ExercíciosDokumen93 halamanLógica Sequencial - CIs Contadores e ExercíciosLuiz Paulo OliveiraBelum ada peringkat

- EXERCICIOS Flip Flops e ContadoresDokumen3 halamanEXERCICIOS Flip Flops e ContadoresmarcosBelum ada peringkat

- Contador JohnsonDokumen2 halamanContador JohnsonMarcelo Dhom100% (1)

- Aula 7 - Codificadores e Decodificadores PDFDokumen37 halamanAula 7 - Codificadores e Decodificadores PDFVictor Jesus Delgado SantosBelum ada peringkat

- Cálculo Numérico - Bases, Erros e Zeros de FunçõesDokumen67 halamanCálculo Numérico - Bases, Erros e Zeros de Funçõesapdf20Belum ada peringkat

- Codificadores Binário-Gray 4-bitsDokumen7 halamanCodificadores Binário-Gray 4-bitsRonildo NicodemosBelum ada peringkat

- Álgebra Booleana e Simplificação de CircuitosDokumen27 halamanÁlgebra Booleana e Simplificação de CircuitosRafa SouzaBelum ada peringkat

- Resolução de equações cúbicasDokumen7 halamanResolução de equações cúbicasAguinaldo MendesBelum ada peringkat

- Aula prática sobre portas lógicas e displays de 7 segmentosDokumen21 halamanAula prática sobre portas lógicas e displays de 7 segmentosPaulo SilvaBelum ada peringkat

- Aula 5 - Circuitos Lógicos CombinacionaisDokumen12 halamanAula 5 - Circuitos Lógicos CombinacionaisCarlos Alberto SeboldBelum ada peringkat

- Lista de Exercicios Circuitos LógicosDokumen3 halamanLista de Exercicios Circuitos LógicosAndre BomjardimBelum ada peringkat

- Zeros Reais Newton Raphson e Secante 2018 2Dokumen8 halamanZeros Reais Newton Raphson e Secante 2018 2HORUS_KHANBelum ada peringkat

- Critério Routh-Hurwitz para análise de estabilidade de sistemas de controleDokumen3 halamanCritério Routh-Hurwitz para análise de estabilidade de sistemas de controlegustavo luiz0% (1)

- Lista de TPS de Apontamento Dos Principais Satélites de Canais em Banda Ku (15°w, 30°w, 40Dokumen7 halamanLista de TPS de Apontamento Dos Principais Satélites de Canais em Banda Ku (15°w, 30°w, 40Anderson BadauíBelum ada peringkat

- 03 - Circuitos Combinacionais-20182Dokumen27 halaman03 - Circuitos Combinacionais-20182AlanCrystianSantosBelum ada peringkat

- Ponte-H Com Controle PWM (Mec009)Dokumen5 halamanPonte-H Com Controle PWM (Mec009)nazuragomesBelum ada peringkat

- Linguagem CDokumen85 halamanLinguagem CCarlos Neto100% (1)

- Programar Microcontroladores PIC16F62XDokumen21 halamanProgramar Microcontroladores PIC16F62XTiago Caetano50% (2)

- Funcionamento de um Oscilador a Cristal ligado a um multiplicador de freqüências (Classe CDokumen16 halamanFuncionamento de um Oscilador a Cristal ligado a um multiplicador de freqüências (Classe CPoliana Tafarelo NascimentoBelum ada peringkat

- Exp Lab Sistemas DigitaisDokumen33 halamanExp Lab Sistemas DigitaisautojhBelum ada peringkat

- Lronetto - Eng Forno InduçãoDokumen7 halamanLronetto - Eng Forno InduçãoDantes Alves de SantanaBelum ada peringkat

- Notas de Mecanica Quantica II 00Dokumen80 halamanNotas de Mecanica Quantica II 00Alexandre Borges BidinottoBelum ada peringkat

- Relatório 2Dokumen28 halamanRelatório 2Rafael RinconBelum ada peringkat

- Gabarito Lista Complementar Cap01Dokumen3 halamanGabarito Lista Complementar Cap01Miguel PauliBelum ada peringkat

- FC Lista2Dokumen5 halamanFC Lista2Agostinho GinabayBelum ada peringkat

- Relatório Contador Síncrono em AnelDokumen16 halamanRelatório Contador Síncrono em AnelFelix GabrielBelum ada peringkat

- Relatório 3.12Dokumen18 halamanRelatório 3.12Felix GabrielBelum ada peringkat

- Relatório 3.1Dokumen30 halamanRelatório 3.1Felix GabrielBelum ada peringkat

- Relatório 3Dokumen38 halamanRelatório 3Felix GabrielBelum ada peringkat

- Sicoob 2023 06 02 16 46 39Dokumen1 halamanSicoob 2023 06 02 16 46 39Ivanir Ferreira da SilvaBelum ada peringkat

- Lição 2 - Histórico e Definições de AutomaçãoDokumen11 halamanLição 2 - Histórico e Definições de AutomaçãoIvanir Ferreira da SilvaBelum ada peringkat

- Desenvolvimento Da Técnica Do Ar ComprimidoDokumen31 halamanDesenvolvimento Da Técnica Do Ar ComprimidoIvanir Ferreira da SilvaBelum ada peringkat

- Lista CLP PDFDokumen13 halamanLista CLP PDFIvanir Ferreira da SilvaBelum ada peringkat

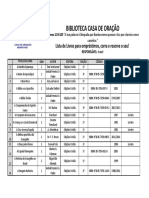

- Cadastro de LivrosDokumen16 halamanCadastro de LivrosIvanir Ferreira da SilvaBelum ada peringkat

- A Evolucao Da Eletronica Embarcada Na Industria Automobilistica BrasileiraDokumen125 halamanA Evolucao Da Eletronica Embarcada Na Industria Automobilistica BrasileiraLuciene Rodrigues De Oliveira Carvalho100% (1)

- Avaliação UE1 - O Papel Do Docente Feita Pela 2 Vez 80PtsDokumen2 halamanAvaliação UE1 - O Papel Do Docente Feita Pela 2 Vez 80PtsIvanir Ferreira da SilvaBelum ada peringkat

- Sistema S e suas entidadesDokumen2 halamanSistema S e suas entidadesIvanir Ferreira da SilvaBelum ada peringkat

- Programação IEC 61131Dokumen242 halamanProgramação IEC 61131Igor GonçalvesBelum ada peringkat

- Avaliação UE2 - Política e Legislaçã Educacional 100Pts 14-09-2017Dokumen2 halamanAvaliação UE2 - Política e Legislaçã Educacional 100Pts 14-09-2017Ivanir Ferreira da SilvaBelum ada peringkat

- Manutenção industrial: técnicas e práticasDokumen31 halamanManutenção industrial: técnicas e práticaswerigueBelum ada peringkat

- Avaliação UE2 - Política e Legislaçã Educacional 100PtsDokumen3 halamanAvaliação UE2 - Política e Legislaçã Educacional 100PtsIvanir Ferreira da SilvaBelum ada peringkat

- Sistemas supervisórios e SCADADokumen61 halamanSistemas supervisórios e SCADAMkleberBelum ada peringkat

- Avaliação UE3 - Fundamentos Da Metodologia SENAI de Educação Profissional 80PtsDokumen3 halamanAvaliação UE3 - Fundamentos Da Metodologia SENAI de Educação Profissional 80PtsIvanir Ferreira da SilvaBelum ada peringkat

- Resumos de artigos sobre aprendizagem e desenvolvimento profissionalDokumen2 halamanResumos de artigos sobre aprendizagem e desenvolvimento profissionalIvanir Ferreira da SilvaBelum ada peringkat

- Scadatutorial BRDokumen148 halamanScadatutorial BRFernanda Galvani de OliveiraBelum ada peringkat

- Acionamento de motores com inversor de frequênciaDokumen9 halamanAcionamento de motores com inversor de frequênciaLarissa XavierBelum ada peringkat

- Acionamento Apostila LaboratorioDokumen24 halamanAcionamento Apostila Laboratorioluis gomezBelum ada peringkat

- Ebook Soft StarterDokumen8 halamanEbook Soft StarterIvanir Ferreira da SilvaBelum ada peringkat

- Sistemas supervisórios e SCADADokumen61 halamanSistemas supervisórios e SCADAMkleberBelum ada peringkat

- Apresentacao e HistoricoDokumen13 halamanApresentacao e HistoricoIvanir Ferreira da SilvaBelum ada peringkat

- Prova de PLC 2017 Turma Da NoiteDokumen2 halamanProva de PLC 2017 Turma Da NoiteIvanir Ferreira da SilvaBelum ada peringkat

- Tutorial de Utilização Do Simulador s7 200Dokumen1 halamanTutorial de Utilização Do Simulador s7 200Ivanir Ferreira da SilvaBelum ada peringkat

- A Eternidade de DeusDokumen8 halamanA Eternidade de DeusIvanir Ferreira da SilvaBelum ada peringkat

- EL04 Motores Eletricos Numero de Polos Rotacao e Deslizamento TecemDokumen1 halamanEL04 Motores Eletricos Numero de Polos Rotacao e Deslizamento TecemDairoBelum ada peringkat

- Sistema Base de DadosDokumen19 halamanSistema Base de Dadosjose suniBelum ada peringkat

- Configurar link secundário MikroTikDokumen2 halamanConfigurar link secundário MikroTikAutor EbomiBelum ada peringkat

- Processadores de despacho múltiplo: arquiteturas VLIW, EPIC e técnicas de especulaçãoDokumen2 halamanProcessadores de despacho múltiplo: arquiteturas VLIW, EPIC e técnicas de especulaçãoMarcos CeronBelum ada peringkat

- Manual LabINO PDFDokumen38 halamanManual LabINO PDFFabiano BertucheBelum ada peringkat

- Manual Servico TV LCD Philco Ph19c Ver ADokumen11 halamanManual Servico TV LCD Philco Ph19c Ver Anaughtybigboy100% (1)

- Super Star Banda LargaDokumen49 halamanSuper Star Banda LargaGeovane BarbosaBelum ada peringkat

- Frases de InformaticaDokumen3 halamanFrases de Informaticajames_adesBelum ada peringkat

- Explicaçiones Gerais Sobre o QuadroDokumen6 halamanExplicaçiones Gerais Sobre o QuadroEduardo LemosBelum ada peringkat

- Estágio em manutenção de computadoresDokumen8 halamanEstágio em manutenção de computadoresMayara Silva100% (2)

- Ports EntryDokumen3 halamanPorts Entryapi-3699756Belum ada peringkat

- Configuração do equipamento ArgosDokumen38 halamanConfiguração do equipamento ArgosMarcio Alves0% (1)

- Tabela de Orcamento InformaticaDokumen3 halamanTabela de Orcamento InformaticaClaudio HenriqueBelum ada peringkat

- Normas para Cabeamento EstruturadoDokumen16 halamanNormas para Cabeamento Estruturadossantos_303882100% (1)

- Exercicios de Redes de ComputadoresDokumen5 halamanExercicios de Redes de ComputadoresNilson PereiraBelum ada peringkat

- LabVIEW em I/O reconfigurável - LED e temporizador com NI-DAQmxDokumen36 halamanLabVIEW em I/O reconfigurável - LED e temporizador com NI-DAQmxSergio Luis Brockveld Jr.Belum ada peringkat

- Fontes Gregas Estratégias de Uso para o Grego Moderno-Monotônico - e Antigo-PolitônicoDokumen14 halamanFontes Gregas Estratégias de Uso para o Grego Moderno-Monotônico - e Antigo-PolitônicoawcatarimBelum ada peringkat

- Plano Disciplina Banco DadosDokumen4 halamanPlano Disciplina Banco DadosWagner FernandesBelum ada peringkat

- Worflow P11Dokumen3 halamanWorflow P11Flávio OliveiraBelum ada peringkat

- Histórico de redes e padrõesDokumen11 halamanHistórico de redes e padrões111babem100% (1)

- Tabela ASCII PDFDokumen3 halamanTabela ASCII PDFLiege Silva da RosaBelum ada peringkat

- BSI 2013 Revista TechnologiesDokumen111 halamanBSI 2013 Revista TechnologiesJordy AllysonBelum ada peringkat

- 9-1 QoS Modelos e Tecnicas de Implementacao PDFDokumen15 halaman9-1 QoS Modelos e Tecnicas de Implementacao PDFEmanuel SilvaBelum ada peringkat

- Proteo PC PLC Programming Manual BPT (REV A)Dokumen59 halamanProteo PC PLC Programming Manual BPT (REV A)EMERSON100% (1)

- Sistema Saci ensina programação onlineDokumen10 halamanSistema Saci ensina programação onlinePedroBelum ada peringkat