Lecture Plan: Code & Name of Subject: 141403 - Computer Organization and Architecture Unit No: 4

Diunggah oleh

CharanDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Lecture Plan: Code & Name of Subject: 141403 - Computer Organization and Architecture Unit No: 4

Diunggah oleh

CharanHak Cipta:

Format Tersedia

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Memory organization

RAM composed of a large number of (2

M)

of addressable

locations, each of which stores a w-bit word.

RAM operates as follows: first the address of the target location to

be accessed is transferred via the address bus to the RAMs address

buffer.

The address is then processed by the address decoder, which

selects the required location in the storage cell unit.

If a read operation is requested, the contents of the addressed

location are

transferred from the storage cell unit to the data buffer and from there to

the data bus.

If a write operation is requested, the word to be stored is

transferred from the data bus to the selected location in the stored unit.

The storage unit is made up of many identical 1-bit memory cells

and their

Interconnections. In each line connected to the storage cell unit, we can

expect to

find a driver that acts as either an amplifier or a transducer of physical

signals.

Organization

assume that each word is stored in a single track and that each

access results

In the transfer of a block of words.

The address of the data to be accessed is applied to the address

decoder, whose output determines the track to be used and the location of

the desired block of

Information within the track.

the track address determines the particular read-write head to

be selected.The selected head is moved into position to transfer data to of

from the target track.

A track position indicator generates the address of the block

that isCurrently passing the read-write head.

The generated address is compared with the block address

produced by the address decoder.

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

The selected head is enabled and the data transfer between the

storage track

and the memory data buffer register begins.

The read-write head is disabled when a complete block of

information has

been transferred.

Static memories (RAM)

Circuits capable of retaining their state as long as power is applied

Static RAM(SRAM)

volatile

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

DRAMS:

Charge on a capacitor

Needs Refreshing

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Synchronous DRAMs

Synchronized with a clock signal

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Memory system considerations

Cost

Speed

Power dissipation

Size of chip

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Principle of locality:

Temporal locality (locality in time): If an item is referenced, it will tend to

be referenced again soon.

Spatial locality (locality in space): If an item is referenced, items whose

addresses are close by will tend to be referenced soon.

Sequentiality (subset of spatial locality ).

The principle of locality can be exploited implementing the memory of

computer as a memory hierarchy, taking advantage of all types of memories.

Method: The level closer to processor (the fastest) is a subset of any level

further away, and all the data is stored at the lowest level (the slowest).

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

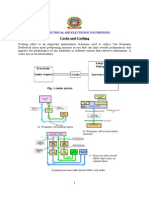

Cache Memories

Speed of the main memory is very low in comparison with the speed of

processor

For good performance, the processor cannot spend much time of its time

waiting to access instructions and data in main memory.

Important to device a scheme that reduces the time to access the

information

An efficient solution is to use fast cache memory

When a cache is full and a memory word that is not in the cache is

referenced, the

cache control hardware must decide which block should be removed to

create space for the new block that contain the referenced word.

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

The basics of Caches

" The caches are organized on basis of blocks, the smallest amount of data

which can be copied between two adjacent levels at a time.

" If data requested by the processor is present in some block in the upper

level,

it is called a hit.

" If data is not found in the upper level, the request is called a miss and the

data is retrieved from the lower level in the hierarchy.

" The fraction of memory accesses found in the upper level is called a hit

ratio.

" The storage, which takes advantage of locality of accesses is called a cache

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Performance of caches Accessing

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Accessing a Cache

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Virtual memory

Virtual memory is a computer system technique which gives an

application program the impression that it has contiguous working memory

(an address space), while in fact it may be physically fragmented and may

even overflow on to disk storage.

Virtual memory provides two primary functions:

1. Each process has its own address space, thereby not required to be

relocated nor required to use relative addressing mode.

2. Each process sees one contiguous block of free memory upon launch.

Fragmentation is hidden.

All implementations (Excluding emulators) require hardware support.

This is typically in the form of a Memory Management Unit built into the

CPU.

Systems that use this technique make programming of large

applications easier and use real physical memory (e.g. RAM) more

efficiently than those without virtual memory. Virtual memory differs

significantly from memory virtualization in that virtual memory allows

resources to be virtualized as memory for a specific system, as opposed to a

large pool of memory being virtualized as smaller pools for many different

systems.

Note that "virtual memory" is more than just "using disk space to

extend physical memory size" - that is merely the extension of the memory

hierarchy to include hard disk drives. Extending memory to disk is a normal

consequence of using virtual memory techniques, but could be done by other

means such as overlays or swapping programs and their data completely out

to disk while they are inactive. The definition of "virtual memory" is based

on redefining the address space with a contiguous virtual memory addresses

to "trick" programs into thinking they are using large blocks of contiguous

addresses.

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Paged virtual memory

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Compiler time: If it is known in advance that a program will reside

at a specific location of main memory, then the compiler may be told to

build the object code with absolute addresses right away. For example, the

boot sect in a bootable disk may be compiled with the starting point of code

set to 007C:0000.

Load time: It is pretty rare that we know the location a program will

be assigned ahead of its execution. In most cases, the compiler must

generate relocatable code with logical addresses. Thus the address

translation may be performed on the code during load time. Figure 3 shows

that a program is loaded at location x. If the whole program resides on a

monolithic block, then every memory reference may be translated to be

physical by added to x.

Memory Management Requirements

Partitioning Strategies Fixed

Fixed Partitions divide memory into equal sized pieces (except

for OS)

Degree of multiprogramming = number of partitions

Simple policy to implement

All processes must fit into partition space

Find any free partition and load the process

Partitioning Strategies Variable

Idea: remove wasted memory that is not needed in each partition

Memory is dynamically divided into partitions based on process needs

Definition:

Hole: a block of free or available memory

Holes are scattered throughout physical memory

External fragmentation

memory that is in holes too small to be usable by any process

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Memory Allocation Mechanism

MM system maintains data about free and allocated memory alternatives

Bit maps - 1 bit per allocation unit

Linked Lists - free list updated and coalesced when not allocated to a

process

At swap-in or process create

Find free memory that is large enough to hold the process

Allocate part (or all) of memory to process and mark remainder as free

Compaction

Moving things around so that holes can be consolidated

Expensive in OS time

Memory Management Policies

First Fit: scan free list and allocate first hole that is large enough fast

Next Fit: start search from end of last allocation

Best Fit: find smallest hole that is adequate slower and lots of

fragmentation

Worst fit: find largest hole

OS

process 1

process 2

process 3

O

S

process 1

process 3

Process 2

Terminates

OS

process 1

process 3

Process 4

Starts

process 4

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

ASSOCIATIVE MEMORY

A content addressable processor is a content addressable memory

with the added capability to write in parallel (multi-write) into all

those words indicating agreement as the result of a search.

A typical associative memory has the following

components:

Memory array

Comparand register

Mask register

Match/Mismatch (response) register

Multiple match resolver

Search logic

Input/Output register

Word select register

--Memory Cell Array provides storage and search medium for data.

--Comparand Register contains the data to be compared against the

contents of the memory cell array.

--Mask Register is used to mask off portions of the data words

which do not participate in the operations.

Comparand Reg.

Mask Reg.

Memory Cell

Array

Input/Output Reg.

Tag Reg.

Multiple

Match

Resolver

Word Select

Reg.

Some/

None Bit

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

-- Word Select Register is used to mask off the memory

words which do not participate in the operation.

-- Match/Mismatch Register indicates the success or failure of a

search operation.

--Input/Output Buffer acts as an interface between associative

memory and the outside word.

-- Multiple Match Resolver narrows down the scope of the

search to a specific location in the memory cell array in a cases

where more than one memory word will satisfy the search

condition(s).

-- Some/None bit shows the overall search result.

SECONDARY STORAGE DEVICES

Optical storage, the typical Optical disc, stores information in deformities on the surface

of a circular disc and reads this information by illuminating the surface with a laser diode

and observing the reflection. Optical disc storage is non-volatile. The deformities may be

permanent (read only media ), formed once (write once media) or reversible (recordable

or read/write media). The following forms are currently in common use:

CD, CD-ROM, DVD, BD-ROM: Read only storage, used for mass distribution of

digital information (music, video, computer programs)

CD-R, DVD-R, DVD+R BD-R: Write once storage, used for tertiary and off-line

storage

CD-RW, DVD-RW, DVD+RW, DVD-RAM, BD-RE: Slow write, fast read storage,

used for tertiary and off-line storage

Ultra Density Optical or UDO is similar in capacity to BD-R or BD-RE and is slow

write, fast read storage used for tertiary and off-line storage.

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

Magneto-optical disc storage is optical disc storage where the magnetic state on a

ferromagnetic surface stores information. The information is read optically and written by

combining magnetic and optical methods. Magneto-optical disc storage is non-volatile,

sequential access, slow write, fast read storage used for tertiary and off-line storage.

A Compact Disc (also known as a CD) is an optical disc used to store digital data. It was

originally developed to store sound recordings exclusively, but later it also allowed the

preservation of other types of data. Audio CDs have been commercially available since

October 1982. In 2009, they remain the standard physical storage medium for audio.

Standard CDs have a diameter of 120 mm and can hold up to 80 minutes of

uncompressed audio (700 MB of data). The Mini CD has various diameters ranging from

60 to 80 mm; they are sometimes used for CD singles or device drivers, storing up to 24

minutes of audio.

The technology was eventually adapted and expanded to encompass data storage CD-

ROM, write-once audio and data storage CD-R, rewritable media CD-RW, Video

Compact Discs (VCD), Super Video Compact Discs (SVCD), PhotoCD, PictureCD, CD-

i, and Enhanced CD.

Magnetic disk memories

A magnetic disk consists of 1-12 platters (metal or glass disk covered with magnetic

recording material on bothsides), with diameters between 1-3.5 inches

Each platter is comprised of concentric tracks (5-30K) and each track is divided into

sectors (100 500 per track, each about 512 bytes)

A movable arm holds the read/write heads for each disk surface and moves them all

in tandem a cylinder of data is accessible at a time

To read/write data, the arm has to be placed on the correct track this seek time

usually takes 5 to 12 ms on average can take less if there is spatial locality

Rotational latency is the time taken to rotate the correct sector under the head

average is typically more than 2 ms (15,000 RPM)

Transfer time is the time taken to transfer a block of bits out of the disk and is

typically 3 65 MB/second.

http://csetube.co.nr/

h

t

t

p

:

/

/

c

s

e

t

u

b

e

.

c

o

.

n

r

/

Lecture plan

Code & name of subject: 141403 computer organization and architecture

Unit no: 4

http://csetube.co.nr/

Anda mungkin juga menyukai

- SAS Programming Guidelines Interview Questions You'll Most Likely Be AskedDari EverandSAS Programming Guidelines Interview Questions You'll Most Likely Be AskedBelum ada peringkat

- Memory Organization: Registers, Cache, Main Memory, Magnetic Discs, and Magnetic TapesDokumen15 halamanMemory Organization: Registers, Cache, Main Memory, Magnetic Discs, and Magnetic TapesShivam KumarBelum ada peringkat

- Research Paper On Cache MemoryDokumen8 halamanResearch Paper On Cache Memorypib0b1nisyj2100% (1)

- Nonvolatil: RotationalDokumen6 halamanNonvolatil: RotationalPrafulla ShaijumonBelum ada peringkat

- Computer ArchitectureDokumen14 halamanComputer ArchitectureMartine Mpandamwike Jr.Belum ada peringkat

- Shashank Aca AssignmentDokumen21 halamanShashank Aca AssignmentNilesh KmBelum ada peringkat

- Computer Organization AnswerDokumen6 halamanComputer Organization Answersamir pramanikBelum ada peringkat

- UNIT II - Multi Core ArchitectureDokumen102 halamanUNIT II - Multi Core ArchitectureVivek DubeyBelum ada peringkat

- Cache EntriesDokumen13 halamanCache EntriesAnirudh JoshiBelum ada peringkat

- ICS 143 - Principles of Operating SystemsDokumen83 halamanICS 143 - Principles of Operating SystemsManoj SharmaBelum ada peringkat

- CPU Cache: Details of OperationDokumen18 halamanCPU Cache: Details of OperationIan OmaboeBelum ada peringkat

- Memory Management: Background Swapping Contiguous AllocationDokumen51 halamanMemory Management: Background Swapping Contiguous AllocationFazrul RosliBelum ada peringkat

- TAREKEGN OSA - Computer Organization and ArchitectureDokumen38 halamanTAREKEGN OSA - Computer Organization and Architectureyayatarekegn123Belum ada peringkat

- Computer MemoryDokumen51 halamanComputer MemoryWesley SangBelum ada peringkat

- OS Module IVDokumen73 halamanOS Module IVsitsekharBelum ada peringkat

- Basic Hardware IssuesDokumen18 halamanBasic Hardware IssuesRakesh PatilBelum ada peringkat

- CO - MODULE - 2 (A) - Memory-SystemDokumen78 halamanCO - MODULE - 2 (A) - Memory-Systemddscraft123Belum ada peringkat

- Memory-Management StrategiesDokumen70 halamanMemory-Management StrategiesNico Jhon R AlmarinezBelum ada peringkat

- Unit 4 NotesDokumen36 halamanUnit 4 NotesHare Ram SinghBelum ada peringkat

- Unit IV CAL 817 Operating SystemDokumen17 halamanUnit IV CAL 817 Operating SystemRAZEB PATHANBelum ada peringkat

- Unit 4 - Computer System Organisation - WWW - Rgpvnotes.inDokumen8 halamanUnit 4 - Computer System Organisation - WWW - Rgpvnotes.inmukulgrd1Belum ada peringkat

- Krishna M. Kavi The University of Alabama in Huntsville: Cache MemoriesDokumen5 halamanKrishna M. Kavi The University of Alabama in Huntsville: Cache MemoriesNithyendra RoyBelum ada peringkat

- Term Paper: Cahe Coherence SchemesDokumen12 halamanTerm Paper: Cahe Coherence SchemesVinay GargBelum ada peringkat

- Memory Management OverviewDokumen9 halamanMemory Management OverviewbernardoakoBelum ada peringkat

- CO & OS Unit-3 (Only Imp Concepts)Dokumen26 halamanCO & OS Unit-3 (Only Imp Concepts)0fficial SidharthaBelum ada peringkat

- CPU Cache: From Wikipedia, The Free EncyclopediaDokumen19 halamanCPU Cache: From Wikipedia, The Free Encyclopediadevank1505Belum ada peringkat

- What Is The Base Register and What Is The Limit Register?: SystemDokumen9 halamanWhat Is The Base Register and What Is The Limit Register?: SystemGaby Mbugua67% (3)

- Coa BlogDokumen17 halamanCoa BlogA Zizi ZiziBelum ada peringkat

- Memory Management: Background Swapping Contiguous Allocation Paging Segmentation Segmentation With PagingDokumen55 halamanMemory Management: Background Swapping Contiguous Allocation Paging Segmentation Segmentation With PagingsumipriyaaBelum ada peringkat

- Main Memory ManagementDokumen7 halamanMain Memory ManagementpoojajadhavBelum ada peringkat

- Chapter-6 Memory ManagementDokumen98 halamanChapter-6 Memory ManagementYasar KhatibBelum ada peringkat

- Memory ManagmentDokumen24 halamanMemory ManagmentRamin Khalifa WaliBelum ada peringkat

- Memory Hierarchy - Introduction: Cost Performance of Memory ReferenceDokumen52 halamanMemory Hierarchy - Introduction: Cost Performance of Memory Referenceravi_jolly223987Belum ada peringkat

- Shared-Memory Multiprocessors - Symmetric Multiprocessing HardwareDokumen7 halamanShared-Memory Multiprocessors - Symmetric Multiprocessing HardwareSilvio DresserBelum ada peringkat

- Caches in Multicore Systems: Universitatea Politehnica Din Timisoara Facultatea de Automatica Şi CalculatoareDokumen7 halamanCaches in Multicore Systems: Universitatea Politehnica Din Timisoara Facultatea de Automatica Şi CalculatoarerotarcalinBelum ada peringkat

- Implementation of Cache MemoryDokumen15 halamanImplementation of Cache MemoryKunj PatelBelum ada peringkat

- Unit 4Dokumen182 halamanUnit 4Vamsi KrishnaBelum ada peringkat

- Memory and ClassificationDokumen8 halamanMemory and Classificationsingh7863Belum ada peringkat

- Lecture 6 8405 Computer ArchitectureDokumen16 halamanLecture 6 8405 Computer ArchitecturebokadashBelum ada peringkat

- Cache MemoryDokumen4 halamanCache MemoryPlay ZoneBelum ada peringkat

- Unit 4aDokumen104 halamanUnit 4aKoushik ThummalaBelum ada peringkat

- Basic Introduction Availability, Security, and Scalability. RAID Technology Made AnDokumen17 halamanBasic Introduction Availability, Security, and Scalability. RAID Technology Made AnvishnuBelum ada peringkat

- Chapter 7Dokumen39 halamanChapter 7gemedakelbesa9Belum ada peringkat

- Memory HierarchyDokumen6 halamanMemory HierarchyIsuru KasthurirathneBelum ada peringkat

- Slides Ch3 Memory ManagementDokumen23 halamanSlides Ch3 Memory ManagementAbuky Ye AmanBelum ada peringkat

- Cache Memory Term PaperDokumen6 halamanCache Memory Term Paperafdttricd100% (1)

- Chapter 8 Main Memory: Bernard Chen Spring 2007Dokumen51 halamanChapter 8 Main Memory: Bernard Chen Spring 2007dolfinblablaBelum ada peringkat

- Computer Organization and Architecture Module 3Dokumen34 halamanComputer Organization and Architecture Module 3Assini Hussain100% (1)

- Memory Hierarchy: Memory Hierarchy Design in A Computer System MainlyDokumen16 halamanMemory Hierarchy: Memory Hierarchy Design in A Computer System MainlyAnshu Kumar TiwariBelum ada peringkat

- Literature Review of Cache MemoryDokumen7 halamanLiterature Review of Cache Memoryafmzhuwwumwjgf100% (1)

- Usha Mittal Institute of Technology SNDT Women'S University: MUMBAI - 400049Dokumen19 halamanUsha Mittal Institute of Technology SNDT Women'S University: MUMBAI - 40004914-Shruti Chavan-CSTBelum ada peringkat

- The University of Zambia in Conjuction With Zambia Ict CollegeDokumen12 halamanThe University of Zambia in Conjuction With Zambia Ict CollegeMartine Mpandamwike Jr.Belum ada peringkat

- Associative MemoryDokumen31 halamanAssociative MemoryaswinpBelum ada peringkat

- Module 4 Coa CoeDokumen10 halamanModule 4 Coa CoeVanshima Kaushik 2003289Belum ada peringkat

- Anatomy of A Program in Memory - Gustavo DuarteDokumen41 halamanAnatomy of A Program in Memory - Gustavo DuarteRigs JuarezBelum ada peringkat

- Main MemoryDokumen20 halamanMain MemoryS.M. SIAMBelum ada peringkat

- Assignment ArbazDokumen11 halamanAssignment Arbazvishwajeet singhBelum ada peringkat

- Cache and Caching: Electrical and Electronic EngineeringDokumen15 halamanCache and Caching: Electrical and Electronic EngineeringEnock OmariBelum ada peringkat

- CEA201-Trương Vĩnh Thịnh-SE17D09Dokumen6 halamanCEA201-Trương Vĩnh Thịnh-SE17D09Ookami GinjiBelum ada peringkat

- Computer Architecture: Computer Architecture Refers To Those Attributes of A System Visible To ADokumen6 halamanComputer Architecture: Computer Architecture Refers To Those Attributes of A System Visible To AKobinaBelum ada peringkat

- MM - Nov 2011 QPDokumen3 halamanMM - Nov 2011 QPCharanBelum ada peringkat

- Hazard (Computer Architecture)Dokumen10 halamanHazard (Computer Architecture)CharanBelum ada peringkat

- Basic Processing Unit: Lecture PlanDokumen15 halamanBasic Processing Unit: Lecture PlanCharanBelum ada peringkat

- Unit1 Cajan10Dokumen222 halamanUnit1 Cajan10Charan100% (1)

- Gta V RGHDokumen3 halamanGta V RGHBog DannBelum ada peringkat

- Inspiron 14 3467 Laptop Service Manual en UsDokumen108 halamanInspiron 14 3467 Laptop Service Manual en UskalteBelum ada peringkat

- Mechanical Chart.01.Dokumen25 halamanMechanical Chart.01.sri7877Belum ada peringkat

- Sas 8 Nursing InformaticsDokumen4 halamanSas 8 Nursing InformaticsmathewdumayacBelum ada peringkat

- Emc CFGMGR - SHDokumen1 halamanEmc CFGMGR - SHRamesh RajaBelum ada peringkat

- Introduction To Processes: Dr. Yann-Hang Lee GWC 224 Yhlee@asu - EduDokumen19 halamanIntroduction To Processes: Dr. Yann-Hang Lee GWC 224 Yhlee@asu - EduChutiyaBelum ada peringkat

- User Manual For E-R Alarm Monitoring SystemDokumen124 halamanUser Manual For E-R Alarm Monitoring SystemTomislav Korencic100% (1)

- Scheduling and DeadlockDokumen14 halamanScheduling and DeadlockSamuel UdoemaBelum ada peringkat

- Compute Basics For Competitive ExamDokumen151 halamanCompute Basics For Competitive ExamHARSHAL KADDAKBelum ada peringkat

- Instalación de Proxmox - Guía CompletaDokumen10 halamanInstalación de Proxmox - Guía CompletaRoberto Malgrado CortésBelum ada peringkat

- Mht-Cet Biology PDFDokumen7 halamanMht-Cet Biology PDFbadamsmith100% (1)

- Scheme of Work: Cambridge IGCSE Information and Communication Technology 0417Dokumen64 halamanScheme of Work: Cambridge IGCSE Information and Communication Technology 0417Benish RehanBelum ada peringkat

- CA PracticalDokumen29 halamanCA PracticalDurgesh DhoreBelum ada peringkat

- CMIDokumen6 halamanCMIChitranjan KumarBelum ada peringkat

- Learn Computer ScienceDokumen24 halamanLearn Computer SciencefabiobonadiaBelum ada peringkat

- Macintosh IisiDokumen64 halamanMacintosh Iisimatthew katzensteinBelum ada peringkat

- 1.0 Introduction To The Personal Computer SystemDokumen35 halaman1.0 Introduction To The Personal Computer SystemAdron LimBelum ada peringkat

- Is - Lecture 1Dokumen37 halamanIs - Lecture 1Suneeta SinghBelum ada peringkat

- In-Memory Columnar Formats in Flash CacheDokumen2 halamanIn-Memory Columnar Formats in Flash CacheNand Lal RiarBelum ada peringkat

- OS Lab ManualDokumen63 halamanOS Lab ManualKaranBelum ada peringkat

- Computer StudiesDokumen17 halamanComputer StudiesMJAY GRAPHICSBelum ada peringkat

- CG-Electronics Product Assembly and ServiciDokumen57 halamanCG-Electronics Product Assembly and ServiciRetchel AmuraoBelum ada peringkat

- Etro8 Memory IcDokumen12 halamanEtro8 Memory IcAr VinBelum ada peringkat

- Linear Block Coding: Presented byDokumen12 halamanLinear Block Coding: Presented bypranay639Belum ada peringkat

- Urkund Report - Roopa - Final Year Report (1) .PDF (D70633383)Dokumen13 halamanUrkund Report - Roopa - Final Year Report (1) .PDF (D70633383)RenjithBelum ada peringkat

- Dell Poweredge R920technical Guide 2018junDokumen52 halamanDell Poweredge R920technical Guide 2018junLeads InsightsBelum ada peringkat

- Datasheet VSMDokumen3 halamanDatasheet VSMGabo NuñezBelum ada peringkat

- Sample File - (Solaris) : by Jeffrey Hunter, Sr. Database AdministratorDokumen2 halamanSample File - (Solaris) : by Jeffrey Hunter, Sr. Database Administratorapi-3701740Belum ada peringkat

- GPW MTB FX Mh01ea ConnectDokumen98 halamanGPW MTB FX Mh01ea ConnecttungocgoogleBelum ada peringkat

- Brother Ads2400n Scanner Ita Usr CDokumen131 halamanBrother Ads2400n Scanner Ita Usr Cmario rossiBelum ada peringkat